шины; на фиг.7, 8 - функциональные схемы соответственно блока формирования сигнала внутренней готовности, блока формирования готовности и блока формирования интерфейсных сигналов; на фиг.9 - компо- новка системы на базе заявляемого устройства..

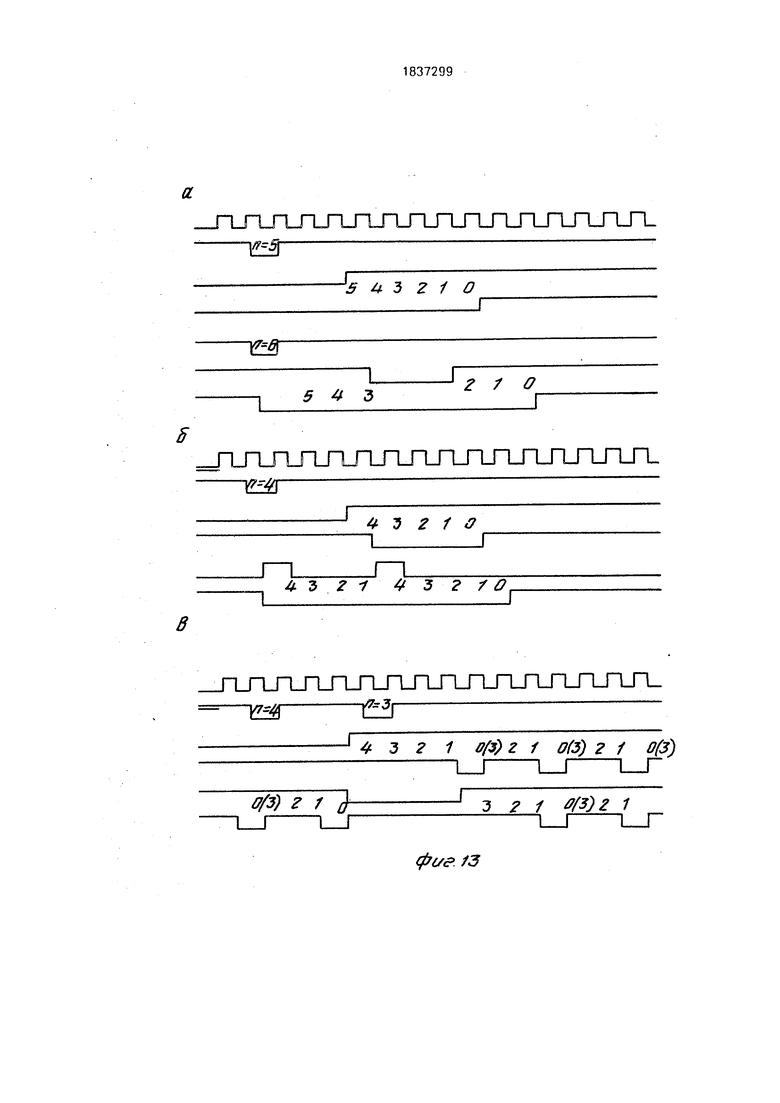

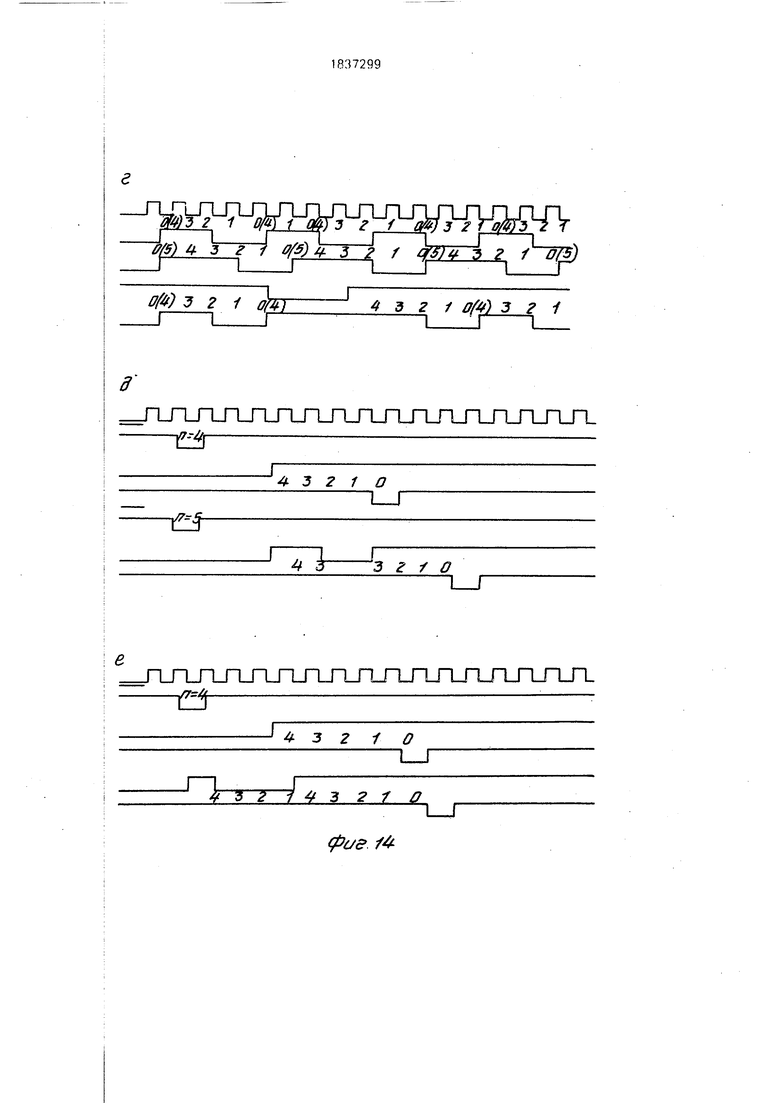

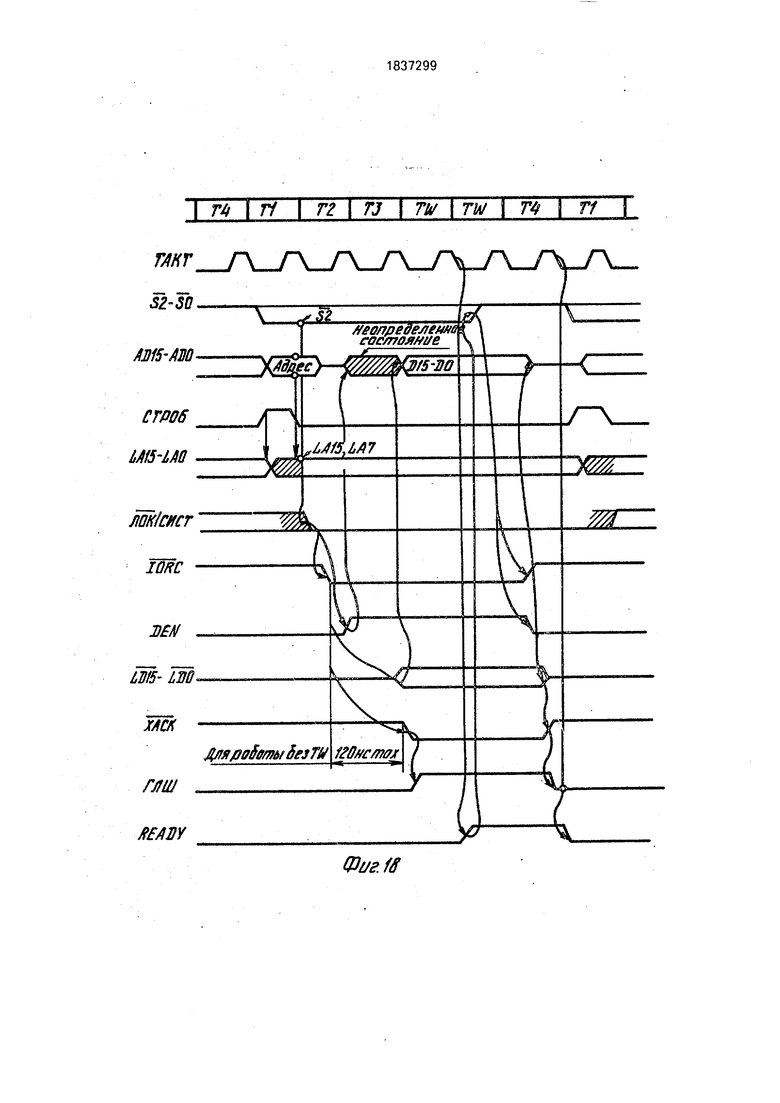

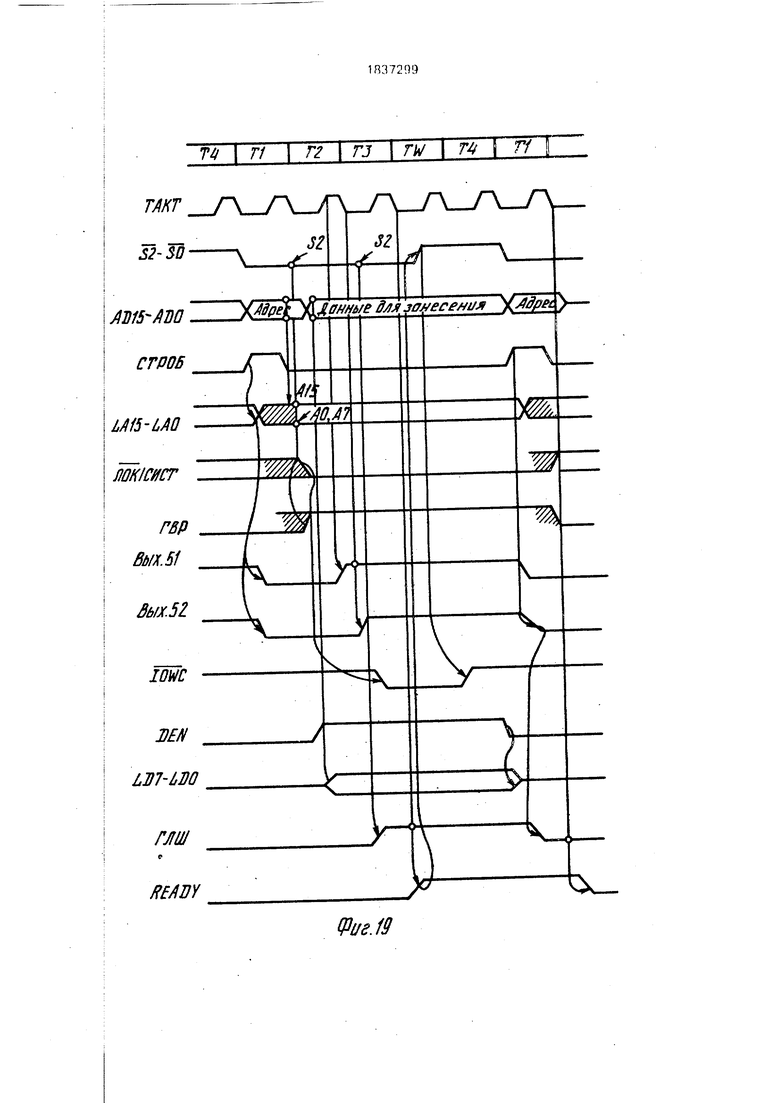

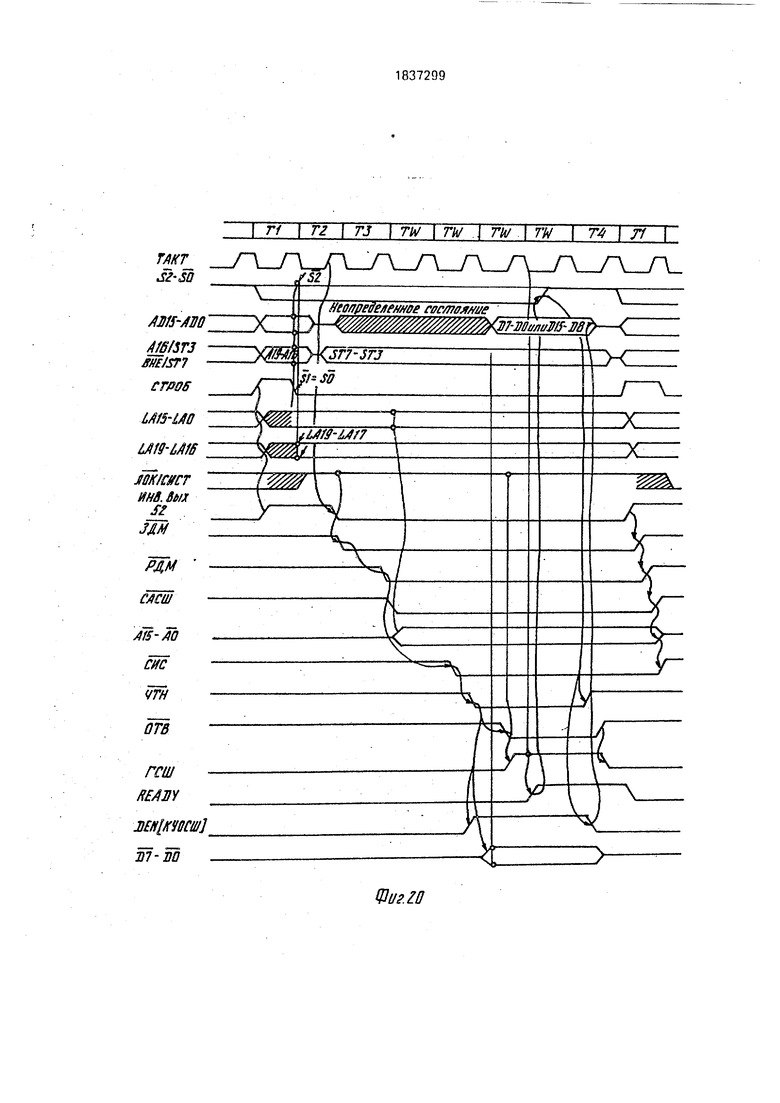

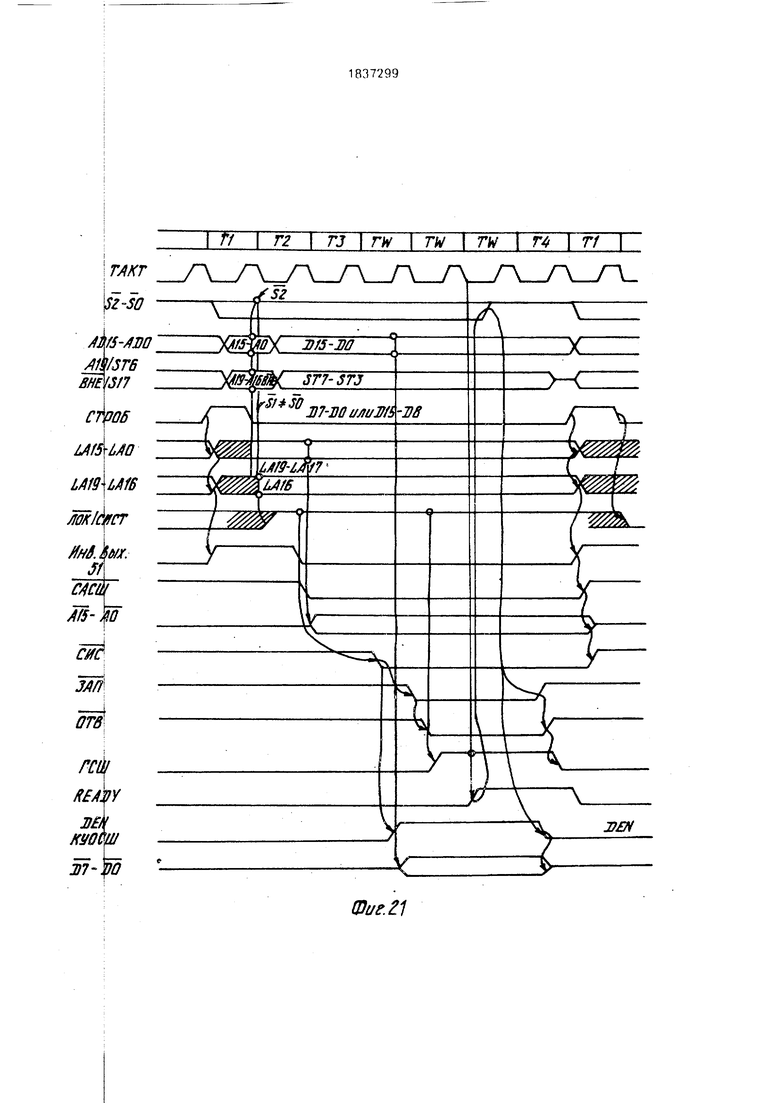

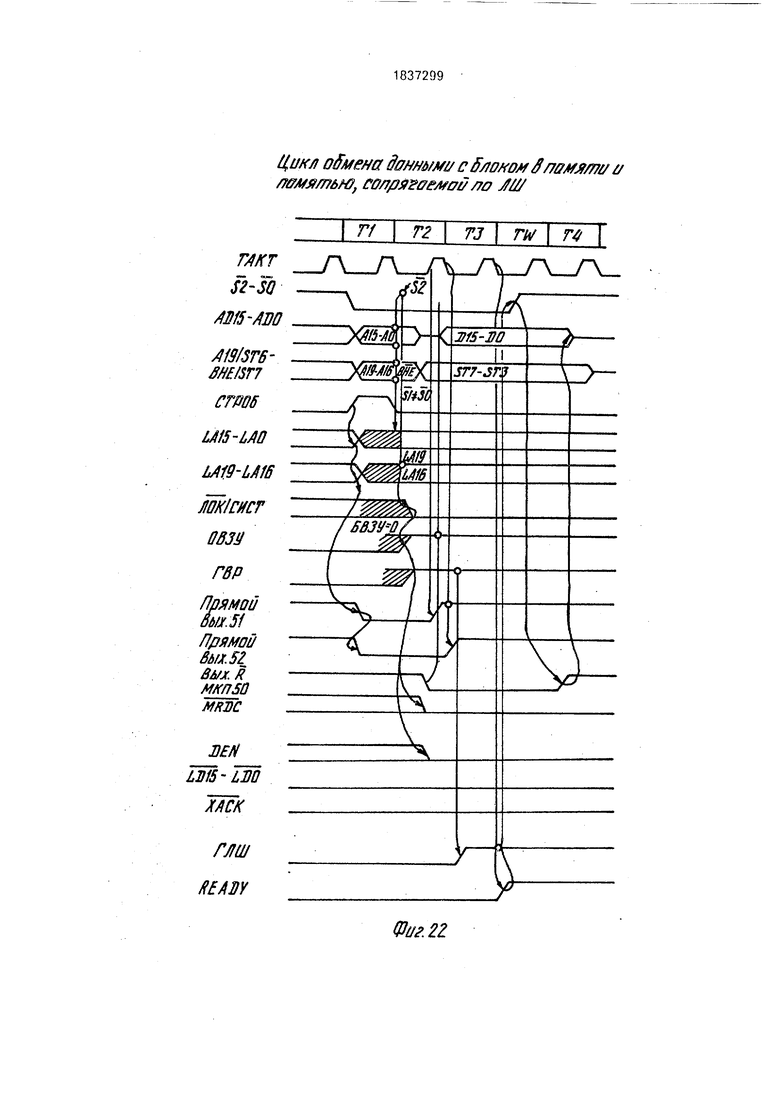

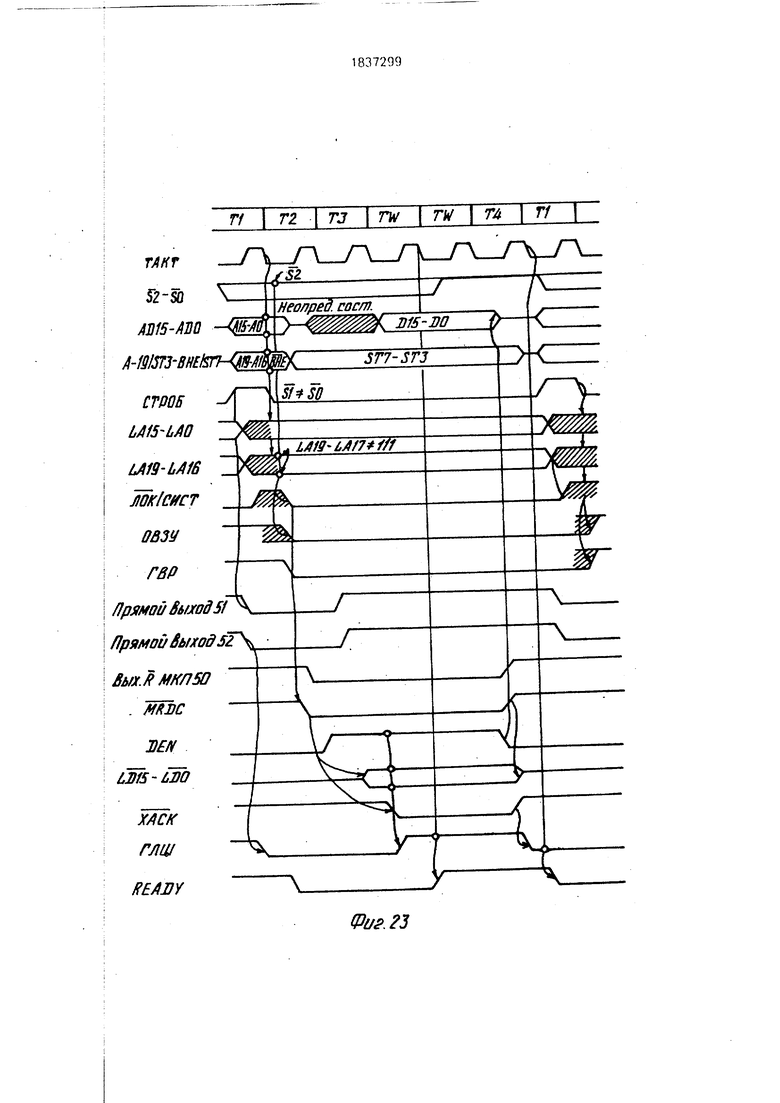

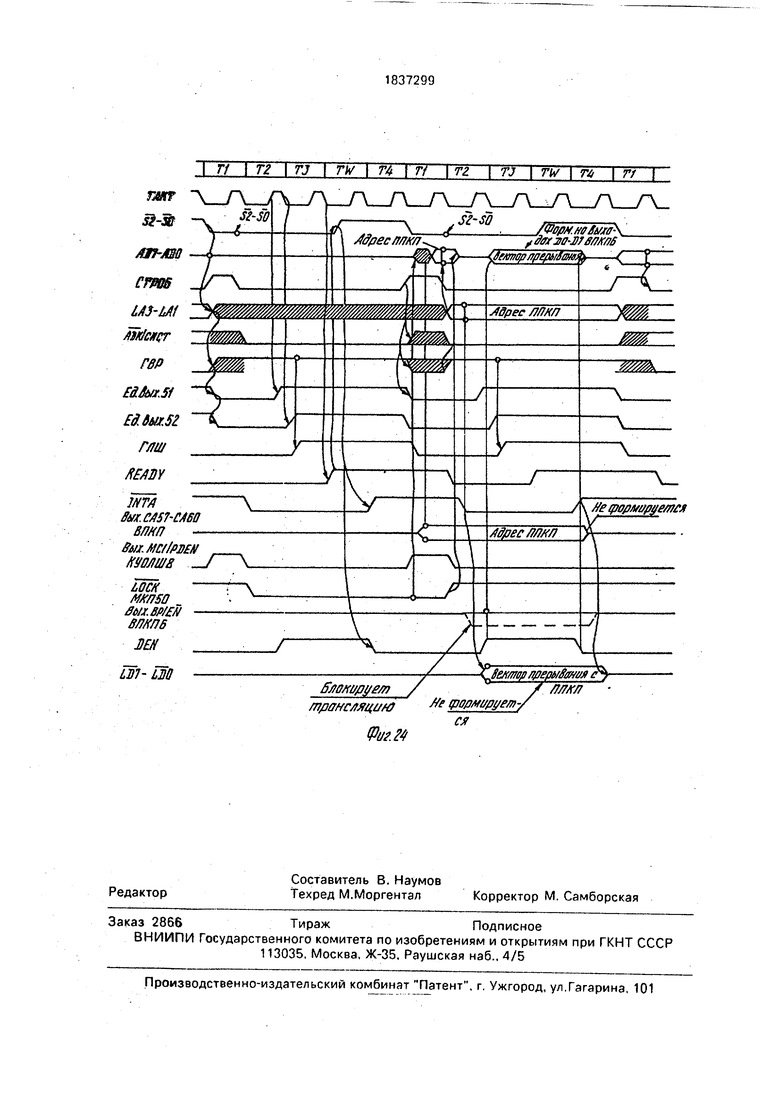

На фиг.10, 11, 12 поясняется порядок программирования таймера. На фиг.13, 14(ate) приведены временные диаграммы работы таймера в различных режимах; на фиг.15 - типы операция обмена данными между микропроцессором и программируемыми контроллерами прерываний; на фиг.15, 17 - схема, поясняющая функциони- рование программируемых контроллеров прерываний в режиме опроса и в режиме автоматической ротации приоритетов; на фиг.18-24 - временные диаграммы работы заявляемого устройства.

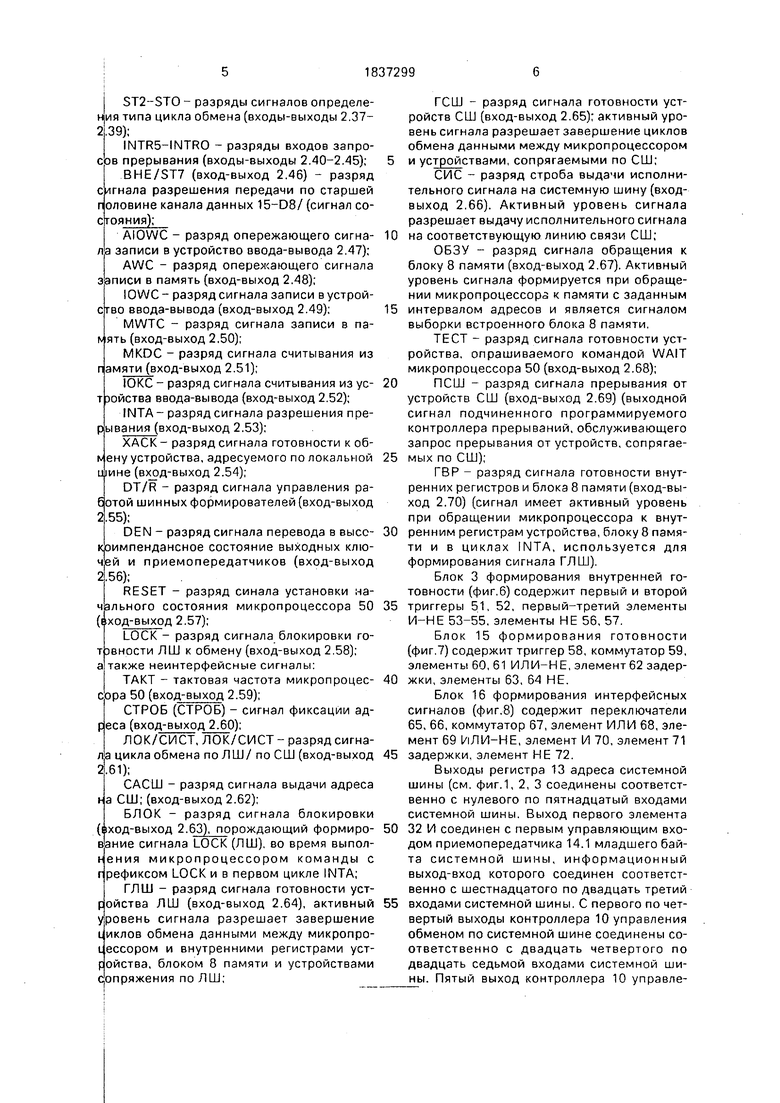

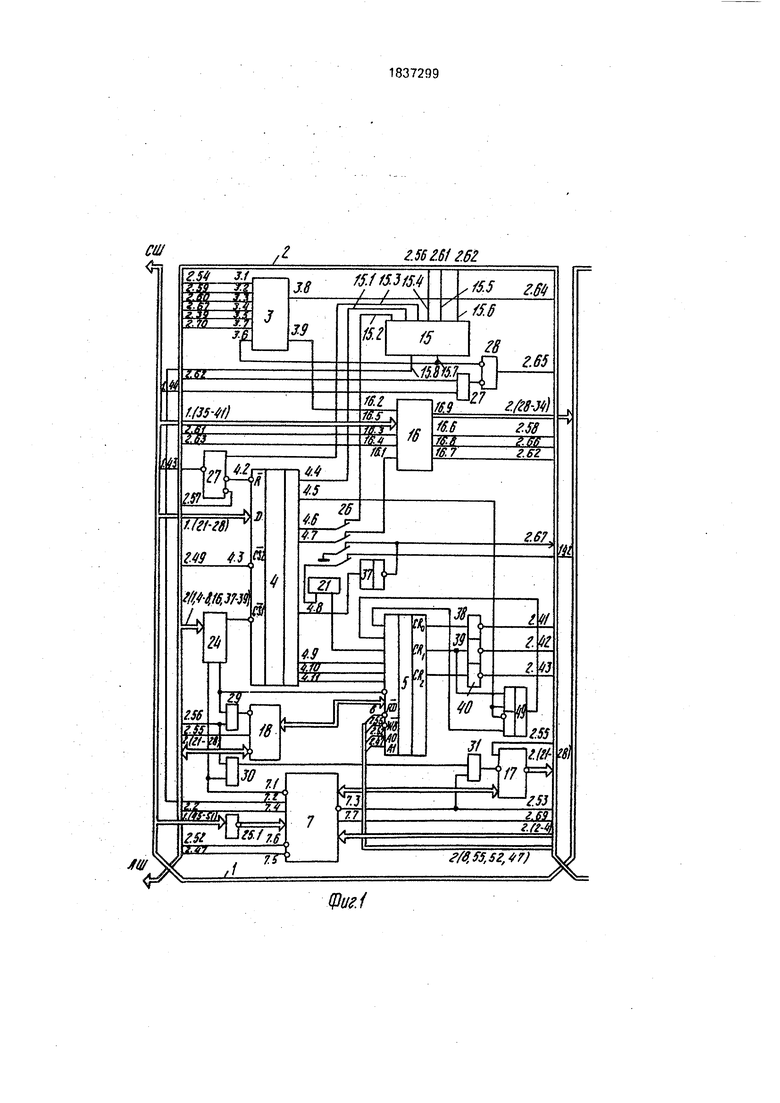

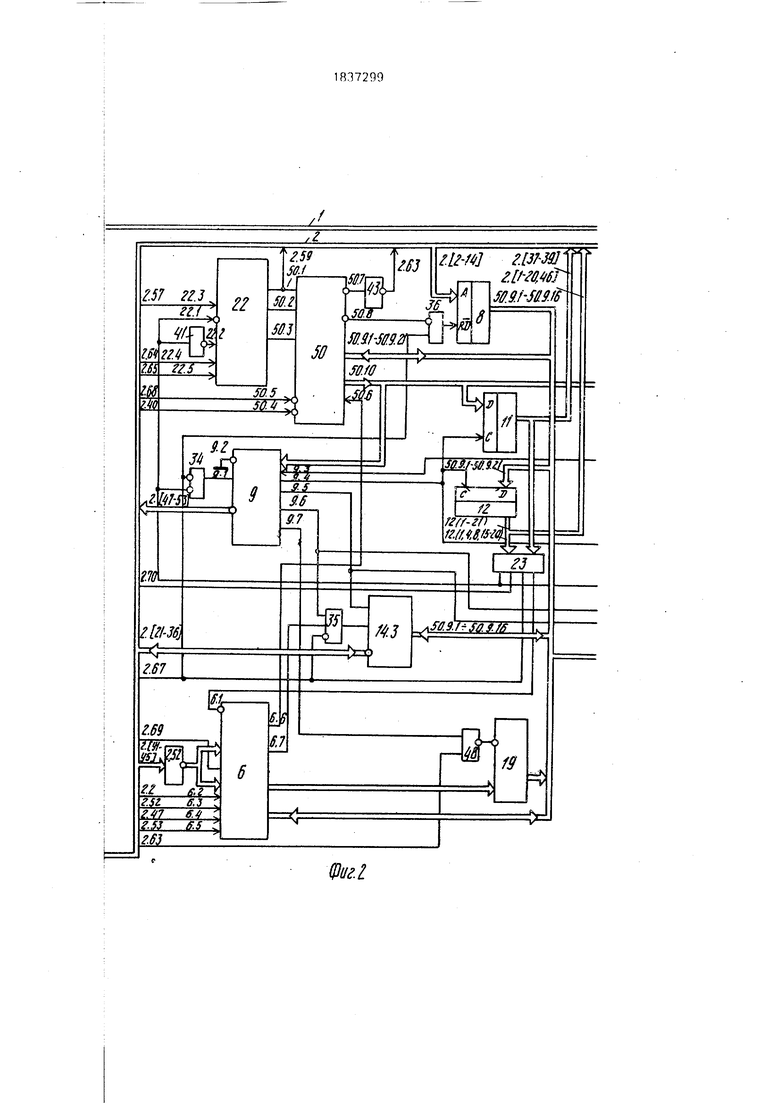

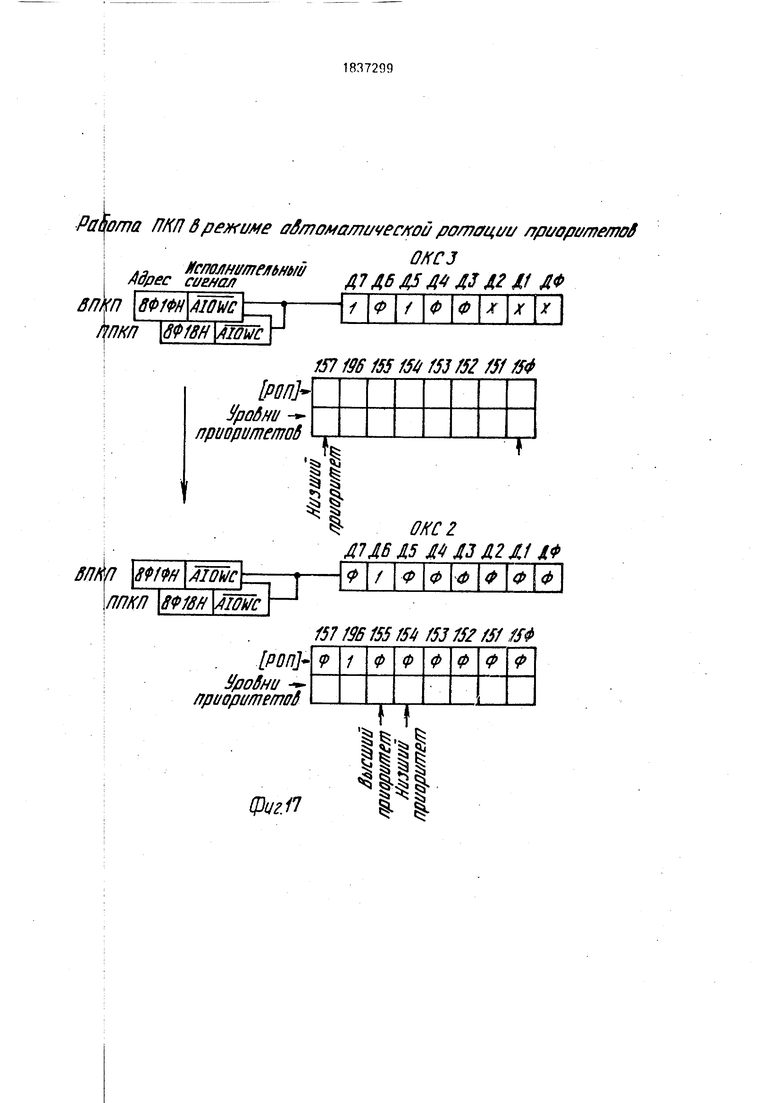

На фиг.1,2, 3 показаны системная шина 1 с вводами-выводами 1,0-1.51, локальная шина 2 с вводами-выводами 2.1-2.70, блок 3 формирования внутренней готовности с первого по седьмой входами 3.1-3.7, пер- вым и вторым выходами 3.8, 3.9, регистр 4 конфигурации с первого по третий управляющими входами 4.1-4.3 и с первого по восьмой выходами 4.4-4.11, таймер 5, ведущий программируемый контроллер 6 прерыва- ний (ВПКП) с первого по пятый управляющими входами 6.1-6,5, с первым и вторым выходами 6.6, 6.7, подчиненный программируемый контроллер 7 прерываний (ППКП) с первого по шестой управляющими входами 7.1-7.6 и управляющим выходом 7.7, блок 8 памяти, контроллер 9 управления обменом по локальной шине (КУОЛШ) с первым 9.1 и вторым 9.2 входами, первым управляющим входом 9,3, с первого по четвертый 9,4-9.7 управляющими выходами, контроллер 10 управления по системной шине (КУОСШ) с первого по третий управляющими входами 10.1-10.3 и с первого по седьмой 10.4-10.10 выходами, регистр 11 фиксации кода типа цикла обмена, регистр 12 адреса с первого по двадцать первый выходами 12.1-12.21, регистр 13 адреса системной шины (РАСШ), приемопередатчик 14.1 младшего байта системной шины (ПМСШ), приемопередатчик 14.2 старшего байта системной шины (ПССШ), приемопередатчик 14.3 локальной шины 2, блок 15 формирования готовности с первого по шестой входами 15.1-15.6 и первым и вторым выходами 15.7, 15.8, блок 16 формирования интерфейсных сигналов с первого по четвертый управляющими входами 16.1-16.4, информационным входом 16.5, первым, вторым и третьим управляющими выходами 16.6-16.8. первый и второй

двунаправленные шинные формирователи 17, 18, шинный формирователь 19 адреса выборки подчиненного контроллера (ШФА), генератор 20 пуска-останова, генератор 21 импульсов, системный генератор 22, содержащий с первого по пятый входы 22.1-22,5, блок 23 памяти коммутации, дешифратор 24 адреса обмена, первую и вторую группы 25,1, 25.2 элементов НЕ, переключатель 26, с первого по пятый элементы ИЛИ 27-31, с первого по шестой элементы И 32-37, с первого по девятый элементы НЕ 38-46, эле- мент 47 неравнозначности, элемент И-НЕ 48, коммутатор 49 сигналов, сопрягаемый микропроцессор 50 с первого по шестой управляющими входами 50.1-50.6, первым и вторым управляющими выходами 50.7, 50.8, адресно-информационной шиной 50.9, управляющей шиной 50.10.

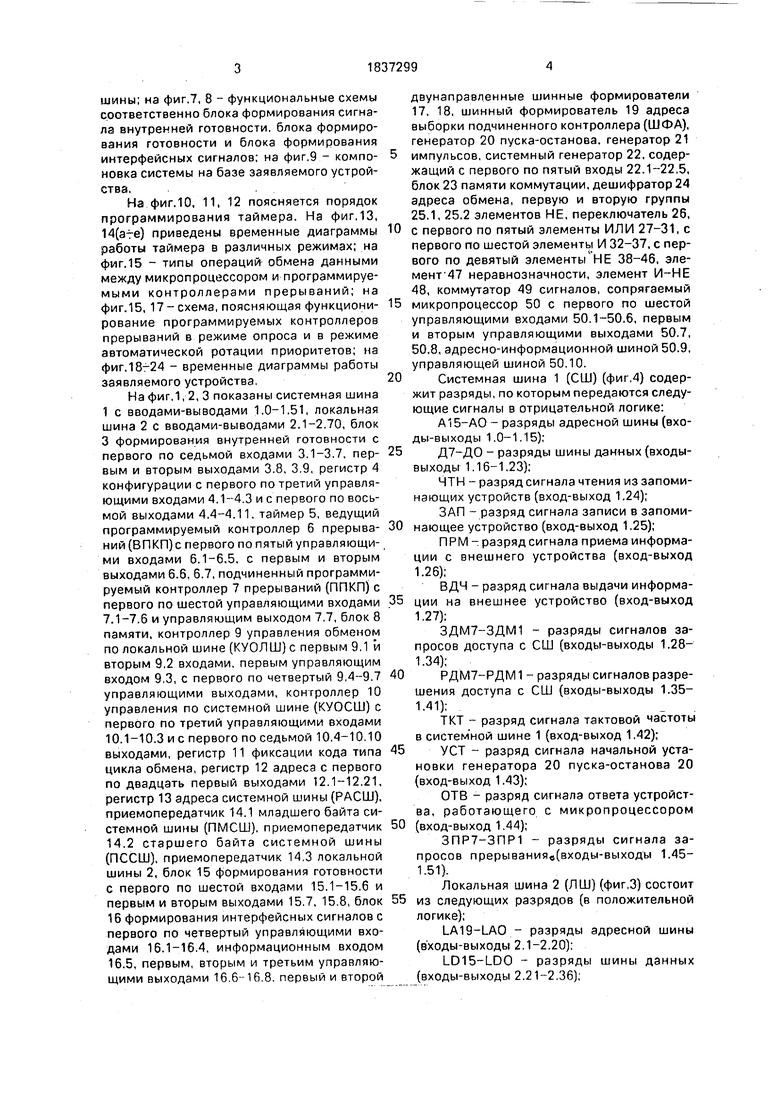

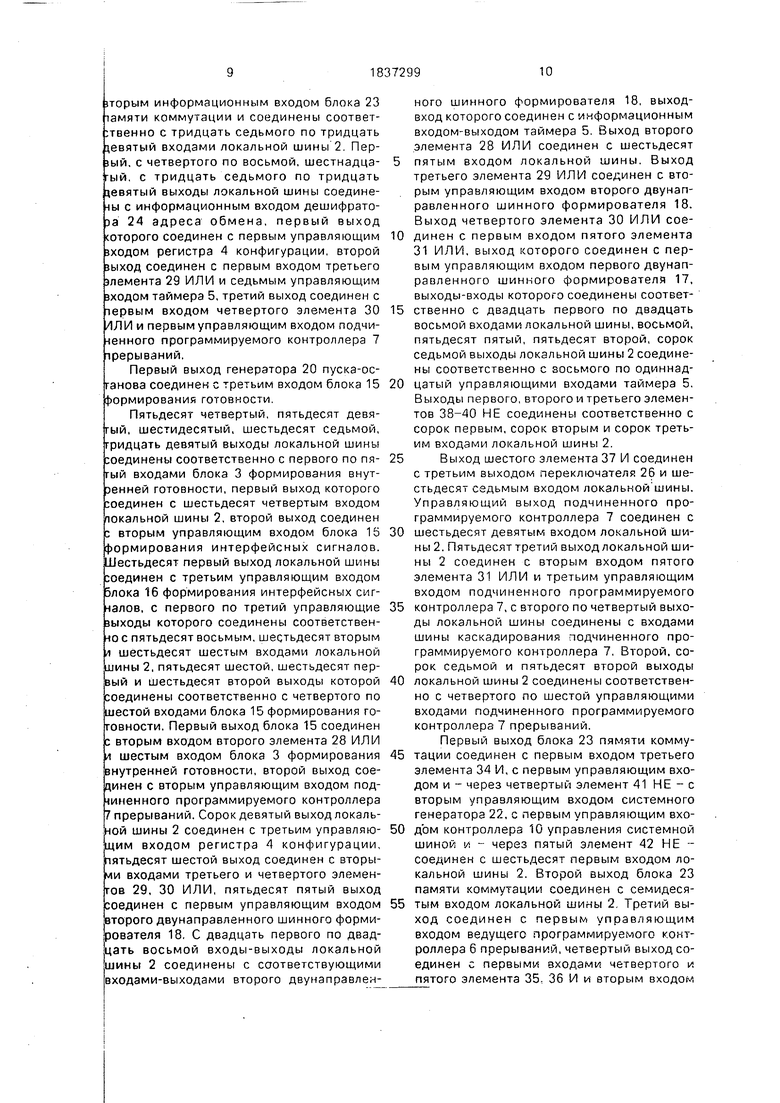

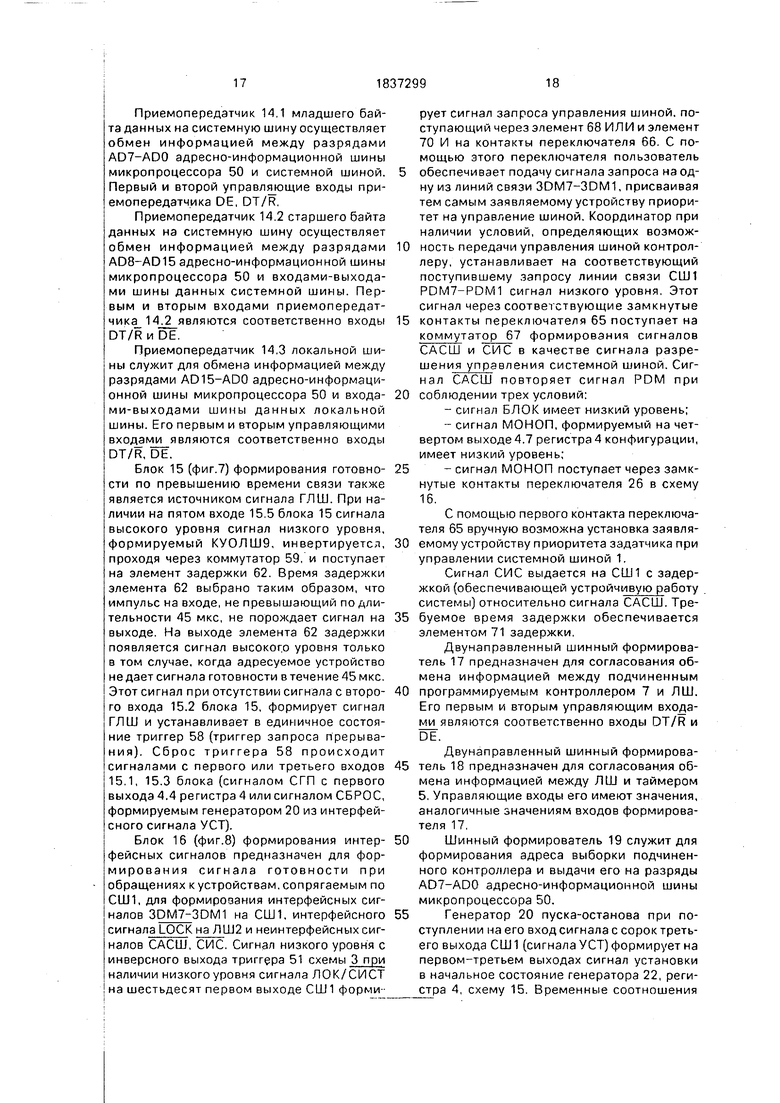

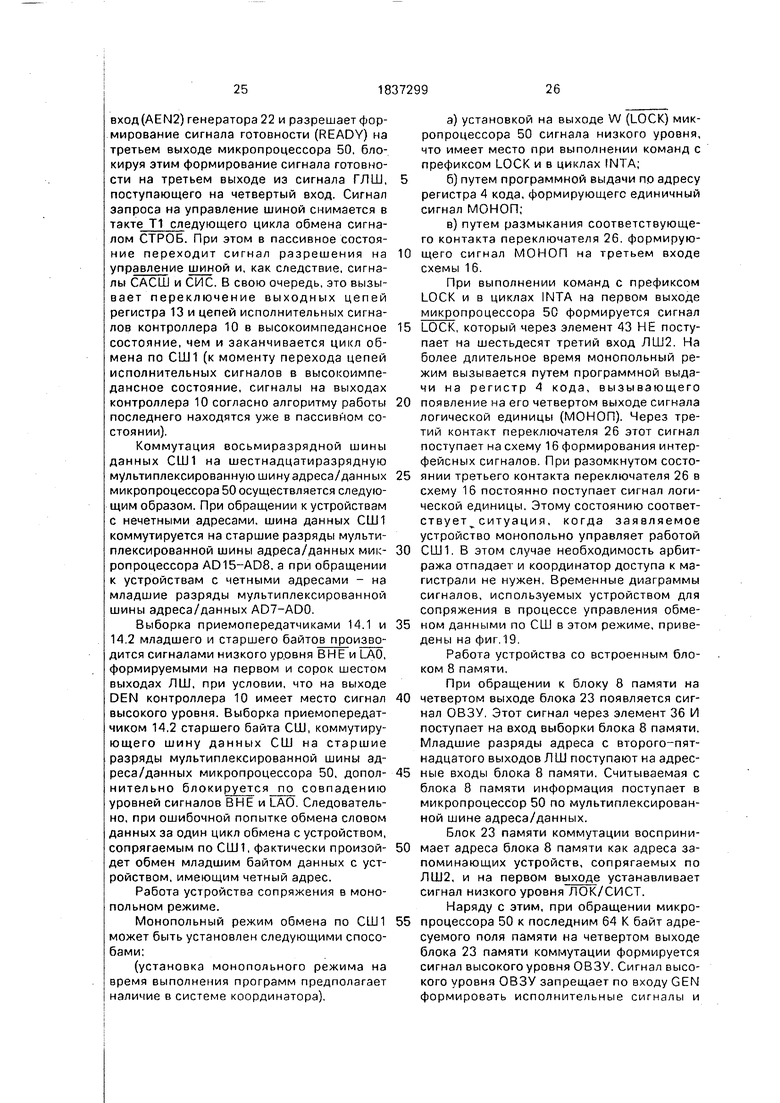

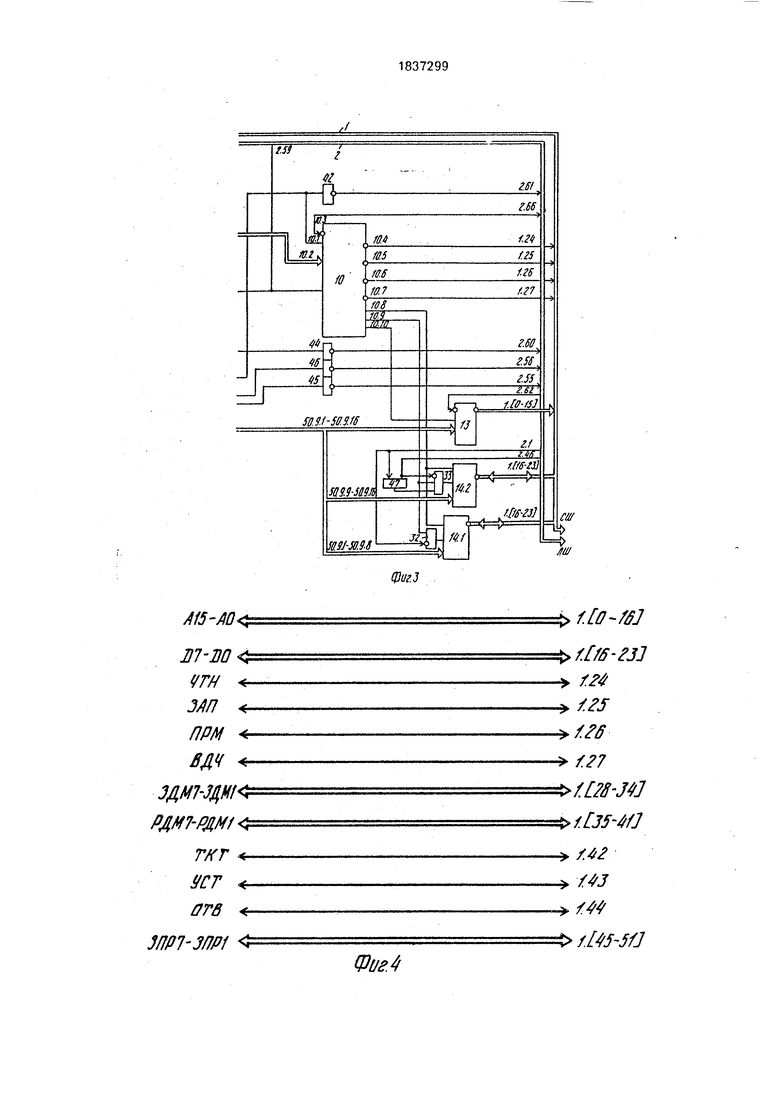

Системная шина 1 (СШ) (фиг,4) содержит разряды, по которым передаются следующие сигналы в отрицательной логике:

А15-АО - разряды адресной шины (входы-выходы 1.0-1.15);

Д7-ДО - разряды шины дакных (входы- выходы 1.16-1.23);

ЧТН - разряд сигнала чтения из запоминающих устройств (вход-выход 1.24);

ЗАП - разряд сигнала записи в запоминающее устройство (вход-выход 1.25);

ПРМ - разряд сигнала приема информации с внешнего устройства (вход-выход 1.26);

ВДЧ - разряд сигнала выдачи информации на внешнее устройство (вход-выход 1,27);

ЗДМ7-ЗДМ1 - разряды сигналов запросов доступа с СШ (входы-выходы 1.28- 1.34);

РДМ7-РДМ1 - разряды сигналов разрешения доступа с СШ (входы-выходы 1.35- 1.41);

ТКТ - разряд сигнала тактовой частоты в системной шине 1 (вход-выход 1.42);

УСТ - разряд сигнала начальной установки генератора 20 пуска-останова 20 (вход-выход 1.43);

ОТВ - разряд сигнала ответа устройства, работающего с микропроцессором (вход-выход 1.44);

ЗПР7-ЗПР1 - разряды сигнала запросов прерыванияв(входы-выходы 1.45- 1.51).

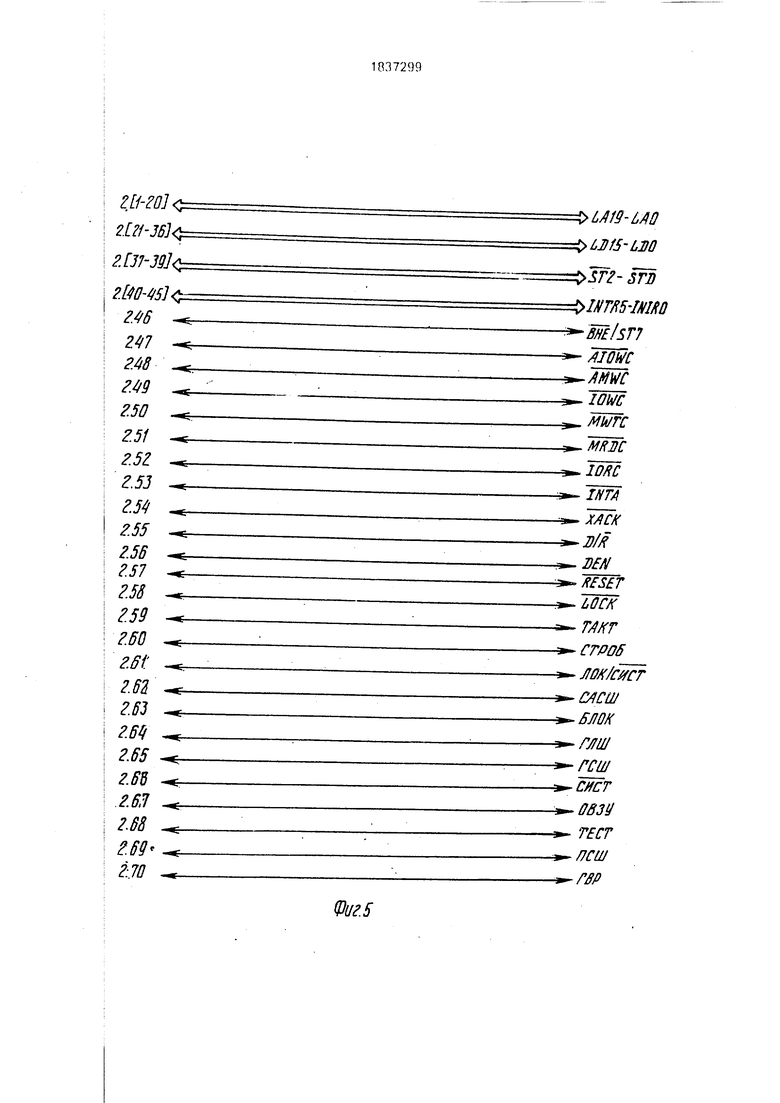

Локальная шина 2 (ЛШ) (фиг.З) состоит из следующих разрядов (в положительной логике);

LA19-LAO - разряды адресной шины (входы-выходы 2.1-2.20);

LD15-LDO - разряды шины данных (входы-выходы 2.21-2.36);

ST2-STO - разряды сигналов определения типа цикла обмена (входы-выходы 2.37- 2.39);

INTR5-INTRO - разряды входов запросов прерывания (входы-выходы 2.40-2.45);

BHE/ST7 (вход-выход 2.46) - разряд сигнала разрешения передачи по старшей половине канала данных 15-D8/ (сигнал состояния

AIOWC - разряд опережающего сигнала записи в устройство ввода-вывода 2,47);

AWC - разряд опережающего сигнала записи в память (вход-выход 2.48);

IOWC- разряд сигнала записи в устройство ввода-вывода (вход-выход 2.49);

MWTC - разряд сигнала записи в память (вход-выход 2,50);

MKDC - разряд сигнала считывания из памяти (вход-выход 2.51);

IOKC - разряд сигнала считывания из ус- тэойства ввода-вывода (вход-выход 2.52);

INTA - разряд сигнала разрешения пре- рывания (вход-выход 2.53):

ХАСК - разряд сигнала готовности к об- ь ену устройства, адресуемого по локальной шине (вход-выход 2.54);

DT/R - разряд сигнала управления работой шинных формирователей (вход-выход 2.55);

DEN - разряд сигнала перевода в высс- кримпендансное состояние выходных ключей и приемопередатчиков (вход-выход 2.56);

RESET - разряд синала установки начального состояния микропроцессора 50 (иход-выход 2.57);

LOCK - разряд сигнала блокировки готовности ЛШ к обмену (вход-выход 2.58); а также неинтерфейсные сигналы:

ТАКТ - тактовая частота микропроцессора 50 (вход-выход 2.59);

СТРОБ (СТРОБ) - сигнал фиксации адреса (вход-выход 2.60):

ЛОК/СИСТ, ЛОК/СИСТ - разряд сигнала цикла обмена по ЛШ/ по СШ (вход-выход 2.61);

САСШ - разряд сигнала выдачи адреса на СШ; (вход-выход 2.62);

БЛОК - разряд сигнала блокировки (пход-выход 2.63), порождающий формирование сигнала LOCK (ЛШ), во время выполнения микропроцессором команды с префиксом LOCK и в первом цикле INTA;

ГЛШ - разряд сигнала готовности устройства ЛШ (вход-выход 2.64), активный уровень сигнала разрешает завершение ииклов обмена данными между микропроцессором и внутренними регистрами устройства, блоком 8 памяти и устройствами

tip

пряжения по ЛШ;

ГСШ - разряд сигнала готовности устройств СШ (вход-выход 2.65); активный уровень сигнала разрешает завершение циклов обмена данными между микропроцессором

и устройствами, сопрягаемыми по СШ;

СИС - разряд строба выдачи исполнительного сигнала на системную шину (вход- выход 2.66). Активный уровень сигнала разрешает выдачу исполнительного сигнала

0 на соответствующую линию связи СШ;

ОБЗУ - разряд сигнала обращения к блоку 8 памяти (вход-выход 2.67). Активный уровень сигнала формируется при обращении микропроцессора к памяти с заданным

5 интервалом адресов и является сигналом выборки встроенного блока 8 памяти.

ТЕСТ - разряд сигнала готовности устройства, опрашиваемого командой WAIT микропроцессора 50 (вход-выход 2.68);

0ПСШ - разряд сигнала прерывания от

устройств СШ (вход-выход 2.69) (выходной сигнал подчиненного программируемого контроллера прерываний, обслуживающего запрос прерывания от устройств, сопрягае5 мых по СШ);

ГВР - разряд сигнала готовности внутренних регистров и блока 8 памяти (вход-выход 2.70) (сигнал имеет активный уровень при обращении микропроцессора к внут0 ренним регистрам устройства, блоку 8 памяти и в циклах INTA, используется для формирования сигнала ГЛШ).

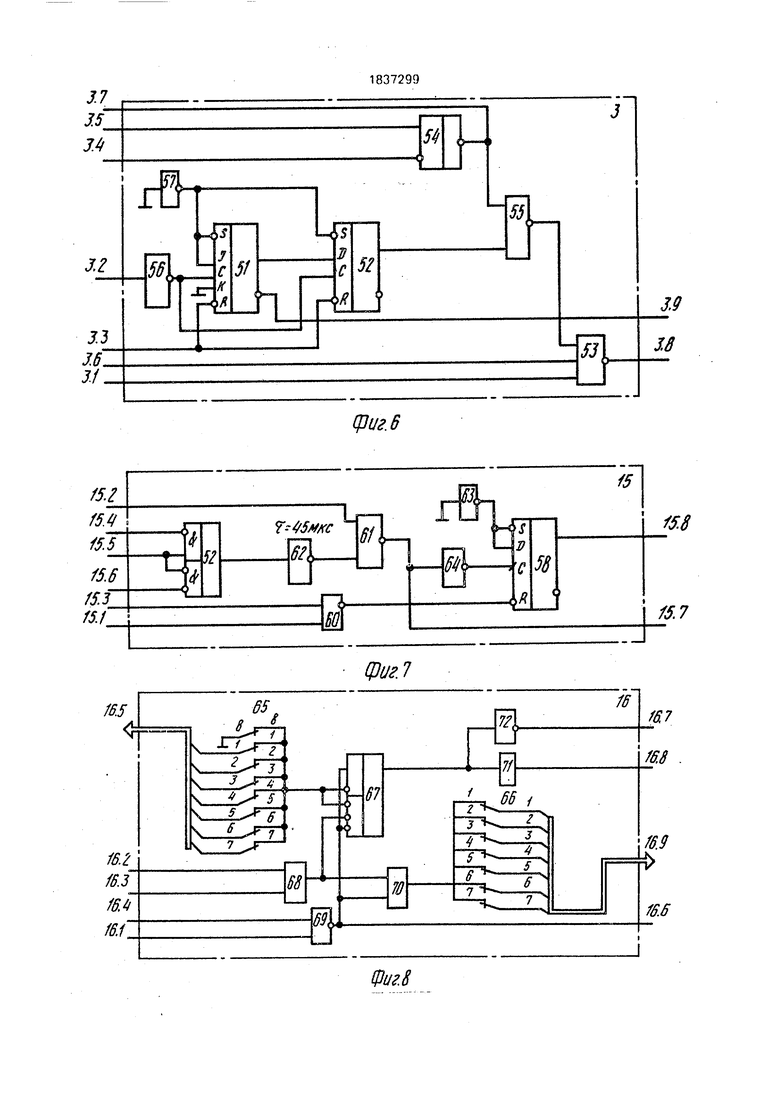

Блок 3 формирования внутренней готовности (фиг.6) содержит первый и второй

5 триггеры 51, 52, первый-третий элементы И-НЕ 53-55, элементы НЕ 56, 57.

Блок 15 формирования готовности (фиг.7) содержит триггер 58, коммутатор 59, элементы 60, 61 И Л И-НЕ, элемент 62 задер0 жки, элементы 63, 64 НЕ.

Блок 16 формирования интерфейсных сигналов (фиг.8) содержит переключатели 65, 66, коммутатор 67, элемент ИЛИ 68, элемент 69 ИЛИ-НЕ, элемент И 70, элемент 71

5 задержки, элемент НЕ 72.

Выходы регистра 13 адреса системной шины (см. фиг. 1, 2, 3 соединены соответственно с нулевого по пятнадцатый входами системной шины. Выход первого элемента

0 32 И соединен с первым управляющим входом приемопередатчика 14.1 младшего байта системной шины, информационный выход-вход которого соединен соответственно с шестнадцатого по двадцать третий

5 входами системной шины. С первого по четвертый выходы контроллера 10 управления обменом по системной шине соединены соответственно с двадцать четвертого по двадцать седьмой входами системной шины. Пятый выход контроллера 10 управления обменом по системной шине соединен с вторым управляющим входом приемопередатчика 14.1 младшего байта системной шины и с первым управляющим входом приемопередатчика 14.2 старшего байта системной шины, выход-вход которого соединен с шестнадцатого по двадцать третий входами системной шины. Шестой выход контроллера Юуправления обменом по системной шине соединен с первыми входами первого и второго элементов 32, 33 И. Выход второго элемента 33 И соединен с вторым управляющим входом приемопередатчика 14.2 старшего байта системной шины, седьмой выход контроллера 10 управления обменом по системной шине соединен с входом синхронизации регистра 13 адреса системной шины. С сорок первого попятьдесятпервый

выходы системной шины через элементы НЕ первой группы 25.1 элементов НЕ соединены соответственно с первого по седьмой информационными входами подчиненного программируемого контроллера 7 прерываний, информационный выход- вход которого соединен с информационным входом-выходом первого двунаправленного шинного формирователя 17. С двадцать первого по двадцать восьмой выходы системной шины соединены с информационными входами регистра 4 конфигурации. Первый выход регистра 4 конфигурации соединен с первым входом блока 15 формирования готовности, второй выход соединен с управляющим входом коммутатора 49 сигнала, третий и четвертый выходы соединены с первым и вторым входами переключателя 26, пятый выход соединен с входом шестого элемента 37 И, с шестого по восьмой выходы соединены соответственно с первого по третий входами таймера 5. С первого по третий выходы таймера 5 соединены соответственно с входами первого, второго и третьего элементов 38--40 НЕ, первый выход таймера 5 соединен с четвертым входом таймера 5 и первым информационным входом коммутатора 49 сигналов. Второй выход таймера 5 соединен с вторым информационным входом коммутатора 49 сигналов, выход которого соединен с пятым входом таймера 5. Третий вход переключателя соединен с шиной нулевого потенциала, первый выход генератора 21 импульсов через четвертый вход переключателя 26 соединен с сорок вторым входом системной шины, второй выход генератора 21 импульсов соединен с шестым входом таймера 5. Первый выход переключателя 26 соединен с вторым входом блока 15 формирования готовности, второй выход соединен с первым

управляющим входом блока 16 формирования интерфейсных сигналов, информационные выходы которого соединены соответственно с двадцать восьмого по тридцать четвертый входами системной шины. С тридцать пятого по сорок первый выходы системной шины соединены с информационными входами блока 16 формирования интерфейсных сигналов. Сорок третий вы0 ход системной шины соединен с входом генератора 20 пуска-останова. Сорок четвертый выход системной шины соединен с первым входом первого элемента 27 ИЛИ, выход которого соединен с первым входом

5 второго элемента 28 ИЛИ, с первого по двадцатый и двадцать первый выходы регистра 12 адреса соединены соответственное первого по двадцатый и сорок шестым входами локальной шины, а первый, четвертый,

0 восьмой, с пятнадцатого по двадцатый выходы соединены с соответствующими входами первого информационного входа блока 23 памяти коммутации. С двадцать первого по тридцать шестой входы-выходы

5 локальной шины 2 соединены с соответствующими входами-выходами информационного входа-выхода приемопередатчика 14.3. С первого по двадцать первый выходы-входы устройства для соединения с адресно0 информационной шиной микропроцессора 50 соединены с информационными входами регистра 12 адреса. С первого по восьмой выходы адресно-информационной шины соединены с информационным входом-выхо5 дом ведущего контроллера 6 прерываний, с соответствующими выходами шинного формирователя 19 адреса выборки подчиненного контроллера 7, с информационными входами приемопередатчика 14.1 младшего

0 байта системной шины, с первого по шестнадцатый входы-выходы устройства для подключения адресно-информационной шины микропроцессора 50 соединены с соответствующими выходами-входами при5 емопередатчика 14.3 локальной шины, выходами блока 8 памяти, с девятого по шестнадцатый выходы соединены с соответствующими входами информационного входа регистра 13 адреса системной шины

0 и информационного входа-выхода приемопередатчика 14.2 старшего байта системной шины. С первого по третий выходы устройства для подключения управляющего выхода микропроцессора 50 соединены с

5 соответствующими входами управляющего входа контроллера 9 управления обменом по локальной шине,контроллера 10 управления обменом по системной шине 1 и информационного входа регистра 11 фиксации кода типа обмена, выходы которого соединены с

)торым информационным входом блока 23 тамяти коммутации и соединены соответ- :твенно с тридцать седьмого по тридцать девятый входами локальной шины 2. Пер- зый, с четвертого по восьмой, шестнадцатый, с тридцать седьмого по тридцать девятый выходы локальной шины соединены с информационным входом дешифрато- эа 24 адреса обмена, первый выход соторого соединен с первым управляющим зходом регистра 4 конфигурации, второй зыход соединен с первым входом третьего элемента 29 ИЛИ и седьмым управляющим зходом таймера 5, третий выход соединен с первым входом четвертого элемента 30 /1ЛИ и первым управляющим входом подчиненного программируемого контроллера 7 прерываний.

Первый выход генератора 20 пуска-ос- ганова соединен с третьим входом блока 15 формирования готовности.

Пятьдесят четвертый, пятьдесят девятый, шестидесятый, шестьдесят седьмой, тридцать девятый выходы локальной шины соединены соответственно с первого по пятый входами блока 3 формирования внутренней готовности, первый выход которого соединен с шестьдесят четвертым входом покальной шины 2, второй выход соединен с вторым управляющим входом блока 15 формирования интерфейсных сигналов. Шестьдесят первый выход локальной шины соединен с третьим управляющим входом элока 16 формирования интерфейсных сигналов, с первого по третий управляющие зыходы которого соединены соответственно с пятьдесят восьмым, шестьдесят вторым л шестьдесят шестым входами локальной пины 2, пятьдесят шестой, шестьдесят первый и шестьдесят второй выходы которой соединены соответственно с четвертого по шестой входами блока 15 формирования готовности. Первый выход блока 15 соединен с вторым входом второго элемента 28 ИЛИ и шестым входом блока 3 формирования внутренней готовности, второй выход соединен с вторым управляющим входом подчиненного программируемого контроллера 7 прерываний. Сорок девятый выход локальной шины 2 соединен с третьим управляющим входом регистра 4 конфигурации, пятьдесят шестой выход соединен с вторыми входами третьего и четвертого элементов 29, 30 ИЛИ, пятьдесят пятый выход соединен с первым управляющим входом второго двунаправленного шинного форми- Ователя 18. С двадцать первого по двад- ать восьмой входы-выходы локальной ины 2 соединены с соответствующими входами-выходами второго двунаправленного шинного формирователя 18, выход- вход которого соединен с информационным входом-выходом таймера 5. Выход второго элемента 28 ИЛИ соединен с шестьдесят

пятым входом локальной шины. Выход третьего элемента 29 ИЛИ соединен с вторым управляющим входом второго двунаправленного шинного формирователя 18. Выход четвертого элемента 30 ИЛИ сое0 динен с первым входом пятого элемента 31 ИЛИ, выход которого соединен с первым управляющим входом первого двунаправленного шинного формирователя 17, выходы-входы которого соединены соответ5 ственно с двадцать первого по двадцать восьмой входами локальной шины, восьмой, пятьдесят пятый, пятьдесят второй, сорок седьмой выходы локальной шины 2 соединены соответственно с восьмого по одиннад0 цатый управляющими входами таймера 5, Выходы первого, второго и третьего элементов 38-40 НЕ соединены соответственно с сорок первым, сорок вторым и сорок третьим входами локальной шины 2.

5Выход шестого элемента 37 И соединен

с третьим выходом переключателя 26 и шестьдесят седьмым входом локальной шины. Управляющий выход подчиненного программируемого контроллера 7 соединен с

0 шестьдесят девятым входом локальной шины 2. Пятьдесят третий выход локальной шины 2 соединен с вторым входом пятого элемента 31 ИЛИ и третьим управляющим входом подчиненного программируемого

5 контроллера 7, с второго по четвертый выходы локальной шины соединены с входами шины каскадирования подчиненного программируемого контроллера 7, Второй, сорок седьмой и пятьдесят второй выходы

0 локальной шины 2 соединены соответственно с четвертого по шестой управляющими входами подчиненного программируемого контроллера 7 прерываний.

Первый выход блока 23 пямяти комму5 тации соединен с первым входом третьего элемента 34 И, с первым управляющим входом и - через четвертый элемент 41 НЕ - с вторым управляющим входом системного генератора 22, с первым управляющим вхо0 дом контроллера 10 управления системной шиной и - через пятый элемент 42 НЕ - соединен с шестьдесят первым входом локальной шины 2. Второй выход блока 23 памяти коммутации соединен с семидеся5 тым входом локальной шины 2, Третий выход соединен с первым управляющим входом ведущего программируемого контроллера 6 прерываний, четвертый выход соединен с первыми входами четвертого и пятого элемента 35, 36 И и вторым входом

третьего элемента 34 И, с шестьдесят седьмым входом локальной шины. Пятьдесят седьмой, шестьдесят четвертый и шестьдесят пятый выходы локальной шины 2 соединены соответственно с третьим, четвертым и пятым управляющими входами системного генератора 22, первый, второй и третий выходы которого соединены с первым, вторым и третьим управляющими входами микропроцессора 50. Первый выход системного генератора 22 соединен с пятьдесят девятым входом локальной шины. Сороковой и шестьдесят восьмой выходы локальной шины соединены с четвертым и пятым управляющими входами микропроцессора 50. Первый управляющий выход микропроцессора 50 соединен через шестой элемент 43 НЕ с шестьдесят третьим входом локальной шины, второй управляющий выход соединен с вторым входом пятого элемента 36 И, шестой управляющий вход соединен с первым управляющим выходом ведущего программируемого контроллера 6 прерываний.

С второго по четырнадцатый выходы системной шины 1 соединены с соответствующими входами адресного входа блока 8 памяти.

-Выход третьего элемента 34 И соединен с первым входом контроллера 9 управления обменом по локальной шине. Шина нулевого потенциала соединена с вторым входом контроллера 9. С первого по седьмой информационные выходы контроллера 9 соединены соответственно с 47-53 входами, локальной шины. Первый, управляющий вход контроллера 9 соединен с вторым входом контроллера 10 обмена по системной шине и пятьдесят девятым входом локальной шины 2, первый управляющий выход соединен с входами синхронизации регистра 11 фиксации кода типа цикла обмена, регистра 12 адреса и входом седьмого элемента 44 НЕ, а второй управляющий выход - с первым управляющим входом приемопередатчика 14.3 локальной шины и входом восьмого элемента 45 НЕ. третий управляющий выход соединен с вторым входом четвертого элемента 35 И и входом девятого элемента 46 НЕ, четвертый управляющий выход соединен с первым входом элемента 48 И-НЕ. С сорок первого по сорок пятый выходы локальной шины соединены через вторую группу элементов 25.2 НЕ с первого по третий, пятым и шестым входами информационного входа ведущего контроллера 6 прерываний. Шестьдесят девятый выход локальной шины соединен с четвертым входом информационного входа ведущего контроллера 6 прерываний. Второй, пятьдесят второй, сорок седьмой и пятьдесят третий выходы локальной шины соединены соответственно с второго по пятый управляющими входами ведущего программируемо5 го контроллера 6 прерываний, входы-выходы шины каскадирования которого соединены С входами информационного входа шинного формирователя 19 адреса выборки подчиненного контроллера, а второй управ0 ляющий выход соединен с третьим входом, четвертого элемента 35 И, выход которого соединен с вторым управляющим входом приемопередатчика 14.3 локальной шины, шестьдесят третий выход локальной шины

5 соединен с вторым входом элемента 48 И- НЕ, выход которого соединен с управляющим входом шинного формирователя 19 адреса выборки подчиненного контроллера. Выход пятого элемента 36 И соединен с

0 управляющим входом блока 8 памяти. Выходы с седьмого по девятый элементов 44, 45, 46 НЕ соединены соответственно с шестидесятым, пятьдесят пятым и пятьдесят шее-, тым входами локальной шины. Шестьдесят

5 второй выход локальной шины соединен с управляющим входом регистра 13 адреса системной шины. Первый выход локальной шины соединен с первым входом первого элемента 32 И и первым входом элемента

0 неравнозначности 47. Сорок шестой выход локальной шины соединен с вторым входом элемента неравнозначности и вторым входом второго элемента 33 И. Выход элемента 47 соединен с третьим входом второго

5 элемента 33 И, семидесятый выход локальной шины соединен с седьмым входом блока 3 формирования внутренней готовности. Шестьдесят третий выход локальной шины соединен с четвертым управляющим вхо0 дом блока 16 формирования интерфейсных сигналов. Второй выход генератора 20 пуска-останова соединен с вторым управляющим входом регистра 4 конфигурации, третий выход соединен с пятьдесят седь5 мым входом локальной шины 2. Шестьдесят шестой выход локальной шикы соединен с третьим управляющим входом контроллера 10 управления обменом по системной шине 1.

0

Блок 3 формирования внутренней готовности (фиг.6) для формирования на первом выходе 3.8 сигнала готовности устройств локальной шины (ГЛ Ш), Активный

5 уровень этого сигнала разрешает завершение циклов обмена данными между микропроцессором 50, внутренними регистрами устройства, блоком 8 памяти (сопрягаемыми по ЛШ), подключаемыми по Л Ш устройствами, а также окончание циклов INTA.

j В начале каждого цикла обмена по сигналу СТРОБ, поступающему на третий вход 0.3 блока 3, триггеры 51, 52 устанавливаются в ноль. По переднему фронту сигнала на зтором входе блока 3 (сигналу ТАКТ) в такте Г2 триггер 51 устанавливается в единичное :остояние. Сигнал с выхода триггера 51 по ;тупает на D-вход триггера 52. Триггер 52 устанавливается в единичное состояние за- цним фронтом сигнала ТАКТ в начале такта 3.

При наличии сигнала высокого уровня ГВР) на входе 3.7 элемента 53 И-НЕ сигнал , выхода триггера 52 через элемент 55 И-Н Е 1 элемент 53 И-НЕ поступит на шестьдесят етвертый вход ЛШ, формируя тем самым игнал ГЛШ. Если обрещение к блоку 8 па- ляти заблокировано, то формирование сиг- шла ГВР на седьмом входе 3.7 схемы 3 в 1иклах обращения к памяти не происходит i сигнал ГЛШ не формируется.

Формирование блоком 3 сигнала ГЛШ |ри обращении к блоку 8 памяти, портам вода-вывода и в циклах INTA в начале такта 3 цикла обмена гарантирует выполнение перечисленных циклов обмена на пять таков синхросигнала ТАКТ (один так TW).

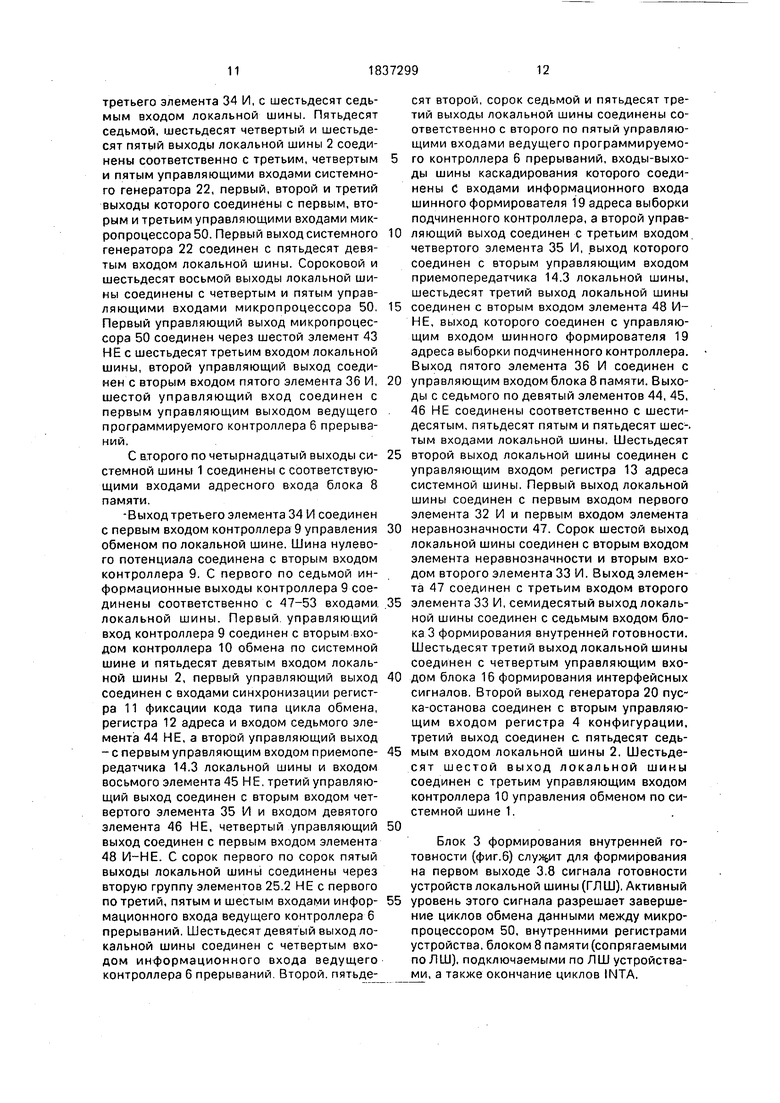

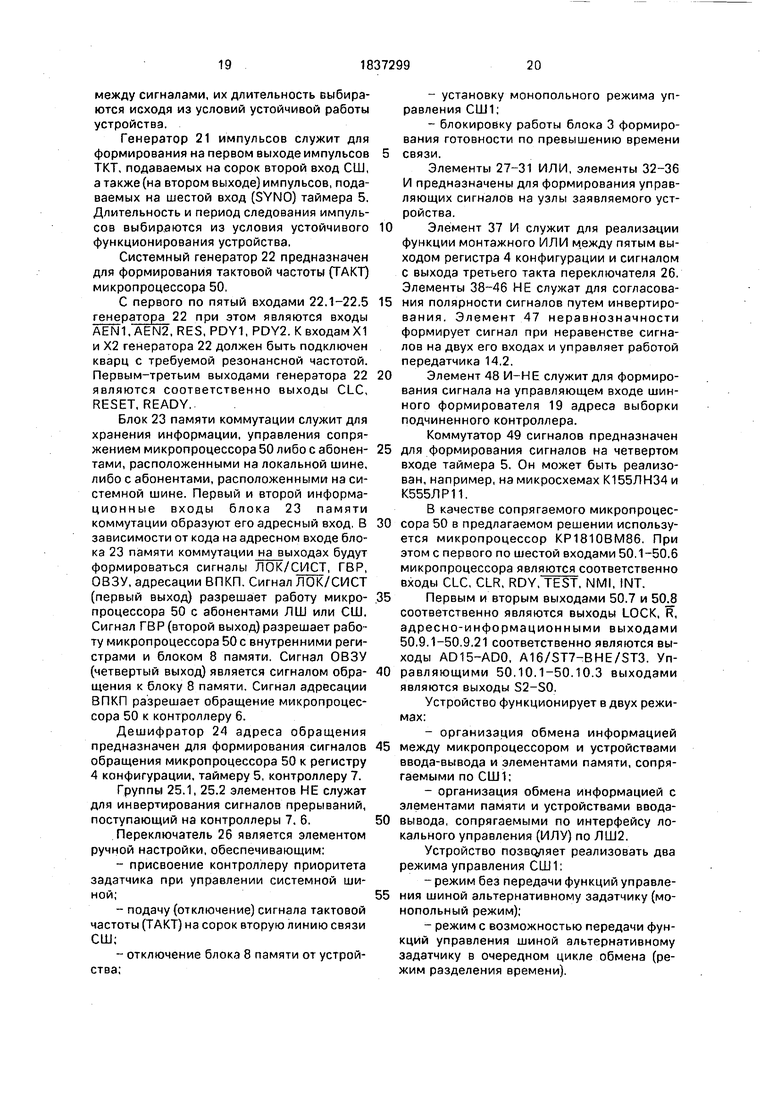

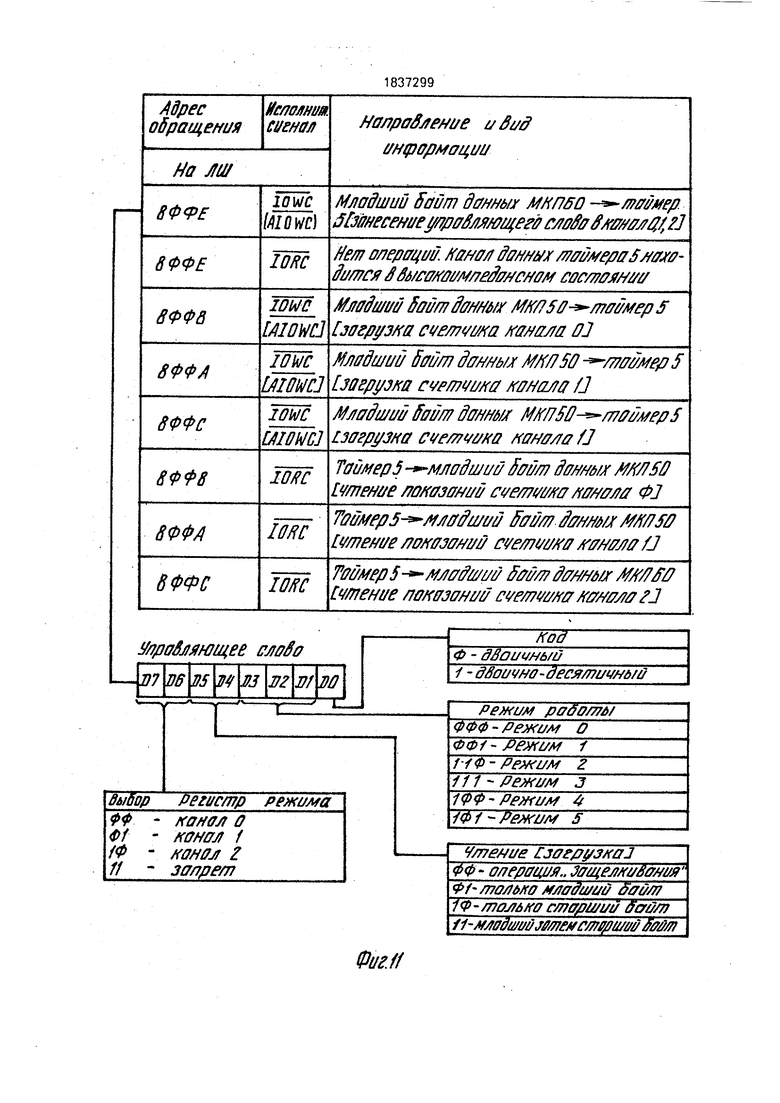

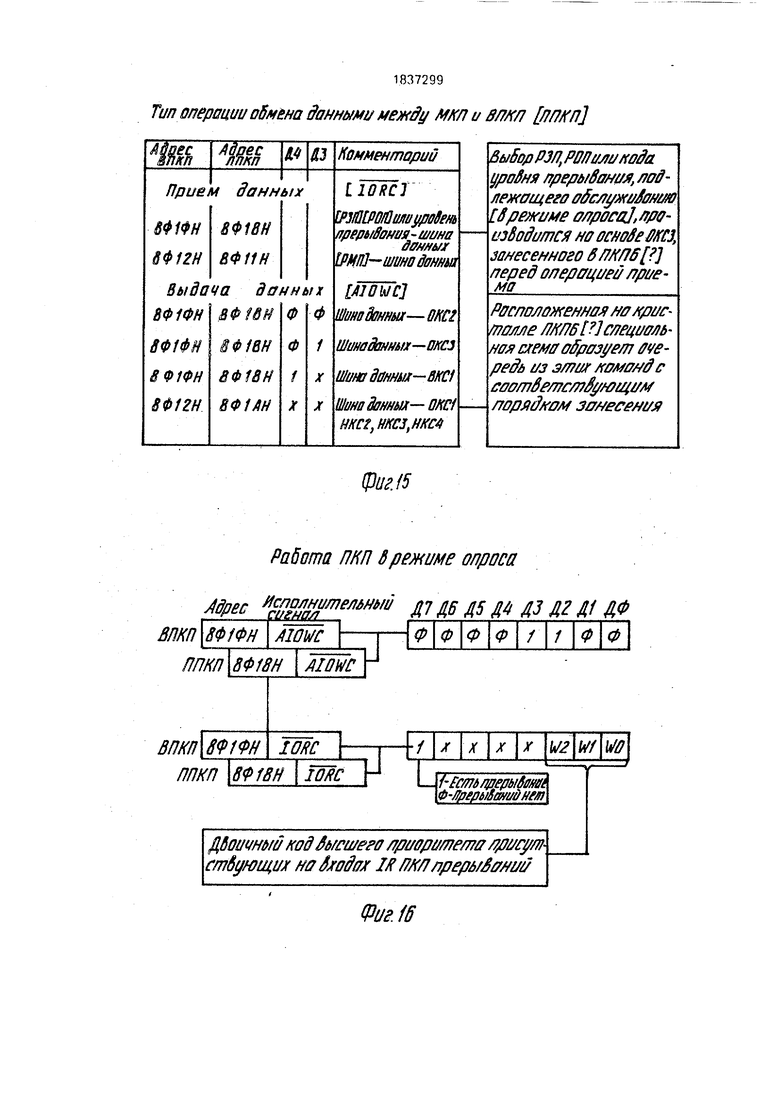

Временные диаграммы формирования отовности на третьем входе (входе READY) микропроцессора 50 в рассмотренных слу- чаях приведены на фиг.15а. i Регистр 4 конфигурации предназначен для программного управления таймером 5, ( ыбором режима синхронизации таймера 5, сброса триггера 58 прерывания по превы- иению времени связи схемы 3, включения и Елокировки схемы 15 готовности по превы- иению времени связи, временной установки и сброса монопольного режима при f аботе устройства по СШ с альтернативным аадатчиком, блокировки и подключения Елокав памяти. Последние три функции дублируются элементами ручной регулировки (: помощью переключателя 26). Регистр 4 доступен для записи как устройство вывода с адресом 8 Н. Обмен данными с регистром осуществляется по восьми младшим разрядам данных микропроцессора 50. F егистр 4 может быть реализован на регистрах К589ИР12. Формат байта данных при обмене данными регистра 4 с микропроцес- с эром 50 приведен на фиг.8. При включении питания регистр 4 автоматически обнуляетС1.

| С первого по третий управляющие входы 4.1-4.3 регистра 4 являются соот- вэтственно входами CS1, R, CS2, информационные входы являются D-входами, На пэрвом-восьмом выходах 4.4-4.11 регистра 4 формируются следующие сигналы:

СТП - сброс триггера прерывания;

КАСК - каскадное включение счетчиков в таймере 5;

БГПВС - блокировка формирования готовности по превышению времени связи;

МОНОП - монопольное использование микропроцессором 50 системной шины 1;

БВЗУ - блокировка работы блока 8 памяти;

УПРО-УПР2 - сигналы управления работой таймера 5.

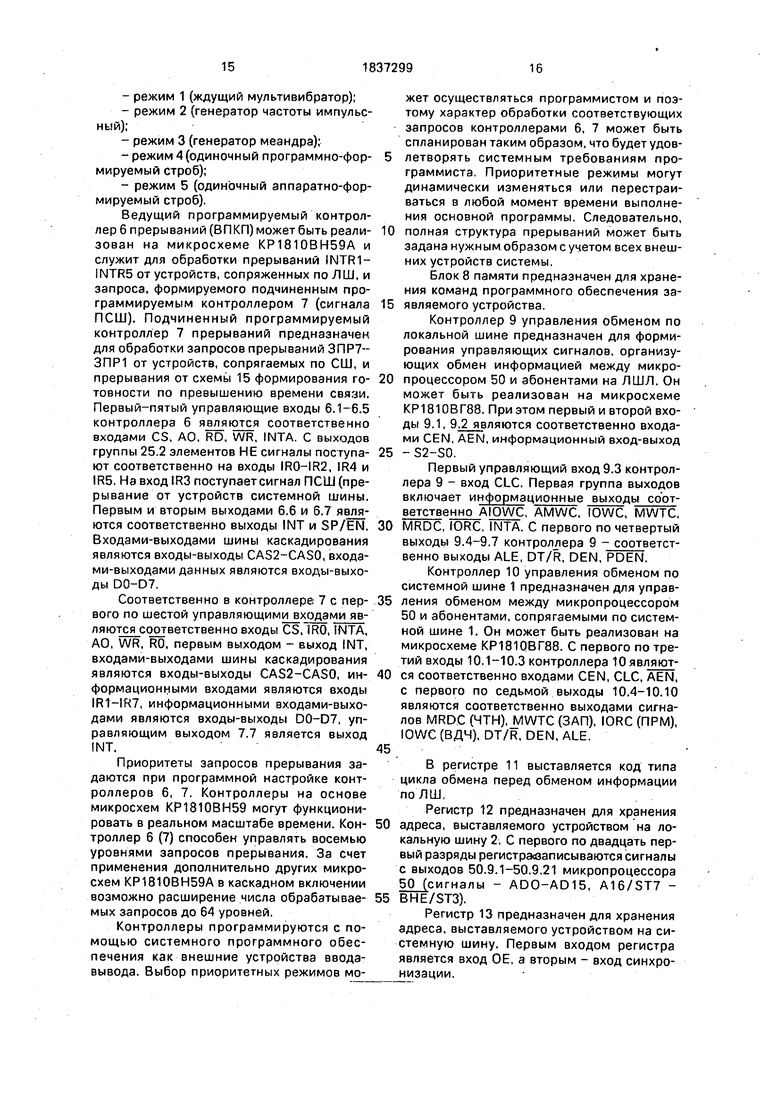

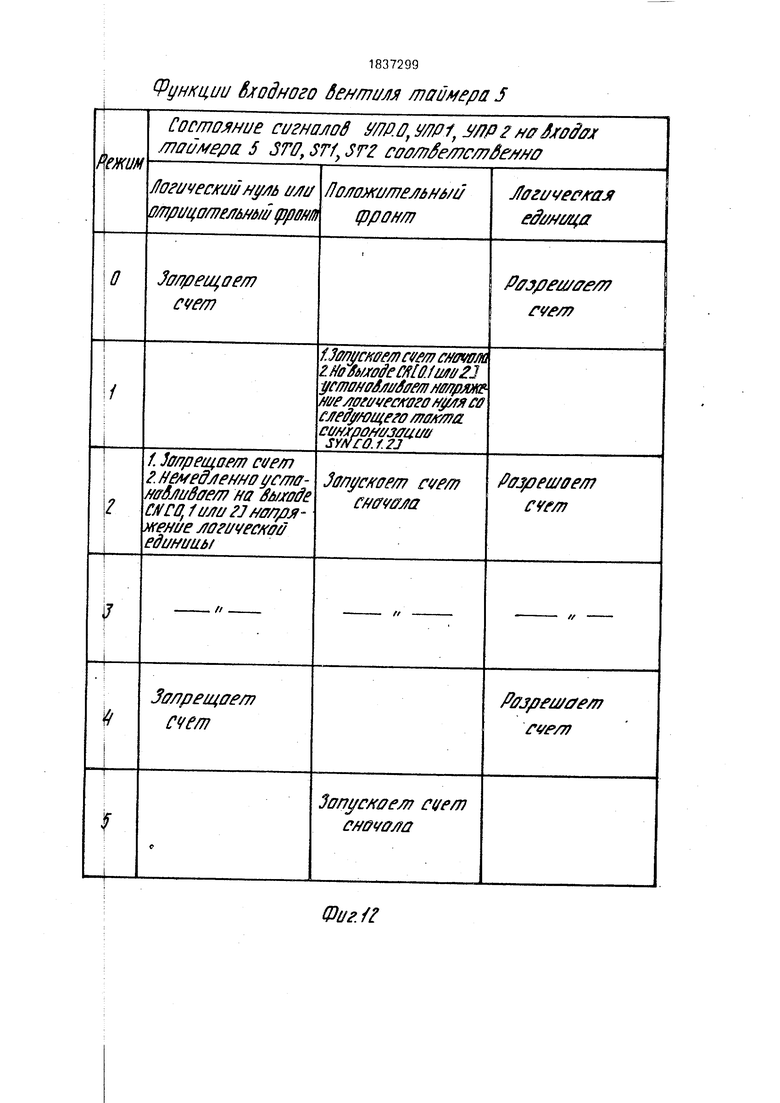

Таймер 5 обеспечивает независимый отсчет временных интервалов параллельно выполнению арифметической и логической обработки информации микропроцессором 50. В качестве таймера может быть использована микросхема КР580ВИ53, управление работой таймера 5, а также выбор режима синхронизации (параллельная работа второго и третьего каналов или их каскадное включение) осуществляется с выходов 4.9-4.11 регистра 4 конфигурации.

С первого по третий управляющие входы таймера 5 - соответственно входы STO- ST2, с четвертого по шестой управляющие входы - соответственно входы SYN1, SYN2, SYNO, с седьмого по одиннадцатый входы - соответственно входы CS, RO, WR. АО, А1. С первого по третий управляющие выходы таймера соответствуют выходам CRO-CR2 микросхемы.

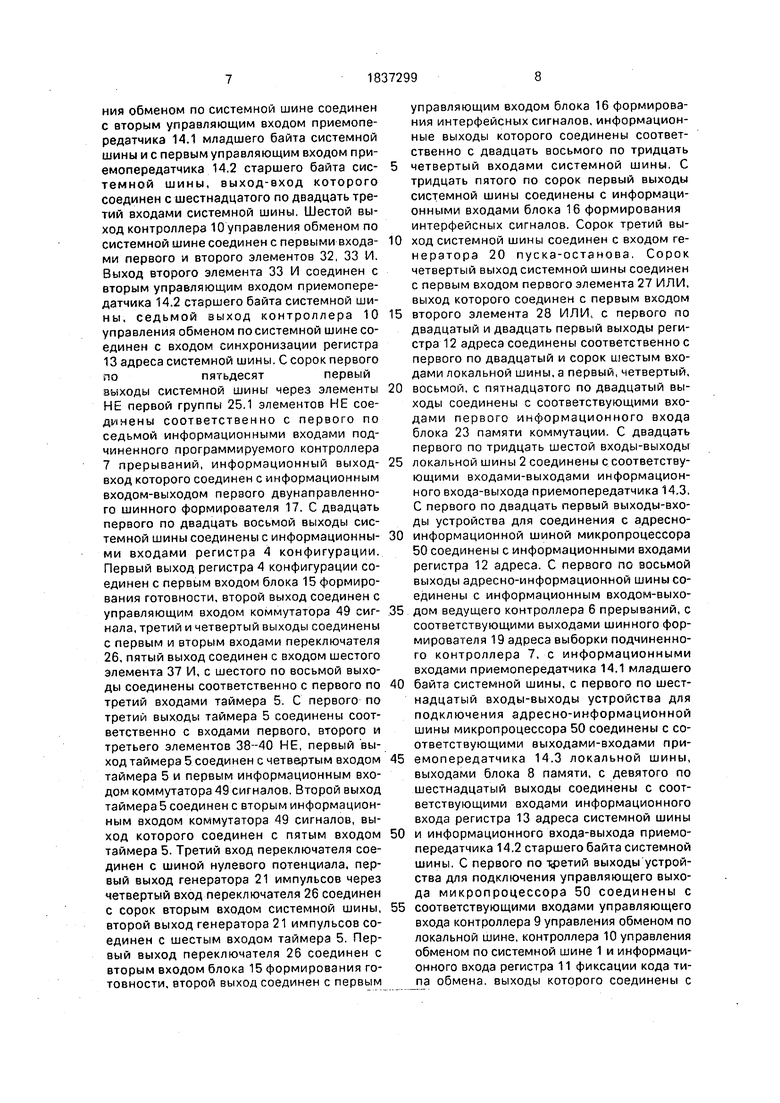

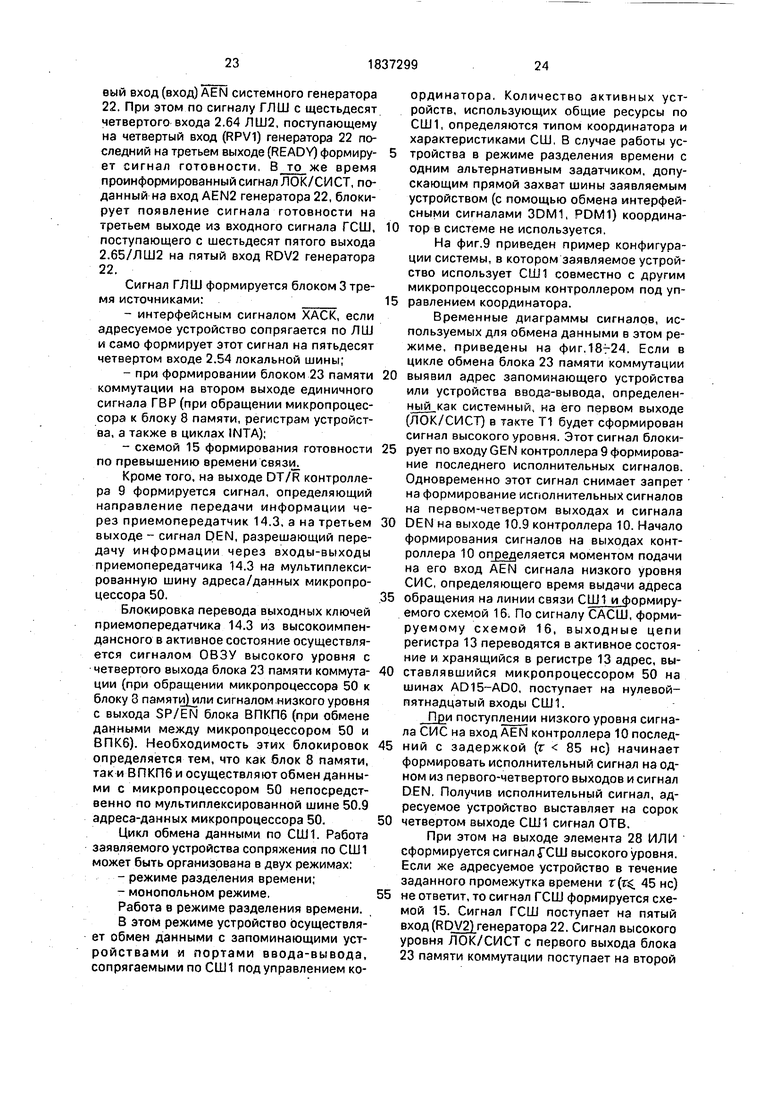

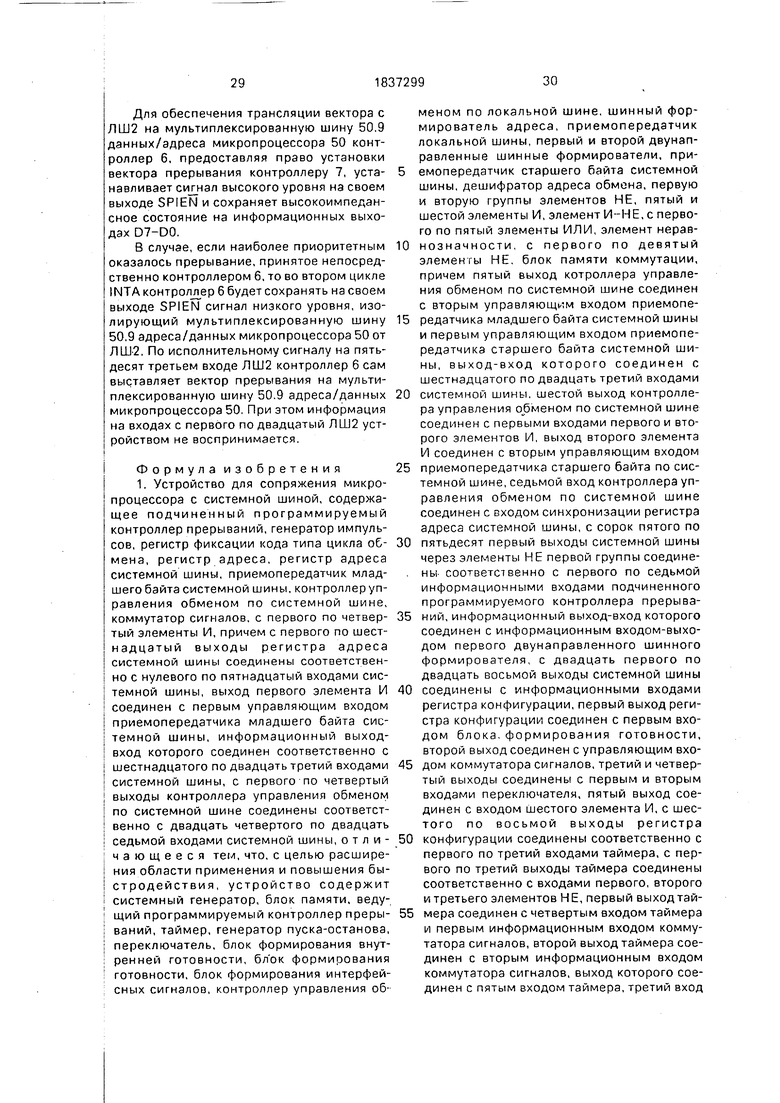

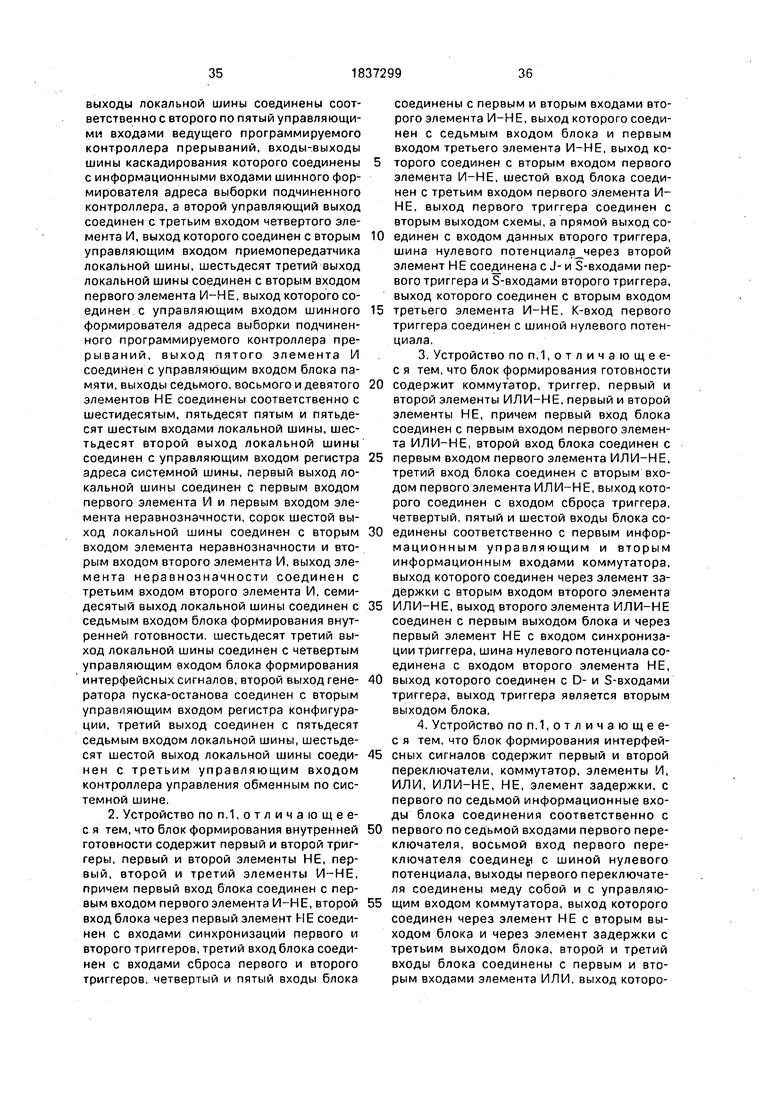

На фиг.11, 12, 13 приведен формат управляющего слова таймера 5, порядок его программирования и временные диаграммы, работы во всех режимах работы. По выходным сигналам счетчиков каналов таймера формируются запросы прерывания на соответствующих линиях связи ЛШ. При параллельной работе второго и третьего каналов тактовая частота подается на их входы с выхода первого канала. При каскадном включении тактовая частота подается на вход второго счетчика с выхода первого, а на вход третьего счетчика - с выхода второго.

Режим работы каналов таймера 5 программируется с помощью простых операций ввода-вывода (фиг. 11). Каждый из трех каналов таймера программируется отдельно путем записи в регистр режима управляющего слова и запрограммированного количества байтов. Режим работы каждого канала таймера 5 определяется содержимым регистра режима. После записи управляющего слова в регистр режима выбранного канала он переводится в один из шести режимов работы:

- режим 0 (прерывание терминального счета);

-режим 1 (ждущий мультивибратор);

-режим 2 (генератор частоты импульсный);

-режим 3 (генератор меандра);

-режим 4(одиночный программно-фор- мируемый строб);

-режим 5 (одиночный аппаратно-фор- мируемый строб).

Ведущий программируемый контроллер 6 прерываний (ВПКП) может быть реали- зован на микросхеме КР1810ВН59А и служит для обработки прерываний INTR1- INTR5 от устройств, сопряженных по ЛШ, и запроса, формируемого подчиненным программируемым контроллером 7 (сигнала ПСШ). Подчиненный программируемый контроллер 7 прерываний предназначен для обработки запросов прерываний ЗПР7-- ЗПР1 от устройств, сопрягаемых по СШ, и прерывания от схемы 15 формирования го- товности по превышению времени связи. Первый-пятый управляющие входы 6.1-6.5 контроллера 6 являются соответственно входами CS, АО, RD, WR, INTA. С выходов группы 25.2 элементов НЕ сигналы поступа- ют соответственно на входы IRQ-IR2, IR4 и IR5. На вход IR3 поступает сигнал ПСШ (прерывание от устройств системной шины. Первым и вторым выходами 6.6 и 6.7 явля- ются соответственно выходы INT и SP/EN. Входами-выходами шины каскадирования являются входы-выходы CAS2-CASO, входами-выходами данных являются входы-выходы DO-D7.

Соответственно в контроллере 7 с пер- вого по шестой управляющими входами являются соответственно входы CS, IRQ, INTA, АО, WR, RO, первым выходом - выход INT, входами-выходами шины каскадирования являются входы-выходы CAS2-CASO, ин- формационными входами являются входы IR1-IR7, информационными входами-выходами являются входы-выходы DO-D7, управляющим выходом 7.7 является выход INT.

Приоритеты запросов прерывания задаются при программной настройке контроллеров 6, 7. Контроллеры на основе микросхем КР1810ВН59 могут функционировать в реальном масштабе времени. Кон- троллер 6 (7) способен управлять восемью уровнями запросов прерывания. За счет применения дополнительно других микросхем КР1810ВН59А в каскадном включении возможно расширение числа обрабатывав- мых запросов до 64 уровней.

Контроллеры программируются с помощью системного программного обеспечения как внешние устройства ввода- вывода. Выбор приоритетных режимов может осуществляться программистом и поэтому характер обработки соответствующих запросов контроллерами 6, 7 может быть спланирован таким образом, что будет удовлетворять системным требованиям программиста. Приоритетные режимы могут динамически изменяться или перестраиваться в любой момент времени выполнения основной программы. Следовательно, полная структура прерываний может быть задана нужным образом с учетом всех внешних устройств системы.

Блок 8 памяти предназначен для хранения команд программного обеспечения заявляемого устройства.

Контроллер 9 управления обменом по локальной шине предназначен для формирования управляющих сигналов, организующих обмен информацией между микропроцессором 50 и абонентами на ЛШЛ. Он может быть реализован на микросхеме КР1810ВГ88. При этом первый и второй входы 9.1, 9.2 являются соответственно входами CEN, AEN, информационный вход-выход - S2-SO.

Первый управляющий вход 9.3 контроллера 9 - вход CLC. Первая группа выходов включает информационные выходы соответственно AIOWC. AMWC, IOWC, MWTC, MRDC, IORC, INTA. С первого по четвертый выходы 9.4-9.7 контроллера 9 соответственно выходы ALE, DT/R, DEN, PDEN.

Контроллер 10 управления обменом по системной шине 1 предназначен для управления обменом между микропроцессором 50 и абонентами, сопрягаемыми по системной шине 1. Он может быть реализован на микросхеме КР1810ВГ88. С первого по третий входы 10.1-10.3 контроллера 10 являются соответственно входами CEN, CLC, AEN, с первого по седьмой выходы 10.4-10.10 являются соответственно выходами сигналов MRD.C (ЧТН),JMWTC (ЗАП), IORC (ПРМ), IOWC (ВДЧ), DT/R, DEN, ALE.

В регистре 11 выставляется код типа цикла обмена перед обменом информации поЛШ,

Регистр 12 предназначен для хранения адреса, выставляемого устройством на локальную шину 2. С первого по двадцать первый разряды регистраваписываются сигналы с выходов 50.9.1-50,9.21 микропроцессора 50 (сигналы - ADO-AD15, A16/ST7 - BHE/ST3).

Регистр 13 предназначен для хранения адреса, выставляемого устройством на системную шину. Первым входом регистра является вход ОЕ, а вторым - вход синхронизации.

Приемопередатчик 14.1 младшего байта данных на системную шину осуществляет обмен информацией между разрядами AD7-ADO адресно-информационной шины микропроцессора 50 и системной шиной. Первый и второй управляющие входы приемопередатчика DE, DT/R.

Приемопередатчик 14.2 старшего байта данных на системную шину осуществляет обмен информацией между разрядами AD8-AD15 адресно-информационной шины микропроцессора 50 и входами-выходами шины данных системной шины. Первым и вторым входами приемопередатчику 14. я ются соответственно входы DT/R и DE.

Приемопередатчик 14.3 локальной шины служит для обмена информацией между разрядами AD15-ADO адресно-информационной шины микропроцессора 50 и входа- ми-выходами шины данных локальной шины. Его первым и вторым управляющими входами являются соответственно входы DT/R, ШЁ.

Блок 15 (фиг.7) формирования готовно- сти по превышению времени связи также является источником сигнала ГЛШ. При наличии на пятом входе 15.5 блока 15 сигнала высокого уровня сигнал низкого уровня, формируемый КУОЛШ9, инвертируется, проходя через коммутатор 59, и поступает на элемент задержки 62. Время задержки элемента 62 выбрано таким образом, что импульс на входе, не превышающий по длительности 45 мкс, не порождает сигнал на выходе. На выходе элемента 62 задержки появляется сигнал высокого уровня только в том случае, когда адресуемое устройство не дает сигнал а готовности в течение 45 мкс. Этот сигнал при отсутствии сигнала с второ- го входа 15.2 блока 15, формирует сигнал ГЛШ и устанавливает в единичное состояние триггер 58 (триггер запроса прерывания). Сброс триггера 58 происходит сигналами с первого или третьего входов 15.1, 15.3 блока (сигналом СГП с первого выхода 4.4 регистра 4 или сигналом СБРОС, формируемым генератором 20 из интерфейсного сигнала УСТ).

Блок 16 (фиг.8) формирования интер- фейсных сигналов предназначен для формирования сигнала готовности при обращениях к устройствам, сопрягаемым по СШ1, для формирования интерфейсных сигналов 3DM7-3DM1 на СШ1, интерфейсного сигнала LOCK на ЛШ2 и неинтерфейсных сигналов САСШ, СПС. Сигнал низкого уровня с инверсного выхода триггера 51 схемы 3 при наличии низкого уровня сигнала ЛОК/СИСТ на шестьдесят первом выходе СШ1 формирует сигнал запроса управления шиной, поступающий через элемент 68 ИЛИ и элемент 70 И на контакты переключателя 66. С помощью этого переключателя пользователь обеспечивает подачу сигнала запроса на одну из линий связи 3DM7-3DM1, присваивая тем самым заявляемому устройству приоритет на управление шиной. Координатор при наличии условий, определяющих возможность передачи управления шиной контроллеру, устанавливает на соответствующий поступившему запросу линии связи СШ1 PDM7-PDM1 сигнал низкого уровня. Этот сигнал через соответствующие замкнутые контакты переключателя 65 поступает на коммутатор 67 формирования сигналов САСШ и СИС в качестве сигнала разре- шения управления системной шиной. Сигнал САСШ повторяет сигнал PDM при соблюдении трех условий:

-сигнал БЛОК имеет низкий уровень;

-сигнал МОНОП, формируемый на четвертом выходе 4.7 регистра 4 конфигурации, имеет низкий уровень;

-сигнал МОНОП поступает через замкнутые контакты переключателя 26 в схему 16.

С помощью первого контакта переключателя 65 вручную возможна установка заявляемому устройству приоритета задатчика при управлении системной шиной 1.

Сигнал СИС выдается на СШ1 с задержкой (обеспечивающей устройчивую работу системы) относительно сигнала САСШ. Требуемое время задержки обеспечивается элементом 71 задержки.

Двунаправленный шинный формирователь 17 предназначен для согласования обмена информацией между подчиненным программируемым контроллером 7 и ЛШ. Его первым и вторым управляющим входа- ми являются соответственно входы DT/R и Dl.

Двунаправленный шинный формирователь 18 предназначен для согласования обмена информацией между ЛШ и таймером 5. Управляющие входы его имеют значения, аналогичные значениям входов формирователя 17.

Шинный формирователь 19 служит для формирования адреса выборки подчиненного контроллера и выдачи его на разряды AD7-ADO адресно-информационной шины микропроцессора 50.

Генератор 20 пуска-останова при поступлении на его вход сигнала с сорок третьего выхода СШ 1 (сигнала УСТ) формирует на первом-третьем выходах сигнал установки в начальное состояние генератора 22, регистра 4, схему 15. Временные соотношения

между сигналами, их длительность выбираются исходя из условий устойчивой работы устройства.

Генератор 21 импульсов служит для формирования на первом выходе импульсов ТКТ, подаваемых на сорок второй вход СШ, а также (на втором выходе) импульсов, подаваемых на шестой вход (SYNO) таймера 5, Длительность и период следования импульсов выбираются из условия устойчивого функционирования устройства,

Системный генератор 22 предназначен для формирования тактовой частоты (ТАКТ) микропроцессора 50.

С первого по пятый входами 22.1-22.5 генератора 22 при этом являются входы AEN1, AEN2, RES, PDY1, PDY2. К входам Х1 и Х2 генератора 22 должен быть подключен кварц с требуемой резонансной частотой. Первым-третьим выходами генератора 22 являются соответственно выходы CLC, RESET, READY.

Блок 23 памяти коммутации служит для хранения информации, управления сопряжением микропроцессора 50 либо с абонентами, расположенными на локальной шине, либо с абонентами, расположенными на системной шине. Первый и второй информа- ционные входы блока 23 памяти коммутации образуют его адресный вход. В зависимости от кода на адресном входе блока 23 памяти коммутации на выходах будут формироваться сигналы ЛОК/СИСТ, ГВР, ОВЗУ, адресации ВПКП. Сигнал ЛОК/СИСТ (первый выход) разрешает работу микропроцессора 50 с абонентами ЛШ или СШ, Сигнал ГВР (второй выход) разрешает работу микропроцессора 50 с внутренними регистрами и блоком 8 памяти. Сигнал ОВЗУ (четвертый выход) является сигналом обращения к блоку 8 памяти. Сигнал адресации ВПКП разрешает обращение микропроцессора 50 к контроллеру 6.

Дешифратор 24 адреса обращения предназначен для формирования сигналов обращения микропроцессора 50 к регистру 4 конфигурации, таймеру 5, контроллеру 7.

Группы 25.1, 25.2 элементов НЕ служат для инвертирования сигналов прерываний, поступающий на контроллеры 7. 6.

Переключатель 26 является элементом ручной настройки, обеспечивающим:

-присвоение контроллеру приоритета задатчика при управлении системной шиной;

-подачу (отключение) сигнала тактовой частоты (ТАКТ) на сорок вторую линию связи СШ;

-отключение блока 8 памяти от устройства;

-установку монопольного режима управления СШ1;

-блокировку работы блока 3 формирования готовности по превышению времени

5 связи.

Элементы 27-31 ИЛИ, элементы 32-36 И предназначены для формирования управляющих сигналов на узлы заявляемого устройства.

0 Элемент 37 И служит для реализации функции монтажного ИЛИ между пятым выходом регистра 4 конфигурации и сигналом с выхода третьего такта переключателя 26. Элементы 38-46 НЕ служат для согласова5 ния полярности сигналов путем инвертирования. Элемент 47 неравнозначности формирует сигнал при неравенстве сигналов на двух его входах и управляет работой передатчика 14.2.

0Элемент 48 И-НЕ служит для формирования сигнала на управляющем входе шинного формирователя 19 адреса выборки подчиненного контроллера.

Коммутатор 49 сигналов предназначен

5 для формирования сигналов на четвертом входе таймера 5, Он может быть реализован, например, на микросхемах К155ЛН34 и К555ЛР11.

В качестве сопрягаемого микропроцес0 сора 50 в предлагаемом решении используется микропроцессор КР1810ВМ86. При этом с первого по шестой входами 50.1-50.6 микропроцессора являются соответственно входы CLC, CLR, RDY, TEST, NMI. INT.

5 Первым и вторым выходами 50.7 и 50JS соответственно являются выходы LOCK, R, адресно-информационными выходами 50,9.1-50.9.21 соответственно являются выходы AD15-ADO, A16/ST7-BHE/ST3. Уп0 равляющими 50.10.1-50.10.3 выходами являются выходы S2-SO.

Устройство функционирует в двух режимах:

-организация обмена информацией 5 между микропроцессором и устройствами

ввода-вывода и элементами памяти, сопрягаемыми по СШ1;

-организация обмена информацией с элементами памяти и устройствами ввода0 вывода, сопрягаемыми по интерфейсу локального управления (ИЛУ) по ЛШ2.

Устройство позволяет реализовать два режима управления СШ1:

-режим без передачи функций управле- 5 ния шиной альтернативному задатчику (монопольный режим);

-режим с возможностью передачи функций управления шиной альтернативному задатчику в очередном цикле обмена (режим разделения времени).

Устройство сопряжения обеспечивает обслуживание инициативных сопрягаемых элементов по запросам прерывания.

Все функции по арифметической и логической обработке информации реализуются микропроцессором 50 в ходе выполнения программы и сопровождаются обменом информацией с запоминающими устройствами и устройствами ввода-вывода.

Чтение кодов команд программ из бло- ка 8 памяти и.обмен информацией в ВПКП производится непосредственно по интерфейсу, реализованному на выходах микропроцессора 50. Обмен информацией с элементами памяти и устройствами ввода- вывода, сопрягаемыми по ЛШ2 и СШ1, требует согласования интерфейса микропроцессора 50 с СШ1 и ЛШ2 соответственно и реализуется заявляемым устройст- вом.

Согласование интерфейсов заключает- ся путем:

-демультиплексирования адресов обращения, формируемых микропроцессором 50 на мультиплексированных шинах адреса/данных и адреса-слова состояния:

-коммутации доступа микропроцессора 50 к СШ1 и ЛШ2 в соответствии с адресом обращения;

-синхронизации цепей приема-передачи данных.

Синхронизация процессов в устройстве сопряжения осуществляется сигналами ТАКТ, формируемыми генератором 22 и поступающими на пятьдесят девятый вход 2.59ЛШ2.

В первом такте каждого цикла обмена микропроцессор 50 выставляет на управляющих выходах 50.10.1-50.10.3 слова состояния SO, S1, S2 код типа цикла обмена, отличный от кода 111. Одновременно с этим, микро- процессор 50 выставляет на мультиплексированных шинах 50.9 адрес/данные, адрес/слово состояния, адрес обращения и сигнал ВНЕ, являющийся признаком обращения к старшему байту данных.

Демультиплексирование адресов обращений.

Код с выходов 50.10 SO, S1, S2 микропроцессора 50 поступает на КУОЛШ9 и КУ- ОСШ 10. Если он отличается от кода 111, то он служит сигналом начала цикла обмена данными. По сигналу ТАКТ эта информация воспринимается КУОЛШ9 и КУОСШ10. В свою очередь контроллеры 9, 10 формируют короткий импульс на выходах ALE.

По заднему фронту этого импульса в регистры 12, 13 записывается адрес, а в регистр 11 - код типа цикла обмена. При этом в регистре 11 запишется код SO, S1, S2 в регистре 12 - код AD15-ADO. A19/ST6A16/ST3, BHE/ST7, в регистре 13 - код AD15-ADO.

Демультиплексированный адрес(LA19- LAO, ВНЕ) и слово состояния (ST2-STO) немедленно поступают на входы 1-20, 37-39, 46 ЛШ2. С выхода регистра 13 (РАСШ)адрес на СШ1 не поступает, так как выходы регистра 13 установлены в высокоимпендансное состояние высоким уровнем сигнала САСШ шестьдесят второго выхода ЛШ.

Сигналы адреса и кода типа цикла обмена с регистров 11,12 через Л Ш2 поступают на дешифратор 24 и блок 23 памяти коммутации. В заявляемом решении принимается следующее условие - при обращении к устройствам ввода-вывода дешифрируются разряды адреса LAO, LA7-LA3, LA15 при обращении к памяти - LA19-LA14.

Далее следует цикл обмена данными по ЛШ2 или СШ1.

Цикл обмена данными по ЛШ.

Если выставленный на регистре 11 адрес запоминающего устройства или устройства ввода-вывода попадает в область адресов, заранее определенных как локальные (в эту область входят адреса устройств, сопрягаемых по ЛШ2, адреса блока 8 памяти и регистров заявляемого устройства сопряжения, то на первом выходе блока 23 памяти коммутации появляется сигнал низкого уровня (ЛОК-СИСТ). Этот сигнал (если отсутствует сигнал на четвертом выходе блока 23 памяти коммутации) через элемент И 34 поступает на первый вход (CEN) контроллера 9 и разрешЈет ему в соответствии с кодом на входах S2-SO сформировать исполнительный сигнал на соответствующей линии ЛШ2. Одновременно сигнал низкого уровня ЛОК/СИСТ с первого выхода блока 23 коммутации запрещает контроллеру 10 сформировать соответствующий исполнительный сигнал на СШ1.

Сигнал ЛОК/СИСТ проходит через элемент НЕ 42 и инвертируется. Сигнал с выхода элемента НЕ 42 поступает через шестьдесят первый вход ЛШ2 на схему 16 и блокирует формирование сигналов запроса доступа к магистрали (3DM7-3DM1) на линиях связи СШ1, что приводит к блокировке сигналов (САСШ, СИС) на входах 2.62, 2.66 ЛШ2. Сигнал высокого уровня СИС запрещает блоку КУОСШ 10 формировать как исполнительные сигналы (на выходах 1-4), так и сигнал на выходе DEN. Выходы исполнительных сигналов при этом поддерживаются в высокоимпедансном состоянии. Низким уровнем сигнала на выходе поддерживаются в высокоимпедансном состоянии выходные ключи ПМСШ 14.1 и ПССШ 14.2. Сигнал ЛОК/СИСТ поступает также на первый вход (вход) AEN системного генератора 22. При этом по сигналу ГЛШ с шестьдесят четвертого входа 2.64 ЛШ2, поступающему на четвертый вход (RPV1) генератора 22 последний на третьем выходе (READY) формиру- ет сигнал готовности, В то же время проинформированный сигнал ЛОК/СИСТ, поданный на вход AEN2 генератора 22, блокирует появление сигнала готовности на третьем выходе из входного сигнала ГСШ, поступающего с шестьдесят пятого выхода 2.65/ЛШ2 на пятый вход RDV2 генератора 22.

Сигнал ГЛШ формируется блоком 3 тремя источниками:

-интерфейсным сигналом ХАСК, если адресуемое устройство сопрягается по ЛШ и само формирует этот сигнал на пятьдесят четвертом входе 2.54 локальной шины;

-при формировании блоком 23 памяти коммутации на втором выходе единичного сигнала ГВР (при обращении микропроцессора к блоку 8 памяти, регистрам устройства, а также в циклах INTA);

-схемой 15 формирования готовности по превышению времени связи,.

Кроме того, на выходе DT/R контроллера 9 формируется сигнал, определяющий направление передачи информации через приемопередатчик 14.3, а на третьем выходе - сигнал DEN, разрешающий передачу информации через входы-выходы приемопередатчика 14.3 на мультиплексированную шину адреса/данных микропроцессора 50.

Блокировка перевода выходных ключей приемопередатчика 14.3 из высокоимпен- дансного в активное состояние осуществляется сигналом ОВЗУ высокого уровня с четвертого выхода блока 23 памяти коммута- ции (при обращении микропроцессора 50 к блоку 3 памяти и1ли сигналом низкого уровня с выхода SP/EN блока ВПКП6 (при обмене данными между микропроцессором 50 и ВПК6). Необходимость этих блокировок определяется тем, что как блок 8 памяти, так и ВПКПби осуществляют обмен данными с микропроцессором 50 непосредственно по мультиплексированной шине 50.9 адреса-данных микропроцессора 50.

Цикл обмена данными по СШ1. Работа заявляемого устройства сопряжения по СШ1 может быть организована в двух режимах: - режиме разделения времени;

-монопольном режиме, Работа в режиме разделения времени.

В этом режиме устройство осуществляет обмен данными с запоминающими устройствами и портами ввода-вывода, сопрягаемыми по СШ1 под управлением координатора, Количество активных устройств, использующих общие ресурсы по СШ1, определяются типом координатора и характеристиками СШ, В случае работы устройства в режиме разделения времени с одним альтернативным задатчиком, допускающим прямой захват шины заявляемым устройством (с помощью обмена интерфейсными сигналами 3DM1, PDM1) координаторе системе не используется.

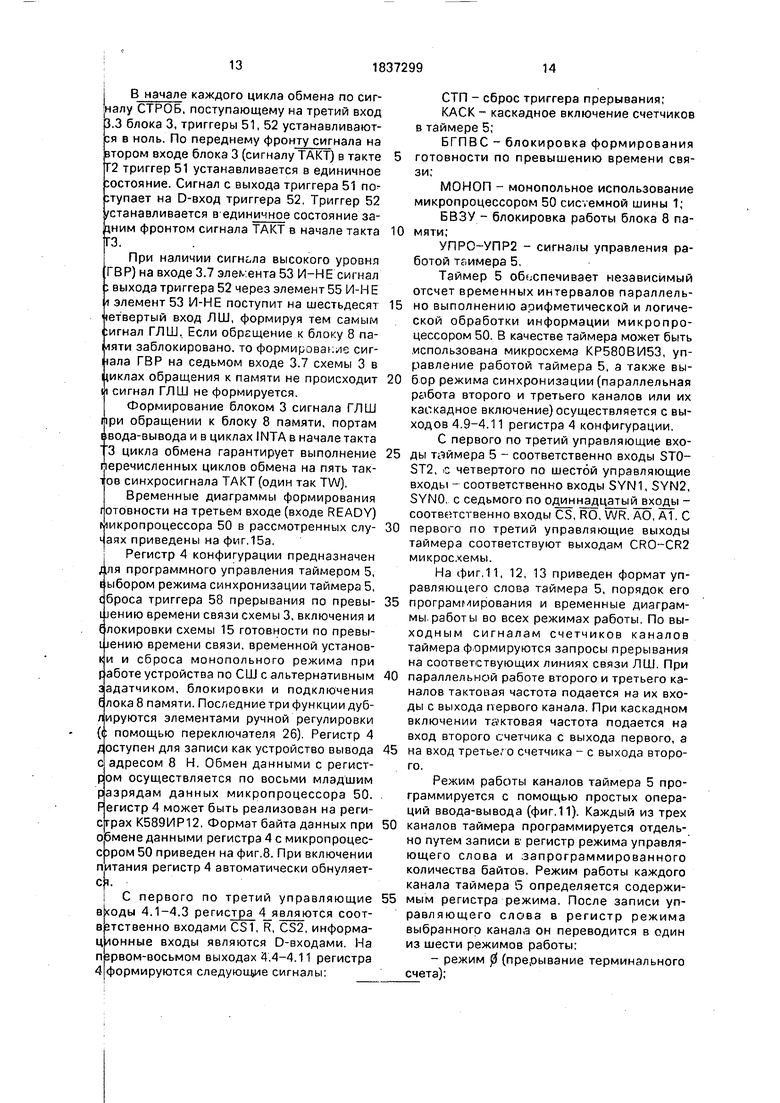

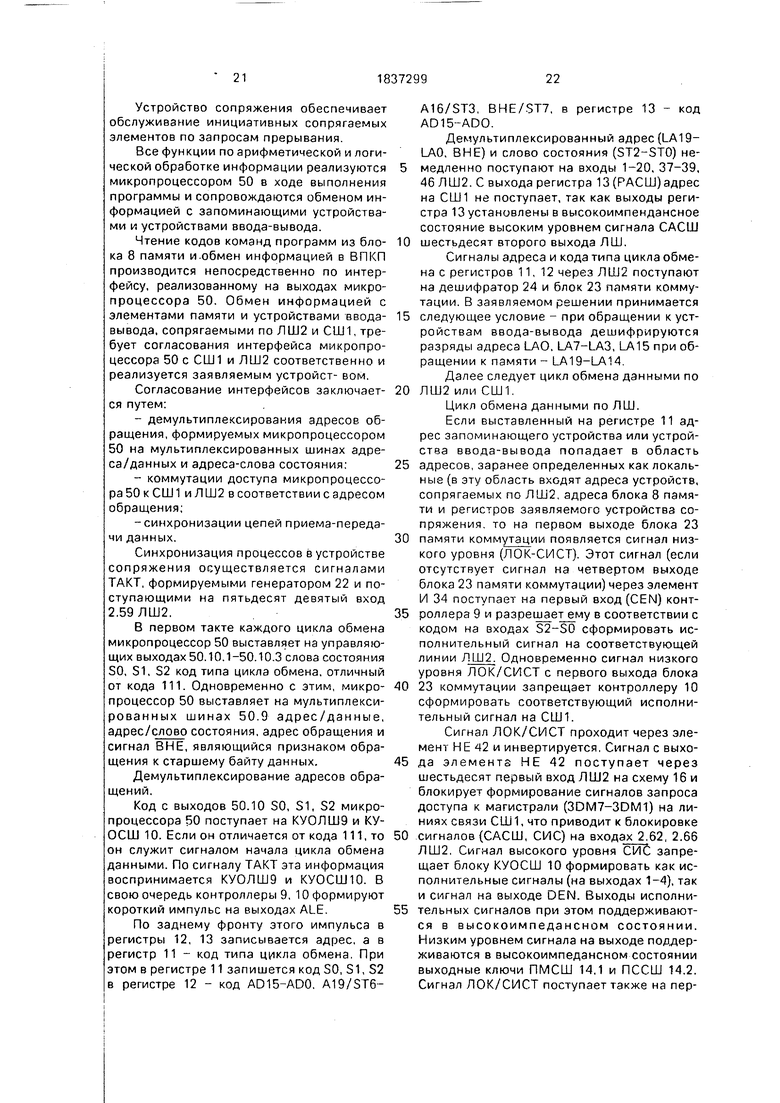

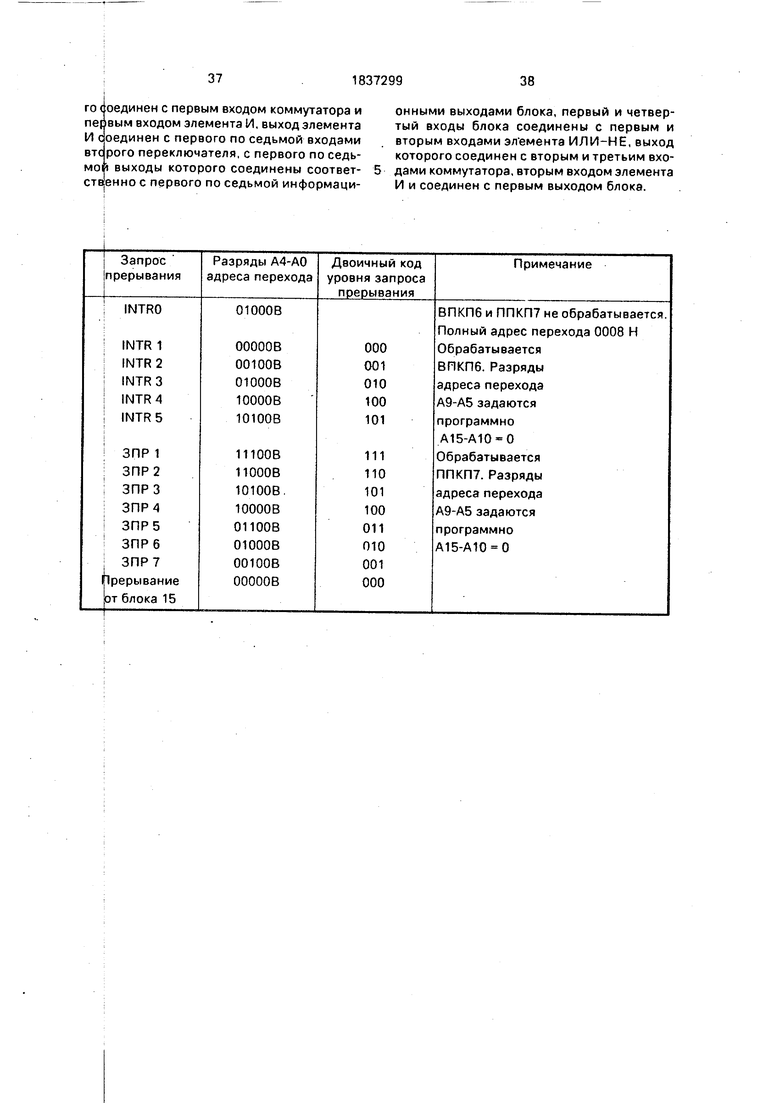

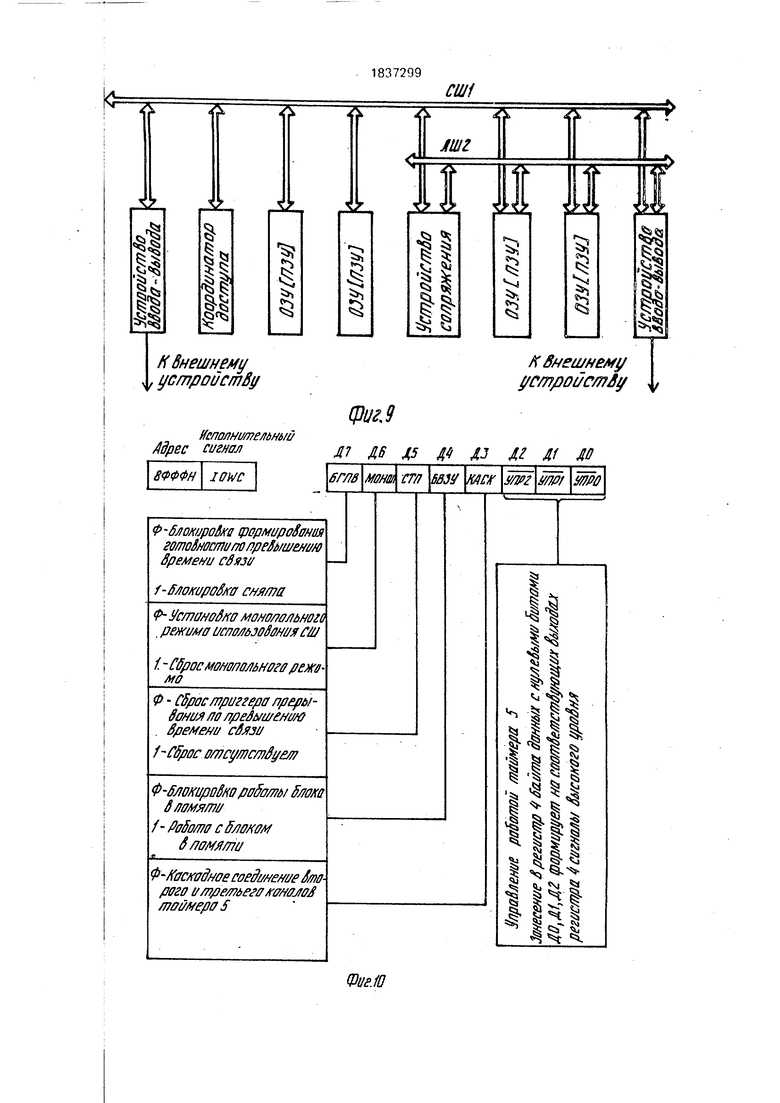

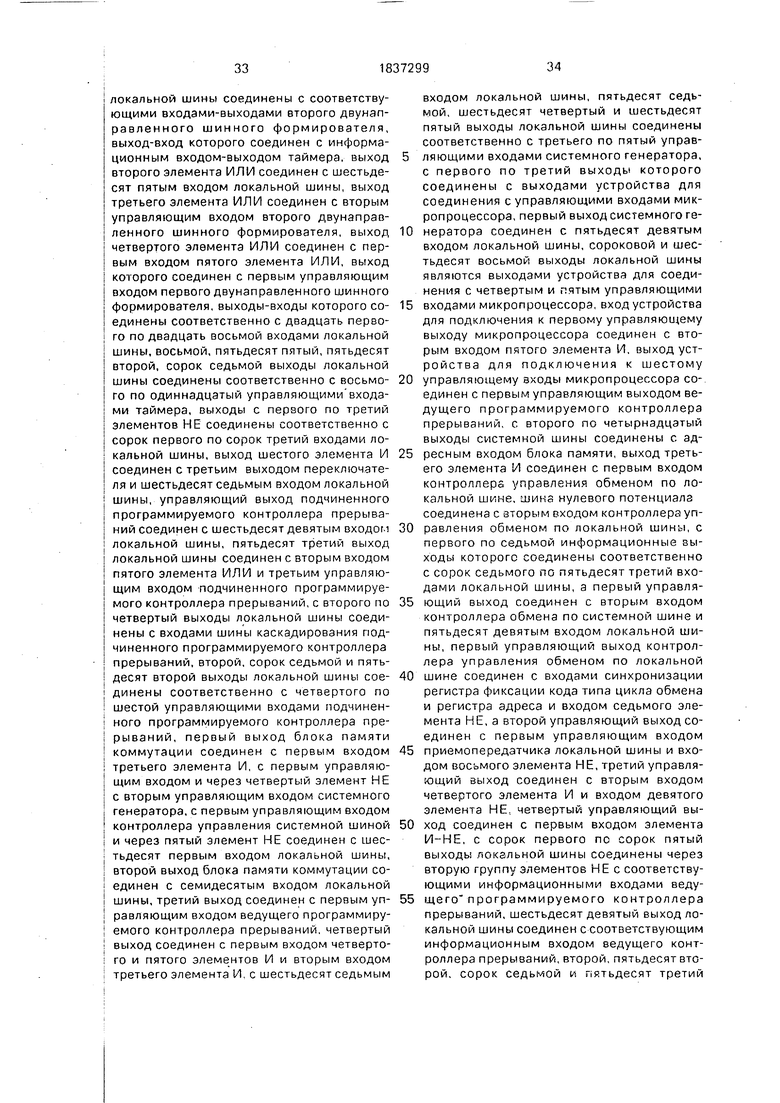

На фиг.9 приведен пример конфигурации системы, в котором заявляемое устройство использует СШ1 совместно с другим микропроцессорным контроллером под управлением координатора.

Временные диаграммы сигналов, используемых для обмена данными в этом режиме, приведены на фиг.18т-24. Если в цикле обмена блока 23 памяти коммутации выявил адрес запоминающего устройства или устройства ввода-вывода, определенный, как системный, на его первом выходе (ЛОК/СИСТ) в такте И будет сформирован сигнал высокого уровня. Этот сигнал блокирует по входу GEN контроллера 9 формирование последнего исполнительных сигналов. Одновременно этот сигнал снимает запрет на формирование исполнительных сигналов на первом-четвертом выходах и сигнала DEN на выходе 10.9 контроллера 10. Начало формирования сигналов на выходах контроллера 10 определяется моментом подачи на его вход AEN сигнала низкого уровня СПС, определяющего время выдачи адреса обращения на линии связи СШ 1 и формиру- емого схемой 16, По сигналу САСШ, формируемому схемой 16, выходные цепи регистра 13 переводятся в активное состояние и хранящийся в регистре 13 адрес, выставлявшийся микропроцессором 50 на шинах AD15-ADO, поступает на нулевой- пятнадцатый входы СШ1.

поступлении низкого уровня сигнала СПС на вход AEN контроллера 10 последний с задержкой (т 85 не) начинает формировать исполнительный сигнал на одном из первого-четвертого выходов и сигнал DEN. Получив исполнительный сигнал, адресуемое устройство выставляет на сорок четвертом выходе СШ1 сигнал ОТВ.

При этом на выходе элемента 28 ИЛИ сформируется сигнал f СШ высокого уровня. Если же адресуемое устройство в течение заданного промежутка времени т(т 45нс) не ответит, то сигнал ГСШ формируется схемой 15. Сигнал ГСШ поступает на пятый вход (RDV2) генератора 22. Сигнал высокого уровня ЛОК/СИСТ с первого выхода блока 23 памяти коммутации поступает на второй

вход(АЕ№) генератора 22 и разрешает формирование сигнала готовности (READY) на третьем выходе микропроцессора 50. блокируя этим формирование сигнала готовности на третьем выходе из сигнала ГЛШ, поступающего на четвертый вход. Сигнал запроса на управление шиной снимается в такте Т1 следующего цикла обмена сигналом СТРОБ. При этом в пассивное состояние переходит сигнал разрешения на управление шиной и, как следствие, сигналы САСШ и СИС. В свою очередь, это вызывает переключение выходных цепей регистра 13 и цепей исполнительных сигналов контроллера 10 в высокоимпедансное состояние, чем и заканчивается цикл обмена по СШ1 (к моменту перехода цепей исполнительных сигналов в высокоимпедансное состояние, сигналы на выходах контроллера 10 согласно алгоритму работы последнего находятся уже в пассивном состоянии).

Коммутация восьмиразрядной шины данных СШ1 на шестнадцатиразрядную мультиплексированную шину адреса/данных микропроцессора 50 осуществляется следующим образом. При обращении к устройствам с нечетными адресами, шина данных СШ1 коммутируется на старшие разряды мультиплексированной шины адреса/данных микропроцессора AD15-AD8, а при обращении к устройствам с четными адресами - на младшие разряды мультиплексированной шины адреса/данных AD7-ADO.

Выборка приемопередатчиками 14.1 и 14.2 младшего и старшего байтов произво- дится сигналами низкого ур.овня ВНЕ и LAO, формируемыми на первом и сорок шестом выходах ЛШ. при условии, что на выходе DEN контроллера 10 имеет место сигнал высокого уровня. Выборка приемопередатчиком 14.2 старшего байта СШ, коммутирующего шину данных СШ на старшие разряды мультиплексированной шины адреса/данных микропроцессора 50, дополнительно блокируется по совпадению уровней сигналов ВНЕ и LAO. Следовательно, при ошибочной попытке обмена словом данных за один цикл обмена с устройством, сопрягаемым по СШ1, фактически произойдет обмен младшим байтом данных с устройством, имеющим четный адрес.

Работа устройства сопряжения в монопольном режиме.

Монопольный режим обмена по СШ1 может быть установлен следующими способами:

(установка монопольного режима на время выполнения программ предполагает наличие в системе координатора),

а) установкой на выходе W (LOCK) микропроцессора 50 сигнала низкого уровня, что имеет место при выполнении команд с префиксом LOCK и в циклах INTA;

б) путем программной выдачи по адресу

регистра 4 кода, формирующего единичный сигнал МОНОП;

в) путем размыкания соответствующего контакта переключателя 26. формирую0 щего сигнал МОНОП на третьем входе схемы 16.

При выполнении команд с префиксом LOCK и в циклах INTA на первом выходе микропроцессора 50 формируется сигнал

5 LOCK, который через элемент 43 НЕ поступает на шестьдесят третий вход ЛШ2. На более длительное время монопольный режим вызывается путем программной выдачи на регистр 4 кода, вызывающего

0 появление на его четвертом выходе сигнала логической единицы (МОНОП). Через третий контакт переключателя 26 этот сигнал поступает на схему 16 формирования интерфейсных сигналов. При разомкнутом состо5 янии третьего контакта переключателя 26 в схему 16 постоянно поступает сигнал логической единицы. Этому состоянию соответствует ситуация, когда заявляемое устройство монопольно управляет работой

0 СШ1. В этом случае необходимость арбитража отпадает и координатор доступа к магистрали не нужен. Временные диаграммы сигналов, используемых устройством для сопряжения в процессе управления обме5 ном данными по СШ в этом режиме, приведены на фиг.19.

Работа устройства со встроенным блоком 8 памяти.

При обращении к блоку 8 памяти на

0 четвертом выходе блока 23 появляется сигнал ОВЗУ. Этот сигнал через элемент 36 И поступает на вход выборки блока 8 памяти. Младшие разряды адреса с второго-лят- надцатого выходов Л Ш поступают на адрес5 ные входы блока 8 памяти. Считываемая с блока 8 памяти информация поступает в микропроцессор 50 по мультиплексированной шине адреса/данных.

Блок 23 памяти коммутации восприни0 мает адреса блока 8 памяти как адреса запоминающих устройств, сопрягаемых по ЛШ2, и на первом выходе устанавливает сигнал низкого уровня ЛОК/СИСТ.

Наряду с этим, при обращении микро5 процессора 50 к последним 64 К байт адресуемого поля памяти на четвертом выходе блока 23 памяти коммутации формируется сигнал высокого уровня ОВЗУ. Сигнал высокого уровня ОВЗУ запрещает по входу GEN формировать исполнительные сигналы и

сигнал на выходе PEN контроллера 9, а сигнал низкого уровня ЛОК/СИСТ запрещает формировать исполнительные сигналы и сигнал на выходе DEN контроллера 10. Таким образом, шины данных как СШ1, так и ЛШ2 оказываются изолированными от мультиплексированной шины 50.9 адреса/данных микропроцессора 50. Выборка данных из блока 8 памяти осуществляется исполнительным сигналом низкого уровня, формируемым на выходе R микропроцессора 50, При наличии высокого уровня сигнала ОВЗУ сигнал с второго выхода микропроцессора 50 через элемент 36 И выбирает из блока 8 памяти информацию (см. фиг.22).

Обработка прерываний.

Заявляемое устройство обрабатывает следующие запросы прерываний:

-семи уровней приоритета с СШ1;

-шести уровней приоритета с ЛШ2;

-внутренние прерывания от схемы 15 (схемы формирования готовности по превышению времени связи).

Прерывание, поступающее с сорокового выхода 2.40. ЛШ2 подается на четвертый вход 50.4 микропроцессора 50 и обрабатывается как аппаратное немаскируемое прерывание. Для приоритетной обработки остальных запросов прерывания используется ВАКП6 и ППКП7 в каскадном включе- нии. Приоритеты запросов прерывания задаются при программной настройке контроллеров 6, 7. Адреса переходов программ по приему вектора прерывания при обработке прерываний приведены в таблице.

Запросы прерываний (INTR4, INTR5) на сорок четвертом и сорок пятом выходах ЛШ2 могут формироваться в заявляемом устройстве непосредственно, либо на эти линии связи ЛШ2 могут быть выведены проинвертированные сигналы с выходов INT подчиненных контроллеров, входящих в состав устройств, сопрягаемых по ЛШ2, В последнем случае каждый запрос прерывания INTR4 или INTR5 распадается на 8 радиальных приоритетных запросов, обрабатываемых подчиненными ПКП.

В циклах INTA микропроцессор может принимать вектор прерывания как от контроллера 6, так и от подчиненного контрол- лера 7, либо подчиненных программируемых контроллеров прерываний, входящих в состав устройств, сопрягаемых микропроцессором 50 по ЛШ2. Контроллер 6 выставляет код вектора прерывания непос- редственно на мультиплексированную шину адреса/данных микропроцессора 50, а подчиненные ПКП - на СШ1, Адрес подчиненного ПКП, которому предоставлено право передачи вектора прерывания микропроцессору 50, формируется контроллером 6 в цикле INTA на адресном выходе (CASO- CAS2), запоминается и передается на вто- рой-четвертый входы ЛШ2.

При обработке прерывания, принятого как от ВПКП6, так и от ППКП7, микропроцессор 50 выполняет два следующих друг за другом цикла INTA (см. фиг.23). Первый цикл сопровождается установкой сигнала низкого уровня LOCK на первом выходе W микропроцессора 50.

Первый цикл не сопровождается передачей данных по мультиплексированной шине 50.9 адреса/данных микропроцессора 50, т.к. выходные ключи шинного формирователя 19, коммутирующего сигналы с адресных выходов контроллера 6, установлены в высокоимпедансное состояние сигналом единичного уровня с выхода элемента 48 И-НЕ (высокий уровень сигнала на выходе элемента 48 И-НЕ имеет место, так как сигнал на первом выходе микропроцессора LOCK имеет низкий уро- . вень, а сигнал на четвертом выходе контроллера 9 - высокий уровень). В начале второго цикла INTA формируются условия для коммутации сигналов с адресных выходов контроллера 6 через формирователь 19 на мультиплексированную шину 5.9 адреса/данных микропроцессора 50. Сигналы с адресных выходов контроллера 6 содержат полезную информацию (адрес подчиненного ПКП, которому предоставлено право установки кода вектора прерываний на ЛШ2 при соблюдении следующих условий:

-запрос прерывания был принят подчиненным ПКП;

-принятый ВПКП6 от подчиненного ПКП запрос был расценен ВПКП как наиболее приоритетный,

Адрес выбранного подчиненного ПКП с адресных выходов контроллера 6 транслируется на мультиплексированную шину 50.9 адреса/данных микропроцессора 50 (AD3- AD1) в течение времени одновременного существования сигнала низкого уровня на выходе LOCK микропроцессора 50 и сигнала высокого уровня на выходе PDEN контроллера 9.

Адрес подчиненного ПКП фиксируется по сигналу ALE с третьего выхода контроллера 9 в регистре 12 « поступает на второй- четвертый входы ЛШ2.

Подчиненный ПКП, которому программно присвоен адрес, совпадающий с установленным на второй-четвертой линиях ЛШ2, по исполнительному сигналу INTA выставляет на двадцать первый - двадцать восьмой входы ЛШ2 вектор прерывания.

Для обеспечения трансляции вектора с ЛШ2 на мультиплексированную шину 50.9 данных/адреса микропроцессора 50 контроллер 6, предоставляя право установки вектора прерывания контроллеру 7, устанавливает сигнал высокого уровня на своем выходе SPIEN и сохраняет высокоимпедан- сное состояние на информационных выходах D7-DO.

В случае, если наиболее приоритетным оказалось прерывание, принятое непосредственно контроллером 6, то во втором цикле INTA контроллер 6 будет сохранять на своем выходе SPIEN сигнал низкого уровня, изолирующий мультиплексированную шину 50.9 адреса/данных микропроцессора 50 от ЛШ-2. По исполнительному сигналу на пятьдесят третьем входе ЛШ2 контроллер 6 сам выставляет вектор прерывания на мультиплексированную шину 50.9 адреса/данных микропроцессора 50. При этом информация на входах с первого по двадцатый ЛШ2 устройством не воспринимается.

Формула изобретения 1. Устройство для сопряжения микропроцессора с системной шиной, содержащее подчиненный программируемый контроллер прерываний, генератор импульсов, регистр фиксации кода типа цикла обмена, регистр адреса, регистр адреса системной шины, приемопередатчик младшего байта системной шины, контроллер управления обменом по системной шине, коммутатор сигналов, с первого по четвер- тый элементы И, причем с первого по шест- надцатый выходы регистра адреса системной шины соединены соответствен- но с нулевого по пятнадцатый входами сис- темной шины, выход первого элемента И соединен с первым управляющим входом приемопередатчика младшего байта сис- темной шины, информационный выход- вход которого соединен соответственно с шестнадцатого по двадцать третий входами системной шины, с первого по четвертый выходы контроллера управления обменом по системной шине соединены соответственно с двадцать четвертого по двадцать седьмой входами системной шины, отличающееся тем, что, с целью расширения области применения и повышения быстродействия, устройство содержит системный генератор, блок памяти, ведущий программируемый контроллер прерываний, таймер, генератор пуска-останова, переключатель, блок формирования внутренней готовности, блок формирования готовности, блок формирования интерфейсных сигналов, контроллер управления обменом по локальной шине, шинный формирователь адреса, приемопередатчик локальной шины, первый и второй двунаправленные шинные формирователи, приемопередатчик старшего байта системной шины, дешифратор адреса обмена, первую и вторую группы элементов НЕ, пятый и шестой элементы И, элемент И-НЕ, с первого по пятый элементы ИЛИ, элемент нерав0 нозначности, с первого по девятый элементы НЕ. блок памяти коммутации, причем пятый выход котроллера управления обменом по системной шине соединен с вторым управляющем входом приемопе5 редатчика младшего байта системной шины и первым управляющим входом приемопередатчика старшего байта системной шины, выход-вход которого соединен с шестнадцатого по двадцать третий входами

0 системной шины, шестой выход контроллера управления обменом по системной шине соединен с первыми входами первого и второго элементов И, выход второго элемента И соединен с вторым управляющим входом

5 приемопередатчика старшего байта по системной шине, седьмой вход контроллера управления обменом по системной шине соединен с входом синхронизации регистра адреса системной шины, с сорок пятого по

0 пятьдесят первый выходы системной шины

через элементы НЕ первой группы соедине. ны- соответственно с первого по седьмой

информационными входами подчиненного

программируемого контроллера прерыва5 ний, информационный выход-вход которого соединен с информационным входом-выходом первого двунаправленного шинного формирователя, с двадцать первого по двадцать восьмой выходы системной шины

0 соединены с информационными входами регистра конфигурации, первый выход регистра конфигурации соединен с первым входом блока, формирования готовности, второй выход соединен с управляющим вхо5 дом коммутатора сигналов, третий и четвертый выходы соединены с первым и вторым входами переключателя, пятый выход соединен с входом шестого элемента И, с шестого по восьмой выходы регистра

0 конфигурации соединены соответственно с первого по третий входами таймера, с первого по третий выходы таймера соединены соответственно с входами первого, второго «третьего элементов НЕ, первый выходтай5 мера соединен с четвертым входом таймера и первым информационным входом коммутатора сигналов, второй выход таймера соединен с вторым информационным входом коммутатора сигналов, выход которого соединен с пятым входом таймера, третий вход

переключателя соединен с шиной нулевого потенциала, первый выход генератора импульсов через четвертый вход переключателя соединен с сорок вторым входом системной шины, второй выход генератора импульсов соединен с шестым входом таймера, первый выход переключателя соединен с первым управляющим входом блока формирования интерфейсных сигналов, информационные выходы которого соединены соответственно с двадцать восьмого по тридцать четвертый входами системной шины, с тридцать пятого по сорок первый выходы системной шины соединены с информационными входами блока форми- рования интерфейсных сигналов, сорок третий выход системной шины соединен с входом генератора пуска-останова, сорок четвертый выход системной шины соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, с первого по двадцатый и двадцать первый выходы регистра адреса соединены соответственно с первого по двадцатый и сорок шестой входами локальной шины, а первый, четвертый, восьмой и с пятнадцатого по двадцатый выходы соединены с соответствующими входами первого информационного входа блока памяти коммутации, с двадцать первого по тридцать шестой входы-выходы локальной шины соединены с соответствующими входами-выходами информационного входа- выхода приемопередатчика локальной шины, с первого по двадцать первый вы- ходы-входы устройства для соединения с адресно-информационной шиной микропроцессора соединены с информационными входами регистра адреса, с первого по восьмой выходы адресно-информационной шины устройства соединены с информационным входом-выходом ведущего контроллера прерываний, с выходами шинного формирователя адреса выборки подчиненного контроллера, с информационными вхо- дами приемопередатчика младшего байта системной шины, с первого по шестнадцатый входы-выходы устройства для подключения адресно-информационной шины микропроцессора соединены с первыми вы- ходами-входами приемопередатчика локальной шины, с выходами блока памяти, с девятого по шестнадцатый выходы соединены с информационным входом регистра адреса системной шины и приемопередатчика старшего байта системной шины, с первого по третий выходы устройства для подключения управляющего выхода микропроцессора соединены с соответствующими управляющими входами контроллера управления обменом по локальной шине, контроллера управления обменом по системной шине и информационными входами регистра фиксации кода типа обмена, выходы которого соединены с вторым информационным входом блока памяти коммутации и с тридцать седьмого по тридцать девятый входами локальной шины, первый с четвертого по восьмой, шестнадцатый, с тридцать седьмого по тридцать девятый выходы локальной шины соединены с информационным входом дешифратора адреса обмена, первый выход которого соединен с первым управляющим входом регистра конфигурации, второй выход соединен с первым входом третьего элемента ИЛИ и седьмым управляющим входом таймера, третий выход соединен с первым входом четвертого элемента ИЛИ и первым управляющим входом подчиненного программируемого контроллера прерываний, первый выход генератора пуска-останова соединен с третьим входом блока формирования готовности, пятьдесят четвертый, пятьдесят девятый, шестидесятый, шестьдесят седьмой, тридцать девятый выходы локальной шины соединены соответственно с первого по пятый входами блока формирования внутренней готовности, первый выход которого соединен с шестьдесят четвертым входом локальной шины, второй выход соединен с вторым управляющим входом блока формирования интерфейсных сигналов, шестьдесят первый выход локальной шины соединен с третьим управляющим входом блока формирования интерфейсных сигналов, с первого по третий правляющие выходы которого соединены соответственно с пятьдесят восьмым, шестьдесят вторым и шестьдесят шестым входами локальной шины, пятьдесят шестой, шестьдесят первый и шестьдесят второй выходы которой соединены соответственно с четвертого по шестой входами блока формирования готовности, первый выход которого соединен с вторым входом второго элемента ИЛИ и шестым входом блока формирования внутренней готовности, второй выход соединен с вторым управляющим входом подчиненного программируемого контроллера прерываний, сорок девятый выходэлокальной шины соединен с третьим управляющим входом регистра конфигурации, пятьдесят шестой выход соединен с вторыми входами третьего и четвертого элементов ИЛИ, пятьдесят пятый выход соединен с первым управляющим входом второго двунаправленного шинного формирователя, с двадцать первого по двадцать восьмой выходы-входы

локальной шины соединены с соответствующими входами-выходами второго двунаправленного шинного формирователя, выход-вход которого соединен с информационным входом-выходом таймера, выход второго элемента ИЛИ соединен с шестьдесят пятым входом локальной шины, выход третьего элемента ИЛИ соединен с вторым управляющим входом второго двунаправленного шинного формирователя, выход четвертого элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, выход которого соединен с первым управляющим входом первого двунаправленного шинного формирователя, выходы-входы которого соединены соответственно с двадцать первого по двадцать восьмой входами локальной шины, восьмой, пятьдесят пятый, пятьдесят второй, сорок седьмой выходы локальной шины соединены соответственно с восьмого по одиннадцатый управляющими входами таймера, выходы с первого по третий элементов НЕ соединены соответственно с сорок первого по сорок третий входами локальной шины, выход шестого элемента И соединен с третьим выходом переключателя и шестьдесят седьмым входом локальной шины, управляющий выход подчиненного программируемого контроллера прерываний соединен с шестьдесят девятым входом локальной шины, пятьдесят третий выход локальной шины соединен с вторым входом пятого элемента ИЛИ и третьим управляющим входом подчиненного программируемого контроллера прерываний, с второго по четвертый выходы локальной шины соединены с входами шины каскадирования подчиненного программируемого контроллера прерываний,второй, сорок седьмой и пятьдесят второй выходы локальной шины соединены соответственно с четвертого по шестой управляющими входами подчиненного программируемого контроллера прерываний, первый выход блока памяти коммутации соединен с первым входом третьего элемента И, с первым управляющим входом и через четвертый элемент НЕ с вторым управляющим входом системного генератора, с первым управляющим входом контроллера управления системной шиной и через пятый элемент НЕ соединен с шестьдесят первым входом локальной шины, второй выход блока памяти коммутации соединен с семидесятым входом локальной шины, третий выход соединен с первым управляющим входом ведущего программируемого контроллера прерываний, четвертый выход соединен с первым входом четвертого и пятого элементов И и вторым входом третьего элемента И, с шестьдесят седьмым

входом локальной шины, пятьдесят седьмой, шестьдесят четвертый и шестьдесят пятый выходы локальной шины соединены соответственно с третьего по пятый управляющими входами системного генератора, с первого по третий выходы которого соединены с выходами устройства для соединения с управляющими входами микропроцессора, первый выход системного ге0 нератора соединен с пятьдесят девятым входом локальной шины, сороковой и шестьдесят восьмой выходы локальной шины являются выходами устройства для соединения с четвертым и пятым управляющими

5 входами микропроцессора, вход устройства для подключения к первому управляющему выходу микропроцессора соединен с вторым входом пятого элемента И, выход устройства для подключения к шестому

0 управляющему входы микропроцессора соединен с первым управляющим выходом ведущего программируемого контроллера прерываний, с второго по четырнадцатый выходы системной шины соединены с. ад5 ресным входом блока памяти, выход третьего элемента И соединен с первым входом контроллера управления обменом по локальной шине, шина нулевого потенциала соединена с вторым входом контроллера уп0 равления обменом по локальной шины, с первого по седьмой информационные выходы которого соединены соответственно с сорок седьмого по пятьдесят третий входами локальной шины, а первый управля5 ющий выход соединен с вторым входом контроллера обмена по системной шине и пятьдесят девятым входом локальной шины, первый управляющий выход контроллера управления обменом по локальной

0 шине соединен с входами синхронизации регистра фиксации кода типа цикла обмена и регистра адреса и входом седьмого элемента НЕ, а второй управляющий выход соединен с первым управляющим входом

5 приемопередатчика локальной шины и входом восьмого элемента НЕ, третий управляющий выход соединен с вторым входом четвертого элемента И и входом девятого элемента НЕ, четвертый управляющий вы0 ход соединен с первым входом элемента И-НЕ, с сорок первого по сорок пятый выходы локальной шины соединены через вторую группу элементов НЕ с соответствующими информационными входами веду5 щего программируемого контроллера прерываний, шестьдесят девятый выход локальной шины соединен с соответствующим информационным входом ведущего контроллера прерываний,второй,пятьдесят второй, сорок седьмой и пятьдесят третий

выходы локальной шины соединены соответственно с второго по пятый управляющими входами ведущего программируемого контроллера прерываний, входы-выходы шины каскадирования которого соединены с информационными входами шинного формирователя адреса выборки подчиненного контроллера, а второй управляющий выход соединен с третьим входом четвертого элемента И, выход которого соединен с вторым управляющим входом приемопередатчика локальной шины, шестьдесят третий выход локальной шины соединен с вторым входом первого элемента И-НЕ, выход которого соединен с управляющим входом шинного формирователя адреса выборки подчиненного программируемого контроллера прерываний, выход пятого элемента И соединен с управляющим входом блока памяти, выходы седьмого, восьмого и девятого элементов НЕ соединены соответственно с шестидесятым, пятьдесят пятым и пятьдесят шестым входами локальной шины, шестьдесят второй выход локальной шины соединен с управляющим входом регистра адреса системной шины, первый выход локальной шины соединен с первым входом первого элемента И и первым входом элемента неравнозначности, сорок шестой выход локальной шины соединен с вторым входом элемента неравнозначности и вторым входом второго элемента И, выход элемента неравнозначности соединен с третьим входом второго элемента И, семидесятый выход локальной шины соединен с седьмым входом блока формирования внутренней готовности, шестьдесят третий выход локальной шины соединен с четвертым управляющим входом блока формирования интерфейсных сигналов, второй выход гене- ратора пуска-останова соединен с вторым управляющим входом регистра конфигурации, третий выход соединен с пятьдесят седьмым входом локальной шины, шестьдесят шестой выход локальной шины соеди- нен с третьим управляющим входом контроллера управления обменным по системной шине.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок формирования внутренней готовности содержит первый и второй триггеры, первый и второй элементы НЕ, первый, второй и третий элементы И-НЕ, причем первый вход блока соединен с первым входом первого элемента И-НЕ, второй вход блока через первый элемент НЕ соединен с входами синхронизации первого и второго триггеров, третий вход блока соединен с входами сброса первого и второго триггеров, четвертый и пятый входы блока

соединены с первым и вторым входами второго элемента И-НЕ, выход которого соединен с седьмым входом блока и первым входом третьего элемента И-НЕ, выход которого соединен с вторым входом первого элемента И-НЕ, шестой вход блока соединен с третьим входом первого элемента И-НЕ. выход первого триггера соединен с вторым выходом схемы, а прямой выход соединен с входом данных второго триггера, шина нулевого потенциала через второй элемент НЕ соединена с J- и S-входами первого триггера и S-входами второго триггера, выход которого соединен с вторым входом третьего элемента И-НЕ, К-вход первого триггера соединен с шиной нулевого потенциала,

3.Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок формирования готовности содержит коммутатор, триггер, первый и второй элементы ИЛИ-НЕ, первый и второй элементы НЕ, причем первый вход блока соединен с первым входом первого элемента ИЛИ-НЕ, второй вход блока соединен с первым входом первого элемента ИЛИ-НЕ, третий вход блока соединен с вторым входом первого элемента ИЛИ-НЕ, выход которого соединен с входом сброса триггера, четвертый, пятый и шестой входы блока соединены соответственно с первым информационным управляющим и вторым информационным входами коммутатора, выход которого соединен через элемент задержки с вторым входом второго элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с первым выходом блока и через первый элемент НЕ с входом синхронизации триггера, шина нулевого потенциала соединена с входом второго элемента НЕ, выход которого соединен с D- и S-входами триггера, выход триггера является вторым выходом блока.

4.Устройство поп.1,отличающее- с я тем, что блок формирования интерфейсных сигналов содержит первый и второй переключатели, коммутатор, элементы И, ИЛИ, ИЛИ-НЕ, НЕ, элемент задержки, с первого по седьмой информационные входы блока соединения соответственно с первого по седьмой входами первого переключателя, восьмой вход первого переключателя соединеу с шиной нулевого потенциала, выходы первого переключателя соединены меду собой и с управляющим входом коммутатора, выход которого соединен через элемент НЕ с вторым выходом блока и через элемент задержки с третьим выходом блока, второй и третий входы блока соединены с первым и вторым входами элемента ИЛИ. выход которого соединен с первым входом коммутатора и первым входом элемента 1/1, выход элемента И соединен с первого по седьмой входами втс рого переключателя, с первого по седьмой выходы которого соединены соответ- с первого по седьмой информационными выходами блока, первый и четвертый входы блока соединены с первым и вторым входами эл емента ИЛИ-НЕ, выход которого соединен с вторым и третьим входами коммутатора, вторым входом элемента И и соединен с первым выходом блока.

191 № 9$7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| Устройство автоматического контроля электронных систем | 1982 |

|

SU1129570A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

662IC81

2Щ

2

ббш;81

здмщм $

РЛМТ-ЩМК

гкг «.

УСТ «UTB +

3 lP7-3fJPf

f.L S-J4J f.35-4f

+ /.4(2 + {43

+ S.44 f.L45-5f

Фиг. 4

j.f

м

Я/

1837299

,

#7й.Ј

Л

Ъ8

f6.8 .

I II

1 1 §1

Г

1

il

ti

rf

H 11

I

%

it

Ч

I

I

Y

t

i

t

I

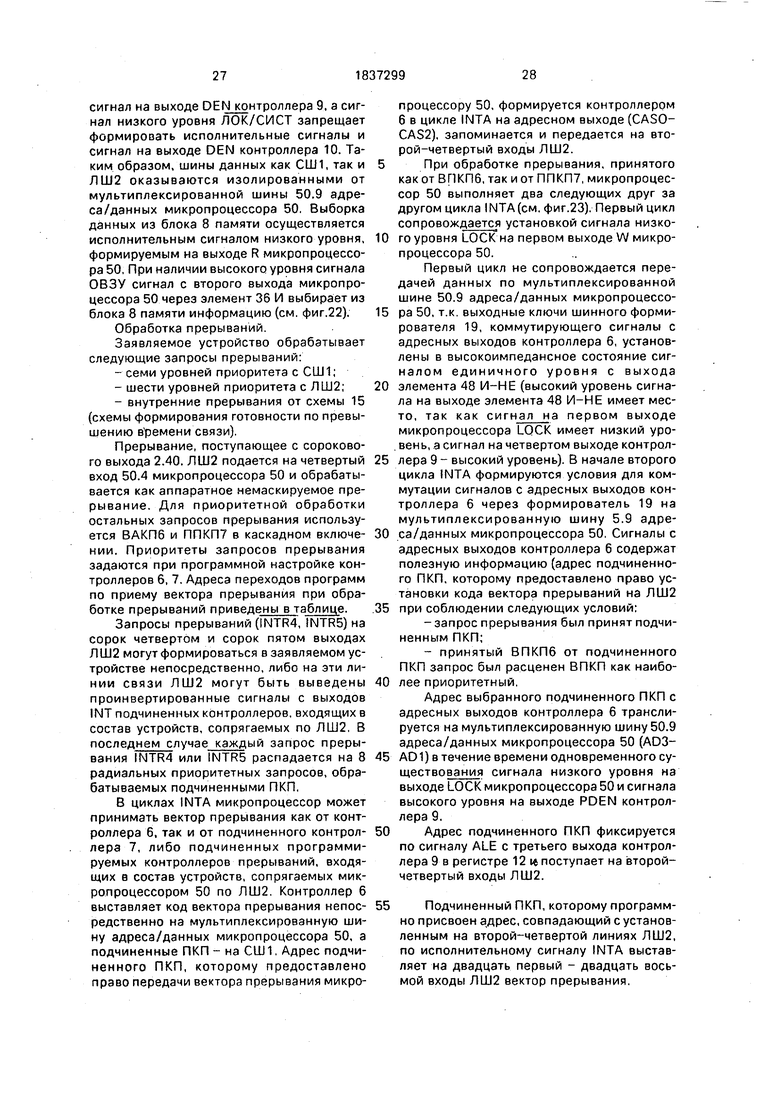

Упра8ление работой таймера S Занесение Ј регистр 4Ја.иш данш/х с щлебь/ми Ии/яоми ДО, Јf} Д2 срормируе/л на соо/яйетс/яйр/ощм Дшод&х регистра 4 сигналы Джокого уройня

11

ill

ill

i

ll

«

§

s

i i

w

II

§1 II

II

ll

e

t w

M.

I

1

til

Н

§1

Ц

II li

s

I

t

it I

t

4

Ус/ппойство ВДода-fo/tloda

Моирдинатор доступа

J

fc

t

«

Устройство сопряжения

оэ

4 Ю О CD

I

§

ь

1

I

41

ОЗУ1/73У

УстаоустДе еЈоа0- вьшодв.

Улр-айлтщее CMS о

ffff

0s

м

№

яг

я/ яо

Выбор Регистр режима

ФФ- канал о

ф{- канал f

Ф- /TWOS Z

11- зрлрел

К00

Ф - дЗоичный

/ - дДоично-оеся/личный

PeWL/At 0000/776/

ФФФ - режим о

ФФ -#ежим 1

//# - Режим г

111 -Режим з

- Режим 4

1Ф1-Режим 5

У/яемие Јj0f/ pj/faJ

ФФ- оле/нщия.. загщелмммия Ф/- /no/two м/tffЯшин ffffu/я

1 P-/7 0/7A/Cff Cff qpU/l/U ffffl//7J

н-м/юдшшмжмс/яера/мШ/л

Фиг.М

1837299

Функции Годного бентмя /яаймера S

Фиг.1

а

-jnjojiJijijTjarij

о

1 5 « 3 ,

S

jiruiJiJijnjiJiJTjnja

--ЈfЈi

4 Ъ 214 3 2 7 О.

ЛI

в

nJ JlJTJ JTJlJ Jnjn

1±3

4$ г JJ з г / #з)2 1

pt/c. f3

5 U Ъ 2 i О

г о

,

4 Ъ 2 1 ff

4 з 2 1 ф)г f 0(3) г t 0(3}

LJ