(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Нерекурсивный цифровой фильтр | 1986 |

|

SU1365349A2 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для высокоточного преобразо вания цифровой информации в аналоговую. Цель изобретения - уменьшение нелинейных искажений и повышение достоверности преобразования. Цифроаналоговый преобразователь содержит входную шину 1 Вы

vj ю о о

CJ

о

бор режима, входную шину 2 Запуск, входную информационную шину 3, источник 4 опорного тока,преобразователь 5 кода в ток, выходное устройство 6, блок 7 регулирования задержки, первый регистр 8, блок 9 выделения разности, компаратор 10 напряжения, триггер 11, цифровой коммутатор 12, регистр 13 сдвига, цифровую схему 14 сравнения, первый блок 15 постоянной памяти, элемент ИЛИ, третий блок 17 постоянной памяти, второй блркТВ постоянной памяти, блок 19 суммирования, четвертый

s-,,.;

.:

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых вел йчин в аналоговые,;.

Известен цифроаналоговый преобразователь , содержащий регистр, три декодирующих преобразователя, источник аналогового напряжения, два блока преобразователей кодов и дополнительный разрядный элемент.,, :,-.,.,..,. .. . ; ;

Недостатком устройства является невысокая точность преобразования,

Известен цифроаналоговый преобразователь, содержащий генератор тактовых импульсов, счетчик, постоянное запоминающее устройство и цифроаналоговый преобразователь..

Недостатком данного устройства является невысокая точность преобразования.

Наиболее близким по технической сущности к предлагаемому изобретению является цифроаналоговый преобразователь, содержащий информационный вход, ЦАП, в дальнейшем именуемый преобразователь код-ток и выходное устройство, три блока постоянной памяти, логический элемент ИЛИ, блок суммирования, первый регистр; второй регистр; преобразователь температуры, аналоговый коммутатор, аналого-циф- ровой преобразователь, блок прогноза контроля, именуемые в дальнейшем цифровой датчик температуры; блок управления, первый, второй и третий выходы которого соединены с входами цифрового датчика температуры, выходы которого соединены со старшими входами первого блока постоянной памяти, младшие входы которого соединены с выходами старших разрядов входного регистра, управляющие входы которого соединены с четвертым и пятым выходом блока управления, первый и второй входы которого соединены с выходами циф блок 20 постоянной памяти, цифровой датчик 21 температур, второй регистр 22, блок 23 управления, первую 24 и вторую 25 выходные шины. Введение блока 7 позволило снизить нелинейные искажения за счет оптимального выбора задержки включения знакового разряда, а совокупность блоков 9, 10, 13 и 14 обеспечивает повышение достоверности результатов преобразования за счет формирования,сигнала правильности функционирования преобразователя, 3 з.п. ф-лы, 8 ил.

рового датчика температуры, выходы которого соединены со старшими входами второго блока постоянной памяти, выходы которого соединены с входами младших

разрядов преобразователя код-ток, вход которого соединен с выходом логического элемента ИЛИ, входы которого соединены с выходами старшего разряда второго блока постоянной памяти и младшего разряда

первого блока постоянной памяти, выходы которого соединены с входами старших разрядов преобразователя код-ток, выход которого является выходом устройства и соединен с входом цифрового датчика температуры, выходы которого соединены со

старшими входами третьего блока постоянной памяти, выходы которого соединены с

входами блока суммирования, выходы которого соединены с младшими входами второго блока постоянной памяти; младшие входы третьего блока постоянной памяти соединены с выходами старших разрядов регистра, выходы младших разрядов которого соединены с входами блока суммирования; входы регистра являются входами

устройства; третий вход блока управления

является управляющим входом устройства.

Недостатком данного устройства являются большие нелинейные искажения и низкая достоверность преобразования, обусловленные возникновением всплесков напряжения выходного сигнала при переключении разрядов, особенно при переключении знакового разряда.

Цель изобретения - уменьшение нелинейных искажений и повышение достоверности преобразования.

Поставленная цель достигается тем, что в цифроаналоговый преобразователь, содержащий информационный вход, преобразователь код-ток, выходное устройство, три блока постоянной памяти, логический элемент ИЛИ, два регистра, блок, суммирования, цифровой датчик температуры, блок управления, шестой вход которого соединен с входом первого регистра, входы старших разрядов которого соединены с входами первого и третьего блоков постоянной памяти, выход третьего блока постоянной памяти соединен с входами блока суммирования, вторые входы которого соединены с выходами младших разрядов первого регистра, выходы блока суммирования соединены с входами второго блока постоянной памяти, младший разряд которого и старший разряд второго блока постоянной памяти соединены с входами элемента ИЛИ, дополнительно введены цифровой коммутатор, блок регулирования задержки, источник опорного тока, блок выделения разности, компаратор напряжения, сдвиговый регистр, регистр, триггер, цифровая схема сравнения, четвертый блок постоянной памяти, входы которого соединены с выходами цифрового датчика температуры и входами младших разрядов первого, второго и третьего блоков постоянной памяти, выходы первого и второго блока постоянной памяти соединены.с входами цифрового коммутатора, m-й вход которого соединен с выходом ИЛИ, k-e выходы цифрового коммутатора соединены с выходами четвертого блок.ч постоянной памяти, управляющий вход которого соединен с девятым входом блока управления, третий и четвертый выходы которого соединены с входами цифрового коммутатора, р-е входы которого соединены с нулевой шиной, а выход цифрового коммутатора соединен с вторым ре- гистром, выход которого через преобразователь код-ток и выходное устройство соединен с выходом устройства, первые выходы блока управления соединены с управляющими входами, блока регулирования задержки, выход которого соединен с входом источника опорного тока, выход которого соединен с входом выходного устройства, выходы блока регулирования задержки соединены с третьим и четвертым входами блока управления, первые два входа которого соединены с входами устройства, а пятый вход соединен с выходом устройства и выходом цифровой схемы сравнения, входы которой соединены с выходами регистра сдвига, информационный вход которого соединен с выходом компаратора напряжения, соеди- . ненногос блоком выделения разности, вход которого соединён с выходом устройства, а управляющий вход блока выделения разности соединен с десятым выходом блока управления, седьмой и восьмой выходы

которого соединены с управляющими входами регистра сдвига.

При проведении патентного поиска по соответствующим литературным иеточникам были обнаружены аналогичные решения. Так, в цифроаналоговых преобразователях проблему асимметрии времен включения и выключения разрядов решают с помощью следующих средств:.

0 а) применение буферного регистра для управляющих сигналов(недостатком такого решения является его недостаточность для быстродействующих ЦАП с учетом наличия, как правило, различных времен включения

5- и выключения разрядов противоположной полярности (основных и знакового);

б) тщательная отработка конструкции устройства, правильный выбор элементов и конструктивная симметрия позволяют сни0 зить амплитуду переходных процессов. Однако на практике получить минимальную погрешность преобразования с помощью отработки конструкции достаточно сложно и дорого. Кроме того, полученные результа5 ты ухудшаются с течением времени и под воздействием температуры, В предлагаемом же устройстве введение режима контроля позволяет оптимизировать длительность задержки включения знаково0 го разряда, так как именно это переключение вызывает наибольший всплеск выходного сигнала, и повысить достоверность преобразования.

Причем такое решение уменьшения не5 линейных искажений, не требует применения особе тщательного согласования переходных характеристик аналоговых узлов. Таким образом, следует отметить, что вновь введенные блоки обладают сущест0 венными отличительными признаками, а заявляемое, устройство при этом соответствует критерию существенные отличия.

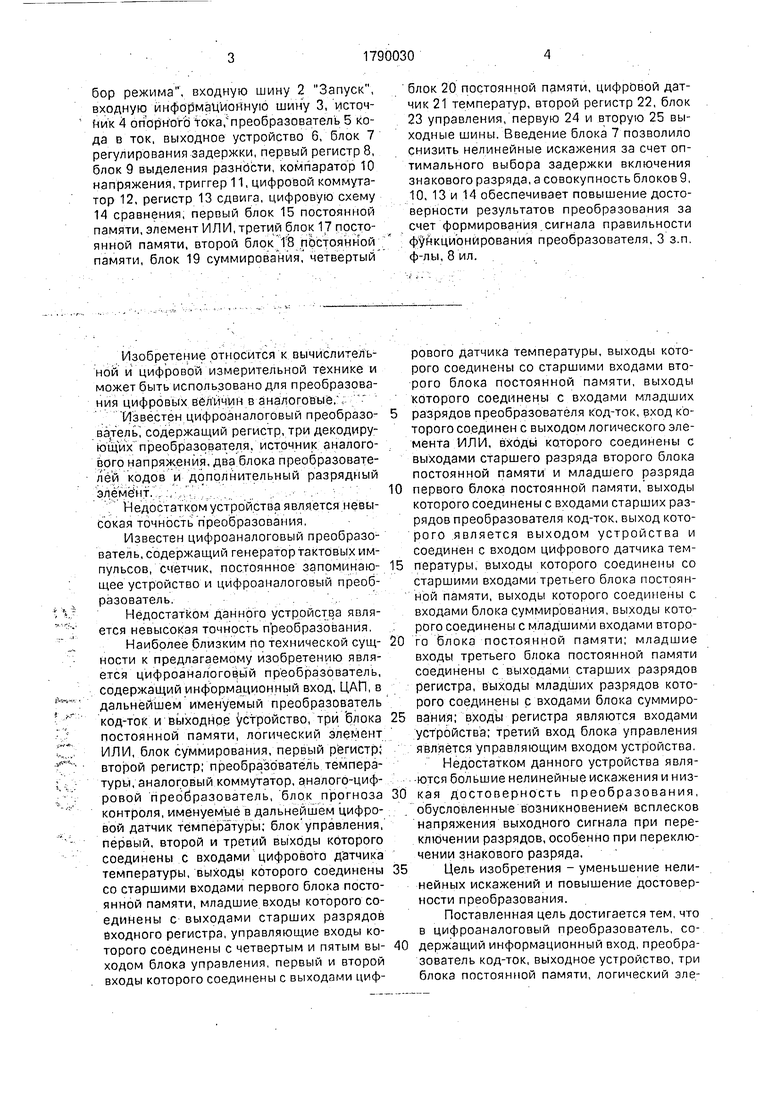

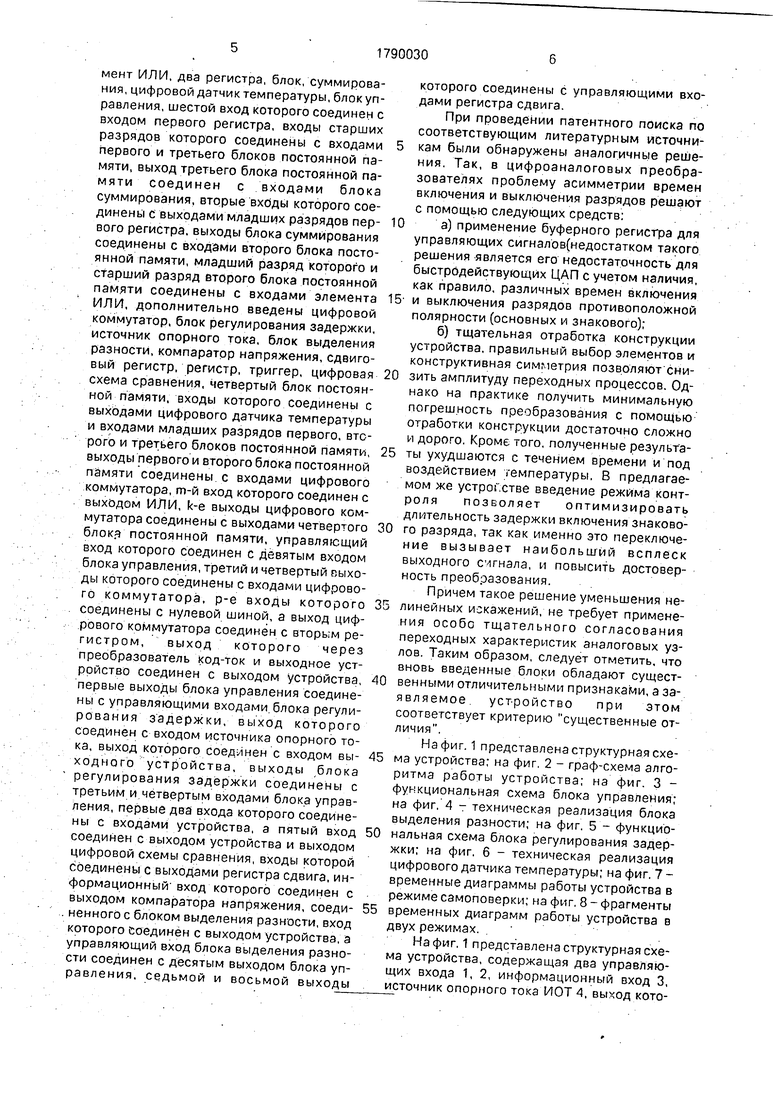

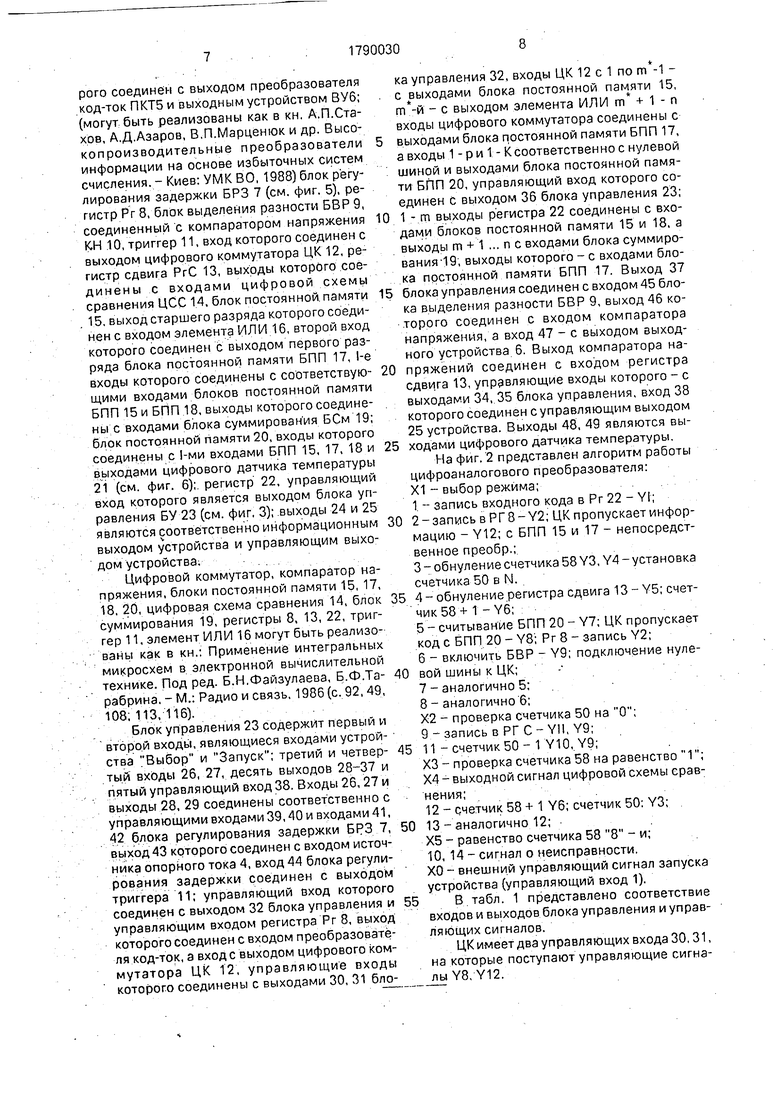

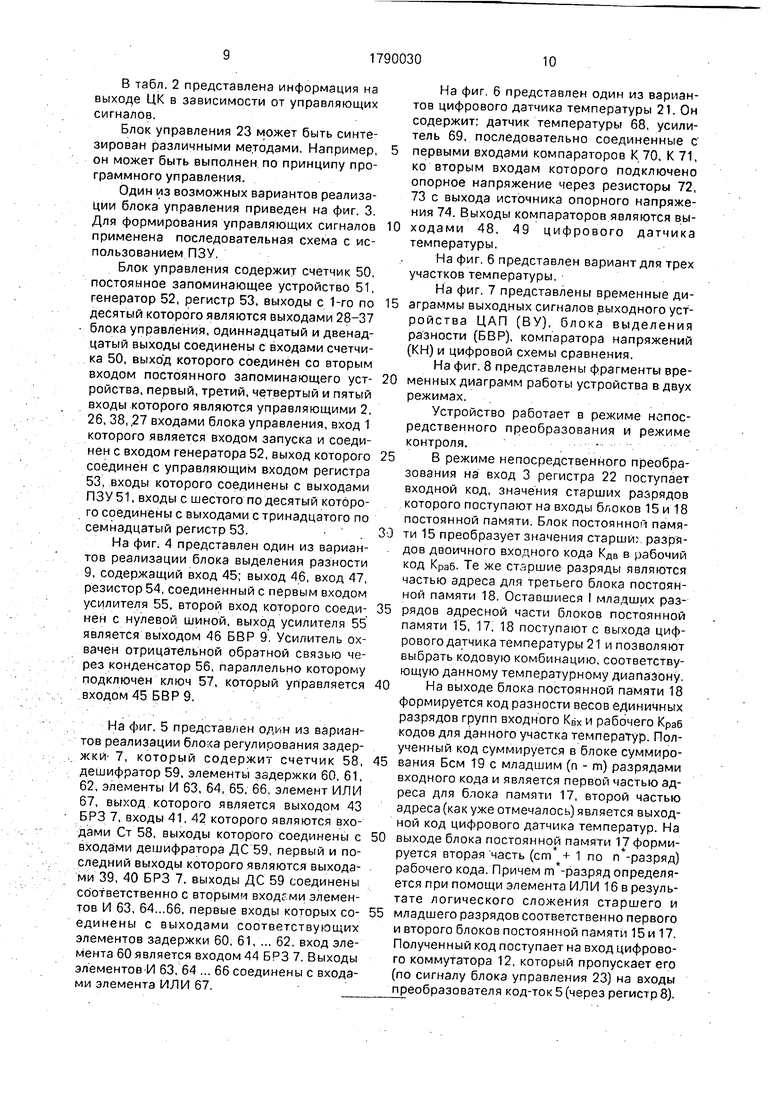

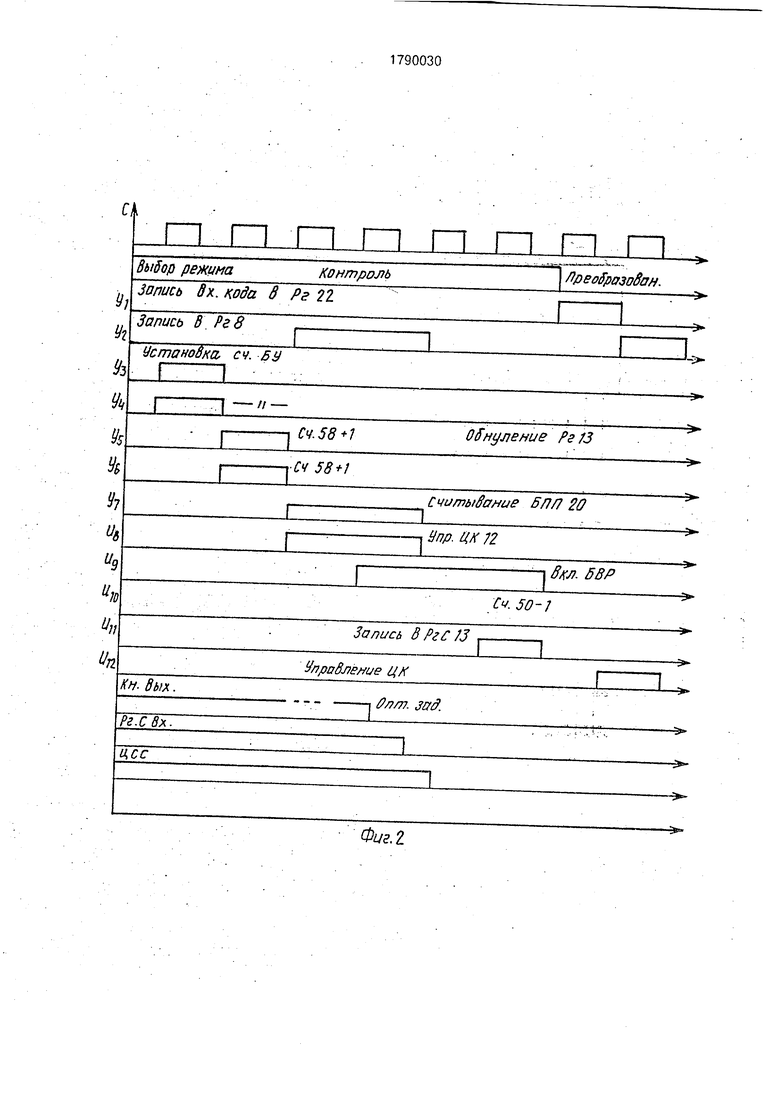

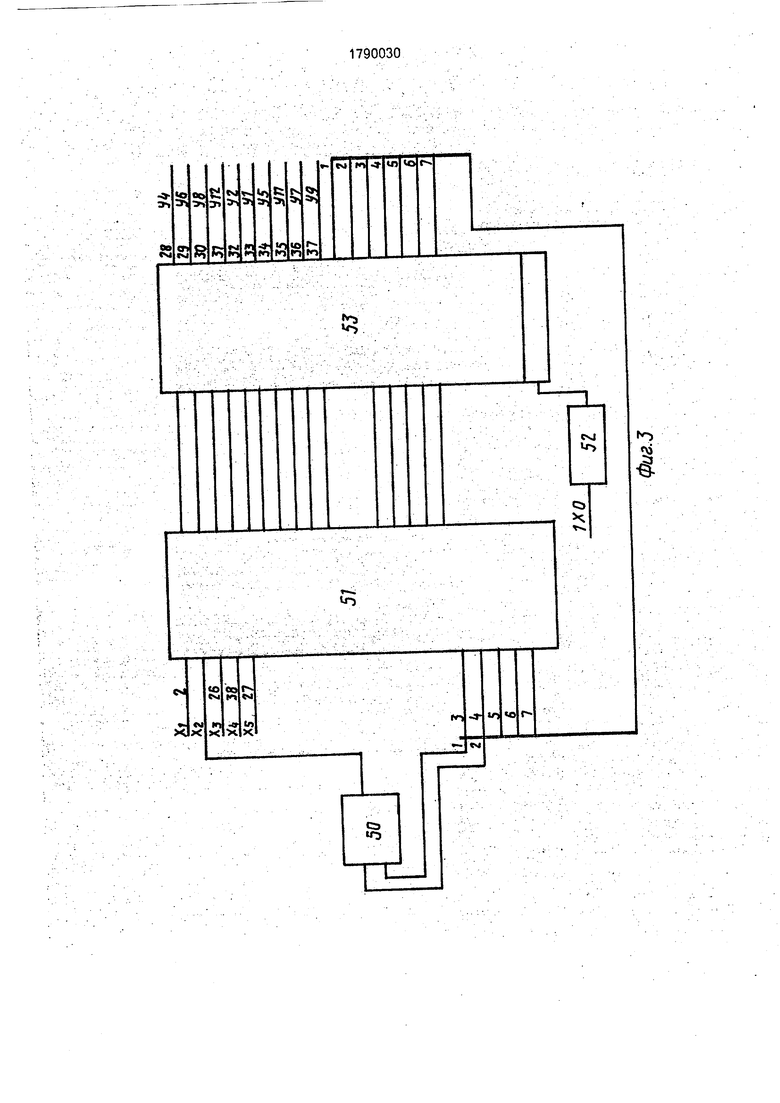

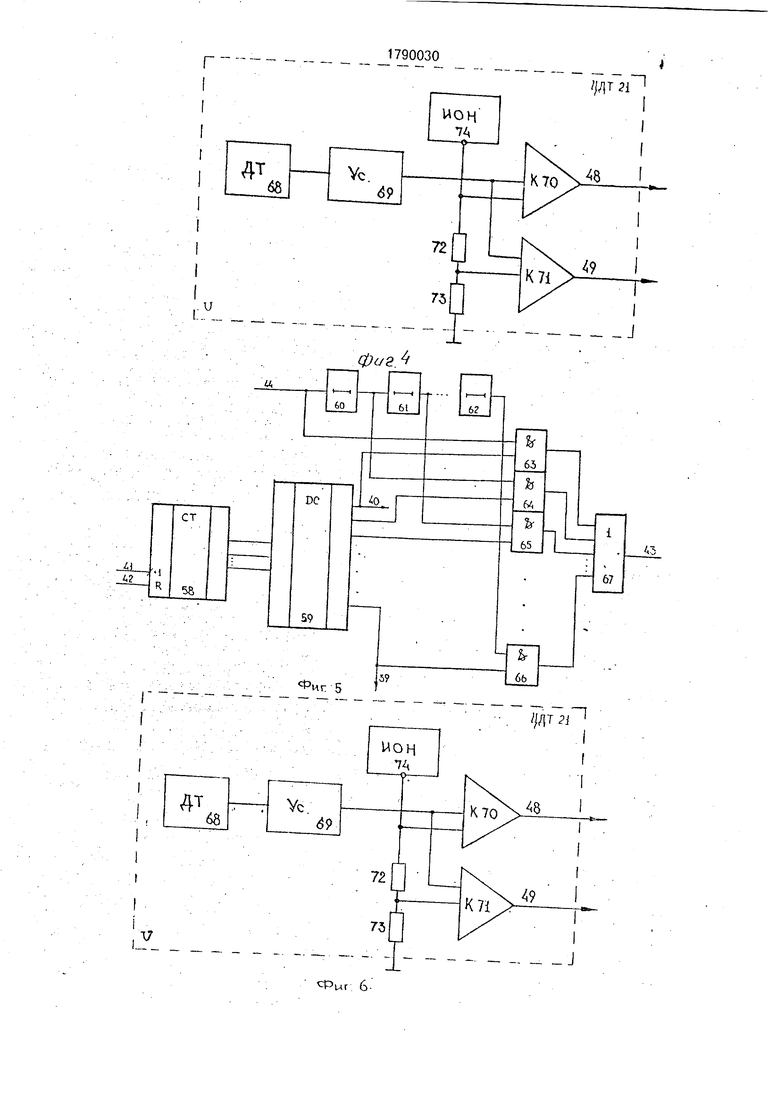

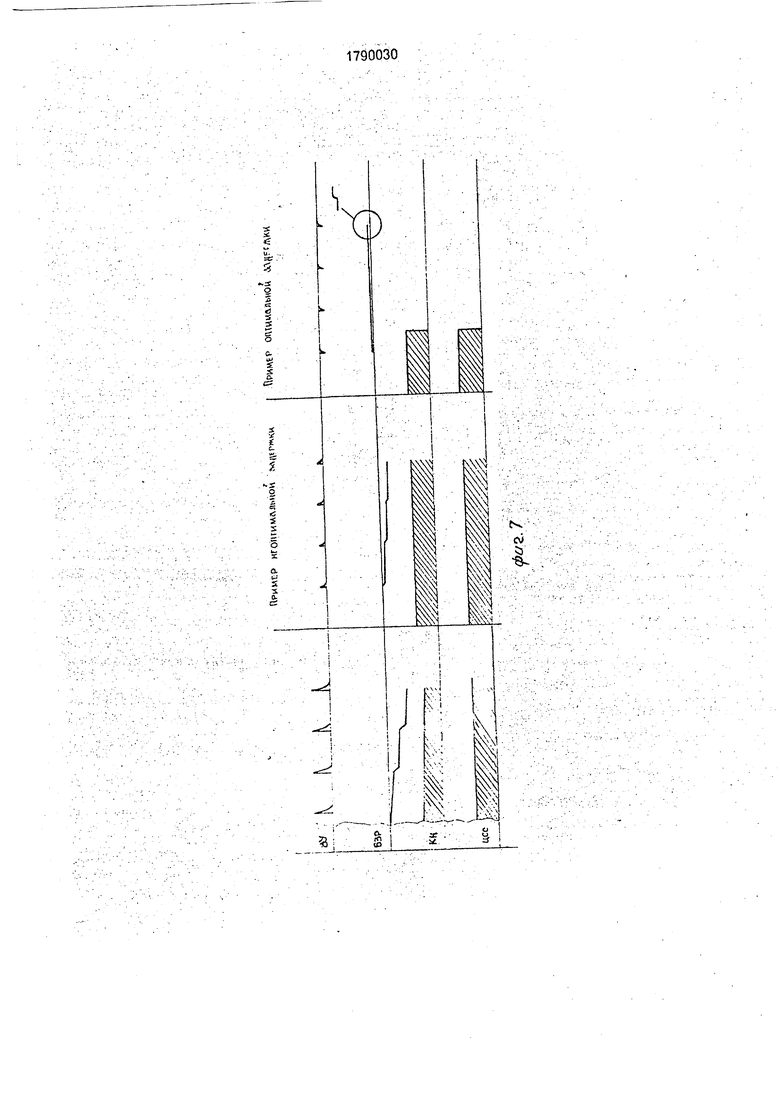

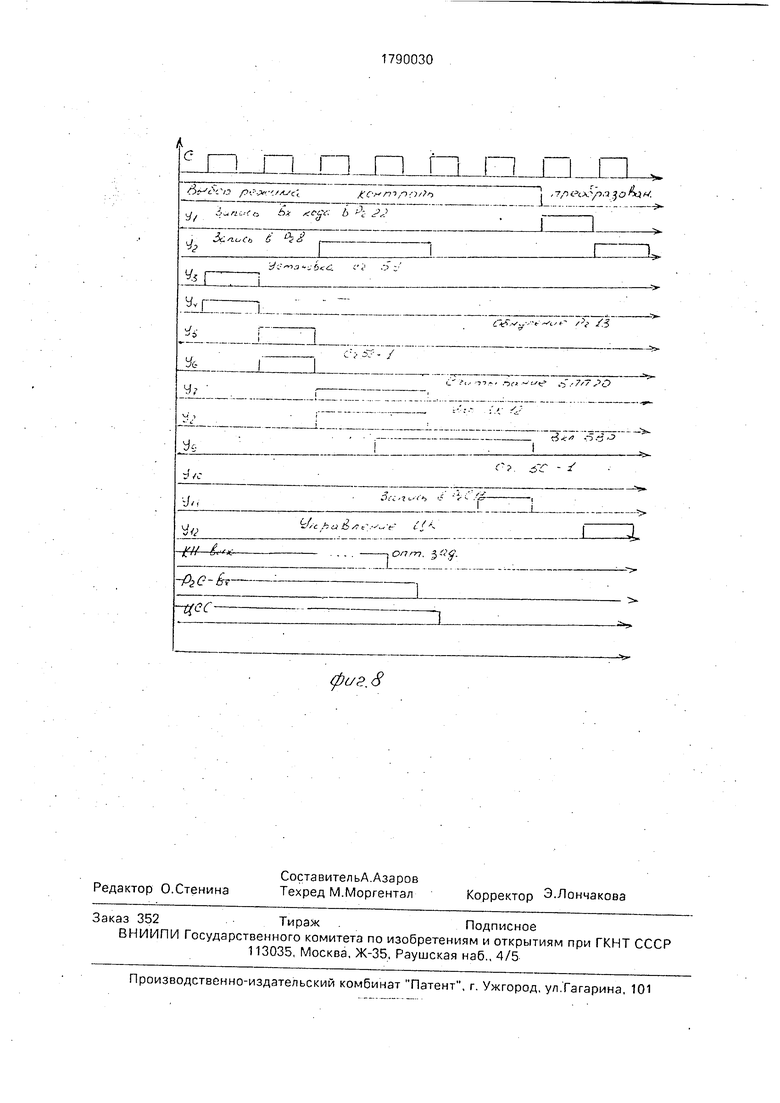

На фиг. 1 представлена структурная схе5 ма устройства; на фиг. 2 - граф-схема алгоритма работы устройства; на фиг. 3 - функциональная схема блока управления; на фиг, 4 - техническая реализация блока выделения разности; на фиг. 5 - функцио0 нальная схема блока регулирования задержки; на фиг, 6 - техническая реализация цифрового датчика температуры; на фиг. 7 - временные диаграммы работы устройства в режиме самоповерки; на фиг. 8 - фрагменты

5 временных диаграмм работы устройства в двух режимах. .

На фиг, 1 представлена структурная схема устройства, содержащая два управляющих входа 1, 2, информационный вход 3, источник опорного тока ЙОТ 4, выход которого соединен с выходом преобразователя код-ток ПКТ5 и выходным устройством ВУ6; (могут быть реализованы как в кн. А.П.Стахов, А.Д.Азаров, В.П.Марценюк и др. Высокопроизводительные преобразователи информации на основе избыточных систем счисления. - Киев: УМК ВО, 1988) блок регулирования задержки БРЗ 7 (см. фиг. 5), регистр Рг 8, блок выделения разности БВР 9, соединенный с компаратором напряжения К.Н .10, триггер 11, вход которого соединен с выходом цифрового коммутатора ЦК 12, регистр сдвига РгС 13, выходы которого соединены с входами цифровой схемы сравнения ЦСС 1.4, блок постоянной, памяти 15, выход старшего разряда которого соединен с входом элемента ИЛИ 16, второй вход которого соединен с выходом первого разряда блока постоянной памяти БПП 17, 1-е входы которого соединены с соответствующими входами блоков постоянной памяти БПП 15 и БПП 18, выходы которого соединены с входами блока суммирования БСм 19; блок постоянной памяти 20, входы которого соединены с l-ми входами БПП 15, 17, 18 и выходами цифрового датчика температуры 21 (см. фиг. 6);. регистр 22, управляющий вход которого является выходом блока управления БУ 23 (см. фиг, 3); .выходы 24 и 25 являются соответственно информационным выходом устройства и управляющим выходом устройства;

Цифровой коммутатор, компаратор напряжения, блоки постоянной памяти 15, 17, 18, 20, цифровая схема сравнения 14, блок суммирования 19, регистры 8, 13, 22, триггер 11, элемент ИЛИ 16 могут быть реализованы как в кн.: Применение интегральных микросхем в электронной вычислительной технике. Под ред. Б.Н.Файзулаева, Б.Ф.Та- рабрина. - М.: Радио и связь, 1986 (с. 92, 49, 108. 113, 116).

Блок управления 23 содержит первый и второй входы, являющиеся входами устройства Выбор и Запуск ; третий и четвертый входы 26, 27, десять выходов 28-37 и пятый управляющий вход 38. Входы 26,27 и выходы.28, 29 соединены соответственно с управляющими входами 39,40 и входами 41, 42 блока регулирования задержки БРЗ 7, выход 43 которого соединен с входом источника опорного тока 4, вход 44 блока регулирования задержки соединен с выходом триггера 11; управляющий вход которого соединен с выходом 32 блока управления и управляющим входом регистра Рг 8, выход которого соединен с входом преобразователя код-ток, а входе выходом цифрового коммутатора ЦК 12, управляющие входы которого соединены с выходами 30, 31 блока управления 32, входы ЦК 12 с 1 по m -1 . с выходами блока постоянной памяти 15,

- с выходом элемента ИЛИ т + 1 - п

входы цифрового коммутатора соединены с

выходами блока постоянной памяти БПП 17, а входы 1 -ри 1 - К соответствен но с нулевой шиной и выходами блока постоянной памяти БПП 20, управляющий вход которого соединен с выходом 36 блока управления 23;

0 1 -т выходы регистра 22 соединены с входами блоков постоянной памяти 15 и 18, а выходы m + 1 ...пс входами блока суммирования 19, выходы которого - с входами блока постоянной памяти БПП 17. Выход 37

5 блока управления соединен с входом 45 блока выделения разности БВР 9, выход 46 которого соединен с входом компаратора напряжения, а вход 47 - с выходом выходного устройства 6. Выход компаратора на0 пряжений соединен с входом регистра сдвига 13, управляющие входы которого - с выходами 34, 35 блока управления, вход 38 которого соединен суправляющим выходом 25 устройства. Выходы 48, 49 являются вы5 ходами цифрового датчика температуры.

На фиг. 2 представлен алгоритм работы цифроаналогового преобразователя: Х1 - выбор режима; 1. - запись входного кода в Рг 22 - YI;

0 2-запись вРГ8-У2; ЦК пропускает информацию - Y12; с БПП 15 и 17 - непосредственное преобр.;

3 - обнуление счетчика 58 Y3, Y4 - установка счетчика 50 в N.

5 4-обнуление регистра сдвига 13-Y5; счетчик 58 + T-Y6;

5 - считывание БПП 20 - Y7; ЦК пропускает коде БПП 20-Y8; Рг 8-запись Y2;

6 - включить БВР - Y9; подключение нуле- 0 вой шины к ЦК;-

7 - аналогично 5;

8 - аналогично 6;

Х2 - проверка счетчика 50 на

9-запись в РГС-Yll. Y9;

5 11 -счетчик 50- 1Y10..Y9;

ХЗ - проверка счетчика 58 на равенство Х4 - выходной сигнал цифровой схемы сравнения;12 - счетчик 58 + 1 Y6; счетчик 50: Y3;

0 13-аналогично 12;

Х5 - равенство счетчика 58 8 - и;

10,14 - сигнал о неисправности.

ХО - внешний управляющий сигнал запуска

устройства (управляющий вход 1),

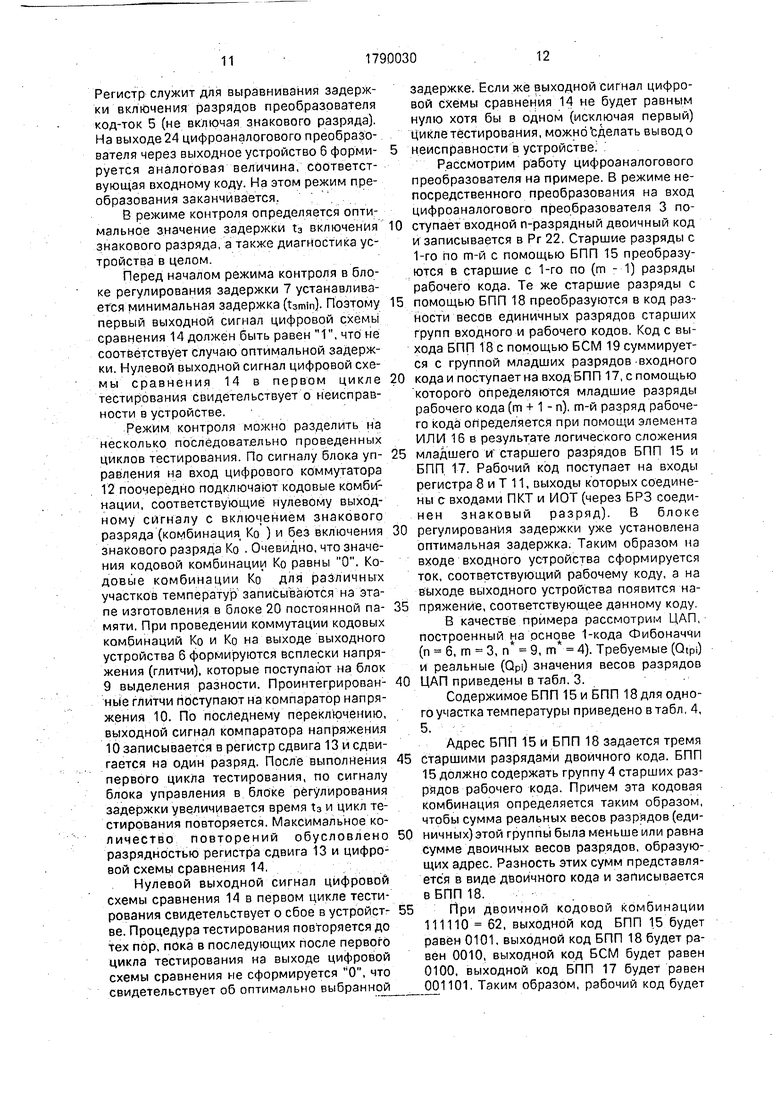

5 В.табл. 1 представлено соответствие входов и выходов блока управления и управляющих сигналов.

ЦК имеет два управляющих входа 30,31, на которые поступают управляющие сигналы Y8.Y12.

В табл. 2 представлена информация на выходе ЦК в зависимости от управляющих сигналов.

Блок управления 23 может быть синтезирован различными методами. Например, он может быть выполнен по принципу программного управления.

Один из возможных вариантов реализации блока управления приведен на фиг. 3. Для формирования управляющих сигналов применена последовательная схема с использованием ПЗУ.

Блок управления содержит счетчик 50, постоянное запоминающее устройство 51, генератор 52, регистр 53, выходы с 1-го по десятый которого являются выходами 28-37 блока управления, одиннадцатый и двенадцатый выходы соединены с входами счетчика 50, выход которого соединён со вторым входом постоянного запоминающего устройства, первый, третий, четвертый и пятый входы которого являются управляющими 2, 26, 38, .27 входами блока управления, вход 1 которого является входом запуска и соединен с входом генератора 52, выход которого соединен с управляющим входом регистра 53, входы которого соединены с выходами ПЗУ 51, входы с шестого по десятый которого соединены с выходами с тринадцатого по семнадцатый регистр 53.

На фиг. 4 представлен один из вариантов реализации блока выделения разности 9, содержащий вход 45; выход 46, вход 47, резистор 54, соединенный с первым входом усилителя 55, второй вход которого соединен с нулевой шиной, выход усилителя 55 является выходом 46 БВР 9. Усилитель охвачен отрицательной обратной связью через конденсатор 56, параллельно которому подключён ключ 57, который управляется входом 45 БВР 9.

На фиг. 5 представлен один из вариантов реализации блока регулирования задержки- 7, который содержит счетчик 58, дешифратор 59, элементы задержки 60, 61, 62, элементы И 63, 64, 65, 66, элемент ИЛИ 67, выход которого является выходом 43 БРЗ 7, входы 41, 42 которого являются входами Ст 58, выходы которого соединены с входами дешифратора ДС 59, первый и последний выходы которого являются выходами 39, 40 БРЗ 7. выходы ДС 59 соединены соответственно с вторыми входами элементов И 63, 64...66. первые входы которых соединены с выходами соответствующих элементов задержки 60, 61, ... 62, вход элемента 60 является входом 44 БРЗ 7. Выходы элементов И 63, 64 ... 66 соединены с входами элемента ИЛИ 67.

На фиг. б представлен один из вариантов цифрового датчика температуры 21. Он содержит: датчик температуры 68, усилитель 69, последовательно соединенные с 5 первыми входами компараторов К 70, К 71, ко вторым входам которого подключено опорное напряжение через резисторы 72, 73 с выхода источника опорного напряжения 74. Выходы компараторов являются вы0 ходами 48. 49 цифрового датчика температуры.

На фиг. 6 представлен вариант для трех участков температуры.

На фиг. 7 представлены временные ди5 аграммы выходных сигналов выходного устройства ЦАП (ВУ), блока выделения разности (БВР), компаратора напряжений (КН) и цифровой схемы сравнения.

На фиг. 8 представлены фрагменты вре0 менных диаграмм работы устройства в двух режимах.

Устройство работает в режиме непосредственного преобразования и режиме контроля,5 В режиме непосредственного преобразования на вход 3 регистра 22 поступает входной код, значения старших разрядов которого поступают на входы блоков 15 и 18 постоянной памяти. Блок постоянной памя0 ти 15 преобразует значения старшй; разря- . дов двоичного входного кода Кдв в рабочий код Краб. Те же старшие разряды являются частью адреса для третьего блока постоянной памяти 18. Оставшиеся I младших раз5 рядов адресной части блоков постоянной памяти 15, 17, 18 поступают с выхода цифрового датчика температуры 21 и позволяют выбрать кодовую комбинацию, соответствующую данному температурному диапазону.

0 На выходе блока постоянной памяти 18 формируется код разности весов единичных разрядов групп входного КвХ и рабочего Краб кодов для данного участка температур. Полученный код суммируется в блоке суммиро5 вания Бсм 19 с младшим (п - гл) разрядами входного кода и является первой частью адреса для блока памяти 17, второй частью адреса (как уже отмечалось) является выходной код цифрового датчика температур. На

0 выходе блока постоянной памяти 17 формируется вторая часть (cm + 1 по п -разряд) рабочего кода. Причем m -разряд определяется при помощи элемента ИЛИ 16 в результате логического сложения старшего и

5 младшего разрядов соответственно первого и второго блоков постоянной памяти 15 и 17. Полученный код поступает на вход цифрового коммутатора 12, который пропускает его (по сигналу блока управления 23) на входы преобразователя код-ток 5 (через регистр 8).

Регистр служит для выравнивания задержки включения разрядов преобразователя код-ток 5 (не включая знакового разряда). На выходе 24 цифроаналогового преобразователя через выходное устройство 6 формируется аналоговая величина, соответствующая входному коду. На этом режим преобразования заканчивается. : .

В режиме контроля определяется оптимальное значение задержки Тз включения знакового разряда, а также диагностика устройства в целом.

Перед началом режима контроля в блоке регулирования задержки 7 устанавливается минимальная задержка (t3min). Поэтому первый выходной сигнал цифровой схемы сравнения 14 должен быть равен 1, что не соответствует случаю оптимальной задержки. Нулевой выходной сигнал цифровой схе- мы сравнения 14 в первом цикле тестирования свидетельствует о неисправности в устройстве.

Режим контроля можно разделить на несколько последовательно проведенных циклов тестирования. По сигналу блока управления на вход цифрового коммутатора 12 поочередно подключают кодовые комби нации, соответствующие нулевому выходному сигналу с включением знакового разряда (комбинация Ко ) и без включения знакового разряда Ко . Очевидно, что значения кодовой комбинации Ко равны О. Кодовые комбинации Ко для различных участков температур записываются на этапе изготовления в блоке 20 постоянной памяти. При проведении коммутации кодовых комбинаций Ко и Ко на выходе выходного устройства б формируются всплески напряжения (глитчи), которые поступают на блок

9 выделения разности. Проинтегрированные глитчи поступают на компаратор напряжения 10. По последнему переключению, выходной сигнал компаратора напряжения

10 записывается в регистр сдвига 13 и сдвигается на один разряд. После выполнения первого цикла тестирования, по сигналу блока управления в блоке регулирования задержки увеличивается время t3 и цикл тестирования повторяется. Максимальное количество повторений обусловлено разрядностью регистра сдвига 13 и цифровой схемы сравнения 14.

Нулевой выходной сигнал цифровой схемы сравнения 14 в первом цикле тестирования свидетельствует о сбое в устройстве. Процедура тестирования повторяется до тех пор, пока в последующих после первого цикла тестирования на выходе цифровой схемы сравнения не сформируется О, что свидетельствует об оптимально выбранной

задержке. Если же выходной сигнал цифровой схемы сравнения 14 не будет равным нулю хотя бы в одном (исключая первый) Цикле тестирования, можно сделать вывод о

неисправности в устройстве

Рассмотрим работу цифроаналогового преобразователя на примере. В режиме непосредственного преобразования на вход цифроаналогового преобразователя 3 по0 ступает входной п-разрядный двоичный код и записывается в Рг 22. Старшие разряды с 1-го по m-й с помощью БПП 15 преобразуются в старшие с 1-го по (т - 1) разряды рабочего кода. Те же старшие разряды с

5 помощью БПП 18 преобразуются в код разности весов единичных разрядов старших групп входного и рабочего кодов. Код с выхода БПП 18с помощью БСМ 19 суммируется с группой младших разрядов Входного

0 кода и поступает на вход БПП 17, с помощью которого определяются младшие разряды рабочего кода (т + 1 - п). т-й разряд рабочего кода определяется при помощи элемента ИЛИ 16 в результате логического сложения

5 младшего и старшего разрядов БПП 15 и БПП 17. Рабочий код поступает на входы регистра 8 и Т 11, выходы которых соединены с входами ПКТ и ЙОТ (через БРЗ соединен знаковый разряд). В блоке

0 регулирования задержки уже установлена оптимальная задержка. Таким образом на входе входного устройства сформируется ток, соответствующий рабочему коду, а на выходе выходного устройства появится на5 пряжение, соответствующее данному коду.

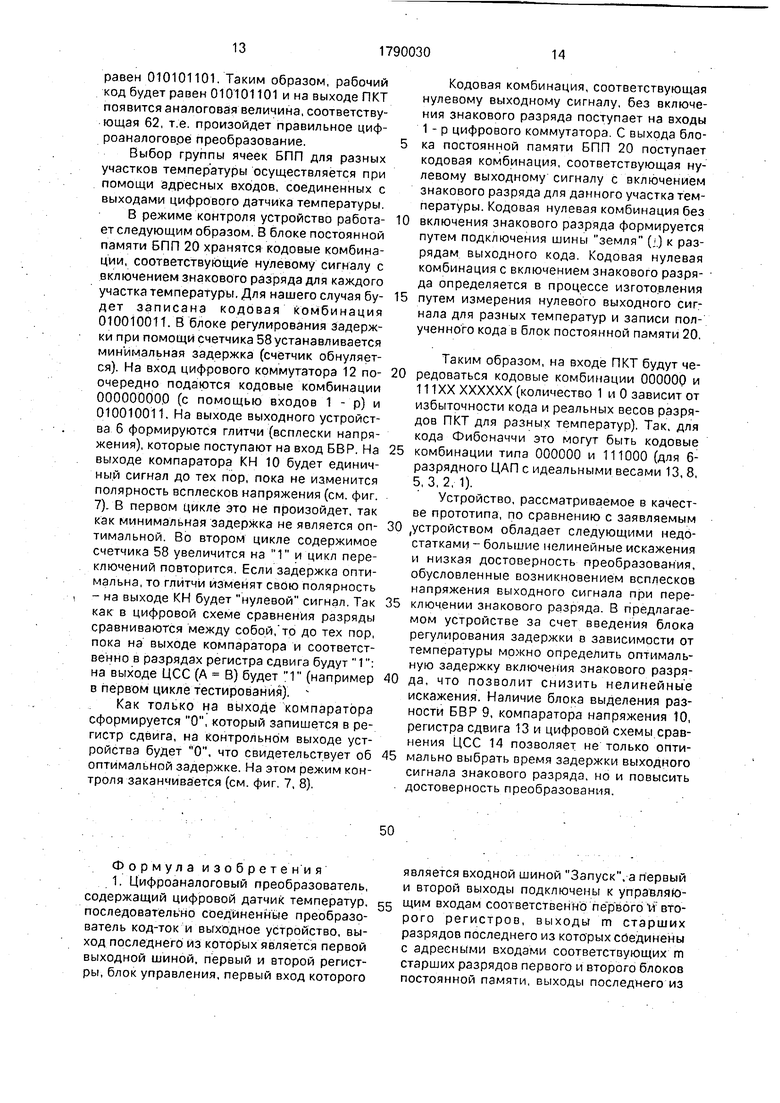

В качестве примера рассмотрим ЦАП,

построенный на основе 1-кода Фибоначчи

(п 6, m 3, п 9, т 4). Требуемые (Qtpi)

и реальные (Qpi) значения весов разрядов

0 ЦАП приведены в табл. 3.

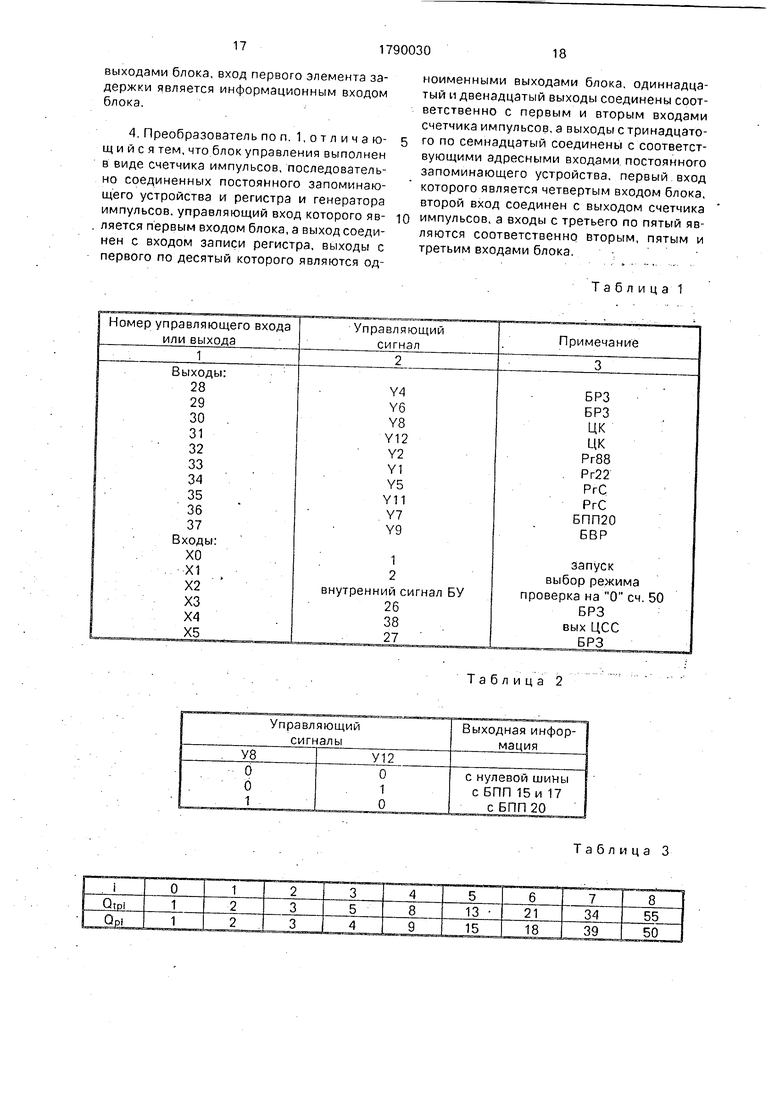

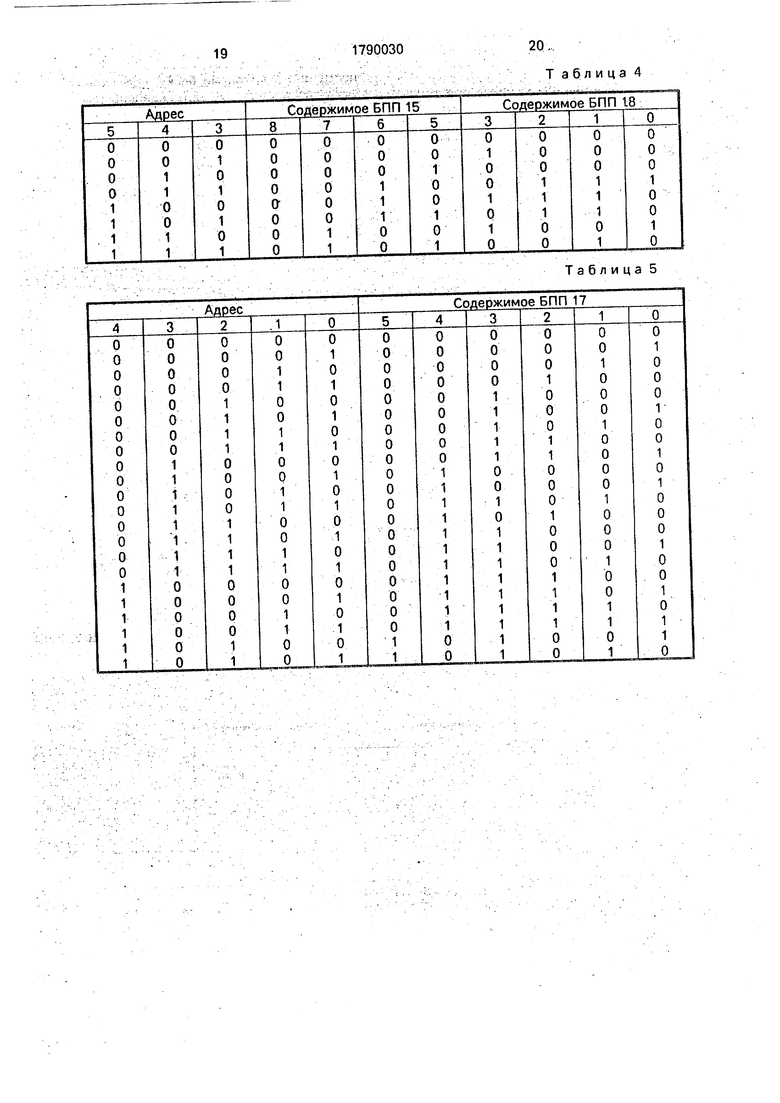

Содержимое БПП 15 и БПП 18 для одного участка температуры приведено втабл, 4, 5. -;-; .

Адрес БПП 15 и БПП 18 задается тремя

5 старшими разрядами двоичного кода. БПП 15 должно содержать группу 4 старших разрядов рабочего кода. Причем эта кодовая комбинация определяется таким образом, чтобы сумма реальных весов разрядов (еди0 ничных) этой группы была меньше или равна сумме двоичных весов разрядов, образующих адрес. Разность этих сумм представляется в виде двоичного кода и записывается в БПП 18.

5 При двоичной кодовой комбинации 111110 62, выходной код БПП 15 будет равен 0101, выходной код БПП 18 будет равен 0010, выходной код БСМ будет равен 0100, выходной код БПП 17 будет равен 001101. Таким образом, рабочий код будет

равен 010101101. Таким образом, рабочий код будет равен 010101101 и на выходе ПКТ появится аналоговая величина, соответствующая 62, т.е. произойдет правильное циф- роаналоговрё преобразование.

Выбор группы ячеек БПП для разных участков температуры осуществляется при помощи адресных входов, соединенных с выходами цифрового датчика температуры.

В режиме контроля устройство работает следующим образом. В блоке постоянной памяти БПП 20 хранятся кодовые комбинации, соответствующие нулевому сигналу с включением знакового разряда для каждого участка температуры. Для нашего случая будет записана кодовая комбинация 010010011. В блоке регулирования задержки при помощи счетчика 58 устанавливается минимальная задержка (счётчик обнуляется). На вход цифрового коммутатора 12 поочередно подаются кодовые комбинации 000000000 (с помощью входов 1 - р) и 010010011. На выходе выходного устройства б формируются глитчи (всплески напряжения), которые поступают на вход БВР. На выходе компаратора КН 10 будет единичный сигнал до тех пор, пока не изменится полярность всплесков напряжения (см. фиг. 7)/В первом цикле это не произойдет, так как минимальная задержка не является оптимальной. Во втором цикле содержимое счетчика 58 увеличится на 1 и цикл переключений повторится. Если задержка оптимальна, то глйтчй изменят свою полярность - на выходе КН будет нулевой сигнал. Так как в цифровой схеме сравнения разряды сравниваются между собой, то до тех пор, пока на выходе компаратора и соответственно в разрядах регистра сдвига будут на выходе ЦСС (А В) будет 1 (например в первом цикле тестирования). Как только на выходе компаратора сформируется О, который запишется в регистр сдвига, на контрольном выходе устройства будет О, что свидетельствует об оптимальной задержке. На этом режим контроля заканчивается (см. фиг, 7, 8).

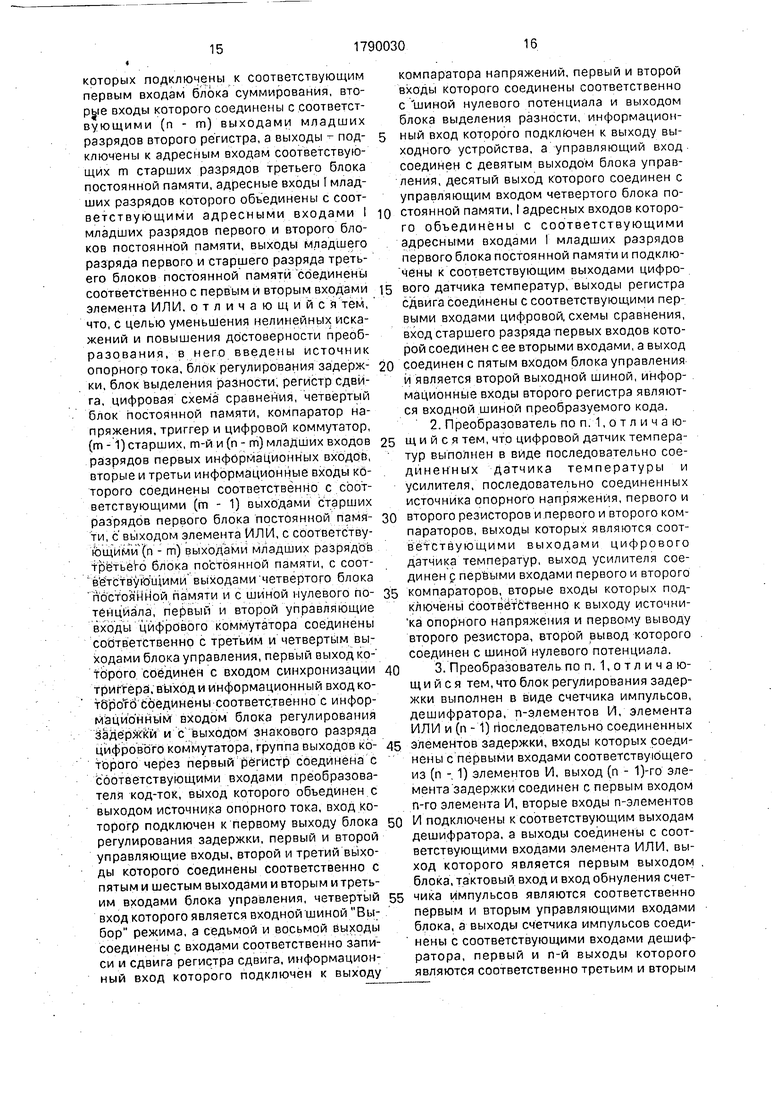

Формула изобретения 1. Цифроаналоговый преобразователь, содержащий цифровой датчик температур, последовательно соединенные преобразователь код-ток и выходное устройство, выход последнего из которых является первой выходной шиной, первый и второй регистры, блок управления, первый вход которого

Кодовая комбинация, соответствующая нулевому выходному сигналу, без включения знакового разряда поступает на входы 1 - р цифрового коммутатора. С выхода блока постоянной памяти БПП 20 поступает кодовая комбинация, соответствующая нулевому выходному сигналу с включением знакового разряда для данного участка температуры. Кодовая нулевая комбинация без

включения знакового разряда формируется путем подключения шины земля (j.) к разрядам выходного кода. Кодовая нулевая комбинация с включением знакового разряда определяется в процессе изготовления

путем измерения нулевого выходного сигнала для разных температур и записи полученного кода в блок постоянной памяти 20.

Таким образом, на входе ПКТ будут чередоваться кодовые комбинации 000000 и 111ХХ ХХХХХХ (количество 1 и 0 зависит от избыточности кода и реальных весов разрядов ПКТ для разных температур). Так, для кода Фибоначчи это могут быть кодовые

комбинации типа 000000 и 111000 (для 6- разрядного ЦАП с идеальными весами 13, 8, 5,3,2,1).

Устройство, рассматриваемое в качестве прототипа, по сравнению с заявляемым

устройством обладает следующими недостатками - большие нелинейные искажения и низкая достоверность преобразования, обусловленные возникновением всплесков напряжения выходного сигнала при переключении знакового разряда. В предлагаемом устройстве за счет введения блока регулирования задержки в зависимости от температуры можно определить оптимальную задержку включения знакового разряда, что позволит снизить нелинейные искажения. Наличие блока выделения разности БВР 9, компаратора напряжения 10, регистра сдвига 13 и цифровой схемы сравнения ЦСС 14 позволяет не только оптимально выбрать оремя задержки выходного сигнала знакового разряда, но и повысить достоверность преобразования.

является входной шиной Запуск, а первый и второй выходы подключены к управляю- щим входам соответственно первого W второго регистров, выходы m старших разрядов последнего из которых соединены с адресными входами соответствующих m старших разрядов первого и второго блоков постоянной памяти, выходы последнего из

которых подключены к соответствующим первым входам блока суммирования, вторые входы которого соединены с соответствующими (п - т) выходами младших разрядов второго регистра, а выходы - подключены к адресным входам соответствующих m старших разрядов третьего блока постоянной памяти, адресные входы I младших разрядов которого объединены с соответствующими адресными входами I младших разрядов первого и второго блоков постоянной памяти, выходы младшего разряда первого и старшего разряда третьего блоков постоянной памяти соединены соответственно с первым и вторым входами элемента ИЛИ, отличающий с я тем, что, с целью уменьшения нелинейных искажений и повышения достоверности преобразования, в него введены источник опорного тока, блок регулирования задержки, блок выделения разности; регистр сдвига, цифровая схема сравнения, четвертый блок постоянной памяти, компаратор напряжения, триггер и цифровой коммутатор, (т -1) старших, m-й и (п - т) младших входов разрядов первых информационных входов, вторые и третьи информационные входы которого соединены соответственно с соответствующими (т - 1) выходами старших разрядов первого блока постоянной памяти, с выходом элемента ИЛИ, с соответствующими (п - т) выходами младших разрядов третьего блока постоянной памяти, с соот- 1 в ётствугогцими выходами четвертого блока по стЪя н йой памяти и с шиной нулевого потенциала, первый и второй управляющие входы цифрового коммутатора соединены соответственно с третьим и четвертым выходами блока управления, первый выход которого соединен с входом синхронизации триггера , выходи информационный вход ко- тб рогб соединены соответственно с информационным входом блока регулирования Зад е рж кй и с выходом знакового разряда цифрового коммутатора, группа выходов которого через первый регистр соединена с соответствующими входами преобразователя код-ток, выход которого объединен с выходом источника опорного тока, вход ко- торогр подключен к первому выходу блока регулирования задержки, первый и второй управляющие входы, второй и третий выходы которого соединены соответственно с пятым и шестым выходами и вторым и третьим входами блока управления, четвертый вход которого является входной шиной Вы; бор режима, а седьмой и восьмой выходы соединены с входами соответственно записи и сдвига регистра сдвига, информационный вход которого подключен к выходу

компаратора напряжений, первый и второй входы которого соединены соответственно с шиной нулевого потенциала и выходом блока выделения разности, информационный вход которого подключен к выходу выходного-устройства, а управляющий вход соединен с девятым выходом блока управления, десятый выход которого соединен с управляющим входом четвертого блока по0 стоянной памяти, I адресных входов которого объединены с соответствующими адресными входами Г младших разрядов первого блока постоянной памяти и подключены к соответствующим выходами цифро5 вого датчика температур, выходы регистра сдвига соединены с соответствующими первыми входами цифровой, схемы сравнения, вход старшего разряда первых входов которой соединен с ее вторыми входами, а выход

0 соединен с пятым входом блока управления и является второй выходной шиной, информационные входы второго регистра являются входной шиной преобразуемого кода. 2. Преобразователь по п. 1, о т л и ч а ю5 щ и и с я тем, что цифровой датчик темпера- тур выполнен в виде последовательно соединенных датчика температуры и усилителя, последовательно соединенных источника опорного напряжения, первого и

0 второго резисторов и.первого и второго компараторов, выходы которых являются соответствующими выходами цифрового датчика температур, выход усилителя соединен р первыми входами первого и второго

5 компараторов, вторые входы которых подключены соответственно к выходу источни- ка опорного напряжения и первому выводу второго резистора, второй вывод которого соединен с шиной нулевого потенциала.

0 3. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок регулирования задержки выполнен в виде счетчика импульсов, дешифратора, n-элементов И, элемента ИЛИ и (п -1) Последовательно соединенных

5 элементов задержки, входы которых соединены с первыми входами соответствующего из (п -. 1) элементов И, выход (п - 1)-го элемента задержки соединен с первым входом n-го элемента И, вторые входы п-элементов

0 И подключены к соответствующим выходам дешифратора, а выходы соединены с соответствующими входами элемента ИЛИ, выход которого является первым выходом блока, тактовый вход и вход обнуления счет5 чика импульсов являются соответственно первым и вторым управляющими входами блока, а выходы счетчика импульсов соединены с соответствующими входами дешифратора, первый и n-й выходы которого являются соответственно третьим и вторым

выходами блока, вход первого элемента задержки является информационным входом блока.

поименными выходами блока, одиннадцатый и двенадцатый выходы соединены соответственно с первым и вторым входами счетчика импульсов, а выходы с тринадцатого по семнадцатый соединены с соответствующими адресными входами постоянного запоминающего устройства, первый вход которого является четвертым входом блока, второй вход соединен с выходом счетчика импульсов, а входы с третьего по пятый являются соответственно вторым, пятым и третьим входами блока.

Таблица 1

Таблица 2

Таблица 3

Т а блица 4

Таблица 5

Выбор режима

Контроль

Запись дх. кода 8 Pa 22

Запись В. Рг8

Установка, сч. БУ

1

1

// -

Сч.58+1

Сч 58+1

ис

И

№

//,

//

Управление ЦК

Кн. 0М.

Рг.Свх.

Лрео$разо$ан.

Од нуление /J

Считы8аше БЛ/7 20

1

У пр. UK 12

5ВР

Сч. 50-1

Запись ВРгЈ 73

0л/п. зад.

Фиг. 1

«

«s

S% Г tTj

й

Ю

(О

CS1

е

i

м

(п

см

к

иэ

Ч

CSJ

ir

I

«о

С

m

JZ.

p-f-

Jf

(t t cffi b fЈCfrT pO/)

6 °гЈ

У,-Г

и.. -ч

L

y,://,

j

12

t// с hi) .-- t / - ---- .... ----i . 3- VЧ%С-&г

фиг.8

7/ CJ4xy3.4.J;P

/W.

-..

fif.-s..- г /5

С ,.. .-71.Л Л.ч .-we ъ.-7 f JO : .-Л ; . --

-с -5--3 -5

...

Гг. Г - /

За {.( / f --.ff-----,

........ ..... . -

| Гнатек Ю.Р | |||

| Справочник по цифроана- логовым и аналого-цифровым преобразователям, - М.: Радио и связь, 1982 | |||

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-01-23—Публикация

1990-05-03—Подача