I

Изобретение относится к области электротехники и может быть использовано в системах управления и регулирования вентильными преобразователями.

Известно устройство управления тиристорным регулятором напряжения, содержащее генератор импульсов, двоичный счетчик и устройство формирования управляющих импульсов flJ.

Недостатком этого устройства является низкая точность регулирования.

Наиболее близким к изобретению по технической сущности является устройство управления тиристорными регуляторами, которое содержит генератор импульсов, синхронизатор, запоминающее устройство, устройство записи, двоичный п-разрядный счетчик, распределитель импульсов, схему сравнения кодов, элементы И, ИЛИ и формирователи управляющих импульсов 23.

Недостатком устройства является невысокая точность..

Целью изобретения является повышение точности.,

Цель достигается тем, что предлагаемое устройство снабжено инвертором, причем вход двоичного п-разрядного счетчика соединен с выходом блока выбора режима, его выходы соединены с входами промежуточного

10 распределителя, вход инвертора подключен к выходу (п+1)- го разряда запоминающего блока и, к BTopo iy входу двухвходового элемента И, выход инвертора соединен с третьим

15 входом трехвходового элемента И.

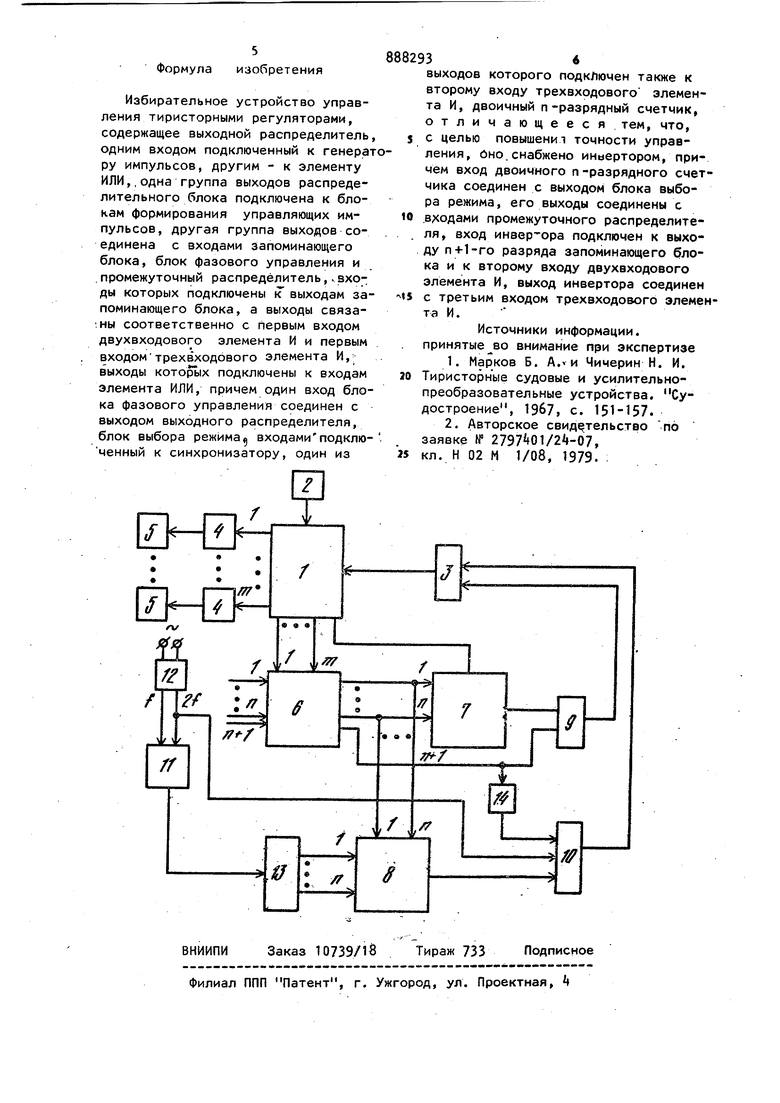

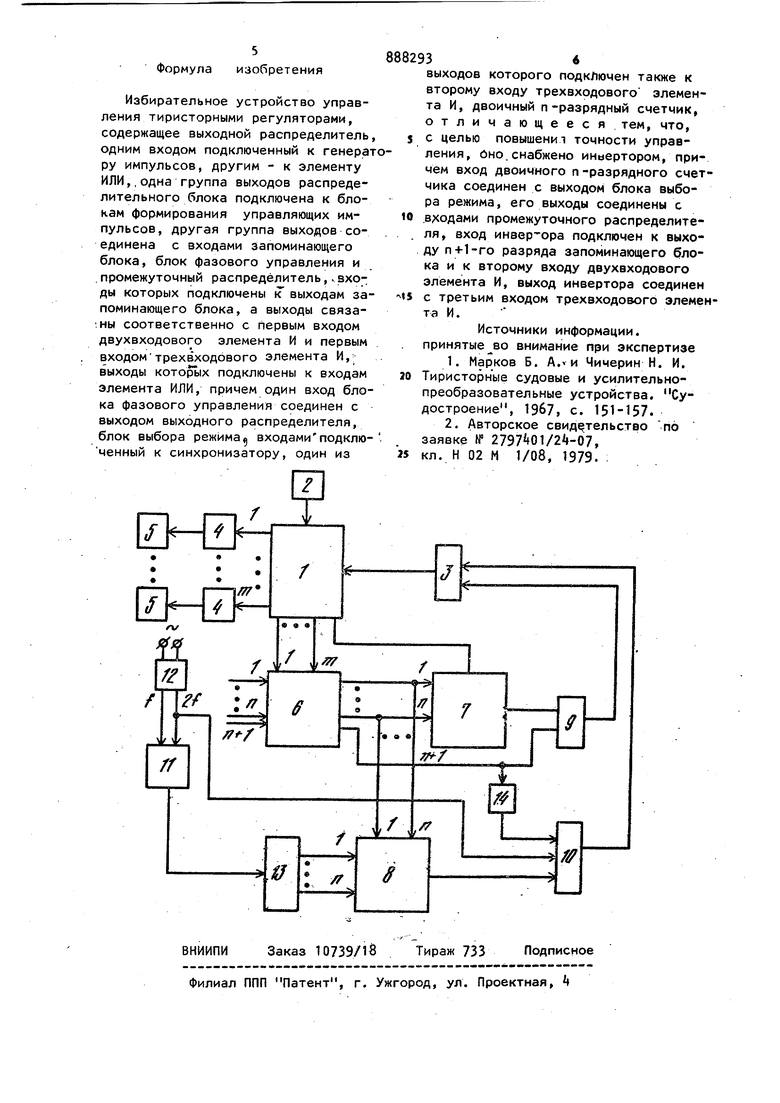

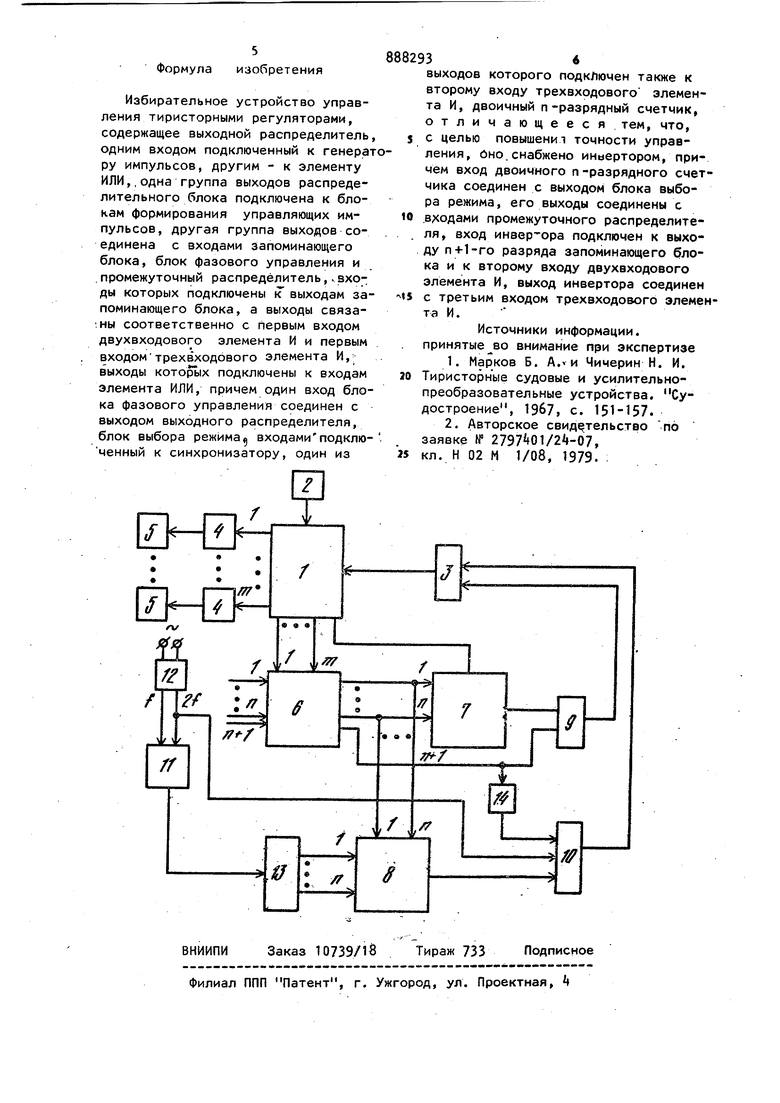

На чертеже показана блок-схема избирательного устройства для управления тиристорными регуляторами.

Устройство состоит из выходного

30 распределителя 1, к одному из входов которого подключен генератор импульсов 2, а к другому выход эле(Мента ИЛИ 3, при этом одна группа n выходов распределителя 1 через блоки формирования управляющих импульсов связана с тиристорными регуляторами 5, а другая группа соединена с входами запоминающего блока 6, Блок фазового управления 7 и промежуточный распределитель .8 своими входами параллельно подключены к n выходным разрядам запоминающего блока 6, а их выходы связаны соответственно с двухвходовым элементом И 9 и трехвходовым элементом И 10, выходы которых подключены к входам элемента ИЛИ 3. Блок 7 также связан одним входом с выходом распределителя 1. Блок выбора режима 11 подключен к синхронизатору 12, одним из выходов которого также связан с входом трехвходового элемента И 10, а его выход соединен с двоичным n-разрядным счетчиком 13, выходы которого подключены к распределителю 8 n информационных входов, и (п+1)-й вход . запоминающего блока подключены к выходному регистру управляющей -вычислительной машины, а его (п+1)-й выход соединен с входом двухвходового элемента И 9 и входом инвертора 1, выход которого подсоединен к входу элемента И 10. Избирательное устройство управления тиристорными регуляторами работает следующим образом. Обновление записи n-разрядных ин формационных кодов по адресам каналов, поступающих на входы запоминаю щего блока 6 от управляющей вычисли тельной машины, производится с пери одом , кратным (2 -Т) , где Т - период напряжения сети, В (пн-1)- и разряд по каждому адресу записываются свои коды режимов работы тиристорных рег ляторов (фазовый или распределитель ный), обновление которых инициирует ся во времени программой машины в зависимости от реализируемых програ зон испытываемого изделия. Распределитель 1, тактируемый стабилизированным генератором импульсов 2, осуществляет последовательную выбор ку кодов по адресам каналов, синхро низирует адрес кода ЗУ с номером канала управления и тактирует блок фазового управления 7 частотой 25,5 к Блоки фазового управления 7 и распределитель 8 работают каждый в 34 своем режиме. Блок фазового управления 7 вырабатывает выходной сигнал в случае совпадения по какомулибо адресу кодов ЗУ и кода, соот.ветствующего накопленному к этому моменту времени тактирующих импульсов. Распределитель о 8 в зависимости от установленного в блоке 11 режима реализует однополупериод-; ное либо двухпблупериодное распределенное управление. Двоичный празрядный счетчик 13 работает как делитель частоты синхроимпульсов, вырабатываемых синхронизатором 12 на базе промышленной частоты, и сигнал его каждого 1-го разряда стрббируется сигналом (п+1) i-ro разряда блоков, причем за время длительности одного синхроимпульса происходит последовательное стробироваНие текущего кода двоичного счетчика всеми кодами ЗУ. В результате этого формируется по каждому каналу на временном интервале обновления информации в блоке 6 выходной сигнал блока распределенного управления. Выходные сигналы блоков фазового и распределенного управления поступают на входы соответственно двухвходового 9 и трехвходового 10 элементов И. На элемент 10 подаются также синхроимпульсы частотой 2f.Отпирание одного из этих элементов про-: изводится сигналом кода режима работы, который,, если он соответствует значению логической 1, отпирает элемент 9 либо благодаря инвертору 1 открывает элемент 10, если его значение равно логическому О, Синхронизация выборки адреса кода блока 6 с номером канала управления обеспечивает посылку одного из выходных си-налов элементов 3, 10 на свой блок формирования управляющих импульсов k, воздействующий на тиристорный регулятор 5. Таким образом, оперативный переход с одного режима управления тиоисторными регуляторами на другой обеспечивает возможность проведения эксперимента так, чтобы получаемое общее температурное поле испытываемого изделия было оптимальным с точки зрения точности воспроизведения температурных графиков в зонах исследования. Кроме того, искажения формы кривой синусоиды питающего напряжения минимальны. Формула изобретения Избирательное устройство управления тиристорными регуляторами, содержащее выходной распределитель одним входом подключенный к генера ру импульсов, другим - к элементу ИЛИ,,одна группа выходов распределительного блока подключена к блокам формирования управляющих импульсов, другая группа выходов соединена с входами запоминающего блока, блок фазового управления и промежуточный распределитель,.входы которых подключены к выходам за поминающего блока, а выходы связаны соответственно с первым входом двухвходового элемента И и первым ВХОДОМтрехвходового элемента И,выходы которъ1х подключены к входам элемента ИЛИ, причем один вход бло ка фазового управления соединен с выходом выходного распределителя, блок выбора режима входамиподклю ченный к синхронизатору, один из 34 выходов которого подключен также к второму входу трехвходового элемента И, двоичный п-разрядный счетчик, отличающееся тем, что, с целью повышения точности управления, Оно.снабжено иньертором, причем вход двоичного п-разрядного счетчика соединен с выходом блока выбора режима, его выходы соединены с входами промежуточного распределителя, вход инвертора подключен к выходу П+1-ГО разряда запоминающего блока и к второму входу двухвходового элемента И, выход инвертора соединен с третьим входом трехвходового элемента И. Источники информации, принятые во внимание при экспертизе 1.Марков Б. А.И Чичерин Н. И. Тиристорные судовые и усилительнопреобразовательные устройства. Судостроение, 1967, с. 151-157. 2.Авторское свидетельство заявке № 2797 01/24-07, кл. Н 02 М 1/08, 1979. :

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления тиристорным регулятором | 1978 |

|

SU744867A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для регулирования подачи волокна к группе чесальных машин | 1989 |

|

SU1730235A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Устройство для преобразования интервалов времени в цифровой код | 1985 |

|

SU1411701A1 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2003 |

|

RU2250489C1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

Авторы

Даты

1981-12-07—Публикация

1980-04-03—Подача