Изобретение относится к вычислительной технике и может быть использовано в управляющих системах и гибридных вычислительных устройствах для получения в следящем режиме одновременно кода непрерывной переменной (X) и кодов функций sin x и cos x.

Известно устройство для вычисления тригонометрических функций [АС 519717 СССР, 1976], содержащее регистры, логические схемы, сумматоры, блок памяти. Недостатком данного устройства является большой объем оборудования.

Известен также синусно-косинусный преобразователь [АС 746535 СССР, 1980], содержащий два 2n-разрядных сумматора (где n - разрядность операндов), группы логических элементов И и ИЛИ, и являющийся наиболее близким к заявляемому преобразователю.

Недостатком известного синусно-косинусного цифрового преобразователя является низкая точность преобразования, обусловленная накоплением погрешности на каждом шаге (итерации) вычисления sin x и cos x.

Задачей изобретения является повышение точности преобразования операндов по закону синуса и косинуса.

Техническим результатом настоящего изобретения является снижение накопленной погрешности, образующейся на каждой итерации за счет метода численного решения дифференциального уравнения (метод трапеций).

Технический результат достигается тем, что синусно-косинусный цифровой преобразователь, содержащий два 2n-разрядных сумматора (где n - разрядность операндов), группы логических элементов И и ИЛИ, два элемента задержки, причем входы n младших разрядов первого сумматора соединены с выходами элементов ИЛИ первой группы, входы которых подключены к выходам соответствующих элементов И первой и второй групп, первые входы которых подключены соответственно к прямым и инверсным выходам n старших разрядов второго сумматора, входы n младших разрядов второго сумматора соединены с выходами элементов ИЛИ второй группы, входы которых подключены к выходам соответствующих элементов И третьей четвертой групп, первые входы которых подключены соответственно к прямым и инверсным выходам n старших разрядов первого сумматора, вход положительного приращения преобразователя соединен со вторыми входами элементов И второй и третьей групп и через первый элемент задержки соединен с третьим входом первого элемента ИЛИ первой группы, вход отрицательного приращения преобразователя соединены со вторыми входами элементов И первой и четвертой групп и через второй элемент задержки соединен с третьим входом первого элемента ИЛИ второй группы, дополнительно содержит два одноразрядных сумматора, четыре логических элементов И и два логических элемента ИЛИ. При этом дополнительные сумматоры подключены к младшим, 2n-м разрядам обоих сумматоров, а логические элементы по входам подключены к выходам старших разрядов каждого из сумматоров, а по выходам - ко входам дополнительных одноразрядных сумматоров.

Введение двух одноразрядных сумматоров, логических элементов И и ИЛИ и их связи с другими узлами и блоками прототипа позволило повысить точность преобразования операндов по закону синуса и косинуса.

Это является новым техническим решением в технике цифровых вычислительных устройств, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенный преобразователь имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяет повысить точность функционирования синусно-косинусного цифрового преобразователя.

Предложенный преобразователь промышленно применим, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических элементов).

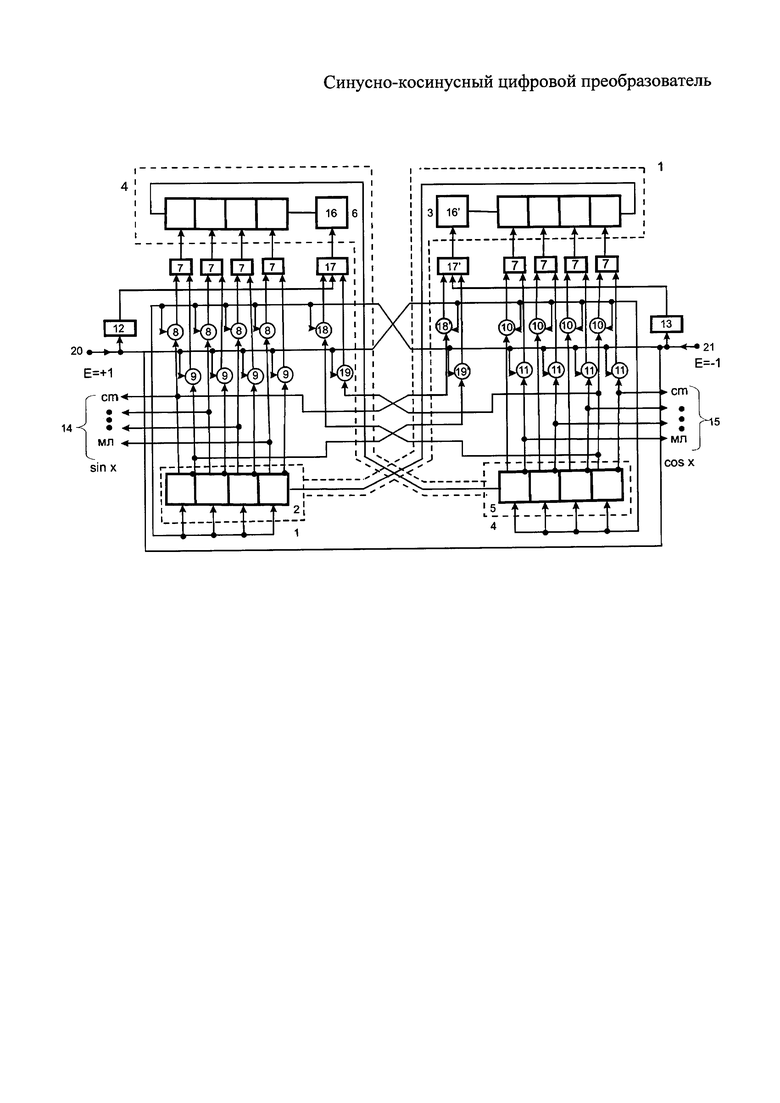

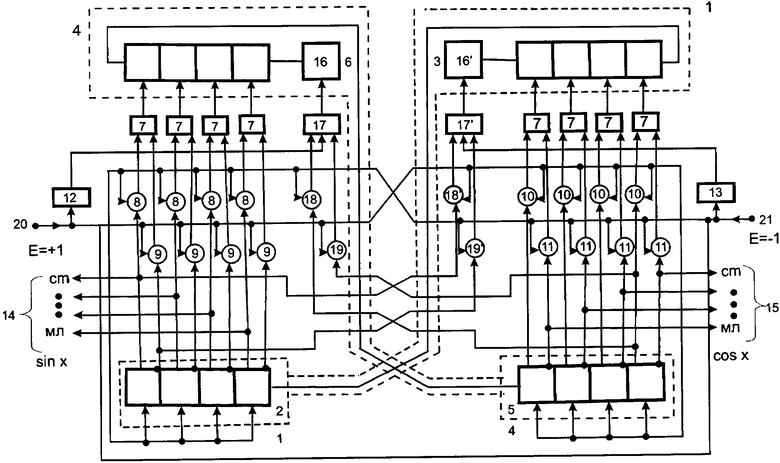

На чертеже изображена функциональная схема предлагаемого преобразователя.

Преобразователь состоит из первого сумматора 1, содержащего старших n разрядов 2 и младших n разрядов 3, второго сумматора 4, содержащего n старших разрядов 5 и n младших разрядов 6, группы элементов ИЛИ 7, группы элементов И 8-11, элементы задержки 12 и 13. Кроме того, он содержит два одноразрядных сумматора 16 и 16', подключенных в качестве младших (2n+1)-х разрядов первого 1 и второго 4 сумматоров. Дополнительно введены два логических элемента ИЛИ 17 и четыре логических элемента И 18, 19, включенных по управляющим входам аналогично группам элементов И 8 и 9, а по сигнальным входам соединенных с выходами самого старшего разряда обоих сумматоров 1 или 4. Входы 20 и 21 являются входами сигналов "ε=+1" и "ε=-1" соответственно. Выходами преобразователя являются 14 (sin x) и 15 (cos x).

В основу принципа действия предлагаемого преобразователя положены формулы, обеспечивающие повышенную точность за счет численного интегрирования дифференциальных уравнений по методу трапеций. [Булатникова И.Н. Целочисленные алгоритмы генерации гармонических сигналов // Изв. вузов, Северо-Кавказский регион, Техн. науки, 2005, №3, с. 13-17].

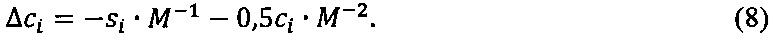

Обозначим si=M⋅sin(i/M) и ci=M⋅cos(i/M). M - масштабный коэффициент, M=2n, i - номер итерации и одновременно единичная величина 2-n в масштабе 1:М. Тогда приращения величин si и ci на единичном интервале (i,i+1) будут следующими:

Формулы (1) и (2) получены на основе усреднения производных в начале и в конце единичного интервала между соседними итерациями. При этом учтено, что производная от синуса равна косинусу, а производная от косинуса равна минус синусу.

Упрощая, имеем систему уравнений

Решая ее относительно Δsi и Δci, получаем

Упростим знаменатели (4М2>>1) и разделив на 4M2, имеем

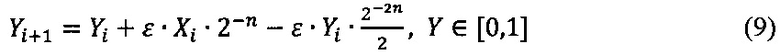

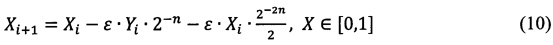

Окончательно, учитывая, что М=2n, имеем

где Yi - текущее значение функции sinθi содержимого первого сумматора 1 (yi=sinθi, y0=0);

Xi - текущее значение функции cosθi содержимого первого сумматора 4 (xi=cosθi, x0=1);

θi - текущее значение аргумента θ (θ0=0);

ε - алгебраический знак операции (ε=sign(UBx-Uθ));

n - разрядность.

Синусно-косинусный цифровой преобразователь работает следующим образом. Перед началом работы устройства старшие n разрядов 5 и младшие (n+1) разрядов 6 второго сумматора 4 устанавливаются в единичное состояние, а n старшие разрядов 2 и младшие (n+1) разрядов 3 первого сумматора 1 - в нулевое состояние, что соответствует θi=0, x0=1, y0=0.

Передача прямого или обратного кода выходов старших n разрядов 2 первого сумматора 4 на входы младших n разрядов 6 второго сумматора 4 соответственно через группу элементов И 8 и 9, группу элементов ИЛИ 7, а также передачей прямого или обратного кода с выходов старших n разрядов 5 второго сумматора 4 на входы младших n разрядов 3 первого сумматора 1 соответственно через группу элементов И 10 и 11, группу элементов ИЛИ 7. Элементы 12, 13 задержки используются для добавления единицы в одноразрядные сумматоры 16' и 16, как в самые младшие разряды первого 1 и второго 4 сумматоров с целью получения дополнительного кода при выполнении операции вычитания.

Таким образом, в предлагаемом преобразователе реализуются вычисления по формулам (9)÷(11), и на выходе 14 n старших разрядов 2 первого сумматора (1) получается код текущего значения функции Y=sinθ, а на выходе 15 n старших разрядов 5 второго 4 сумматора образуется код текущего значения функции X=cosθ.

Все вычисления производятся однообразно, но в зависимости от сигналов "ε=+1" (вход 20) или "ε=-1" (вход 21).

В первом случае ("ε=+1") в работу включаются элементы И первой 10 и третьей 9 групп. Во втором случае ("ε=-1") (вход 21) в работу включаются элементы И второй 11 и четвертой 8 групп.

И в первом и во втором случаях одновременно включаются логические элементы И 19 и 18' (первый случай) или такие же элементы 18 и 19' (второй случай). Они вносят поправки в ход вычислений по (9) и (10).

Аналогично прототипу срабатывают логические элементы ИЛИ 17 (первый случай) и 17' (второй случай). Свое управление они получают от линий задержки 12 (первый случай) или 13 (второй случай). Их выходной сигнал поступает на одноразрядные сумматоры 16 и 16', и формируют дополнительный код при операции вычитания.

В каждой i-й итерации старшие части 2 и 5 каждого из сумматоров 1 и 4, с учетом переносов в младшие части 3 и 6 от одноразрядных сумматоров 16' и 16, подсуммируются к (вычитаются из) содержимым младших частей 6 и 3, которые, кроме того, учитывают переносы из одноразрядных сумматоров 16 и 16', соответственно. Причем всегда, если в одном сумматоре идет одна операция, то в другом - обратная ей по знаку. Это обеспечивается перекрестным подключением входов логических элементов И.

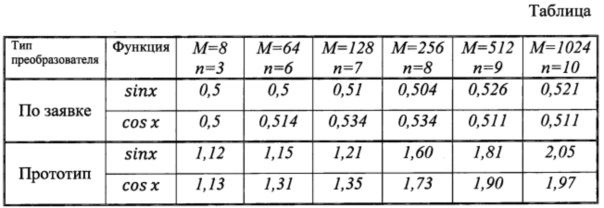

В таблице приведены максимальные абсолютные погрешности прототипа и заявленного синусно-косинусного цифрового преобразователя. Данные получены путем цифрового моделирования на ЭВМ обоих преобразователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный функциональный преобразователь | 2016 |

|

RU2631978C1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Синусно-косинусный цифровой преобразователь | 1973 |

|

SU746535A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1267620A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих системах и гибридных вычислительных устройствах для получения в следящем режиме одновременно кода непрерывной переменной (X) и кодов функций sin x и cos x. Технический результат заключается в повышении точности преобразования операндов по закону синуса и косинуса. Синусно-косинусный цифровой преобразователь содержит два (2n+1)-разрядных сумматоров, разделенных на старшие n разрядов и на (n+1) младших, логические элементы И и ИЛИ, два элемента задержки. Преобразователь дополнительно содержит два одноразрядных сумматора, четыре логических элемента И и два логических элемента ИЛИ в каждой итерации содержимое старших разрядов одного сумматора суммируется (вычитается) к младшим разрядам другого сумматора и наоборот. 1 ил.

Синусно-косинусный цифровой преобразователь, содержащий два 2n-разрядных сумматора, где (n-разрядность операндов), группы элементов И и ИЛИ, два элемента задержки, причем входы n младших разрядов первого сумматора соединены с выходами элементов ИЛИ первой группы, входы которых подключены к выходам соответствующих элементов И первой и второй групп, первые входы которых подключены соответственно к прямым и инверсным выходам n старших разрядов второго сумматора, входы n младших разрядов второго сумматора соединены с выходами элементов ИЛИ второй группы, входы которых подключены к выходам соответствующих элементов И первой и второй групп, первые входы которых подключены соответственно к прямым и инверсным выходам n старших разрядов второго сумматора, входы n младших разрядов второго сумматора соединены с выходами элементов ИЛИ второй группы, входы которых подключены к выходам соответствующих элементов И третьей и четвертой групп, первые входы которых подключены соответственно к прямым и инверсным выходам n старших разрядов первого сумматора, вход положительного приращения преобразователя соединен со вторыми входами элементов И второй и третьей групп и через первый элемент задержки соединен с третьим входом первого элемента ИЛИ первой группы, вход отрицательного приращения преобразователя соединен со вторыми входами элементов И первой и четвертой групп и через второй элемент задержки соединен с третьим входом первого элемента ИЛИ второй группы, отличающийся тем, что дополнительно содержит два одноразрядных сумматора, четыре логических элемента И и два логических элемента ИЛИ, причем каждый одноразрядный сумматор подключен к младшему разряду одного из 2n-разрядных сумматоров в качестве (2n+1)-го разряда, а логические элементы по входу подключены к выходам первого, старшего разряда каждого из сумматоров, а по выходам - ко входам одноразрядных сумматоров.

| Синусно-косинусный цифровой преобразователь | 1973 |

|

SU746535A1 |

| СПОСОБ НАНЕСЕНИЯ ЛАКА НА ЦЕННЫЕ БУМАГИ, В ОСОБЕННОСТИ НА ЦЕННЫЕ БУМАГИ, ОТПЕЧАТАННЫЕ МЕТОДОМ ГЛУБОКОЙ ПЕЧАТИ, НАПРИМЕР, БАНКНОТЫ, И МАШИНА ДЛЯ НАНЕСЕНИЯ ЛАКА ДЛЯ ВЫПОЛНЕНИЯ СПОСОБА | 2009 |

|

RU2513682C2 |

| US 5327133 A, 05.07.1994 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2017-07-17—Публикация

2016-02-25—Подача