Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратного вычисления функций в специализированных цифровых вычислительных машинах и устройствах.

Известны арифметические устройства [А.с. 528891 СССР, Арифметическое устройство, 1976 г.], [А.с. 744595 СССР, Цифровой функциональный преобразователь, 1980 г.], которые содержат сумматоры, регистры, счетчики. Они служат для вычисления ограниченного круга функций (синус, косинус, множительно-делительная функция).

Наиболее близким техническим решением к предлагаемому изобретению является устройство для определения функции z=х·у2 [А.с. 521570 СССР, 1976 г.]. Оно содержит шесть сдвиговых регистров, четыре сумматора, блок анализа сходимости, блок памяти, блок анализа знака, блок управления, выходы которого подключены к входам сдвиговых регистров и входу блока памяти. Кроме того, вход блока анализа сходимости соединен с выходом третьего сдвигового регистра, а выход - со входом блока управления, кроме того, вход блока анализа знака подключен к выходу первого разряда третьего сдвигового регистра, а выход - к первым входам первого, второго и третьего сумматоров.

Недостатком этого устройства является невозможность с его помощью вычисления других (например, дробно-рациональных) функций.

Задачей настоящего изобретения является расширение функциональных возможностей устройства для вычисления функций.

Технический результат настоящего изобретения - возможность вычисления широкого класса алгебраических (дробно-рациональных) функций помимо функции прототипа.

Технический результат достигается предложенным устройством для вычисления функций, которое содержит четыре сумматора, шесть сдвиговых регистров, три регистра исходных данных, блок анализа знака, блок анализа сходимости, блок управления, блок памяти и две группы элементов И. При этом вход блока анализа сходимости соединен с выходом третьего сдвигового регистра, а выход - с входом блока управления, а вход блока анализа знака подключен к выходу первого разряда третьего сдвигового регистра, при этом выход подключен к первым входам первого, второго и третьего сумматоров. Первый и второй регистры исходных данных через группы элементов И соединены с блоком памяти и с шестым сдвиговым регистром, соответственно.

Введение дополнительно двух регистров исходных данных и двух групп элементов И и связей их с другими блоками устройства позволило расширить функциональные возможности устройства за счет его способности вычислять класс алгебраических (дробно-рациональных) функций. Это является новым техническим решением в технике цифровых функциональных преобразователей, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяет расширить функциональные возможности устройства, в частности вычисление алгебраических (дробно-рациональных) функций.

Предложенное устройство для вычисления функций промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических элементов).

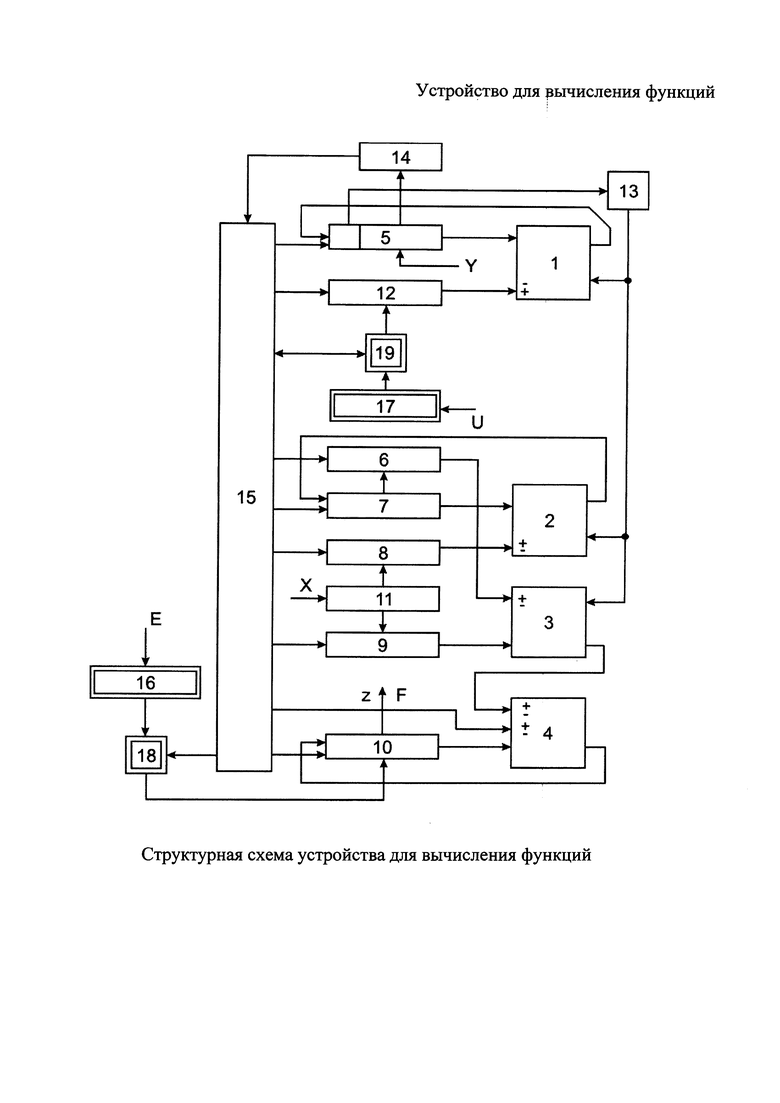

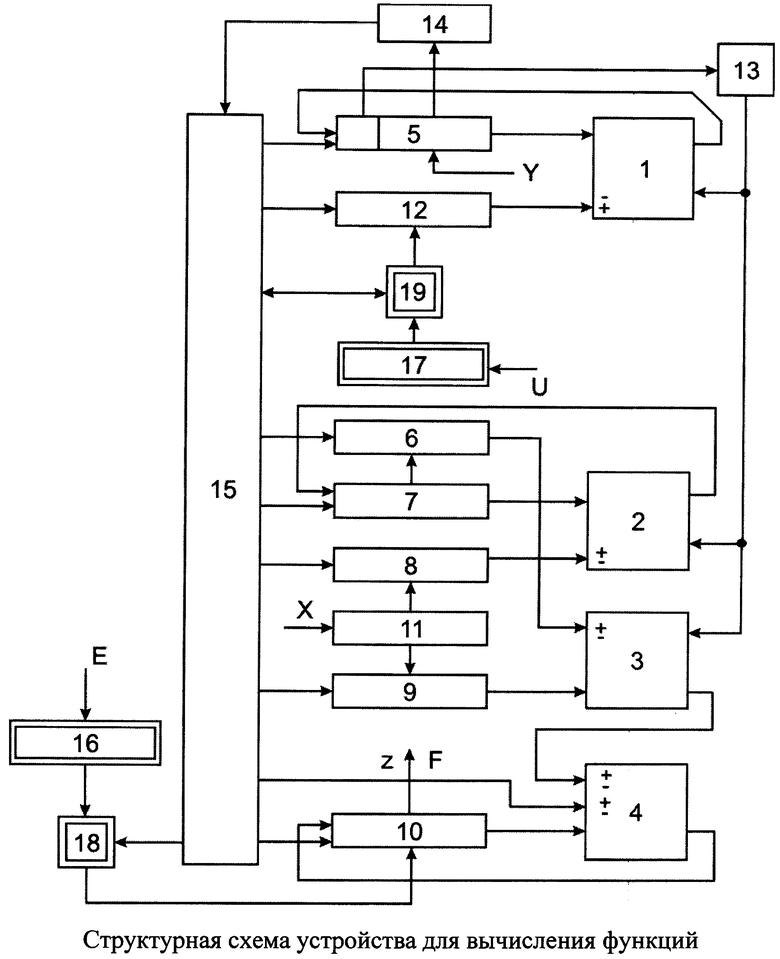

На чертеже представлена структурная схема устройства для вычисления функций.

Заявленное устройство состоит из сумматоров 1-4, сдвиговых регистров 5-10, регистров исходных данных 11, 16, 17, блока 12 памяти, блока 13 анализа знака, блока 14 анализа сходимости, блока 15 управления и двух групп 18, 19 элементов И.

Выход первого регистра 11 соединен с входами первого и второго сдвиговых регистров 9 и 8. Выход первого (знакового) разряда третьего сдвигового регистра 5 соединен с входом блока 13 анализа знака, выход которого соединен с первыми (управляющими) входами сумматоров 1-3. Ко второму (управляемому) входу сумматора 1 подсоединен выход блока 12 памяти. Ко второму входу сумматора 2 подсоединен выход второго сдвигового регистра 8. Ко второму входу сумматора 3 подсоединен выход пятого сдвигового регистра 6. Ко второму входу сумматора 4 подсоединен выход сумматора 3. Выход каждого из сумматоров 1, 2, 4 соединен, соответственно, через третий, четвертый и шестой сдвиговые регистры 5, 7 и 10 со своим третьим входом. Второй выход третьего сдвигового регистра 5 соединен с блоком 14 анализа сходимости, выход последнего соединен с входом блока 15 управления. Выходы последнего соединены со сдвигающими входами всех сдвиговых регистров и входом блока 12 памяти. Выход четвертого сдвигового регистра 7 соединен с входом пятого сдвигового регистра 6. Блок 13 анализа знака состоит из сумматора 4 и логических элементов. Блок 14 анализа сходимости представляет собой цифровую схему сравнения с логическим нулем. Блок 15 управления содержит генератор тактовых (сдвигающих) импульсов, счетчик, дешифратор, логические элементы и схемы сброса (прерывания процесса вычисления). В качестве сумматоров 1-4 применены одноразрядные сумматоры-вычитатели накопительного типа. В блок 12 памяти, который представляет собой одностороннее запоминающее устройство с поразрядной выборкой значений очередного разряда каждым тактовым (сдвигающим) импульсом, записаны константы вида 2-(i+1)·u, где i - номер итерации.

Кроме того, первый 16 и второй 17 регистры исходных данных через первую 18 и вторую 19 группы элементов И связаны с шестым 10 сдвиговым регистром и с блоком 12 памяти, соответственно. Входы первого 16 и второго 17 регистров исходных данных являются дополнительными входами устройства. Один из выходов блока 15 управления связан с управляющим входом сумматора 4.

Входами устройства являются: для аргумента X - входы первого сдвигового регистра 11, для Y - входы третьего сдвигового регистра 5, для U - входы второго 17 регистра исходных данных, и для Е - входы первого 16 регистра исходных данных.

Выходом устройства является выход сдвигового регистра 10 (величины Z или F).

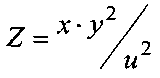

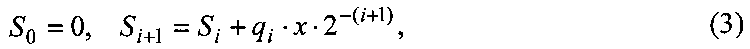

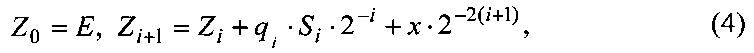

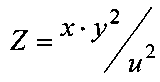

В описываемом устройстве реализуется вычисление по формуле F(x,y)=E±Z, где  (х, у, u, Е - целые положительные двоичные числа). Основные вычисления (величина Z) проходят по нижеприведенному разностно-итерационному алгоритму, который позволяет заменить возведение в квадрат, умножение и деление операциями псевдоделения и псевдоумножения

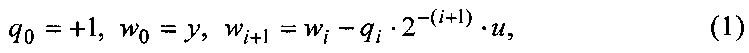

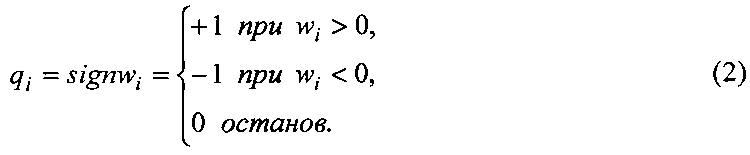

(х, у, u, Е - целые положительные двоичные числа). Основные вычисления (величина Z) проходят по нижеприведенному разностно-итерационному алгоритму, который позволяет заменить возведение в квадрат, умножение и деление операциями псевдоделения и псевдоумножения

где i=0, 1, 2, …, n-1, n - двоичная разрядность аргументов.

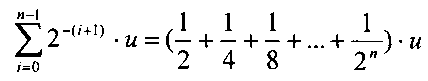

Разностно-итерационные рекуррентные соотношения (1)-(4) обеспечивают параллельный итерационный процесс. Условие его сходимости обеспечено при у≤u<2n. Это базируется на том факте, что из w0=y может быть вычтено максимально возможное число, равное в пределе  . Оно всегда должно быть больше или равно у (см. (1)). Таким образом, величина wi на (n-1)-й итерации или раньше станет равной "0", то есть произойдет останов алгоритма (см. (2)).

. Оно всегда должно быть больше или равно у (см. (1)). Таким образом, величина wi на (n-1)-й итерации или раньше станет равной "0", то есть произойдет останов алгоритма (см. (2)).

Каждое из соотношений (1)-(4) в устройстве реализуется (вычисляется) последовательным путем в каждой (i+1)-й итерации.

В начальном состоянии в первый 11 регистр (и в сдвиговые регистры 8 и 9) заносится значение операнда X, в сдвиговый регистр заносится значение операнда Y, а во второй 16 и третий 17 - значения Е и U, соответственно. Все операнды заносятся в параллельном двоичном коде. В блоке 15 управления выбираются (программируются) режим "вид функции" и знак ±Z.

В любой итерации с выходов блока 15 управления выдаются серии (последовательности) тактовых импульсов, которые продвигают содержание сдвиговых импульсов в сумматоры. Результаты очередного действия с выходов сумматоров 1, 2 и 4 записываются младшими разрядами вперед в освобождающиеся при сдвиге старшие разряды сдвиговых регистров 5, 7 и 6 и продвигаются к началу этих регистров.

Из блока 12 памяти в каждой итерации поступает очередное значение константы единицы или аргумента U. По знаку результата в сдвиговом регистре 5 в конце каждой итерации определяется режим вычитания (сложения) для сумматора 1, сложения (вычитания) для сумматоров 2 и 3. При отрицательном знаке режим работы сумматоров 2 и 3 меняется на обратный. После выполнения итераций в сдвиговом регистре 10 находится значение функции произведения одного аргумента на квадрат второго, в сдвиговом регистре 7 - произведение аргументов, а в сдвиговых регистрах 5, 6, 8 и 9 - нулевые значения. Однако для большинства значений операндов X и Y процесс вычисления заканчивается на итерации с номером меньше значения i. При равенстве содержания сдвигового регистра 5 нулю сигнал с блока 14 анализа сходимости останавливает подачу тактовых импульсов из блока 15 управления на следующей итерации, и процесс вычисления заканчивается.

После завершения итераций в сдвиговом регистре 10 готов промежуточный результат  , к которому с помощью сумматора 4 подсуммируется величина Е, находящаяся во втором 16 регистре через первую 18 группу элементов И, управляемых блоком 15 управления.

, к которому с помощью сумматора 4 подсуммируется величина Е, находящаяся во втором 16 регистре через первую 18 группу элементов И, управляемых блоком 15 управления.

При этом блок 15 управления подает сигнал в сумматор 4 на взятие величины Z со знаком плюс или минус в зависимости от вида реализуемой функции. Данные о них приведены в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления степенных функций | 1977 |

|

SU682895A1 |

| Устройство для определения функции | 1973 |

|

SU521570A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2565010C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

Изобретение относится к цифровой вычислительной технике и применяется для аппаратного вычисления функций в специализированных цифровых машинах и устройствах. Технический результат заключается в обеспечении возможности вычисления дробно-рациональных функций. Технический результат достигается за счет устройства для вычисления функций, которое содержит сумматоры, регистры исходных данных, сдвиговые регистры, блок памяти, блок анализа знака, блок анализа сходимости, группы элементов И, блок управления. В устройство дополнительно введены два регистра исходных данных и две группы элементов И. 1 табл., 1 ил.

Устройство для вычисления дробно-рациональных функций, содержащее шесть сдвиговых регистров, четыре сумматора, три регистра исходных данных, блок памяти, блок анализа знака, блок анализа сходимости, блок управления, выходы которого подключены к входам сдвиговых регистров и к входу блока памяти, к сумматорам, к блокам анализа сходимости и знака, кроме того, вход блока анализа сходимости соединен с выходом третьего сдвигового регистра, а выход - с входом блока управления, вход блока анализа знака подключен к выходу первого разряда третьего сдвигового регистра, а выход - к первым входам первого, второго и третьего сумматоров, второй и третий входы первого сумматора соединены с выходом блока памяти и выходом третьего сдвигового регистра, а выход - с входом третьего сдвигового регистра, второй и третий входы второго сумматора соединены с выходами второго и четвертого сдвиговых регистров, а его выход - с входом четвертого сдвигового регистра, второй и третий входы третьего сумматора соединены с выходами пятого и первого сдвиговых регистров, а его выход - с первым входом четвертого сумматора, второй вход которого подключен к выходу шестого сдвигового регистра, а выход - ко входу этого регистра, выход четвертого сдвигового регистра соединен со входом пятого сдвигового регистра, отличающееся тем, что в него дополнительно введены второй и третий регистры исходных данных, первая и вторая группы элементов И, причем выходы первого и второго регистров через одноименные группы элементов И соединены с шестым сдвиговым регистром и блоком памяти, соответственно, кроме того, управляющие входы обеих групп элементов И связаны с выходами блока управления, один из выходов которого соединен с управляющим входом четвертого сумматора, а входы обоих регистров соединены со входами устройства, выход которого связан с выходом шестого сдвигового регистра.

| Устройство для определения функции | 1973 |

|

SU521570A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Фрикционный механизм для приведения в движение ползуна винтовых прессов | 1946 |

|

SU75072A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| US 6650317 B1, 18.11.2003. | |||

Авторы

Даты

2016-08-27—Публикация

2015-03-13—Подача