подключен к входу k-го младшего разряда второго операнда устройства а второй вход - к 1с-му выходу преобразователя в дополнительный код, выход It-ro коммутатора второго столбца подключен к входу суммы It -и ячейки N -го столбца, tn -И вход преобразователя в дополнительный код подключен .к входу (п1+1)-го разряда первого операнда устройства выходы узла коррекции подключены соответственно к выходам старших разрядов результата устройства, вход переноса узла коррекции подключен к выходу переноса преобразователя в дополнительный код, вход управления узла коррекции, вход управления каждого коммутатора и первый вход первой ячейки первой строки подклйчны к входу управления устройства, второй вход первой ячейки первой строки подключен к входу логическог нуля устройства..

2. Устройство по п, 1,. отличающееся тем, что узел кор(ержит (KlJ-1) одноразрядных

рекции содержит

I, (N-1) элементов ИСКЛГОсуммато.ров, ЧАЮЩЕЕ или,

I, (N-1) элементов И, элемент НЕ, причем вход элемента НЕ соединен с входом управления у.зла коррекции и с Первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй Bxorf m-ro элемента ИСКЛЮЧАЩЕЕ ИЛИ и первый вход ш-го элемента И соединены соответственно с первым и вторым m-ми входами узла коррекции, п -выход которого соединен с выходом т-го одноразрядного сумматора, первый и второй входы которого соеди нены соответственно свыходами тп-го элемента ИСКЛЮЧАЮСШЕ ИЛИ и m-го , элемента И, второй вход которого соединен с выходом элемента НЕ, вход переноса т-го одноразрядного сумматора, кроме tN-l)-ro, соединен с выходом переноса lm+1)-го одноразрядного сумматора, вход переноса .(N-1 )-го одноразрядного сумматора ;соединен ; с входом переноса блоки коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1024910A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Устройство для умножения двоичных чисел в дополнительном коде | 1983 |

|

SU1191907A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

1. МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее матрицу ячеек из N строк и N столбцов, причем первый вход п-ой ячейки всех строк подключен к первому выходу (п-1)-й ячейки той же строки, второй вход п-и ячейки всех столбцов подключен к второму выходу (п -1 )-й ячейки того же столбца, вход суммы каждой ячейки всех строк, за исключением ячеек первой строки и N -го столбца, подключен к выходу ячейки предыдущей строки последующего столбца, вход переноса т -и ячейки каждой строки подключен к выходу переноса (т+1)-иячейки этой же строки, вторые входы ячеек первой строки, за исключением первой ячейки этой же строки, подключены соответственно к входам первого операнда устройства, выходы суммы ячеек N-й строки, за исключением ;первой ячейки этой же строки, являются выходами младших разрядов результата устройства, входы сунады ячеек первой строки, за исключением 1Ч-и ячейки, являются входаьш старших разрядов второго операнда устройства, первые выходы ячеек N -го столбца подключены к входам переноса этих же ячеек, каждая ячейка содержит одноразрядный сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход ячейки соединен с первым выходом ячейки и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом и выходом ячейки, вход суммы последней соединен с первым входом одноразрядного сумматора, второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы переноса и суммы соединены соответственно с выходами переноса и cyMMFJ ячейки, вход переноса кото(Л рой соединен с входом переноса одноразрядного сумматора, отлис чающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения операций умножения, введены преобразователь в дополнительный код, узел коррекции, (N-1) KOT-Iмутаторов первого столбца, N коммусо 42. таторов второго столбца, элемент .ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый ВХОД элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен |О к выходу суммы первой.ячейки N-и строки, второй вход - к входу управления устройства, а выход - к выходу соответствующего младшего разряда результата устройства, первый вход т-го коммутатора первого .столбца подключен к выходу суммы m-и ячейки первого столбца и m-му первому входу узла коррекции, каж,дый m -п второй вход которого подключен к выходу переноса (т+1) -и .ячейки первого столбца, второй .вход гп-го коммутатора первого столбца подключен к входу суммы т-й ячейки первой строки, первый вход k -го коммутатора второго столбца

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях и высокопроизводительных ЭВМ для одноактного выполнения опер ццй умножения и деления над целыми и дробными двоичными числами, представленных в прямых кодах.

Известно матричное вычислительное устройство, содержащее матрицу ячеек из N+1 строк и N столбцов, причем каждая ячейка содержит одноразрядный сумматор, элемент ИСКЛЮЧАЮ1ЦЕЕ ИЛИ и элемент И l.

Недостатком этого устройства являются значительные „аппаратурные затраты.

Известно матричное устройство для умножения и деления, содержащее столбец из N цифровых компараторов и матрицу ячеек из N строк, первая :;трока которой включает N ячеек, а каждая последующая строка содержит на одну ячейку больше чем предыдущая, причем все ячейки матрицы включают два элемента И, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент мажоритарной логики, три входа и три выхода, вход переноса и выход переноса, вход суммы и выход суммы С 2 .

недостатками данного устройства являются значительные аппаратурные затраты и сложность поразрядного секционирования.

Наиболее близким по технической ,сущности к предлагаемому является ;вычислительное устройство, со.держащее матрицу ячеек из N 5 строк и N столбцов, причем

первый вход h-ой ячейки всех строк подключен к nepBoi-iy выходу (п-1)-ой (ячейки той же строки, второй вход iS -и ячейки всех столбцов подключен

0 ко второму выходу (п-1)-й ячейки того же столбца, вход суммы каждой ячейки всех строк, за исключением ячеек первой строки и N -го столбца, подключен .к выходу суммы ячейки

5 передающей строки последующего

столбца, вход переноса m-и ячейки 1 аждой строки подключен к выходу переноса (п +1)-й ячейки этой же строки, вторые входы ячеек первой строки подключены к входам первого

операнда устройства, выходы суммы ячеек N -и строки подключены к выходам младших разрядов результата, входы суммы ячеек первой строки и N-ro столбца подключены к входам

5 второго операнда устройства, выходы переноса ячеек первого столбца являются выходами старших разрядов результата, первые выходы ячеек N-ro столбца подключены к входам

0 переноса этих же ячеек, выход переноса пл-и ячейки первого столбца подключен к первому входу ячейки того же столбца, а также каждая ячейка содержит одноразрядный сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход ячейки соединеи с первым выходом ячейки и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторым входом и выходом ячейки, вход суммы которой соединен с первым входе одноразрядного сумматора, второй вход которого соединен с выходом элемента ИСКЛЮЧАВДЕВ ИЛИ, а выходы переноса и суммы соединены (Соответственно с выходами переноса и суммы ячейки, вход переноса которой соединен с входсм переноса одноразрялного сумматора {п; 2, 3,...,N; ni 1,2,... N-1)C33. ,

Недостаток известного устройства - невозможность выполнения операции умножения.

Цель изобретения - расширение функциональных возможностей вычисли1тельного устройства за счет выполiнения операций умножения.

Поставленная цель достигается тем, что вычислительное устройство, содержащее матрицу ячеек из N стро и .N столбцов (где N - разрядность операндов), причем первый вход П-й ячейки врех строк (П 2,3,... подключен к первому выходу (п-1)-й ячейки той же строки, второй вход h-й ячейки всех столбцов подключен к второму выходу ( ячейки того же столбца, вход сукмы каждой ячейки всех строк, за исключением ячеек первой строки и N -го столбца подключен к выходу суммы ячейки предыдущей строки послед тощего столбца, вход переноса m -и ячеГжи каждой строки (т 1,2,..., N -1 подключен к выходу переноса (т+1)-и

ячейки этой же строки, вторые входы

;ячеек первой строки, за исключением первой ячейки этой же строки, подключены соответственно к входам первого операнда устройства, выходы суммы ячеек N-Й строки, за исключением первой ячейки этой же строки, являются выходами г-шадших разрядов результата устройства, входы суммы ячеек первой строки, за исключением N-й ячейки, являются входами старших разрядов второго операнда устройства, первые выходы ячеек N-ro столбца подключены к входам переноса этих же ячеек, каждая ячейка содержит одноразрядный сукматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первь1й вход ячейки соединен с первым выходом ячейки и nepBtJM входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с вторыми входом и выходом ячейки, вход сукмы последней соединен с первым входом одноразрядного сумматора, второй вход которого соединен с выходом элемента ИСКЛОЧАЮЩЕЕ ИЛИ, а выходы переноса и сум-

пел соединены соответственно с выходами переноса и сумкы ячейки, ;вход переноса которой соединен с входом переноса которой соединен с входом переноса одноразрядного сумматора, введены преобразователь в дополнительный код, узел коррекции, (N-1) коммутаторов первого столбца, N коммутаторов BTOpoiro столбца, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,

0 причем первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подключен к выходу суьмы первой ячейки N-й строки, второй вход - к входу управлени я устройств а, а выход этого элемента - К

5 выходу соответствующего младшего разряда результата устройства, первый вход т-го коммутатора первого столбца подключен к выходу суммы m-и ячейки первого столбца и т-му первому входу узла коррекции, каж0дый 1П-Й второй вход которого подключен к выходу переноса (т+1)-и ячейки первого столбца/ второй вход. m-го KONMyTaTopa первого столбца подключен к входу суммы го-й ячейки

5 первой строки, первый вход It-го коммутатора второго столбца (k 1,2...., N) подключен к входу I: -го глладшего разряда второго операнда устройства, а второй вход 0к 1с-му выходу преобразователя в дополнительный код, выход k-го ко№ утатора второго столбца подключен к входу суммы 1с-и ячейки N-ro столбца, m-и вход преобразователя

5 в дополнительный код подключен к входу (т+1)-го разряда первого операнда устройства, выходы узла коррекции соответственно подключены к выходам старших разрядов резуль0;тата устройства, вход переноса узла коррекции подключен к выходу пере- iHoca преобразователя в дополнительный код, вход управления узла коррекции, вход управления каждого комму5татора и первый вход первой ячейки ртерврй строки подключен к входу |управления устройства, второй вход первой ячейки первой строки подключен к входу логического нуля устрой0 ртва.

Причем узел коррекции содержит (N-1) одноразрядных сумматоров, i(N-l) элемент вИСКЛЮЧАЮЦЕЕ ИЛИ, (N-1) элементми, элемент НЕ, причем-вход

5- элемента НЕ соединен с входом управления узла коррекции и с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход т-то элемента ИСКЛЮЧАЮ ЦЕЕ ИЛИ и первый вход m -го элемента И соединены соответственно с первым и вторым tn -ми входами узла коррекции, m-и которого соединен с выходом m-го одноразрядного cyNwaTopa, первый и второй

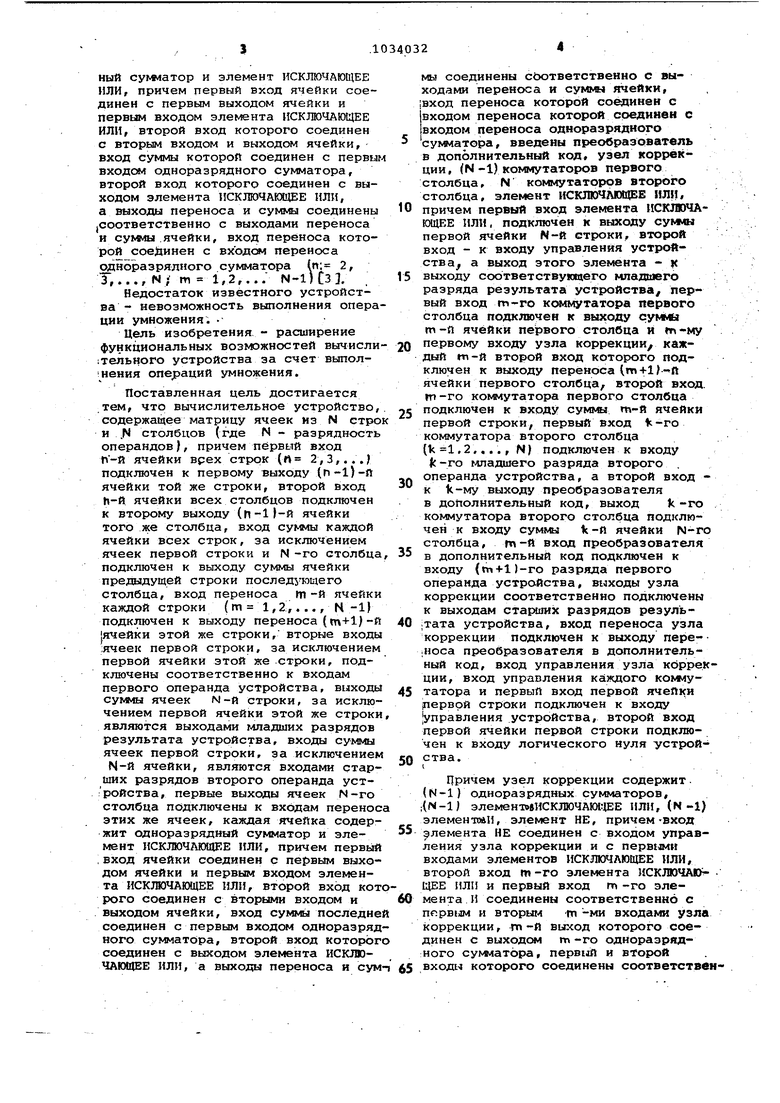

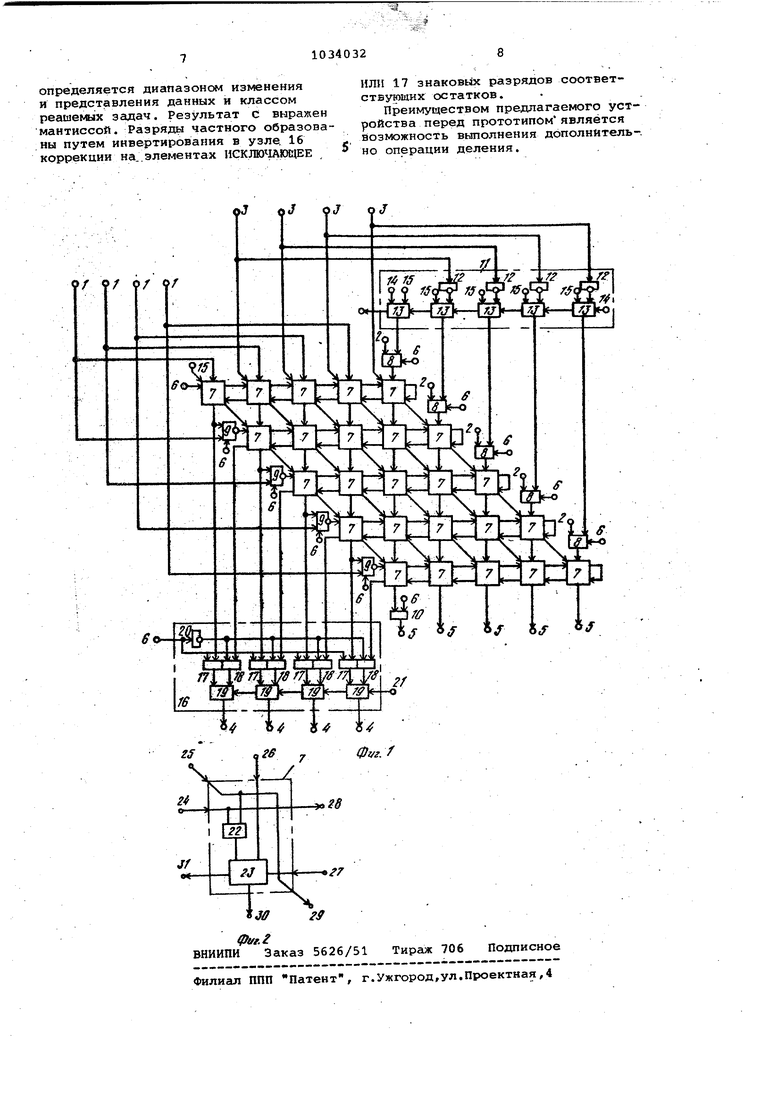

5 входы которого соединены соответственно с выходами m -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ н т-го элемента И, второй вход которого соедийен с выходом элемента НЕ, вход переноса одноразрядного суглиатора, кроме , (N-1)-го, соединен с выходом перенос (h-1+ll-ro одноразрядного сумматора, вход переноса (N-l)-ro одноразрядного сумматора соединен с входом переноса блока коррекции. На фиг. 1 приведена структурная схема матричного вьлчислительного устройства, на фиг. 2 - функциональ ная схема ячейки. Матричное вычислительное устройство (фиг. 11 содержит первые 1, вторые 2 и треть.и 3 информационные входы устройства, старшие 4 и младшие 5 выходы устройства, вход 6 управления устройства, ячейки 7, ко мутаторы второго столбца с прямым 8 и инверсным 9 первого столбца выходом, элемент ИСКЛЮЧАЮЩЕЕ ИЛ1 10, преобразователь 11 в дополнительный код, содержащий элементы НЕ 12, одноразрядные сумматоры 13, входы, подключаем1ле к сигналу логической единицы,14, входы 15, подключаемые к сигналу логического нуля, узел 16 коррекции, содержащий также элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 17 элементы И 18, одноразрядные сумматоры 19 элемент НЕ 20 и вход 21 переноса. Каждая ячейка 7 включает элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22, одноразрядный сумглатор 23, первый 24 и второй 25 входы, вход 26 суммы, вход 27 переноса, первый 28 и второй 29 выходы, выход 30 суммы и выход 31 переноса. Матричное вычислительное устройство оперирует с мантиссами операндов.. На входы 1 подают мантиссы либо множителя, либо делимого. В случае, когда разрядность мантиссы делимого больше N-1, оставшиеся разряды подают на входы 2. На входы 3 подаю разряды мантиссы либо множимого, либо делителя. На выходах 4 формируются либо старшие разряды-произведения, либо частное от деления, на выходах 5 - либо f/шадшие разряды произведения, либо остаток от деления. Управление матричным вычислитель ным устройством осуществляется чере входы 6 управления. При логическом нуле на этом входе выполняется умножение, а при логической единице деление. Сигнал логической единицы на входе управления коммутаторов связывает их выходы с первыми входа ми, а сигнал логического нуля - с BTOpbiMH их входами. Преобразбватель 11 формирует код дополнения от множимого, необходимы ля выполнения умножения, при делеии этот код игнорируется, Узел 16 коррекции при вглюлнении множения учитывает биты переноса сумму на выходах ячеек 1-го столба, возникающих при суммировании сех частичных произведений и попраок. При делении узел 16 коррекции ыполняет в соответствии с алгоритом деление без восстановления статка, инвертирование знаковых разг ядов всех промежуточных остатков. Матричное вычислительное устройтво работает следующим образом, При умножении на входы 6 подают сигнал логического нуля. Умнох ение выполняется старшими разрядами вперед, причем коды множимого поразрядно перемножаются на разряды преОбразованного множителя, представленного в системе счисления с цифрами 1-1, -1-1 ). Произведение двух чисел вычисляется по следующей формуле C(-6) п (c..) где С - мантисса произведения в 2N 2 разрядов; В - модуль кода множимого; CQ -нулевая сумма, равная мантиссе кода множителя; sicjn(o.)- знак t -го разряда преобразованного кода множителя; Пд - нулевое частичное произведение, равное модулю множимого, М - разрядность прячмых кодов операндов. При умножении целых чисел самый младший разряд произведения игнорируется. Для вьтолнения деления на входы 6 (фиг. 1/ необходимо подать сигнал .логической единицы. Деление в матричiHOM вычислительном устройстве выполняется по 1-1етоду без восстановления остатка. При этом в зависимости от соотношения между Делимьл А и делителем В деление выполняется после сдвига А или без. этого сдвига. В первом случае необходимо, чтобы А В , а во втором возможно , но сами /Ч и В должны быть нормализованными дробями, т.е. содержать в старших разрядах мантисс единицы. Наличие элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 позволяет сформировать дополнительный (N-i-1 1-й разряд прямого кода .частного для первого случая и N-й разряд частного для второго случая. Наличие единицы на ставшем разряде выходов 4 свидетельствует о-том, что О 1. Делимое поступает -со сдвигом на разряд в сторону старших разрядов. Необходимость этого сдвига

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 3402542/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Построение и применение | |||

| Под ред | |||

| А.А | |||

| Васенкова, М., Сов | |||

| радио, 1980, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Вычислительные системы и синхронная арифметика | |||

| М., Радио и связь, 1981, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-08-07—Публикация

1982-03-26—Подача