Изобретение относится к вычислительной технике, в частности к частотно-импульсным вычислительным устройствам.

Известен синусно-косинусный функциональный преобразователь, содержащий два преобразователя код-частота, охваченных отрицательной обратной связью, причем каждый преобразователь содержит счетчик результата, соединенный группой элементов И-ИЛИ. Кроме того, имеется также регистр аргумента и развертывающий счетчик, соединенные с блоком сравнения [Воронов А.А. и др. Цифровые аналоги для систем автоматического управления, АН СССР, 1960, с. 184].

Недостатком такого преобразователя является сравнительно низкое быстродействие, обусловленное спецификой работы частотно-импульсных вычислительных устройств.

Наиболее близким к изобретению по технической сущности является синусно-косинусный функциональный преобразователь [А.с. №732884, СССР, 1980], содержащий регистр аргумента, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов развертывающего счетчика, вход которого соединен с первым выходом генератора тактовых импульсов, два основных преобразователя код-частота, каждый из которых содержит счетчик результата и группу элементов И-ИЛИ, причем выходы счетчика результата соединены с первыми входами элементов И-ИЛИ группы, вторые входы которых соединены с второй группой выходов развертывающего счетчика, выходы элементов И-ИЛИ группы первого и второго основных преобразователей код-частота через соответствующие элементы И блокировки соединены, соответственно, с первыми входами счетчиков результата второго и первого основных преобразователей код-частота, управляющие входы которых соединены с выходами блока управления и установки начальных условий, управляющие входы элементов И блокировки соединены с первым выходом блока сравнения, введены два дополнительных преобразователя код-частота, каждый из которых содержит счетчик результата, группу элементов И-ИЛИ и группу элементов И.

Однако недостатком этого преобразователя является низкая точность функционального преобразования по закону синуса и косинуса.

Задачей настоящего изобретения является повышение точности функционирования устройства.

Технический результат - точное преобразование цифровых значений синуса и косинуса для заданного значения их аргумента.

Технический результат достигается предложенным синусно-косинусным функциональным преобразователем, содержащим содержащий регистр аргумента, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов развертывающего счетчика, вход которого соединен с первым выходом генератора тактовых импульсов, два основных преобразователя код-частота, каждый из которых содержит счетчик результата и группу элементов И-ИЛИ, причем выходы счетчика результата соединены с первыми входами элементов И-ИЛИ группы, вторые входы которых соединены с второй группой выходов развертывающего счетчика, выходы элементов И-ИЛИ группы первого и второго основных преобразователей код-частота через соответствующие элементы И блокировки соединены соответственно с первыми входами счетчиков результата второго и первого основных преобразователей код-частота, управляющие входы которых соединены с выходами блока управления и установки начальных условий, управляющие входы элементов И блокировки соединены с первым выходом блока сравнения, введены два дополнительных преобразователя код-частота, каждый из которых содержит счетчик результата, группу элементов И-ИЛИ и группу элементов И, причем выходы старших и младших разрядов счетчика результата соединены соответственно с первыми входами элементов И группы и элементов И-ИЛИ группы, выходы элементов И-ИЛИ группы и элементов И группы первого и второго дополнительных преобразователей код-частота через соответствующие дополнительные элементы И блокировки соединены соответственно со вторыми входами счетчика результата второго и первого основных преобразователей код-частота, в каждый из основных преобразователей, код-частота введена группа элементов И, причем выходы старших разрядов счетчика результата соединены с первыми входами элементов И группы, вторые входы элементов И групп обоих основных и дополнительных преобразователей код-частота соединены со вторым выходом генератора тактовых импульсов, выходы элементов И группы первого и второго основных преобразователей код-частота через соответствующие элементы И блокировки соединены с первыми входами счетчика результата, соответственно, второго и первого основных преобразователей код-частота, вторые входы элементов И-ИЛИ группы обоих дополнительных преобразователей код-частота соединены с соответствующими выходами развертывающего счетчика, выходы переноса счетчика результата первого и второго основных преобразователей код-частота соединены, соответственно, со входами счетчиков результата первого и второго дополнительных преобразователей код-частота управляющие входы дополнительных элементов И блокировки соединены со вторым выходом блока сравнения.

Кроме того, в синусно-косинусный функциональный преобразователь дополнительно в каждый счетчик результатов, включены в качестве самых младших (2n+1)-ых разрядов (n-разрядность результата) одноразрядные двоичные счетчики, логические элементы И блокировки, логические элементы И-ИЛИ, по входу связанные с выходом одноразрядных счетчиков, входы которых связаны с выходами логических элементов И блокировки, причем вход логического элемента И (2n+1)-го разряда каждой группы соединен с инверсным выходом самого старшего разряда одноименного счетчика результата синуса или косинуса.

Это является новым техническим решением в технике функциональных преобразований, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить достоверность (точность) выходного результата.

Предложенное устройство для вычисления функций промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

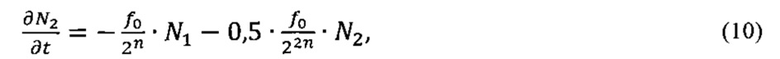

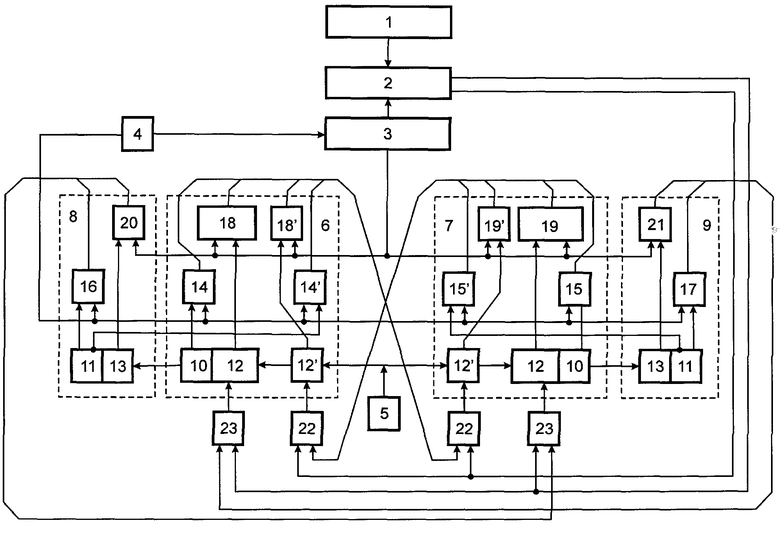

На чертеже представлена структурная схема предложенного синусно-косинусного функционального преобразователя.

Синусно-косинусный функциональный преобразователь содержит регистр 1 аргумента, блок 2 сравнения, развертывающий счетчик 3, генератор 4 тактовых импульсов, блок 5 управления и установки начальных условий, основные преобразователи 6 и 7 код-частота (точного отсчета), дополнительные преобразователи 8 и 9 код-частота (грубого отсчета), старшие 10 и 11 и младшие 12 и 13 разряды счетчиков результата, группы элементов 14-17 И, группы элементов 18-21 И-ИЛИ элементы 22 И блокировки, дополнительные элементы 23 И блокировки.

Кроме того, преобразователь содержит два одноразрядных двоичных счетчика 12/, два логических элемента И 14/ и 15/, два логических элемента И-ИЛИ 18/ и 19/.

В основу принципа функционирования предлагаемого преобразователя положены формулы, обеспечивающие повышенную точность за счет численного интегрирования дифуравнений по методу трапеций [Булатникова И.Н. Целочисленные алгоритмы генерации гармонических сигналов // Изв. вузов, Северо-Кавказский регион, Техн. наук, 2005, №3, с. 13-17].

Их сущность заключается в следующем.

Обозначим  и

и  . М - масштабный коэффициент М=2n, i - величина 2-n в масштабе 1:М.

. М - масштабный коэффициент М=2n, i - величина 2-n в масштабе 1:М.

Тогда приращения величин Si и Qi на единичном интервале (i, i+1)

будут

Формулы (1) и (2) получены на основе усреднения производных в начале и в конце единичного интервала. При этом учтено, что (sinx)/=cosx, (cosx)/=-sinx.

Упрощая, имеем систему уравнений

Решая ее относительно ΔSi и ΔCi, получаем

Учтя, что 4М2>>1, разделим на 4М2 выражения (5) и (6)

Окончательно учтя, что М=2n, имеем

где N1 - содержимое счетчика результата первого преобразователя "код-частота", N2 - содержимое счетчика результата второго преобразователя "код-частота",  - частота генератора 4 тактовых импульсов, n - разрядность кодов аргумента и функций.

- частота генератора 4 тактовых импульсов, n - разрядность кодов аргумента и функций.

Синусно-косинусный функциональный преобразователь работает следующим образом.

Предварительно с помощью блока 5 управления и установки начальных условий осуществляется начальная установка счетчиков результата основных 6, 7 и дополнительных 8, 9 преобразователей код-частота. Затем на регистр 1 аргумента записывается двоичный код аргумента X, после чего включается генератор 4 тактовых импульсов. Дальнейшая работа устройства проходит в два этапа.

На первом этапе - этапе обработки грубого отсчета (ГО) - многосимвольные частотно-импульсные последовательности с выходов основных 6, 7 и дополнительных 8, 9 преобразователей код-частота поступают соответственно на первые и вторые входы счетчиков результата основных 6, 7 преобразователей код-частота. Обработка ГО заканчивается по сигналу с блока 2 сравнения при совпадении кодов в развертывающем счетчике 3 и в старших разрядах регистра 1 аргумента. По этому сигналу отключаются вторые входы счетчиков результата основных 6, 7 преобразователей код-частота с помощью дополнительных элементов 23 И блокировки и начинается второй этап - этап обработки точного отсчета (ТО). При этом работают только основные преобразователи 6 и 7 код-частота.

Работа устройства заканчивается по сигналу из блока 2 сравнения при совпадении кодов в развертывающем счетчике 3 и в младших разрядах регистра 1 аргумента.

В результате в счетчиках результата образуется синус X и косинус X.

В работе преобразователя участвуют одноразрядные двоичные счетчики 12/, логические элементы И 14/ и 15/, а также логические элементы И-ИЛИ 18/ и 19/, которые встроены в группы первого и второго основных преобразователей 6 и 7 код-частота (точного отсчета).

Таким образом, данный преобразователь обеспечивает более точное преобразование цифровых значений синуса и косинуса для заданного значения их аргумента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный цифровой преобразователь | 2016 |

|

RU2625609C1 |

| Синусно-косинусный функциональный преобразователь | 1976 |

|

SU732884A1 |

| Синусно-косинусный преобразователь | 1987 |

|

SU1462367A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2020752C1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ | 1973 |

|

SU389517A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1267620A1 |

| Цифровой синусно-косинусный преобразователь | 1978 |

|

SU800923A1 |

Изобретение относится к вычислительной технике, в частности к частотно-импульсным вычислительным устройствам. Технический результат заключается в повышении точности преобразования устройства. Синусно-косинусный функциональный преобразователь содержит регистр аргумента, блок сравнения, развертывающий счетчик, генератор тактовых импульсов, блок управления и установки начальных условий, два основных и два дополнительных преобразователя код-частота, два счетчика результата, группы элементов И и И-ИЛИ, элементы И и дополнительные элементы И блокировки. При этом в основные преобразователи включены два одноразрядных двоичных счетчика в качестве самых младших, (2n+1)-х разрядов, логические элементы И и И-ИЛИ. 1 ил.

Синусно-косинусный функциональный преобразователь, содержащий регистр аргумента, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов развертывающего счетчика, вход которого соединен с первым выходом генератора тактовых импульсов, два основных преобразователя код-частота, каждый из которых содержит счетчик результата и группу элементов И-ИЛИ, причем выходы счетчика результата соединены с первыми входами элементов И-ИЛИ группы, вторые входы которых соединены с второй группой выходов развертывающего счетчика, выходы элементов И-ИЛИ группы первого и второго основных преобразователей код-частота через соответствующие элементы И блокировки соединены соответственно с первыми входами счетчиков результата второго и первого основных преобразователей код-частота, управляющие входы которых соединены с выходами блока управления и установки начальных условий, управляющие входы элементов И блокировки соединены с первым выходом блока сравнения, кроме того, в него введены два дополнительных преобразователя код-частота, каждый из которых содержит счетчик результата, группу элементов И-ИЛИ и группу элементов И, причем выходы старших и младших разрядов счетчика результата соединены, соответственно, с первыми входами элементов И группы и элементов И-ИЛИ группы, выходы элементов И-ИЛИ группы и элементов И группы первого и второго дополнительных преобразователей код-частота через соответствующие дополнительные элементы И блокировки соединены, соответственно, со вторыми входами счетчика результата второго и первого основных преобразователей код-частота, в каждый из основных преобразователей код-частота введена группа элементов И, причем выходы старших разрядов счетчика результата соединены с первыми входами элементов И группы, вторые входы элементов И групп обоих основных и дополнительных преобразователей код-частота соединены со вторым выходом генератора тактовых импульсов, выходы элементов И группы первого и второго основных преобразователей код-частота через соответствующие элементы И блокировки соединены с первыми входами счетчика результата, соответственно, второго и первого основных преобразователей код-частота, вторые входы элементов И-ИЛИ группы обоих дополнительных преобразователей код-частота соединены с соответствующими выходами развертывающего счетчика, выходы переноса счетчика результата первого и второго основных преобразователей код-частота соединены, соответственно, со входами счетчиков результата первого и второго дополнительных преобразователей код-частота, управляющие входы дополнительных элементов И блокировки соединены со вторым выходом блока сравнения, отличающийся тем, что дополнительно содержит в каждом счетчике результатов в качестве самых младших, (2n+1)-х разрядов одноразрядные двоичные счетчики, логические элементы И, логические элементы И блокировки, логические элементы И-ИЛИ, по входу связанные с выходом одноразрядных счетчиков, входы которых связаны с выходами логических элементов И блокировки, причем вход логического элемента И (2n+1)-го разряда каждой группы соединен с инверсным выходом старшего разряда одноименного счетчика результата синуса и косинуса.

| Синусно-косинусный функциональный преобразователь | 1976 |

|

SU732884A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2017-09-29—Публикация

2016-07-05—Подача