pa подынтеграл л1ой функции, а второй выход - с первым входом узла умножения и с первым входом первого элемента ИЛИ, выход которого соединен с информационным Входом регистра подынтегральной функции, выход которого соединен с третьим входом сумматора подынтегральной функции, выход уз.;а умножения соединен с первым входом сумматора остатка интеграла, первый вход которого соединен через второй элемент задержки с вторым входом сумматора остатка интеграла, а второй выход - с входом первого элемента задержки узла квантования и первым входом седьмого элемента И узля квантования, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным входом регистра остатка интеграла, выход 1 оторого соединен с третьим вхбдом сумматора остатка интеграла, второй вход первого элемента ИЛИ и второй вход второго элемента ИЛИ соединены соответственно с первым и вторым выходами коммутатора, первый, второй и третий входы которого соединены соответственно с входом выбора номера решающего блока, входом начального значения подынтегральной функции и входом начального значения остатка интеграла решающего блоки, первые входы первого и второго элементов И узла масштабирования подключены к входам соответственно положительных и отрицательных приращений подынтегральной функции решающего блока, вторые входы первого и второго элементов И узла масштабирования соединены с входом масштабного сигнала решающего блока, второй вход узла умножения соединен с входом приращения переменной интег1 1рования решающего блока, второй вход седьмого элемента И узла квантования подключен ,к входу сигнала выделения остатка интеграла решающего блока, первый вход второго элемента ИЛИ узла масштабирования , вторьте входы первого и второго элементов ИЛИ узла квантования и входы установки нуля регистра подынтегральной функции и регистра ос1атка интеграла соединены с входом сброса решающего блока, второй вход второго элемента ИЛИ узла мас14

11

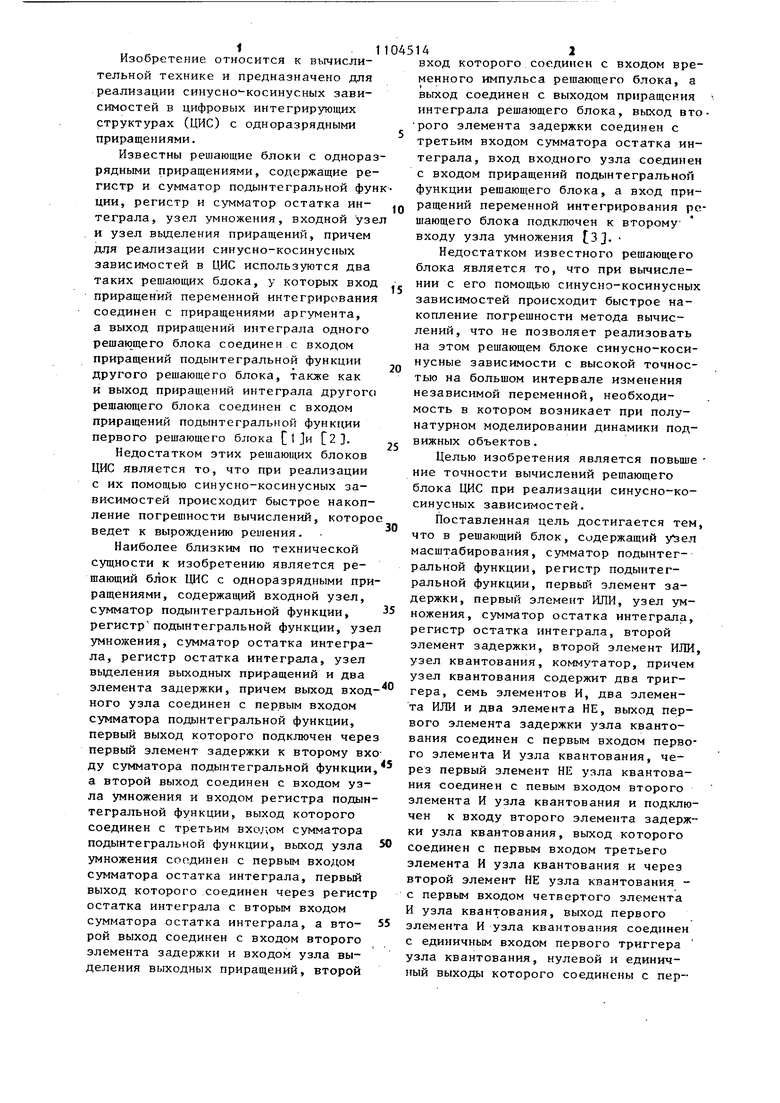

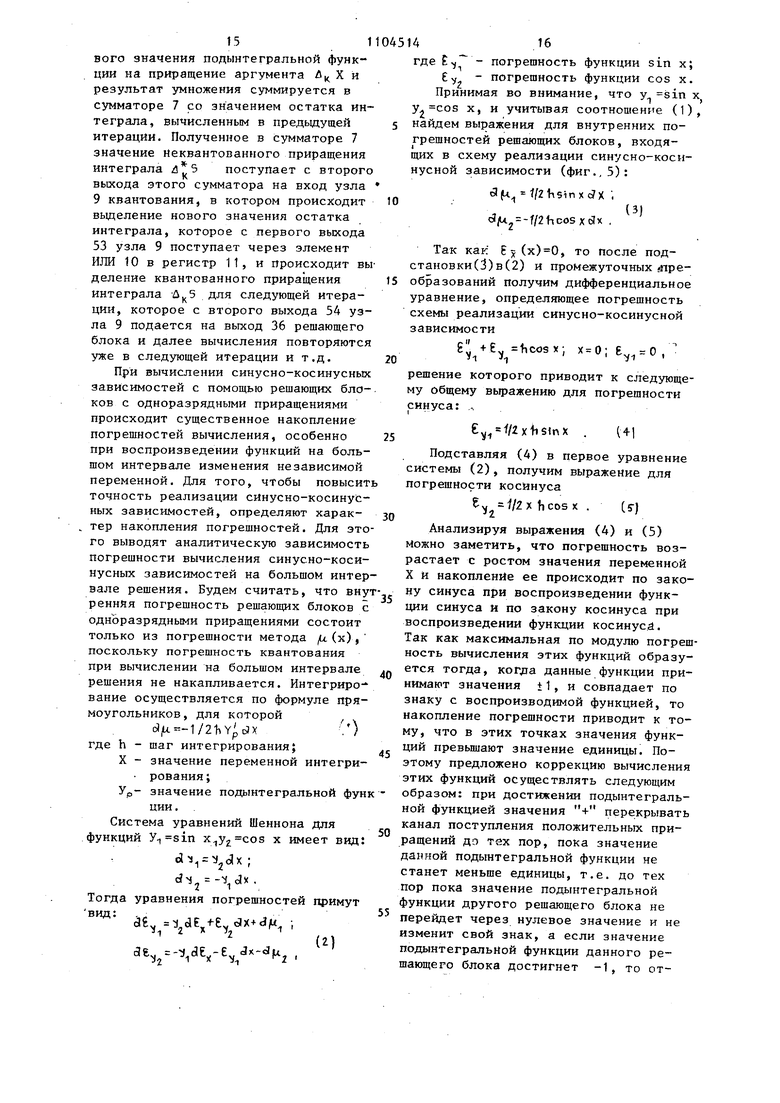

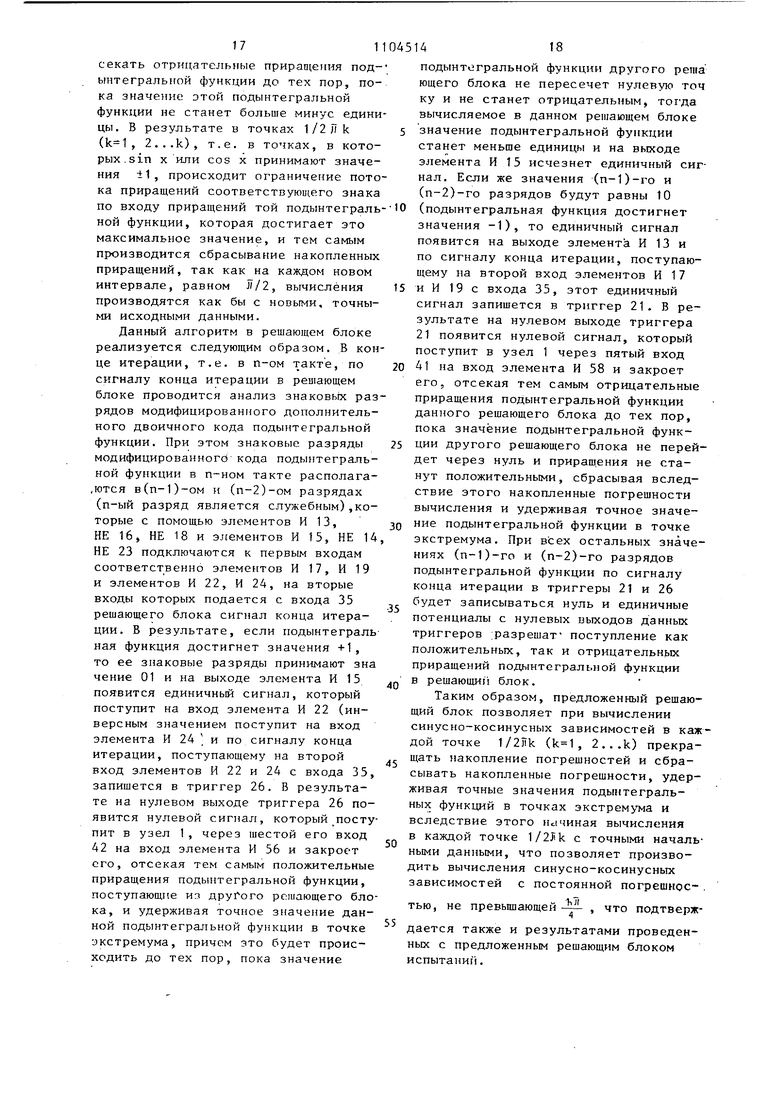

штабирования и вторые входы первогочетвертого элементов И узла квантования соединены с входом конца итера ции решающего блока, выходы пятого и шестого элементов И узла квантования соединены соответственно с выходами положительных и отр П ;ательиых приращений интеграпа решающего блока, отличающий ся тем, что, с целью повышения точности вычислений при реализации синусно-косинусных зависимостей, в него дополнительно введены третий и четвертый элементы ИЛИ, четыре элемента НЕ, шесть элементов И, два RS-триггера, причем единичный выход (п-1)-го разряда регистра подынтегральной функции соединен с первым входом первого элемента И и через первый элемент НЕ - с первым входом второго элемента И, выход (п-2)-го разряда регистра подынтегральной функции соединен с вторым входом второго элемента И и через второй элемент НЕ - с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента И и через третий элемент НЕ - с первым входом четвертого элемента И, выход которого соединен с Первым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом первого RS-триггера, единичный вход которого соединен с выходом третьего элемента И, а нулевой выход с третьим входом второго элемента И узла масштабирования, выход второго элемента И соединен с первым входом пятого элемента И и через четвертый элемент НЕ - с первым входом шестого элемента И( выход которого соединен с первым входом четвертого элемента И, выход которого соединен с нулевым входом второго RS-триггера, единичный вход которого соединен с выходом пятого элемента И, а нулевой выход - с третьим входом первого элемента И узла масштабирования, второй вход третьего элемента ИЛИ и второй вход четвертого элемента ИЛИ соединен с входом сброса решающего блока, а вторые входы третьего, четвертого, пятого и шестого элементов И соединены с входом конца итерации решающего блока. Изобретение относится к вычислительной технике и предназначено для реализации синусно-косинусных зависимостей в цифровых интегриругощих структурах (ЦИС) с одноразрядными приращениями. Известны решающие блоки с однора рядными приращениями, содержа:щие регистр и сумматор подынтегральной фун ции, регистр и сумматор остатка интеграла, узел умножения, входной узе и узел вьщеления приращений, причем для реализации синусно-косинусных зависимостей в ЦИС используются два таких решающих блока, у которых вход приращений переменной интегрирования соединен с приращениями аргумента, а выход приращений интеграла одного решающего блока соединен с входом приращений подынтегральной функции другого решающего блока, также как и выход приращений интеграла другого решающего блока соединен с входом приращений подынтегральной функции первого решающего блока С 1Jn С2. Недостатком этих решающих блоков ЦИС является то, что при реализации с их помощью синусно-косинусных зависимостей происходит быстрое накопление погрешности вычислений, которо ведет к вырож/дению решения. Наиболее близким по технической сущности к изобретению является решающий блок ЦИС с одноразрядными при ращениями, содержащий входной узел, сумматор подынтегральной функции, регистр подынтегральной функции, узе умножения, сумматор остатка интеграла, регистр остатка интеграла, узел выделения выходных приращений и два элемента задержки, причем выход вход кого узла соединен с первым входом сумматора подынтегральной функции, первый выход которого подключен чере первый элемент задержки к второму вх ду сумматора подынтегральной функции а второй выход соединен с входом узла умножения и входом регистра подын тегральной функции, выход которого соединен с третьим вхо;;ом сумматора подынтегральной функции, выход узла умножения соединен с первым входом сумматора остатка интеграла, первьй выход которого соединен через регист остатка интеграла с вторым входом сумматора остатка интеграла, а второй выход соединен с входом второго элемента задержки и входом узла выделения выходных приращений, второй 142 вход которого соединен с входом временного импульса решающего блока, а выход соединен с выходом приращения интеграла решающего блока, выход второго элемента задержки соединен с третьим входом сумматора остатка интеграла, вход входного узла соединен с входом приращений подынтегральной функции решающего блока, а вход приращений переменной интегрирования решающего блока подключен к второму входу узла умножения З. Недостатком известного решающего блока является то, что при вычислении с его помощью синусно-косинусных зависимостей происходит быстрое накопление погрешности метода вычислений, что не позволяет реализовать на этом решающем блоке синусно-косинусные зависимости с высокой точностью на большом интервале изменения независимой переменной, необходимость в котором возникает при полунатурном моделировании динамики подвижных обьектов. Целью изобретения является повьш1е ние точности вычислений решающего блока ЦИС при реализации синусно-косинусных зависимостей. Поставленная цель достигается тем, что в решающий блок, содержащий узел масштабирования, сумматор подынтегральной функции, регистр подынтегральной функции, первый элемент задержки, первый элемент ИЛИ, узел умножения, сумматор остатка интеграла, регистр остатка интеграла, второй элемент задержки, второй элемент ИЛИ, узел квантования, коммутатор, причем узел квантования содержит два три1- гера, семь элементов И, два элемента ИЛИ и два элемента НЕ, выход первого элемента задержки узла квантования соединен с первым входом первого элемента И узла квантования, через первый элемент НЕ узла квантования соединен с певым входом второго элемента И узла квантования и подключен к входу второго элемента задержки узла квантования, выход которого соединен с первым входом третьего элемента И узла квантования и через второй элемент НЕ узла квантования с первым входом четвертого элемента И узла квантования, выход первого элемента И узла квантования соединен с единичным входом первого триггера узла квантования, нулевой и единичный выходы которого соединены с первыми входами соответственно пятого и шестого элементов И узла квантования, выход второго элемента И узла квантования соединен с первым входом первого элемента ИЛИ узла квантоваНИН, выход которого соединен с нулевым входом первого триггера узла квантования, выход третьего элемента И узла квантования соединен с единичным входом второго триггера узла квантования, единичный выход которого соединен с вторыми входами пятого и шестого элементов И узла квантования, а нулевой вход подключен к выходу второго элемента ИЛИ узла квантования, первый вход которого соединен с выходом четвертого элемента И узла квантования, узел масштабирования содержит триггер, два элемента И и два элемента ИЛИ, причем выход первого элемента И узла масштабирования соединен с первым входом первого элемента ИЛИ узла масштабирования, выход второго элемента И узла масштабирования соединен с единичным входом триггера узла масштабирования, единичный выход которого подключен к второму входу первого элемента ИЛИ узла масштабирования, а нулевой вход подключен к выходу второго элемента ИЛИ узла масштабирования, выход первого элемента ИЛИ узла масштабирования , соединен с первым входом сумматора подынтегральной функции, первый выход которого соединен через первый элемент задержки с вторым входом сумматора подынтегральной функции, а второй выход - с первым входом узла умножения и с перлым входом первого элемента ИЛИ, выход которого соединен с информационным входом регистра подынтегральной функции, выход которого соединен с третьим входом сумматора подынтегральной функции, выход узла умножения соединен с первым входом сумматора остатка интеграла, первый выход которого соединен через второй элемент задержки с вторым входом сумматсгра остатка интеграла, а второй выход - с входом первого элемента задержки узла квантования и первым входом седьмого элемента И узла квантования, выход которого соединен с первым входом второго элемента ИЛИ, рыход которого соединен с информационным входом регистра остатка интеграла, выход которого соединен с третьим входом сумматора остатка интеграла, второй вход первого элемента ИЛИ и второй пход второго элемента ИЛИ соединены соответственно с первым и вторым выходами коммутатора первый, второй и третий входы которого соединены соответственно с входом Выбора номера решающего блока, входом начального значения подынтегральной функции и входом начального значения остатка интеграла решающего блока первые входы первого и второго элементов И узла масштабирования подключены к входам соответственно положительных и отрицательных приращений подынтегральной функции решающего блока, BTOpf ie входы первого и второго элемента И узла масштабирова ния соединены с входом масштабного сигнала решающего блока, второй вход узла умножения соединен с входом приращения переменной интегрирования решающего блока, второй вход седьмог элемента И узла квантования подключен к входу сигнала выделения остатка решающего блока, первый вход второго элемента ИЛИ узла масштабирования, вторые входы первого и второго элементов ИЛИ узла квантования и входы установки нуля регистра подынтегральной функции и регистра остатка интеграла соединены с входом сброса решающего блока, второй вход второго элемента ИЛИ узла масштабирования и вторые входы первого-четвертого элементов И узла квантования соединены с входом конца итерации решающего блока выходы пятого и шестого элементов И квантования соединены соответственно с выходами положительных и отрицательных приращений интеграла решающего блока, дополнительно введены третий и четвертый элементы ИЛИ, четыре элемента НЕ, шесть элементов И и два RS-триггера, причем единичный выход (n-l)-ro разряда регистра подынтегральной функции соединен с первым входом первого элемента И и через первый элемент НЕ - с первым входом второго элемента И, выход (п-2)го разряда регистра подынтегральной функции соединен с вторым входом второго элемента И и через второй элемент НЕ - с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента И и -через третий элемент НЕ- с первым входом четвертого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которог соединен с нулевым входом первого S . 11 К8-триггерй, единичный вход которого соединен с выходом, третьего элемента И, а нулевой выход - с третьим входом второго элемента И узла масштаби рования, выход второго элемента И соединен с первым входом пятого элемента И и через четвёртый элемент НЕ - с первым входом шестого элемента И, выход которого соединен с первым вхо дом четвертого элемента ИЛИ, выход которого соединен с нулевым входом второго RS-триггера, единичный вход которого соединен с выходом пятого элемента И, а нулевой выход - с третьим входом первого элемента И узла Масштабирования, второй вход третьего элемента ИЛИ и второй вход четвертого элемента ИЛИ соединены с вхо дом сброса решающего блока, а вторые входы третьего, четвертого, пятого и шестого элементов И соединены с входом конца итерации решающего блока. На фиг, 1 представлена функционал ная схема решающего блока цифровой интегрирующей структуры; на фиг. 2 функциональная схема узла масштабирования; на фиг. 3 - схема коммутатора; на фиг. 4 - схема узла квантования; на фиг. 5 - схема объединения решающих блоков для вычисления синусно-косинусных преобразований. В состав решающего блока (фиг. 1) входят узел 1 масштабирования, сумматор 2 подынтегральной функции, первый элемент 3 задержки, узел 4 умножения, перйый элемент ИЛИ 5, регистр 6подынтегральной функции, сумматор 7остатка интеграла, второй элемент 8 задержки, узел 9 квантования, второй элемент ИЛИ 10, регистр 11 остатка интеграла, коммутатор 12, первый элемент И 13, первьй элемент НЕ 14, второй элемент И 15, второй элемент НЕ 16, третий .элемент И 17, третий элемент НЕ 18, четвертый элемент И 19, третий элемент ИЛИ 20, первый триггер 21, пятый элемент И 22, четвертый элемент НЕ 23, шестой элемент И 24, четвертый элемент ИЛИ 25, второй триггер 26, вход 27 выбора номера решающего блока, вход 28 начального значения подынтегральной функции решающего блока,вход 29 начального значения остатка интеграла решающего блока, вход 30 приращения подынтегральной функции решающего блока, вход 31 масштабного сигнала решающего блока, вход 32 приращения переменвходом узла 4 умножения и с первым входом первого элемента ИЛИ 5, выход которого соединен с информационным входом регистра 6 подынтегральной функции, выход которого соединен с третьим входом сумматора 2 подынтегральной функции. Выход узла 4 умножения соединен с первым входом сумматора 7 остатка интеграла, первый выход которого соединен через второй элемент 8 задержки с вторым входом сумматора 7 остатка интеграла, а второй выход - с первым входом узла 9 квантования, первьй выход которого

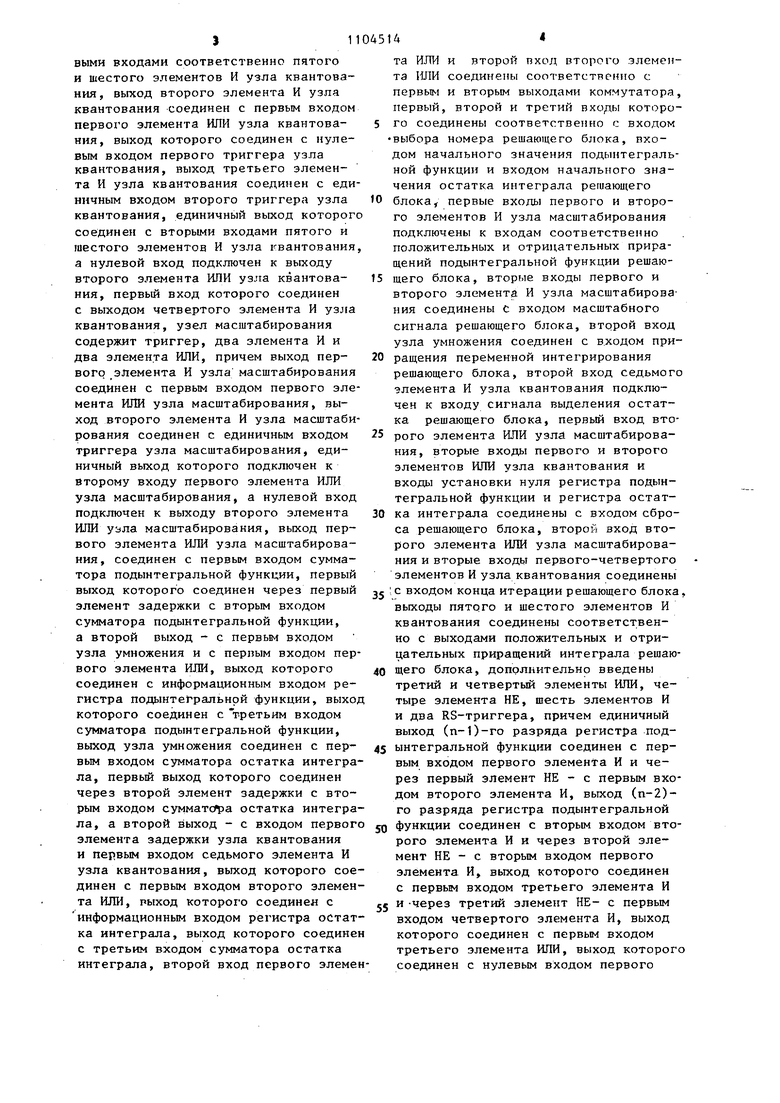

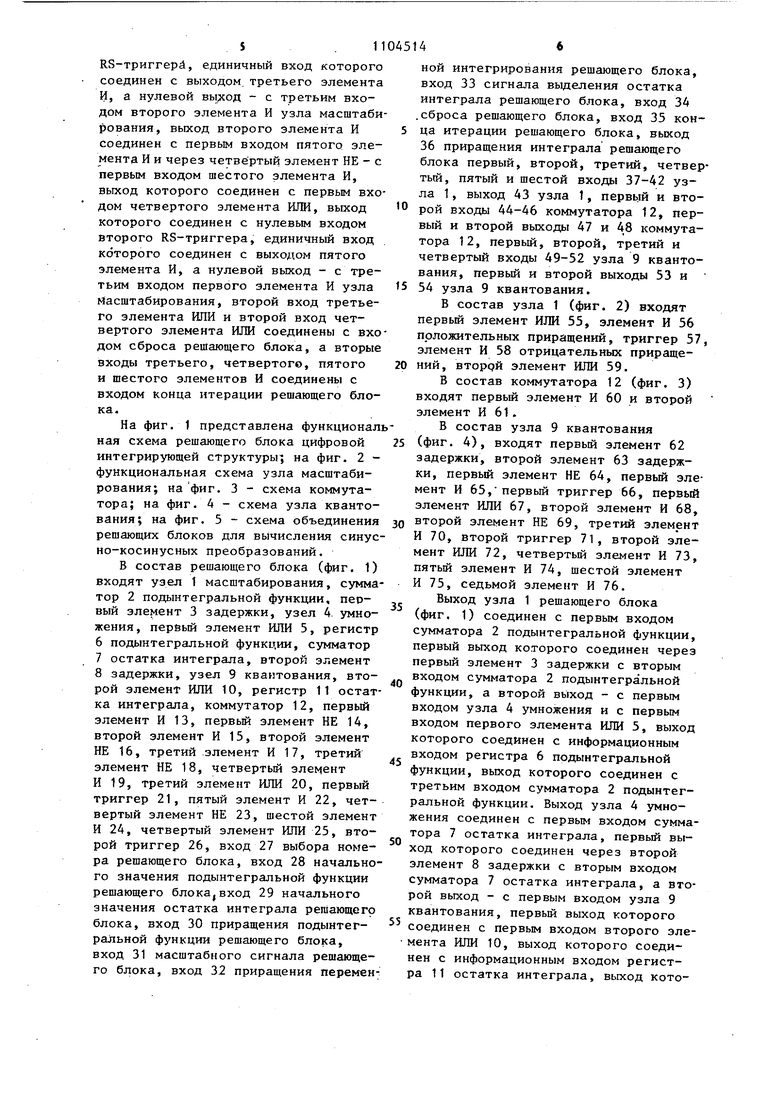

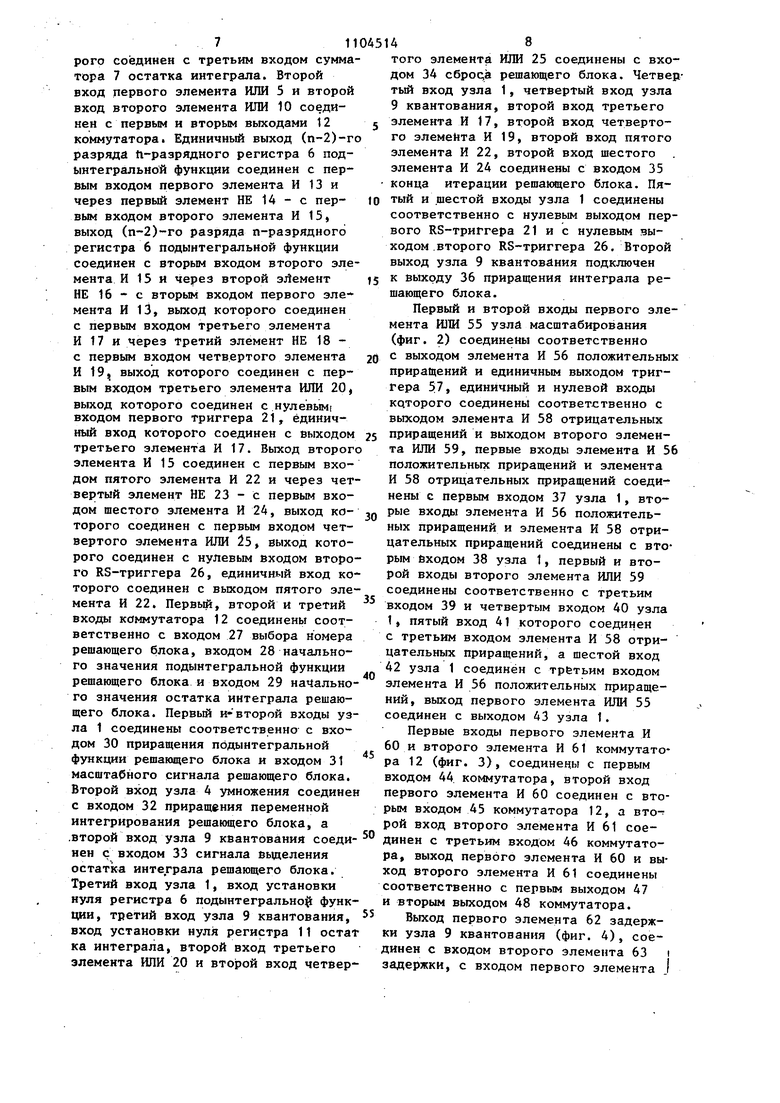

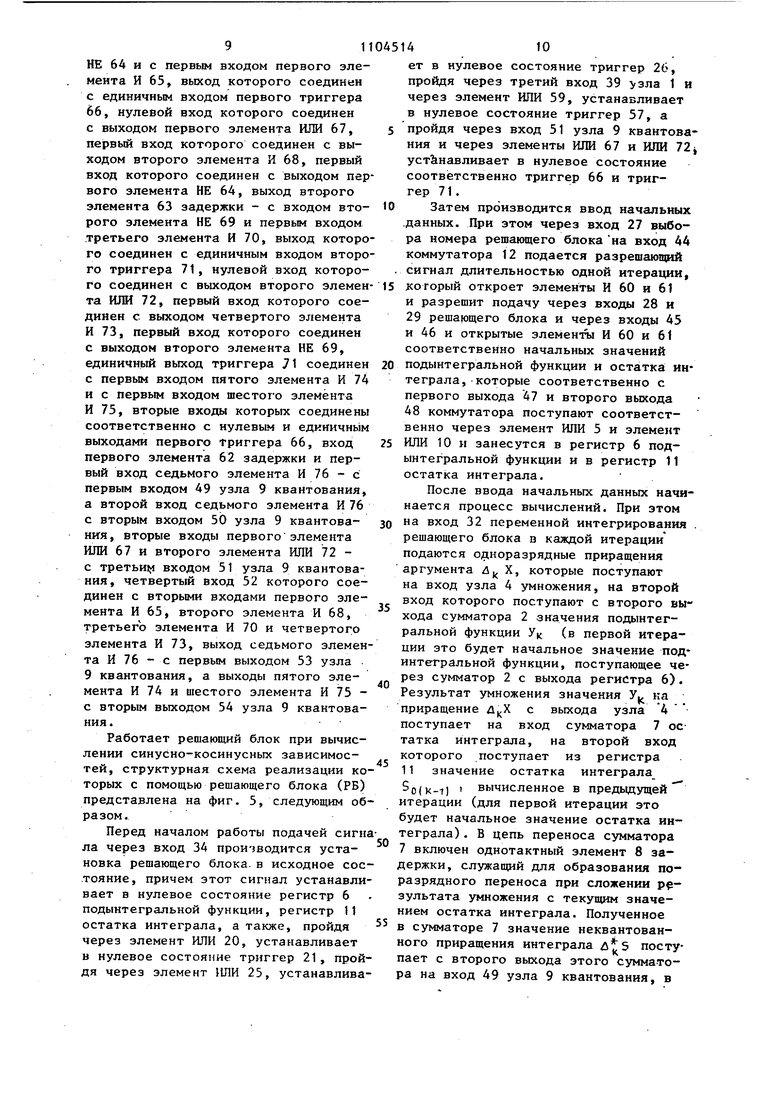

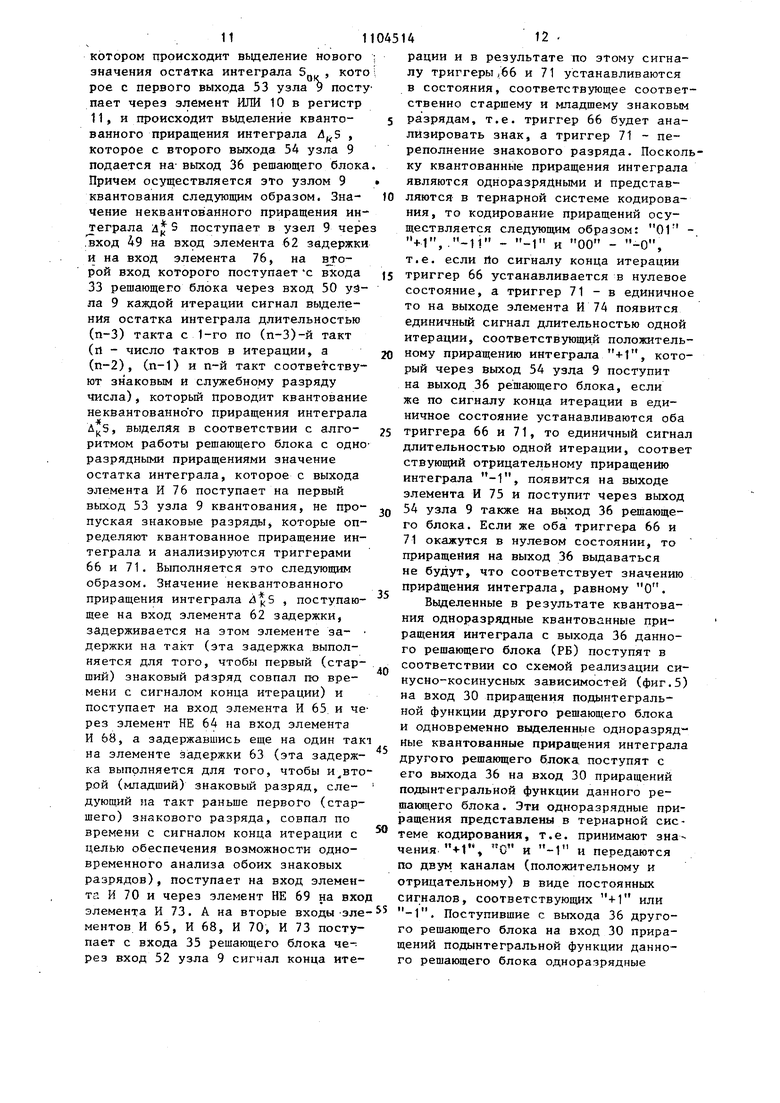

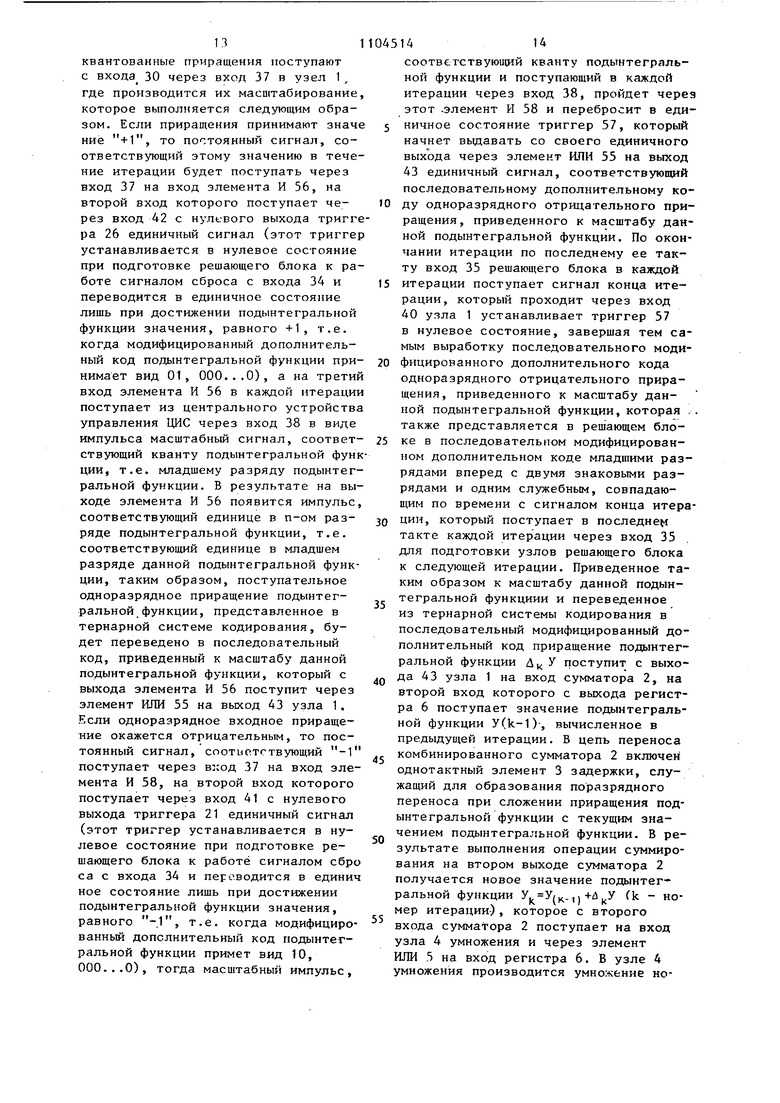

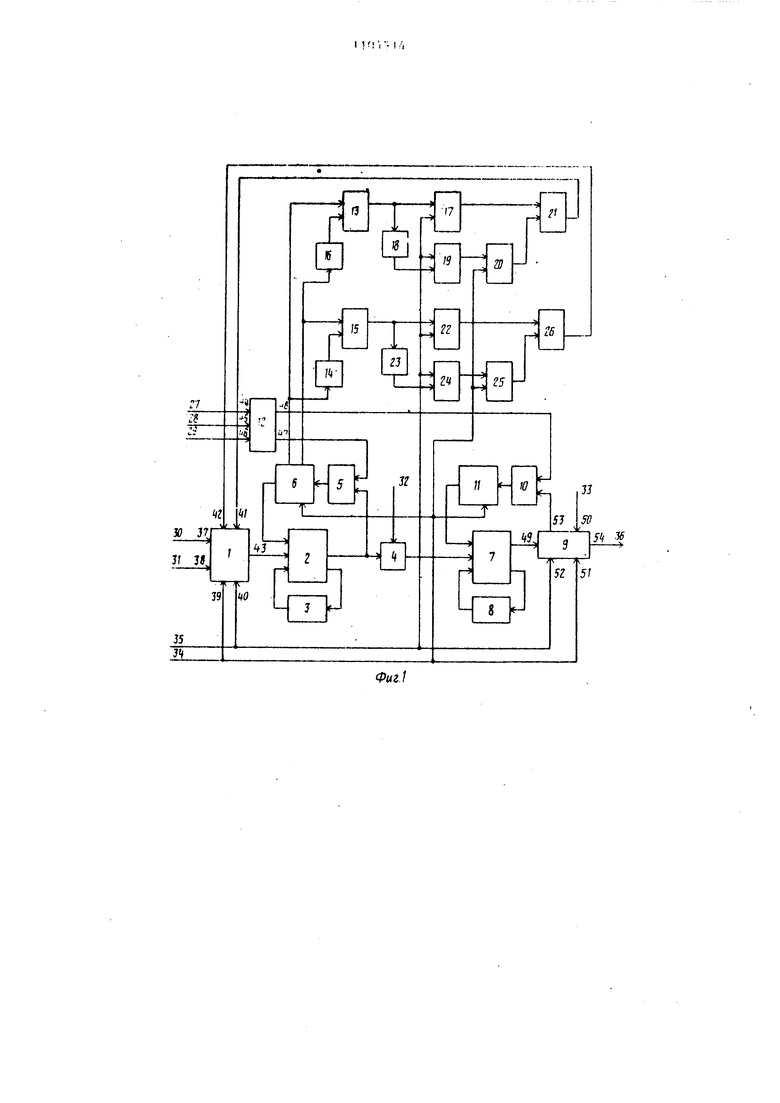

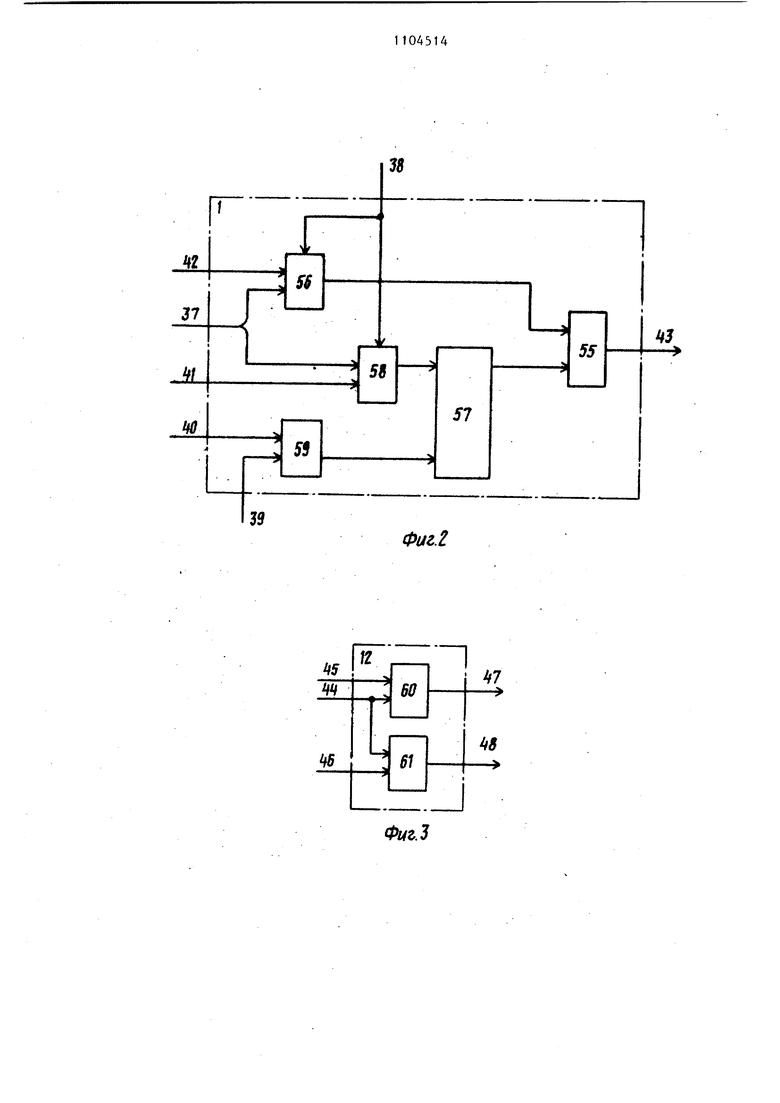

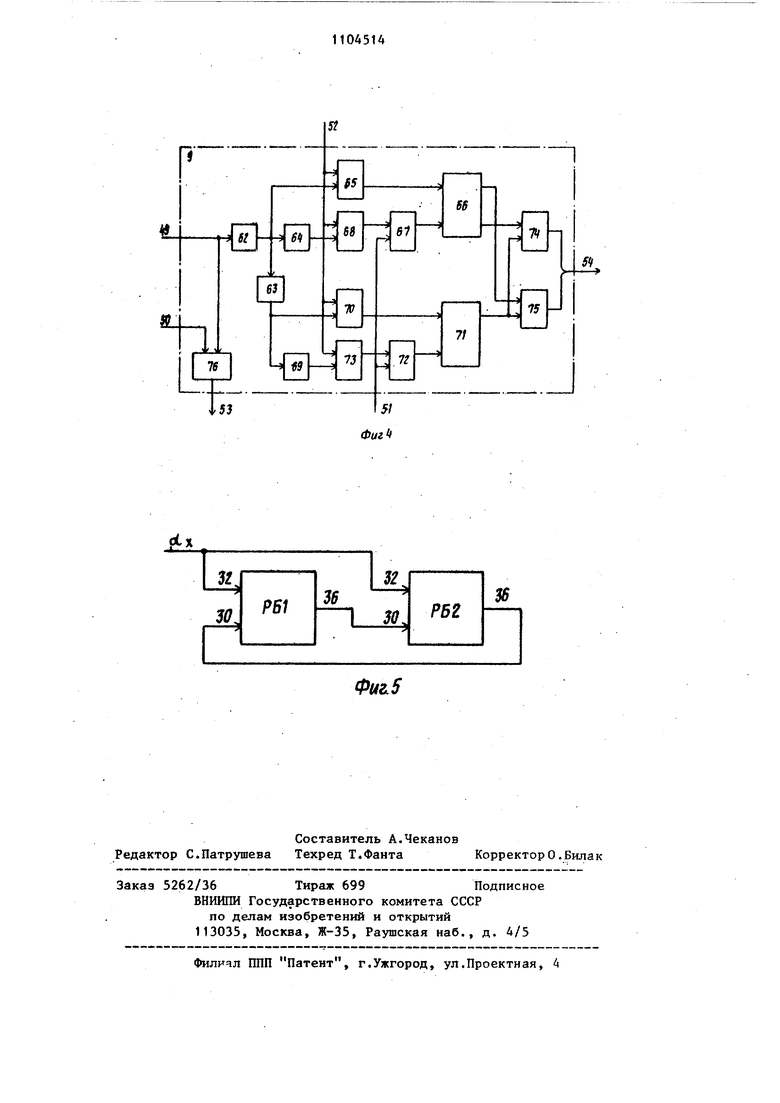

S соединен с первым входом второго элемента ИЛИ 10, выход которого соединен с информационным входом регистра 11 остатка интеграла, выход кото4ной интегрирования решающего блока, вход 33 сигнала выделения остатка интеграла решающего блока, вход 34 сброса решающего блока, вход 35 конца итерации решающего блока, выход 36 приращения интеграла решающего блока первый, второй, третий, четвертый, пятый и шестой входы 37-42 узла 1, выход 43 узла 1, первый и второй входы 44-46 коммутатора 12, первый и второй выходы 47 и 48 коммутатора 12, первый, второй, третий и четвертый входы 49-52 узла 9 квантования, первый и второй выходы 53 и 54 узла 9 квантования. В состав узла 1 (фиг. 2) входят первый элемент ИЛИ 55, элемент И 56 положительных приращений, триггер 57, элемент И 58 отрицательных приращеНИИ, вторрй элемент ИЛИ 59. В состав коммутатора 12 (фиг. 3) входят первый элемент И 60 и второй элемент И 61. В состав узла 9 квантования (фиг. 4), входят первый элемент 62 задержки, второй элемент 63 задержки, первый элемент НЕ 64, первый элемент И 65, первый триггер 66, первый элемент ИЛИ 67, второй элемент И 68, второй элемент НЕ 69, третий элемент И 70, второй триггер 71, второй элемент ИЛИ 72, четвертый элемент И 73, пятый элемент И 74, шестой элемент И 75, седьмой элемент И 76. Выход узла 1 решающего блока (фиг. 1) соединен с первым входом сумматора 2 подынтегральной функции, первый выход которого соединен через первый элемент 3 задержки с вторым входом сумматора 2 подынтегральной функции, а второй выход - с первым рого соединен с третьим входом сумматора 7 остатка интеграла. Второй вход первого элемента ИЛИ 5 и второй вход второго элемента ШШ 10 соединен с первым и вторым выходами 12 коммутатора. Единичный выход (п-2)-го разряда h-разрядного регистра 6 подынтегральной функции соединен с первым входом первого элемента И 13 и через первый элемент НЕ 14 - с первым входом второго элемента И 15, выход (п-2)-го разряда п-разрядного регистра 6 подынтегральной функции соединен с вторым входом второго эле мента И 15 и через второй эЛемент НЕ 16 - с вторым входом первого элемента И 13, выход которого соединен с первым входом третьего элемента И 17 и через третий элемент НЕ 18 с первым входом четвертого элемента И 19, выход которого соединен с первым входом третьего элемента ИЛИ 20, выход которого соединен с нулевым входом первого триггера 21, единичный вход которого соединен с выходом третьего элемента И 17. Выход второг элемента И 15 соединен с первым входом пятого элемента И 22 и через чет вертый элемент НЕ 23 - с первым входом шестого элемента И 24, выход которого соединен с первым входом четвертого элемента ИЛИ 25, выход которого соединен с нулевым входом второ го RS-триггера 26, единичный вход ко торого соединен с выходом пятого эле мента И 22. Первый, второй и третий входы коммутатора 12 соединены соответственно с входом 27 выбора номера решающего блока, входом 28 начального значения подынтегральной функции решающего блока и входом 29 начально го значения остатка интеграла решающего блока. Первый и-второй входы уз ла 1 соединены соответственно с входом 30 приращения подынтегральной функции решающего блока и входом 31 масштабного сигнала решающего блока. Второй вход узла 4 умножения соедине с входом 32 приращения переменной интегрирования решающего блока, а .второй вход узла 9 квантования соеди иен с входом 33 сигнала еьщеления остатка интеграла решающего блока. Третий вход узла 1, вход установки нуля регистра 6 подынтегрально функ ции, третий вход узла 9 квантования, вход установки нуля регистра 11 оста ка интеграла, второй вход третьего элемента ИЛИ 20 и второй вход четвер ТОГО элемента ИЛИ 25 соединены с входом 34 сброца решающего блока. Четвертый вход узла 1, четвертый вход узла 9 квантования, второй вход третьего элемента И 17, второй вход четвертого элемейта И 19, второй вход пятого элемента И 22, второй вход шестого элемента И 24 соединены с входом 35 конца итерации решающего блока. Пятый и шестой входы узла 1 соединены соответственно с нулевым выходом первого RS-триггера 21 и с нулевым выходом .второго RS-триггера 26. Второй выход узла 9 квантования подключен к выходу 36 приращения интеграла решающего блока. Первый и второй входы первого элемента ИЛИ 55 узла масштабирования (фиг. 2) соединены соответственно с выходом элемента И 56 положительных приращений и единичным выходом триггера 57, единичный и нулевой входы которого соединены соответственно с выходом элемента И 58 отрицательных приращений и выходом второго элемента ИЛИ 59, первые входы элемента И 56 положительных приращений и элемента И 58 отрицательных приращений соединены с первым входом 37 узла 1, вторые входы элемента И 56 положительных приращений и элемента И 58 отрицательных приращений соединены с вторым Входом 38 узла 1, первый и второй входы второго элемента ИЛИ 59 соединены соответственно с третьим входом 39 и четвертым входом 40 узла 1, пятый вход 41 которого соединен с третьим входом элемента И 58 отрицательных приращений, а шестой вход 42 узла 1 соединён с третьим входом элемента И 56 положительных приращений, выход первого элемента ИЛИ 55 соединен с выходом 43 узла 1. Первые входы первого элемента И 60 и второго элемента И 61 коммутатора 12 (фиг. 3), соединены с первым входом 44 коммутатора, второй вход первого элемента И 60 соединен с вторым входом 45 коммутатора 12, а второй вход второго элемента И 61 соединен с третьим входом 46 коммутатора, выход первого элемента И 60 и выход второго элемента И 61 соединены соответственно с первым выходом 47 и вторым выходом 48 коммутатора. Выход первого элемента 62 задержки узла 9 квантования (фиг. 4), соединен с входом второго элемента 63 i задержки, с входом первого элемента J НЕ 64 и с первым входом первого элемента И 65, выход которого соединен с единичным входом первого триггера 66, нулевой вход которого соединен с выходом первого элемента ИЛИ 67, первый вход которого соединен с выходом второго элемента И 68, первый вход которого соединен с выходом пер вого элемента НЕ 64, выход второго элемента 63 задержки - с входом второго элемента НЕ 69 и первым входом третьего элемента И 70, выход которо го соединен с единичным входом второ го триггера 71, нулевой вход которого соединен с выходом второго элемен та ИЛИ 72, первый вход которого соединен с выходом четвертого элемента И 73, первый вход которого соединен с выходом второго элемента НЕ 69, единичный выход триггера 71 соединен с первым входом пятого элемента И 74 и с первым входом шестого элемента И 75, вторые входы которых соединены соответственно с нулевым и единичным выходами первого триггера 66, вход первого элемента 62 задержки и первый вход седьмого элемента И 76 - с первым входом 49 узла 9 квантования, а второй вход седьмого элемента И 76 с вторым входом 50 уэла 9 квантования, вторые входы первого элемента ИЛИ 67 и второго элемента ИЛИ 72 с третьи входом 51 уэла 9 квантования, четвертый вход 52 которого соединен с вторыми входами первого элемента И 65, второго элемента И 68, третьего элемента И 70 и четвертого элемента И 73, выход седьмого элемен та И 76 - с первым выходом 53 узла 9 квантования, а выходы пятого элемента И 74 и шестого элемента И 75 с вторым выходом 54 узла 9 квантования. Работает решающий блок при вычислении синусно-косинусных зависимостей, структурная схема реализации ко торых с помощью решающего блока (РБ) представлена на фиг. 5, следующим об разом. Перед началом работы подачей сигн ла через вход 34 проичводится установка решающего блока, в исходное сос .тояние, причем этот сигнал устанавли вает в нулевое состояние регистр 6 подынтегральной функции, регистр 11 остатка интеграла, а также, пройдя через элемент ИЛИ 20, устанавливает в нулевое состояние триггер 21, прой дя через элемент ИЛИ 25, устанавлива ет в нулевое состояние триггер 26, пройдя через третий вход 39 узла 1 и через элемент ИЛИ 59, устанавливает в нулевое состояние триггер 57, а пройдя через вход 51 узла 9 квантования и через элементы ИЛИ 67 и ИЛИ 72 устанавливает в нулевое состояние соответственно триггер 66 и триггер 71. Затем производится ввод начальных .данных. При этом через вход 27 выбора номера решающего блока на вход 44 коммутатора 12 подается разрешающий сигнал длительностью одной итерации, который откроет элементы И 60 и 61 и разрешит подачу через входы 28 и 29 решающего блока и через входы 45 и 46 и открытые элементы И 60 и 61 соответственно начальных значений подынтегральной функции и остатка интеграла, которые соответственно с первого выхода 47 и второго выхода 48 коммутатора поступают соответственно через элемент ИЛИ 5 и элемент ИЛИ 10 и занесутся в регистр 6 подынтегральной функции и в регистр 11 остатка интеграла. После ввода начальных данных начинается процесс вычислений. При этом на вход 32 переменной интегрирования . решающего блока в каждой итерации подаются одноразрядные приращения аргумента Л, X, которые поступают на вход узла 4 умножения, на второй вход которого поступают с второго выхода сумматора 2 значения подынтегральной функции УК (в первой итерации это будет начальное значение подинтегральной функции, поступающее через сумматор 2 с выхода регистра 6). Результат умножения значения У. ка приращение Д,Х с выхода узла 4 поступает на вход сумматора 7 ос татка интеграла, на второй вход которого поступает из регистра 11 значение остатка интеграла So(x-7) 1 вычисленное в предыдущей итерации (для первой итерации это будет начальное значение остатка интеграла) . В цепь переноса сумматора 7 включен однотактный элемент 8 задержки, служащий для образования поразрядного переноса при сложении р зультата умножения с текущим значением остатка интеграла. Полученное в сумматоре 7 значение неквантованного приращения интеграла поступает с второго выхода этого сумматора на вход 49 узла 9 квантования, в котором происходит выделение нового значения остатка интеграла 5 , кото рое с первого выхода 53 узла 9 посту пает через элемент ИЛИ 10 в регистр 11, и происходит выделение квантованного приращения интеграла , которое с второго выхода 54 узла 9 подается на- выход 36 решающего блока Причем осуществляется это узлом 9 квантования следующим образом. Значение неквантованного приращения интеграла а 5 поступает в узел 9 чере ,1вход 49 на вход элемента 62 задержки и на вход элемента 76, на второй вход которого поступает с входа 33 решающего блока через вход 50 узла 9 каждой итерации сигнал выделения остатка интеграла длительностью (п-3) такта с 1-го по (п-З)-й такт (п - ЧИСЛО тактов в итерации, а (п-2), (п-1) и п-й такт соответствуют знаковым и служебному разряду числа), который проводит квантование неквантованного приращения интеграла , выделяя в соответствии с алгоритмом работы решающего блока с одно разрядными приращениями значение остатка интеграла, которое с выхода элемента И 76 поступает на первый выход 53 узла 9 квантования, не пропуская знаковые разряды которые определяют квантованное приращение интеграла и анализируются триггерами 66 и 71. Выполняется это следующим образом. Значение неквантованного приращения интеграла 5 , поступающее на вход элемента 62 задержки, задерживается на этом элементе задержки на такт (эта задержка выполняется для того, чтобы первый (старший) знаковый разряд совпал по времени с сигналом конца итерации) и поступает на вход элемента И 65 и че рез элемент НЕ 64 на вход элемента И 68, а задержавшись еще на один так на элементе задержки 63 (эта задержка выполняется для того, чтобы рой (младший) знаковый разряд, еледующий на такт раньше первого (старшего) знакового разряда, совпал по времени с сигналом конца итерации с целью обеспечения возможности одновременного анализа обоих знаковых разрядов), поступает на вход элемента И 70 и через элемент НЕ 69 на вхо элемента И 73. А на вторые входы-эле ментов И 65, И 68, И 70, И 73 поступает с входа 35 решающего блока через вход 52 узла 9 сигнал конца итерации и в результате по этому сигналу триггеры/66 и 71 устанавливаются в состояния, соответствующее соответственно старшему и младшему знаковым разрядам, т.е. триггер 66 будет анализировать знак, а триггер 71 - переполнение знакового разряда. Поскольку квантованные приращения интеграла являются одноразрядными и представляются в тернарной системе кодирования, то кодирование приращений осуществляется следующим образом: 01 ,.-11 - -1 и 00 - -0, т.е. если rto сигналу конца итерации триггер 66 устанавливается в нулевое состояние, а триггер 71 - в единичное То на выходе элемента И 74 появится единичный сигнал длительностью одной итерации, соответствующий положительному приращению интеграла , который через выход 54 узла 9 поступит на выход 36 решающего блока, если же по сигналу конца итерации в единичное состояние устанавливаются оба триггера 66 и 71, то единичный сигнал длительностью одной итерации, соответ ствующий отрицательному приращению интеграла -1, появится на выходе элемента И 75 и поступит через выход 54 узла 9 также на выход 36 решающего блока. Если же оба триггера 66 и 71 окажутся в нулевом состоянии, то приращения на выход 36 вьщаваться не будут, что соответствует значению приращения интеграла, равному О. Выделенные в результате квантования одноразрядные квантованные приращения интеграла с выхода 36 данного решающего блока (РБ) поступят в соответствии со схемой реализации синусно-косинусных зависимостей (фиг.5) на вход 30 приращения подынтегральной функции другого решающего блока и одновременно выделенные одноразрядные квантованные приращения интеграла другого решающего блока поступят с его выхода 36 на вход 30 приращений подынтегральной функции данного решагацего блока. Эти одноразрядные приращения представлены в тернарной системе кодирования, т.е. принимают значения 41 % О и -1 и передаются по двум каналам (положительному и отрицательному) в виде постоянных сигналов, соответствующих +1 или Поступившие с выхода 36 другого решающего блока на вход 30 приращений подынтегральной функции данного решающего блока одноразрядные

131

квантованные приращения поступают с входа 30 через вход 37 в узел 1, где производится их масштабирование, которое выполняется следующим образом. Если приращения принимают значе ние +1, то постоянный сигнал, соответствующий этому значению в течение итерации будет поступать через вход 37 на вход элемента И 56, на второй вход которого поступает через вход 42 с нулевого выхода тригге ра 26 единичный сигнал (этот триггер устанавливается в нулевое состояние при подготовке решающего блока к работе сигналом сброса с входа 34 и переводится в единичное состояние лишь при достижении подынтегральной функции значения, равного +1, т.е. когда модифицированный дополнительный код подынтегральной функции принимает вид 01, 000...0), а на третий вход элемента И 56 в каждой итерации поступает из центрального устройства управления ЦИС через вход 38 в виде импульса масштабный сигнал, соответствующий кванту подынтегральной функ ции, т.е. младшему разряду подынтег- ральной функции. В результате на выходе элемента И 56 появится импульс, соответствующий единице в п-ом разряде подынтегральной функции, т.е. соответствующий единице в младшем разряде данной подынтегральной функции, таким образом, поступательное одноразрядное приращение подынтегральной функции, представленное в тернарной системе кодирования, будет переведено в последовательный код, приведенный к масштабу данной подынтегральной функции, который с выхода элемента И 56 поступит через элемент ИЛИ 55 на выход 43 узла 1. Если одноразрядное входное приращение окажется отрицательным, то постоянный сигнал, соотиотгтвующий -1 поступает через вход 37 на вход элемента И 58, на второй вход которого поступает через вход 41 с нулевого выхода триггера 21 единичный сигнал (этот триггер устанавливается в нулевое состояние при подготовке решающего блока к работе сигналом сбро са с входа 34 и пергводится в единич ное состояние лишь при достижении подынтегральной функции значения, равного -,1, т.е. когда модифицированный дополнительный код подынтегральной функции примет вид 10, 000...0), тогда масштабный импульс.

0451414

соответствующий кванту подынтегральной функции и поступающий в каждой итерации через вход 38, пройдет через этот .элемент И 58 и перебросит в еди5 ничное состояние триггер 57, который начнет выдавать со своего единичного выхода через элемент ИЛИ 55 на выход 43 единичный сигнал, соответствующий последовательному дополнительному ко10 ду одноразрядного отрицательного приращения, приведенного к масштабу данной подынтегральной функции. По окончании итерации по последнему ее такту вход 35 решающего блока в каждой

15 итерации поступает сигнал конца итерации, который проходит через вход 40 узла 1 устанавливает триггер 57 в нулевое состояние, завершая тем самым выработку последовательного моди20 фицированного дополнительного кода одноразрядного отрицательного приращения, приведенного к масштабу данной подынтегральной функции, которая . , также представляется в решающем бло25 ке в последовательном модифицированном дополнительном коде младшими разрядами вперед с двумя знаковыми разрядами и одним служебным, совпадающим по времени с сигналом конца итера30 ции, который поступает в последнее такте каждой итерации через вход 35 для подготовки узлов решающего блока к следующей итерации. Приведенное таким образом к масштабу данной подынтегральной функциии и переведенное из тернарной системы кодирования в последовательный модифицированный дополнительный код приращение подынтегральной функции Л« У поступит с выхо Q да 43 узла 1 на вход сумматора 2, на второй вход которого с выхода регистра 6 поступает значение подынтегральной функции y(k-1)-, вычисленное в предыдущей итерации. В цепь переноса

j комбинированного сумматора 2 включен однотактный элемент 3 задержки, служащий для образования поразрядного переноса при сложении приращения подынтегральной функции с текущим значением подынтегральной функции. В результате выполнения операции суммирования на втором выходе сумматора 2 получается новое значение подынтегральной функции .)+d У fk - номер итерации), которое с второго входа сумматора 2 поступает на вход узла 4 умножения и через элемент ИЛИ 5 на вход регистра 6. В узле 4 умножения производится умноление но151вого значения подынтегральной функции на приращение аргумента Д X и результат умножения суммируется в сумматоре 7 со значением остатка интеграла, вычисленным в предыдущей итерации. Полученное в сумматоре 7 значение Неквантованного приращения интеграла поступает с второго выхода этого сумматора на вход узла 9 квантования, в котором происходит выделение нового значения остатка интеграла, которое с первого вькода 53 узла 9 поступает через элемент ИЛИ 10 в регистр 11, и происходит вы деление квантованного приращения интеграла -Л .,5 для следующей итера . ции, которое с второго выхода 54 узла 9 подается на выход 36 решающего блока и далее вычисления повторяются уже в следующей итерации и т.д. При вычислении синусно-косинусных зависимостей с помощью решающих блоков с одноразрядными приращениями происходит существенное накопление погрешностей вычисления, особенно при воспроизведении функций на большом интервале изменения независимой переменной. Для того, чтобы повысит точность реализации синусно-косинусных зависимостей, определяют характер накопления погрешностей. Для это го выводят аналитическую зависимость погрешности вычисления синусно-косинусных зависимостей на большом интер вале решения. Будем считать, что вну ренняя погрешность решающих блоков с одноразрядными приращениями состоит только из погрешности метода (х), поскольку погрешность квантования при вычислении на большом интервале решения не накапливается. Интегриро- вание осуществляется по формуле прямоугольников, для которой I oi -1/2tiY/,.) где h - шаг интегрирования; X - значение переменной интегри рования; Ур- значение подынтегральной фун ции . Система уравнений Шеннона для функций X имеет вид: d Vjdlx; 2 . Тогда уравнения погрешностей примут вид: ЗЬ2 где Е,, - погрешность функции sin х; 6 У - погрешность функции cos х. Принимая во внимание, что у sin х у.cos X, и учитывая соотношение (1), найдем выражения для внутренних погрешностей решающих блоков, входящих в схему реализации синусно-косинусной зависимости (фиг., 5): ff2fi5inxc X ; о1д4 -//2bcosxcI( . Так как Ех(х)0, то после подстановки(3)в(2) и промежуточных dipеобразований получим дифференциальное уравнение, определяющее погрешность схемы реализации синусно-косинусной зависимости 8 + Е ficosx; , 0, решение которого приводит к следующему общему выражению для погрешности синуса: , f/Zxiisinx . (ч| Подставляя (4) в первое уравнение системы (2), получим выражение для погрешности косинуса 1 1IZ) hcos X . CS) Анализируя выражения (4) и (5) Можно заметить, что погрешность возрастает с ростом значения переменной X И накопление ее происходит по закону синуса при воспроизведении функции синуса и по закону косинуса при воспроизведении функции косинуса. Так как максимальная по модулю погрешность вычисления этих функций образуется тогда, когда данные функции принимают значения ±1, и совпадает по знаку с воспроизводимой функцией, то накопление погрешности приводит к тому, что в этих точках значения функций превьш1ают значение единицы. Поэтому предложено коррекцию вычисления этих функций осуществлять следующим образом: при достижении подынтегральной функцией значения + перекрывать канал поступления положительных приращений до тех пор, пока значение данной подынтегральной функции не станет меньше единицы, т.е. до тех пор пока значение подынтегральной функции другого решающего блока не перейдет через нулевое значение и не изменит свой знак, а если значение подынтегральной функции данного решающего блока достигнет -1, то отс екать отрицательные прирап(еиия подьттегралытй функции до тех пор, пока значение этой подынтегральной функции не станет больше минус едини цы. В результате в точках 1/2jlk (, 2...k), т.е. в точках, в которых.sin X или cos X принимают значения ±1, происходит ограничение пото ка приращений соответствующего знака по входу приращений той подынтеграль ной функции, которая достигает это максимальное значение, и тем самым производится сбрасывание накопленных приращений, так как на каждом новом интервале, равном Ji/Z, вычисления производятся как бь с новыми, точными исходными данными. Данный алгоритм в решающем блоке реализуется следующим образом. В кон це итерации, т.е. в п-ом такте, по сигналу конца итерации в решающем блоке проводится анализ знаковьЬс раз рядов модифицированного дополнительного двоичного кода подынтегральной функции. При этом знаковые разряды модифицированногс кода подынтегральной функции в п-ном такте располага,ются в(п-1)-ом и (п-2)-ом разрядах (п-ый разряд является служебным),которые с помощью элементов И 13, НЕ 16, НЕ 18 и э; ементов И 15, НЕ U НЕ 23 подключаются к первым входам соответственно элементов И 17, И 19 и элементов И 22, И 24, на вторые входы которых подается с входа 35 решающего блока сигнал конца итерации. В результате, если подынтеграль мая функция достигнет значения +1, то ее знаковые разряды принимают зна чение 01 и на выходе элемента И 15 появится единичный сигнал, который поступит на вход элемента И 22 (инверсным значением поступит на вход элемента И 24 и по сигналу конца итерации, поступающему на второй вход элементов И 22 и 24 с входа 35, запишется в триггер 26. В результате на нулевом выходе триггера 26 появится нулевой сигнал, который посту пит в узел 1 , через шестой его вход 42 на вход элемента И 56 и закроет его, отсекая тем самым положительные приращения подынтегральной функции, поступающие из решающего бло ка, и удерживая точное значение данной подынтегральной функции в точке экстремума, причем это будет происходить до тех пор, пока значение 1 418 подынтегральной функции другого реша ющего блока не пересечет нулевую точ ку и не станет отрицательным, тогда вычисляемое в данном решающем блоке значение подынтегральной функции станет меньше единицы и на выходе элемента И 15 исчезнет единичный сигнал. Если же значения (п-1)-го и (п-2)-го разрядов будут равны 10 (подынтегральная функция достигнет значения -1), то единичный сигнал появится на выходе элемента И 13 и по сигналу конца итерации, поступающему на второй вход элементов И 17 и И 19с входа 35, этот единичный сигнал запишется в триггер 21. В результате на нулевом выходе триггера 21 появится нулевой сигнал, который поступит в узел 1 через пятый вход 1 на вход элемента И 58 и закроет его, отсекая тем самым отрицательные приращения подынтегральной функции данного решающего блока до тех пор, пока значение подынтегральной функции другого решающего блока не перейдет через нуль и прирашения не станут положительными, сбрасывая вследствие этого накопленные погрешности вычисления и удерживая точное значение подынтегральной функции в точке экстремума. При всех остальных значениях (n-l)-ro и (п-2)-го разрядов подынтегральной функции по сигналу конца итерации в триггеры 21 и 26 будет записываться нуль и единичные потенциалы с нулевых выходов данных триггеров :разрешат поступление как положительных, так и отрицательньк приращений подынтегральной функции в решающи блок. Таким образом, предложеннь й решающий блок позволяет при вычислении синусно-косинусных зависимостей в каждой точке 1/2iik ( , 2...k) прекращать накопление погрешностей и сбрасывать накопленные погрешности, удерживая точные значения подынтегральных функций в точках экстрем ма и вследствие этого начиная вычисления в каждой точке 1/2Jik с точными начальными , что позволяет производить вычисления синусно-косинусных зависимостей с постоянной погрешнос- . „ Jj тью, не превышающей - , что подтверждается также и результатами проведенных с предложенным решающим блоком ИСПЫТа)И1 .

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Устройство для суммирования одноразрядных приращений | 1985 |

|

SU1251072A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

РЕШАЮЩИЙ БЛОК ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ СТРУКТУРЫ, содержащий узел масштабирования, сумматор подынтегральной функции, регистр подынтегральной функции, первый элемент задержки, первый элеме.нт ИЛИ, узел умножения, сумматор остатка интеграла, регистр остатка интеграла, второй элемент задержки, второй элемент ИЛИ, узел квантования, коммутатор, причем узел квантования содержит два триггера, семь элементов И, два элемента ИЛИ и два элемента НЕ, выход первого элемента задержки узла квантования соедин.ен с первым входом первого эле.мента И узла квантования, через первый элемент НЕ узла квантования соединен с первым входом- второго элемента И узла квантования и подключен к входу второго элемента задержки узла квантования, выход которого соединен с первым входом третьего элемента И узла квантования и через второй элемент НЕ узла квантования - с первым входом четвертого элемента И узла квантования, выход первого элемента И узла квантования соединен с единичным входом первого триггера узла . квантования, нулевой и единичный вы-ходы которого соединены с первыми входами соответственно пятого и шестого элементов И узла квантования, выход второго элемента И узла квантования соединен с первым входом первого элемента ИЛИ узла квантования, выход которого соединен с нулевым входом первого триггера узла кванто- , вания, выход трет.ьего элемента И узла квантования соединен с единичным входом второго триггера узла квантования, единичный выход которого соединен с вторыми входами пятого и шестого элементов И узла квантования, а нулевой вход подключен к выходу второго элемента ИЛИ узла квантования, первый вход которого соединен с выходом четвертого элемента И узла квантования, узел масштабирования содержит триггер, два элемента И к два элемента ИЛИ, причем выход f первого элемента И узла масштабироOi вания соединен с первым входом первого элемента ИЛИ узла масштабирований, выход второго элемента И узла масштабирования соединен с единичным входом триггера узла масштабирования, единичный выход которого подключен к вто рому входу первого элемента ИЛИ узла масштабирования,, а нулевой вход подключен к выходу второго элемента ИЛИ узла масштабирования, выход первого элемента ИЛИ узла масштабирования соединен с первым входом сумматора подынтегральной функции, первый вход которого соединен через первый элемент задержки с вторым входом

7

60

-

5

5

Ф14е.З

Фиг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 551669, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровые модели | |||

| М.-Л., Энергия, 1964, с | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-07—Подача