Область техники, к которой относится изобретение

Настоящее изобретение относится к сфере защиты компьютеров от несанкционированной деятельности, а конкретно к способу обеспечения защищенной работы вычислительного средства и к прибору для осуществления этого способа.

Уровень техники

Известен способ доверенной загрузки операционной системы программно-аппаратного комплекса (заявка на патент РФ №2007148810, опубл. 10.07.2009), в котором в каждый компьютер устанавливают модуль безопасности, осуществляющий доверенную загрузку программного обеспечения при положительном результате проверки целостности программного обеспечения.

Известен также способ защищенной начальной загрузки операционной системы с использованием проверки состояния (патент РФ №2413295, опубл. 27.02.2011), в котором после осуществления части процедуры запуска проверяется загрузчик операционной системы на правильность, а корректное состояние машины - на существование.

В еще одном способе защиты от несанкционированного доступа к информации, хранимой в персональной ЭВМ (патент РФ №2475823, опубл. 20.02.2013), перед загрузкой резидентной операционной системы (ОС) задают выполнение последовательности команд, которая устанавливает точку останова. При загрузке ОС эту точку останова обрабатывают соответствующим кодом, заданным при работе схемы расширения BIOS, передающим управление на загрузку ОС, и запускают задачу безопасности.

В заявке Китая №101877040 (опубл. 03.11.2010) описан способ защищенной загрузки, в котором сначала проверяется целостность BIOS, после чего надежный BIOS загружается в память компьютера.

Во всех этих способах при фиксации нарушения работы программного обеспечения команду процессору на рестарт подает специальная программа, хранящаяся в той же памяти, что и выполняемое или загружаемое программное обеспечение. Иными словами, перезапуск работы вычислительного средства происходит без физического отключения внешних запоминающих устройств. При этом не исключена возможность введения в защищаемый компьютер вредоносной программы.

Раскрытие изобретения

Задача, решаемая настоящим изобретением, состоит в разработке такого способа обеспечения защищенной работы вычислительного средства и соответствующего прибора, которые, расширяя арсенал технических средств, позволяли бы еще и повысить надежность защиты вычислительного средства при загрузке программного обеспечения.

Для решения этой задачи и достижения указанного технического результата в первом объекте настоящего изобретения предложен способ обеспечения защищенной работы вычислительного средства, в котором: заранее снабжают вычислительное средство по меньшей мере двумя интерфейсами, первый из которых предназначен для подключения постоянной памяти, хранящей основное программное обеспечение, а второй предназначен для соединения с внешними устройствами; при включении вычислительного средства физически размыкают сигнальные цепи второго интерфейса и контролируют длительность загрузки основного программного обеспечения через первый интерфейс; если длительность загрузки основного программного обеспечения превышает первый заранее заданный временной интервал, осуществляют аппаратно повторное включение вычислительного средства; после успешной загрузки основного программного обеспечения, когда длительность его загрузки не превышает первого заранее заданного временного интервала, физически замыкают сигнальные цепи второго интерфейса; в процессе функционирования вычислительного средства периодически, через второй заранее заданный временной интервал, формируют с помощью основного программного обеспечения сигнал подтверждения нормальной работы вычислительного средства; при отсутствии сигнала подтверждения нормальной работы по истечении второго заранее заданного временного интервала физически размыкают сигнальные цепи второго интерфейса и осуществляют аппаратно повторное включение вычислительного средства.

Особенность способа по первому объекту настоящего изобретения состоит в том, что могут дополнительно: контролировать значение в наборе битов, характеризующих состояние второго интерфейса; формировать управляющий сигнал при отклонении значения от заранее заданной величины; осуществлять аппаратно повторное включение вычислительного средства при поступлении управляющего сигнала.

Для решения той же задачи и достижения того же технического результата во втором объекте настоящего изобретения предложен прибор для реализации способа по первому объекту настоящего изобретения, содержащий: процессор; постоянную память, хранящую основное программное обеспечение, которое при его исполнении в процессоре заставляет этот процессор периодически формировать сигнал подтверждения нормальной работы через второй заранее заданный временной интервал; оперативную память, предназначенную для загрузки в него основного программного обеспечения; первый интерфейс, выполненный с возможностью физического замыкания своих сигнальных цепей для подключения постоянной памяти к оперативной памяти при включении вычислительного средства; второй интерфейс, выполненный с возможностью физического замыкания своих сигнальных цепей для подключения внешних устройств к вычислительному средству; блок отключения внешних устройств, выполненный с возможностью физического размыкания сигнальных цепей второго интерфейса на время загрузки основного программного обеспечения; блок аппаратного перезапуска, выполненный с возможностью формировать сигнал аппаратного перезапуска вычислительного средства; стартовый таймер, выполненный с возможностью контролировать длительность загрузки основного программного обеспечения при включении вычислительного средства и формировать сигнал на блок аппаратного перезапуска в случае превышения длительностью загрузки первого заранее заданного временного интервала; сторожевой таймер, выполненный с возможностью формировать сигнал на блок аппаратного перезапуска в случае отсутствия сигнала подтверждения нормальной работы с процессора по истечении второго заранее заданного временного интервала.

Особенность прибора по второму варианту осуществления настоящего изобретения состоит в том, что он может содержать блок контроля внешних устройств, выполненный с возможностью контролировать значение в наборе битов, характеризующих состояние второго интерфейса, и формировать, управляющий сигнал, предназначенный для подачи на сторожевой таймер, при отклонении указанного значения от заранее заданной величины.

Краткое описание чертежей

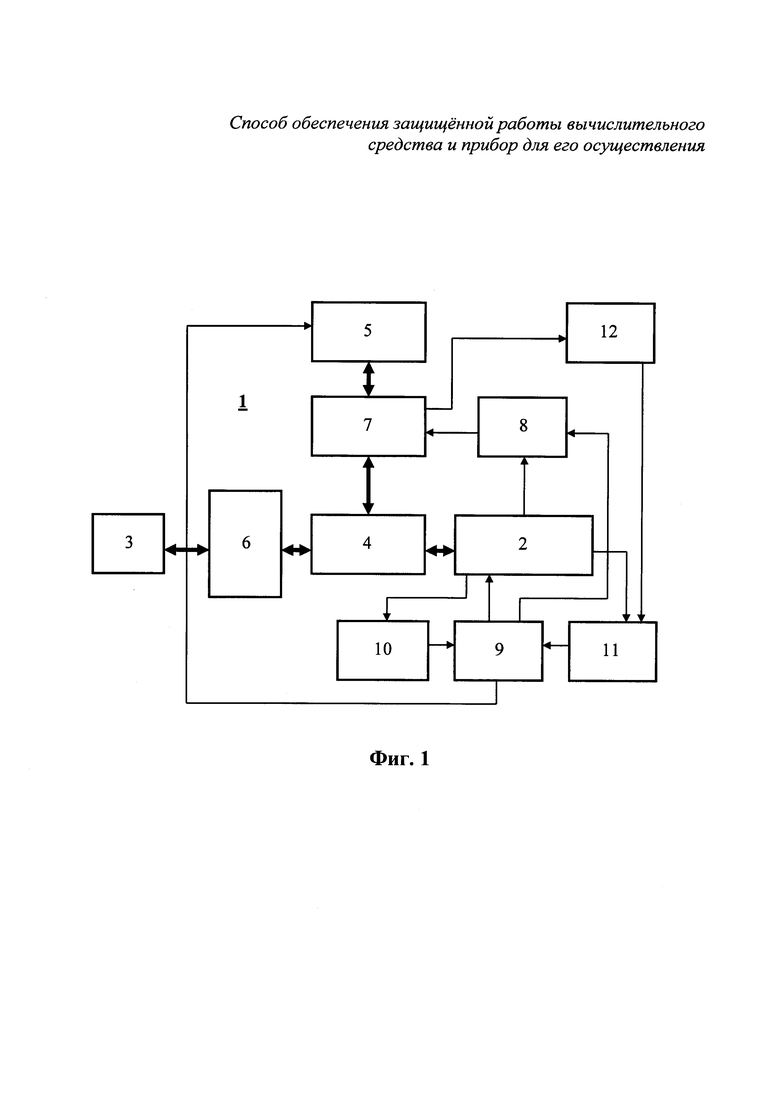

На Фиг. 1 приведена структурная схема прибора, реализующего способ по настоящему изобретению.

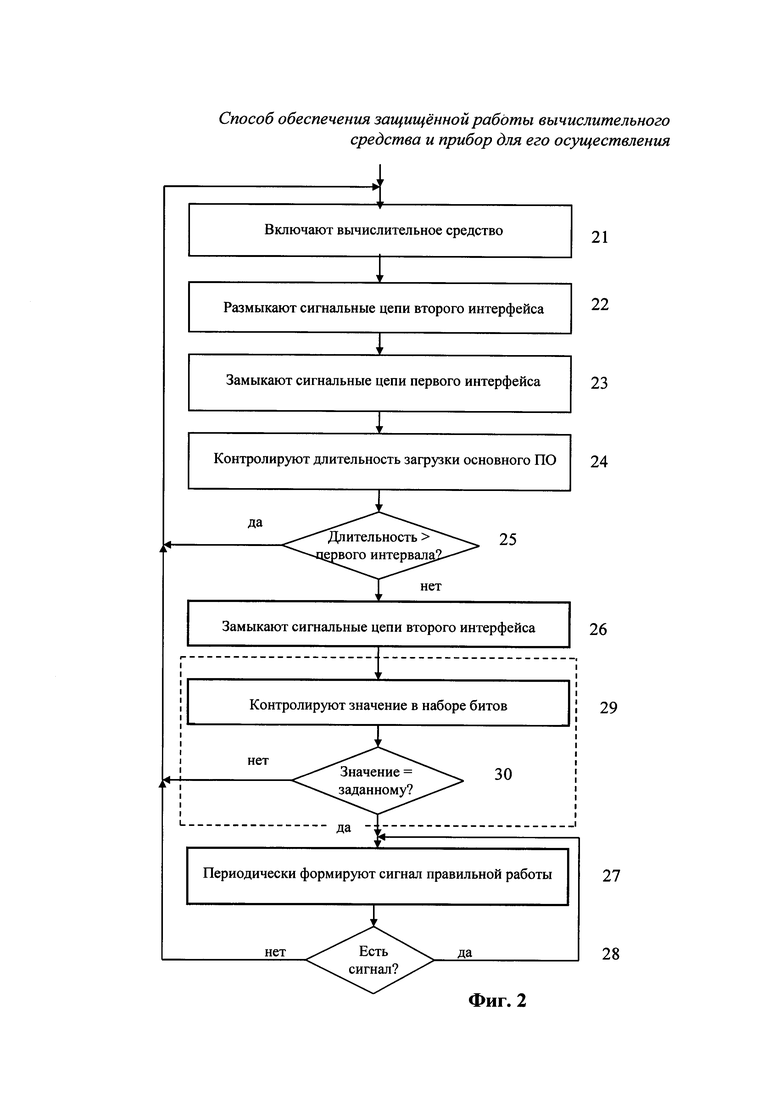

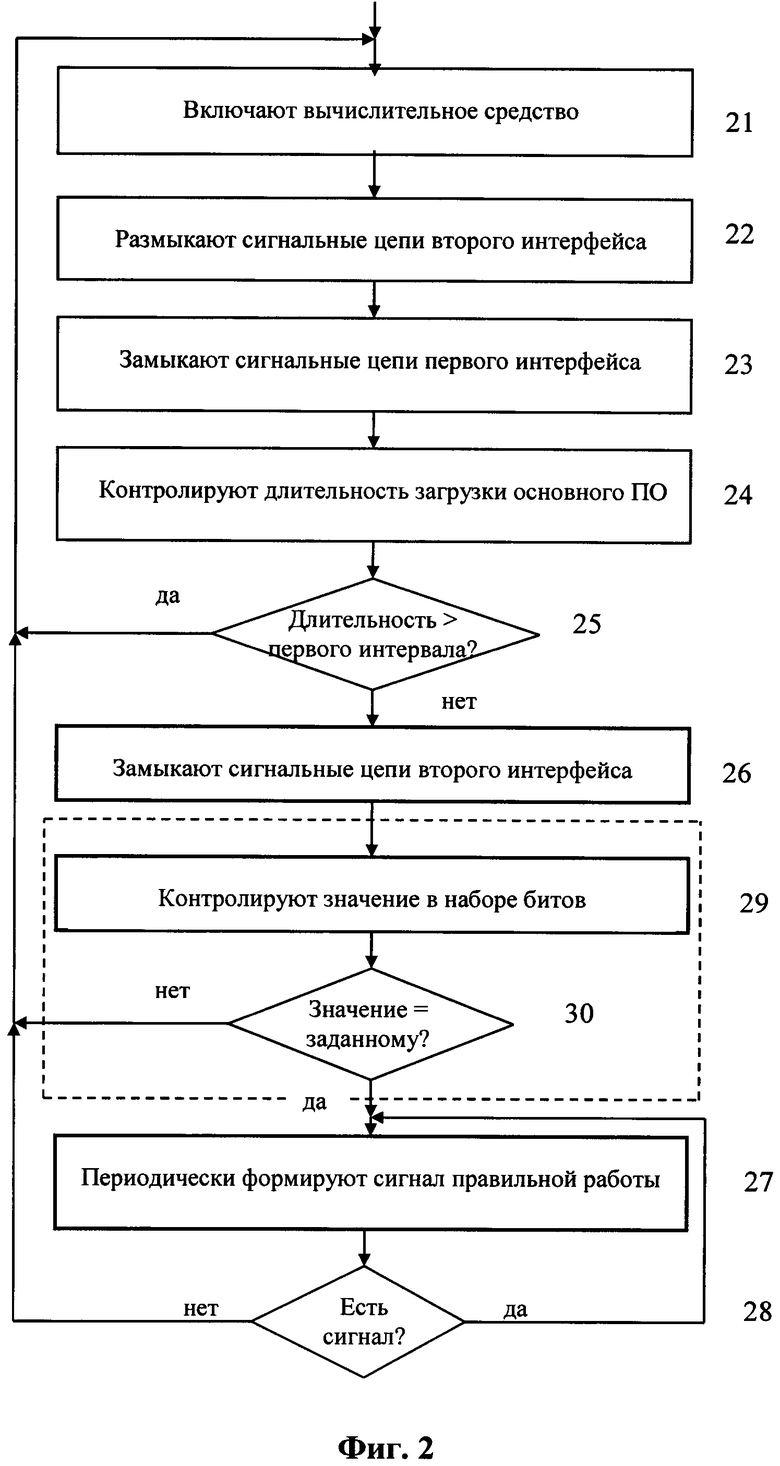

На Фиг. 2 приведена блок-схема алгоритма, выполняемого при реализации способа по настоящему изобретению.

Подробное описание вариантов осуществления

Способ обеспечения защищенной работы вычислительного средства по настоящему изобретению может быть осуществлен в соответствии с блок-схемой, которая приведена на Фиг. 1.

На этой блок-схеме вычислительное средство в целом обозначено ссылочной позицией 1. Ссылочными позициями 2-4 обозначены, соответственно, процессор, постоянная память и оперативная память защищаемого вычислительного средства 1. Постоянная память 3 предназначена для хранения основного программного обеспечения, определяющего при его исполнении в процессоре 2 функционирование вычислительного средства. Оперативная память 4, соединенная с процессором 2, предназначена для загрузки в него основного программного обеспечения из постоянной памяти 3 на время работы вычислительного средства. На Фиг. 1 ссылочной позицией 5 обобщенно обозначены внешние устройства, программы и данные из которых могут использоваться в работе защищаемого вычислительного средства 1.

Загрузка основного программного обеспечения из постоянной памяти 3 в оперативную память 4 осуществляется через первый интерфейс 6, выполненный с возможностью физического замыкания своих сигнальных цепей для подключения постоянной памяти 3 к оперативной памяти 4 при включении вычислительного средства. Второй интерфейс 7 выполнен с возможностью физического замыкания своих сигнальных цепей для подключения внешних устройств 5 к вычислительному средству 1 (к оперативной памяти 4).

Вычислительное средство 1 далее содержит блок 8 отключения внешних устройств, выполненный с возможностью физического размыкания сигнальных цепей второго интерфейса 7 на время загрузки основного программного обеспечения по сигналу с процессора 2, а также блок 9 аппаратного перезапуска, выполненный с возможностью формировать сигнал аппаратного перезапуска вычислительного средства 1, т.е. процессора 2 и внешних устройств 5.

Кроме того, в состав вычислительного средства 1 входит стартовый таймер 10, выполненный с возможностью контролировать длительность загрузки основного программного обеспечения при включении вычислительного средства 1 (по сигналу с процессора 2) и формировать сигнал на блок 9 аппаратного перезапуска в случае превышения длительностью загрузки первого заранее заданного временного интервала.

Наконец, вычислительное средство 1 содержит сторожевой таймер 11, выполненный с возможностью формировать сигнал на блок 9 аппаратного перезапуска в случае отсутствия сигнала подтверждения нормальной работы с процессора 2 по истечении второго заранее заданного временного интервала.

Предпочтительно, вычислительное средство 1 может содержать еще и блок 12 контроля внешних устройств, выполнение и функции которого поясняются ниже.

Процессор 2, постоянная память 3, оперативная память 4 могут иметь любое известное специалистам выполнение. Внешними устройствами 5 могут быть любые устройства, к примеру, запоминающие, измерительные, управляющие и любые иные устройства, приспособленные для взаимодействия с защищаемым вычислительным средством 1.

Первый интерфейс 6 и второй интерфейс 7 могут быть выполнены в виде набора ключей, замыкаемых и размыкаемых по сигналам соответствующих команд.

Блок 8 отключения внешних устройств может быть выполнен в виде формирователя сигнала на размыкание ключей второго интерфейса 7 по соответствующей команде из процессора 2.

Блок 9 аппаратного перезапуска может иметь любое выполнение, которое обеспечивает выдачу сигналов (команд) на перезапуск вычислительного средства 1 и внешних устройств 5 при поступлении на его входы сигналов от блоков 10 или 11.

Стартовый таймер 10 и сторожевой таймер 11 могут иметь любое выполнение, которое позволяет формировать на их выходах сигналы в случае, когда на их входы не поступает соответствующий сигнал по истечении заранее заданного временного интервала. Поступление же такого сигнала на вход таймера 11 или 12 приводит к сбросу подсчитанного времени и началу нового счета.

Осуществление способа обеспечения защищенной работы вычислительного средства по настоящему изобретению можно проиллюстрировать блок-схемой алгоритма, приведенной на Фиг. 2.

До начала работы, т.е. заранее вычислительное средство 1 снабжают по меньшей мере двумя интерфейсами: первый интерфейс 6 предназначен для подключения постоянной памяти 3, хранящей основное программное обеспечение, к оперативной памяти 4, а второй интерфейс 7 предназначен для соединения вычислительного средства 1 (оперативной памяти 4) с внешними устройствами 5.

При включении вычислительного средства 1 (этап 21 на Фиг. 2) физически размыкают сигнальные цепи второго интерфейса 7 (этап 22) по сигналу с блока 8 отключения внешних устройств. Одновременно замыкают сигнальные цепи первого интерфейса 6 (этап 23), например, тем же сигналом или отдельным сигналом с процессора 2.

В процессе загрузки основного программного обеспечения из постоянной памяти 3 в оперативную память 4 через первый интерфейс 6 контролируют длительность этой загрузки (этап 24). На этапе 25 осуществляют проверку того, превышает ли контролируемая длительность загрузки основного программного обеспечения (операционной системы) первый заранее заданный временной интервал. Если длительность этой загрузки превышает этот интервал (выход «да» этапа 25), то осуществляют аппаратно повторное включение вычислительного средства 1, т.е. возврат к этапу 21. Длительность загрузки основного программного обеспечения контролируется стартовым таймером 10, который формирует сигнал на блок 9 аппаратного перезапуска в случае превышения длительностью загрузки заранее заданного первого временного интервала.

Если же длительность загрузки основного программного обеспечения по ее завершении не превышает первого заранее заданного временного интервала (выход «нет» на этапе 25), стартовый таймер 10 не выдает управляющий сигнал на блок 9 аппаратного перезапуска. Тогда, после успешной загрузки производят физическое замыкание сигнальных цепей второго интерфейса 7 (этап 26). После этого происходит функционирование вычислительного средства 1 во взаимодействии с внешними устройствами 5.

В процессе функционирования вычислительного средства 1 периодически, через заранее заданный второй временной интервал, формируют с помощью основного программного обеспечения сигнал подтверждения нормальной работы вычислительного средства 1 (этап 27). На этапе 28 осуществляют проверку наличия сигнала подтверждения нормальной работы, который периодически формируется в процессоре упомянутым основным программным обеспечением в процессе работы вычислительного средства 1. Эта проверка выполняется сторожевым таймером 11.

При отсутствии по истечении второго заранее заданного временного интервала сигнала, который должен поступать с процессора 2 и подтверждать нормальную работу вычислительного средства 1 (выход «нет» на этапе 28), физически размыкают сигнальные цепи второго интерфейса 7 блоком 8 отключения внешних устройств по сигналу блока 9 аппаратного перезапуска, инициируемому сторожевым таймером 11, и осуществляют аппаратно повторное включение вычислительного средства 1 (т.е. возвращаются к началу этапа 21). Если же сигнал, подтверждающий нормальную работу вычислительного средства 1, поступает до истечения второго заранее заданного временного интервала, сторожевой таймер не срабатывает, сигнальные цепи второго интерфейса 7 не размыкаются, а вычислительное средство 1 продолжает свое функционирование (возвращаются к началу этапа 27).

Предпочтительно, после замыкания сигнальных цепей второго интерфейса 7 на этапе 26 могут выполнять этапы 29 и 30, обведенные на Фиг. 2 пунктиром. Для этого вычислительное средство 1 дополняют блоком 12 контроля внешних устройств, который выполнен с возможностью контролировать значение в наборе битов, характеризующих состояние второго интерфейса (этап 29), и формировать управляющий сигнал, предназначенный для подачи на сторожевой таймер 11, при отклонении контролируемого значения от заранее заданной величины. Если контролируемое значение не равно заранее заданной величине, производят аппаратный перезапуск вычислительного средства 1, как это описано выше (выход «нет» на этапе 30). Если же контролируемое значение в наборе битов равно заранее заданному значению, функционирование вычислительного средства 1 продолжается (выход «да» на этапе 28).

Указанные выше первый и второй заранее заданные временные интервалы, используемые на этапах 25 и 28, соответственно, могут быть определены раз и навсегда, если вычислительное средство 1 предназначено для решения одинаковых или сходных задач. Однако эти временные интервалы могут задаваться исходя из условий решаемой задачи, объема перерабатываемых данных, вероятности хакерских атак на вычислительное средство 1 и т.п. То же самое можно сказать и о заранее заданной величине, используемой на этапе 30.

Специалистам известно использование периодически сбрасываемого сторожевого таймера, отсутствие сброса которого свидетельствует о нарушении в работе (патент США №8122258, опубл. 21.02.2012; заявка на патент США №2015/0033004, опубл. 29.01.2015). Однако в настоящем изобретении совокупность его существенных признаков обеспечивает повышение надежности защиты вычислительного средства при загрузке в него программного обеспечения. Такая блокировка загрузки с внешних устройств выполняется путем их физического (аппаратного) отключения до окончания загрузки исполняемого ПО («основного программного обеспечения») и перезапуск вычислительного средства. То же самое происходит в отсутствие сигнала, периодически формируемого введенным программным обеспечением и свидетельствующего о нормальной работе вычислительного средства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровой вычислительной системы | 1987 |

|

SU1529242A1 |

| СИСТЕМА И СПОСОБ ДЛЯ АВТОМАТИЧЕСКОГО ОПОВЕЩЕНИЯ РАБОТАЮЩИХ НА ЖЕЛЕЗНОДОРОЖНЫХ ПУТЯХ | 2021 |

|

RU2773550C1 |

| ИНФОРМАЦИОННО-УПРАВЛЯЮЩИЙ КОМПЛЕКС АВТОМАТИЗИРОВАННОЙ СИСТЕМЫ УПРАВЛЕНИЯ ПОДГОТОВКОЙ ДВИГАТЕЛЬНЫХ УСТАНОВОК И ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ РАКЕТ КОСМИЧЕСКОГО НАЗНАЧЕНИЯ НА ТЕХНИЧЕСКОМ И СТАРТОВОМ КОМПЛЕКСАХ | 2015 |

|

RU2604362C1 |

| Интегрированная вычислительная система самолета МС-21 | 2017 |

|

RU2667040C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПЛОТНОСТИ И ВЯЗКОСТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2349897C2 |

| УСТРОЙСТВА, СИСТЕМЫ И СПОСОБЫ, КАСАЮЩИЕСЯ СБОЯ PLC-СИСТЕМЫ | 2007 |

|

RU2419827C2 |

| СПОСОБ ОТОБРАЖЕНИЯ ЗНАЧКА СЕТИ И ТЕРМИНАЛ | 2021 |

|

RU2810994C1 |

| УСТРОЙСТВА, СИСТЕМЫ И СПОСОБЫ ДЛЯ НАЗНАЧЕНИЯ АДРЕСА PLC-МОДУЛЯ | 2007 |

|

RU2419825C2 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ УСТРОЙСТВОМ И ЭЛЕКТРОННОЕ УСТРОЙСТВО | 2006 |

|

RU2419823C2 |

Изобретение относится к области компьютерной безопасности. Технический результат заключается в повышении надежности защиты вычислительного средства (ВС) при загрузке программного обеспечения (ПО). Способ, в котором снабжают ВС двумя интерфейсами, первый предназначен для подключения постоянной памяти, хранящей основное ПО, а второй для соединения с внешними устройствами; при включении ВС физически размыкают сигнальные цепи второго интерфейса и контролируют длительность загрузки основного ПО через первый интерфейс; если длительность загрузки основного ПО превышает первый заранее заданный временной интервал, осуществляют аппаратно повторное включение ВС; после успешной загрузки основного ПО, когда длительность его загрузки не превышает первого заранее заданного временного интервала, физически замыкают сигнальные цепи второго интерфейса; в процессе функционирования ВС через заранее заданный второй временной интервал формируют с помощью основного ПО сигнал подтверждения нормальной работы ВС; при отсутствии сигнала подтверждения нормальной работы по истечении второго временного интервала физически размыкают сигнальные цепи второго интерфейса и осуществляют аппаратно повторное включение ВС. 2 н. и 2 з.п. ф-лы, 2 ил.

1. Способ обеспечения защищенной работы вычислительного средства, в котором:

- заранее снабжают упомянутое вычислительное средство по меньшей мере двумя интерфейсами, первый из которых предназначен для подключения постоянной памяти, хранящей основное программное обеспечение, а второй предназначен для соединения с внешними устройствами;

- при включении упомянутого вычислительного средства физически размыкают сигнальные цепи упомянутого второго интерфейса и контролируют длительность загрузки основного программного обеспечения через упомянутый первый интерфейс;

- если длительность загрузки упомянутого основного программного обеспечения превышает первый заранее заданный временной интервал, осуществляют аппаратно повторное включение упомянутого вычислительного средства;

- после успешной загрузки упомянутого основного программного обеспечения, когда длительность его загрузки не превышает первого заранее заданного временного интервала, физически замыкают сигнальные цепи упомянутого второго интерфейса;

- в процессе функционирования упомянутого вычислительного средства периодически, через заранее заданный второй временной интервал, формируют с помощью упомянутого основного программного обеспечения сигнал подтверждения нормальной работы упомянутого вычислительного средства;

- при отсутствии упомянутого сигнала подтверждения нормальной работы по истечении упомянутого второго заранее заданного временного интервала физически размыкают сигнальные цепи упомянутого второго

интерфейса и осуществляют аппаратно повторное включение упомянутого вычислительного средства.

2. Способ по п. 1, в котором дополнительно:

- контролируют значение в наборе битов, характеризующих состояние упомянутого второго интерфейса;

- формируют управляющий сигнал при отклонении упомянутого значения от заранее заданной величины;

- осуществляют аппаратно повторное включение упомянутого вычислительного средства при поступлении упомянутого управляющего сигнала.

3. Прибор для реализации способа по п. 1, содержащий:

- процессор;

- постоянную память, хранящую основное программное обеспечение, которое при его исполнении в упомянутом процессоре заставляет упомянутый процессор периодически формировать сигнал подтверждения нормальной работы через второй заранее заданный временной интервал;

- оперативную память, предназначенную для загрузки в него упомянутого основного программного обеспечения;

- первый интерфейс, выполненный с возможностью физического замыкания своих сигнальных цепей для подключения упомянутой постоянной памяти к упомянутой оперативной памяти при включении упомянутого вычислительного средства;

- второй интерфейс, выполненный с возможностью физического замыкания своих сигнальных цепей для подключения внешних устройств к упомянутому вычислительному средству;

- блок отключения внешних устройств, выполненный с возможностью физического размыкания сигнальных цепей упомянутого второго интерфейса на время загрузки упомянутого основного программного обеспечения;

- блок аппаратного перезапуска, выполненный с возможностью формировать сигнал аппаратного перезапуска упомянутого вычислительного средства;

- стартовый таймер, выполненный с возможностью контролировать длительность загрузки упомянутого основного программного обеспечения при включении упомянутого вычислительного средства и формировать сигнал на упомянутый блок аппаратного перезапуска в случае превышения упомянутой длительностью загрузки заранее заданного первого временного интервала;

- сторожевой таймер, выполненный с возможностью формировать сигнал на упомянутый блок аппаратного перезапуска в случае отсутствия сигнала подтверждения нормальной работы с упомянутого процессора по истечении упомянутого второго заранее заданного временного интервала.

4. Прибор по п. 3, содержащий блок контроля внешних устройств, выполненный с возможностью контролировать значение в наборе битов, характеризующих состояние упомянутого второго интерфейса, и формировать управляющий сигнал, предназначенный для подачи на упомянутый сторожевой таймер, при отклонении упомянутого значения от заранее заданной величины.

| EA 201000159 A1, 30.08.2010 | |||

| Инструмент для определения боковых качаний голени относительно бедра | 1961 |

|

SU151429A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА К ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2002 |

|

RU2212705C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| УСТРОЙСТВО СОЗДАНИЯ ДОВЕРЕННОЙ СРЕДЫ ДЛЯ КОМПЬЮТЕРОВ СПЕЦИАЛЬНОГО НАЗНАЧЕНИЯ | 2014 |

|

RU2569577C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА К ИНФОРМАЦИИ | 2012 |

|

RU2524859C2 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| US 6952777B1, 04.10.2005. | |||

Авторы

Даты

2017-09-13—Публикация

2016-12-29—Подача