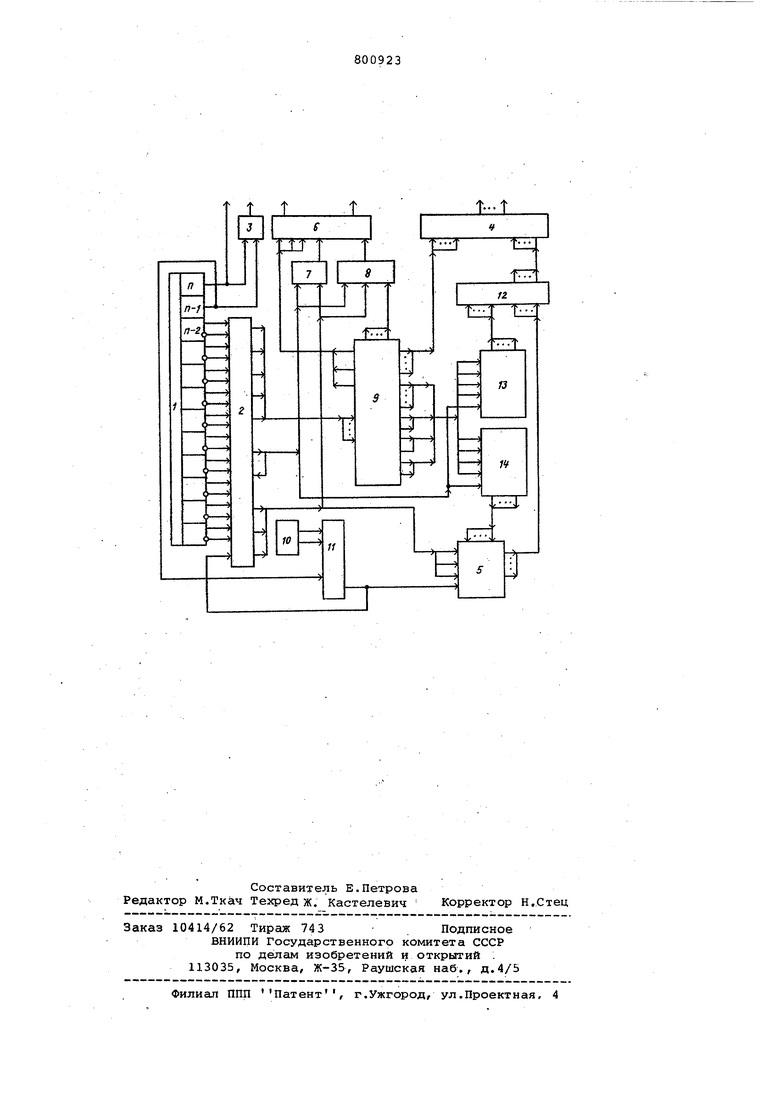

(54) ЦИФРОВОЙ СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ рядов коммутатора соединена с управляющими входами вычислительных блоков, к информационным входам которых подключены соответствующие группы выходов блока памяти. На чертеже приведена структурная электрическая схема предложенного преобразователя. Цифровой синусно-косинусный преобразователь содержит датчик 1 прямого и инверсного п-разрядного кода, коммутатор 2, сумматор 3, выходной сумматор 4, множительный блок 5, блок 6 определения }меток, элемент ИЛИ 7, компаратор 8, блок У памяти, источник 10 синхроимпульсов, блок 11 управления, дополнительный сумматор 12 и. вычислительные блоки 13 и 14. Преобразователь работает следующим образом. п-ый разряд датчика 1 является знаковым разрядом кода Siп х,а знаковый разряд кода cos х определяется сумматором 3 как сумма по модулю логических значений п-1 и п-го разрядов датчика 1. . Определение кодов чисел 1 s i п х| и IGOS х| осуществляется методом кусочно-линейной аппроксимации с ис пользованием тригонометрических фор мул приведения. Аппроксимация функций производится по синусной функци в пределах, от О до . Коды fsfn и jcos х| определяются последовател но в каждом цикле преобразования, i состоящем из двух периодов Т и Tg. В течение Т определяется код |sin х| , а в течение TQ.- код jcos х Для этого блок 11 вьграбатывает по значению п-1-го разряда управляю щий логический сигнал Q(T) таким об разом, что Q(T)Q, ,а Q (T,;)Q|f / где Q,, - логический коэффициент П-1-ГО разряда датчика 1. Коммутатор 2 по сигналу Q(T) и прямому и инверсному п-2 разрядному коду младших разрядов датчика 1 выр батывает код приведенного угла Хщэ ( Для осуществления дальнейшей работы п-2 разрядный код угла Хпр(Т) разде лен на три кода, соответствующих углам Xi ,XQ и Х| соответственно,так, что (T),j+X, где , и Х - углы, величины которых опреде лйются соответственно значениями Старших разрядов и значениями перво и-второй групп младших разрядов ком мутатора 2. Код угла Х поступает на входы блока 9, который по коду угла Х комбинационно: вырабатывает коды углов, соответствующих угловым меткам, код значений синусной функции, коды угловых коэффициентов участков аппроксимации и коды попра вок соответственно. . Коды угловых коэффициентов учасТ stOB аппроксимации и коды поправок с Соответствующих выходов блока 9 поступают на параллельно соединенные информационные входы вычислительных блоков 13 и 14, на параллельно соединенные управляющие входы которых поступает с первой группы выходов . младших разрядов коммутатора 2 код угла Х,. По входным кодам первый вычислительный блок ,13 комбинационно вы- рабатывает код приращения синусной функции, соответствующего приращению аргумента на обрабатываемом участке, а второй вычислительный блок 14 - код углового коэффициента соответствующего подучаетка обрабатываемого участка аппроксимации. С выходов второго вычислительного блока 14 код углового коэффициента поступает на вторую группу входов множительного блока 5, на первую группу входов которого с второй группы выходов младших разрядов коммутатора ii поступает код угла XQ. На корректирующий вход множительного блока 5 с выхода блока 11 поступает логический сигнал Q(TJ . По этим сигналciM множительный блок 5 вь рабатывает код приращения синусной функции, соответствующего приращению аргумента. С выходов первого вычислительного блока 13 код приращения угла Хц и с выходов множительного блока 5 код приращения угла Xj поступайт соответственно на первую и вторую группу входов дополнительного сумматора 12. Дополнительный сумматор 12 вырабатывает код приращения синусной функции соответствующег-о приращения аргумента на обрабатываемом участке аппроксимации на угол (). Этот код приращения с выходов дополнительного сумматора поступает на вторую группу входов выходного сумматора 4, на первую группу входов которого поступает код с второй групры выходов блока 9. По кодам, поступающим с третьей группы блока 9 и с Первой и второй групп младших разрядов коммутатора 2, компаратор 8 вырабатывает соответствующие логические сигналы, поступающие на третий вход блока б, на первые входы и второй вход которого поступают соответствующие сигнгшы с первой группы выходов блока 9 и с выхода элемента ИЛИ 7 соответственно. По этим входным сигналам, блок б вырабатывает код масштабных угловых меток -,сигналы признаков масштабных угловых меток 5 и 30. Перед началом цикла преобразования блок 11 по сигналу логического значения Q п-1-го разряда датчика 1 вырабатывает управляющий сигнал Q(T)Q(TI) Q«, при котором на выходах выходного сумматора 4 вырабатывается код t sin Xf, а на выходах блока 6 - код масштабных угловых меток соответствующий углу Хпр ) Цикл вычисления (преобразования) начинается с приводом от источника 10на блок 11 старт-импульса. По старт-импульсу блок И из последовательности тактовых импульсов источника 10 выделяет два первы импульса, следующих непосредственно после окончания старт-импульса. По первому из этих двух импульсо блок 11 генерирует импульс, по кото рому производится съем с преобразов теля кода sin X, а после его окончания начинается период, в течение которого блок 11 на управпющем выходе вырабатывает управляющий логический сигнал Q(T) Q(T,j) При этом период частоты следования тактовых импульсов источника 10 вырабатывается таким, что за время заключенное между окончанием тактового импульса и началом следующего тактового импульса, все переходные процессы заканчиваются, т.е. на выходах выходного сумматора 4 устанав ливается код числа Icos х| , а на выходах блока б - кодмасштабных угловых меток, соответствующий углу Хпр. (Tjj) . После этого блок 11 генерирует импульс, по которому производится съем с преобразователя кода cos х, а по его окончании на выходе блока 11устанавливается управляющий сигнал Q(T) (7 ) . На этом цикл вычислений заканчивается, а очередной цикл начнется только с приходом от источника 10 на блок 11 очередного старт-импульса. Предложенный преобразователь обе печивает высокую точность воспроизведения функции. Формула изобретения Цифровой синусно-косинусный преобразователь, содержащий датчик пря мого и инверсного п-разрядного кода сумматор, входы которого соединены с выходами двух старших разрядов датчика прямого и инверсного п-раэрядного кода/ прямые и инверсные выходы остальных разрядовкоторого соединены с входами коммутатора, источник синхроимпульсов, выходами соединенный -с входами блока управления, через который один из старших разрядов датчика прямого и инверсного п-разрядного кода соединен с управляющим входом коммутатора и кор{зектирующим входом множительного блока, старшие разряды коммутатора соединены с входами блока памяти, первая группа выходов младших разрядов коммутатора соединена с первыми входами элемента ИЛИ и компаратора, а вторая группа выходов младших разрядов коммутатора соединена с вторыми входами элемента ИЛИ и компаратора и первой группой входов мно кительного блока, первая группа выходов блока памяти соединена с первыми входами блока определения .меток, второй, и третий входил которого соединены соответственно с выходами элемента ИЛИ и ксямпаратора/ вторая группа выходов блока памяти соединена с первой группой входов выходного сумматора, третья группа выходов блока памяти соединена с третьим входом компаратора, отличающ ии с я тем, что, с целью повышения точности, введены два вычислительных блока и дополнительный сумматор, при этом выходы дополнительного сумматора соединены с второй группой входов выходного сумматора, первая и вторая группы входов дополнительного сумматора соединены соответственно с выходами первого вычислительного блока и -с выходами множительного блока, вторая группа входов которого соединена с выходами второго вычислительного блока, а первая группа выходов младших разрядов коммутатора соединена с управляющими входами вычислительных блоков, к информационным входам которых подключены соответствующие группы выходов блока памяти. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке 2587867,кл.С Об F 15/00, 03.03.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой синусно-косинусный преобразователь | 1977 |

|

SU780174A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1302273A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

Авторы

Даты

1981-01-30—Публикация

1978-05-29—Подача