Изобретение относится к области вычислительной техники.

Технический результат - повышение надежности и отказоустойчивости вычислительных устройств и систем управления.

Одним из способов повышения надежности и отказоустойчивости схем является структурное резервирование. При структурном резервировании в схему добавляют избыточные элементы. Известно полное, частичное и поэлементное резервирование, когда резервируется схема полностью или частично, а также может резервироваться один или несколько элементов схемы.

По способу подключения резервного элемента различают постоянное резервирование, подключение при отказе основного элемента и скользящее резервирование (Надежность технических систем. Справочник под ред. Ушакова И.А. М.: Радио и связь, 1985. - 606 с.).

Заявленный способ повышения отказоустойчивости схемы использует скользящее резервирование узлов и элементов. При скользящем резервировании резервный элемент может заменять любой из группы элементов такого же типа.

Заявленный способ реализован в устройстве отказоустойчивой схемы.

Известны аналоги отказоустойчивой схемы - это отказоустойчивые схемы с резервированием. Недостаток аналогов, отказоустойчивых схем и микросхем - это то, что в них используется дублирование, троирование или n-кратное резервирование узлов и фрагментов схемы. Элементы схемы соединены друг с другом шинами и дорожками, по которым передаются информационные сигналы. Если происходит отказ в каком-то одном элементе узла, то выключается из работы целый узел, причем его исправные элементы больше никак не используются.

Предлагается новая отказоустойчивая схема на базе коммутаторов, узлов и элементов.

Отказоустойчивая схема разработана на основе коммутаторной архитектуры. Суть заявленного изобретения состоит в том, что элементы и узлы схемы соединяются друг с другом через коммутатор. Отказ элемента не приводит к отказу узла, вместо него коммутатор подключает резервный элемент.

Наиболее близкие аналоги (прототип) изобретения - это коммутаторные искусственные нейронные сети (ИНС).

В коммутаторных ИНС используются унифицированные, стандартные и взаимозаменяемые элементы. ИНС состоит из элементов двух типов - из нейронов и коммутаторов. Нейрон имеет один вход и один выход и подключается к коммутатору. Коммутаторы могут соединяться друг с другом, образуя древовидную структуру.

Для реализации заявленного способа предлагается отказоустойчивая схема, разработанная на основе коммутаторной архитектуры. Отказоустойчивая схема реализует древовидную структуру, где корень, ствол и ветви образованы взаимными соединениями коммутаторов, а листья образованы подсоединенными к коммутаторам элементами и узлами.

Наиболее близким аналогом к заявленному является способ, реализованный в устройстве нейронной сети, состоящей из нейронов, которые выполняют функции обработки информации и принятия решения, где согласно формуле полезной модели имеются коммутаторы для передачи информации между нейронами, причем коммутатор нейронной сети состоит из таблицы связей нейронов, составляющих фрагмент сети, и устройства, передающего информацию между нейронами на основе этой таблицы, входы и выходы коммутатора соединены с входами и выходами других коммутаторов и входами и выходами нейронов сети, нейроны сети имеют один вход и один выход, входы и выходы нейрона соединены с входами и выходами коммутатора (Кабак И.С., Суханова Н.В. Нейронная сеть. Заявители Кабак И.С., Суханова Н.В. Патент на полезную модель №66831, приоритет 27.09.2007).

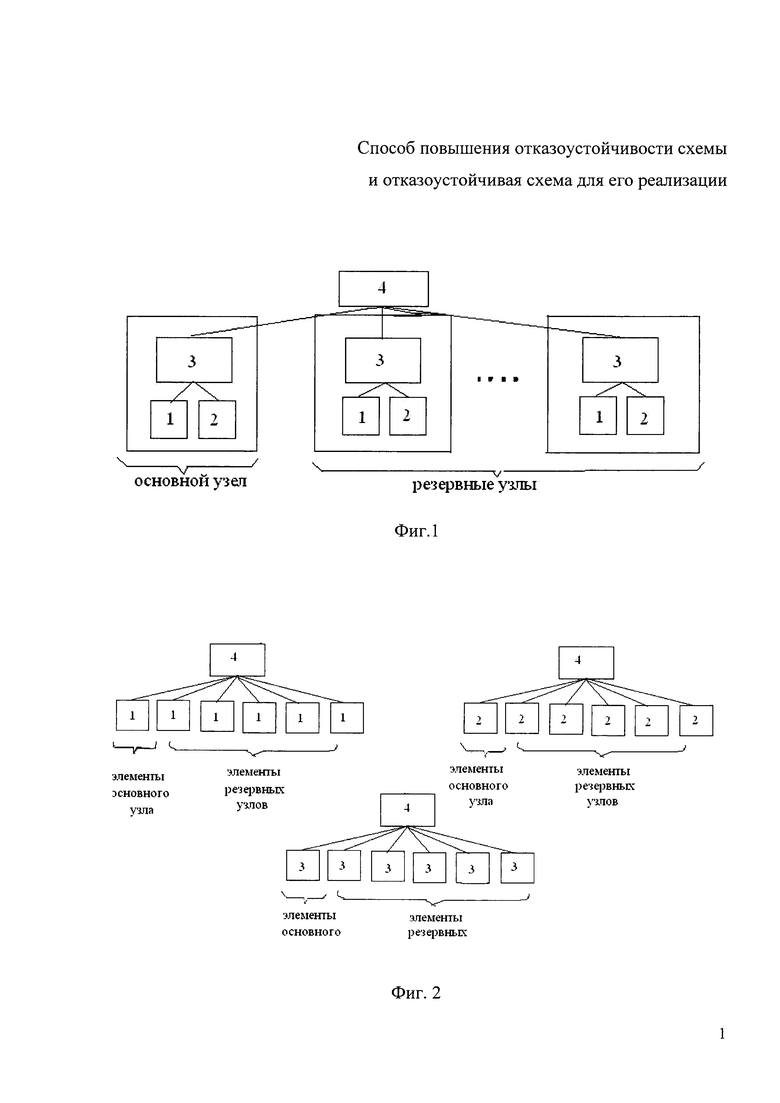

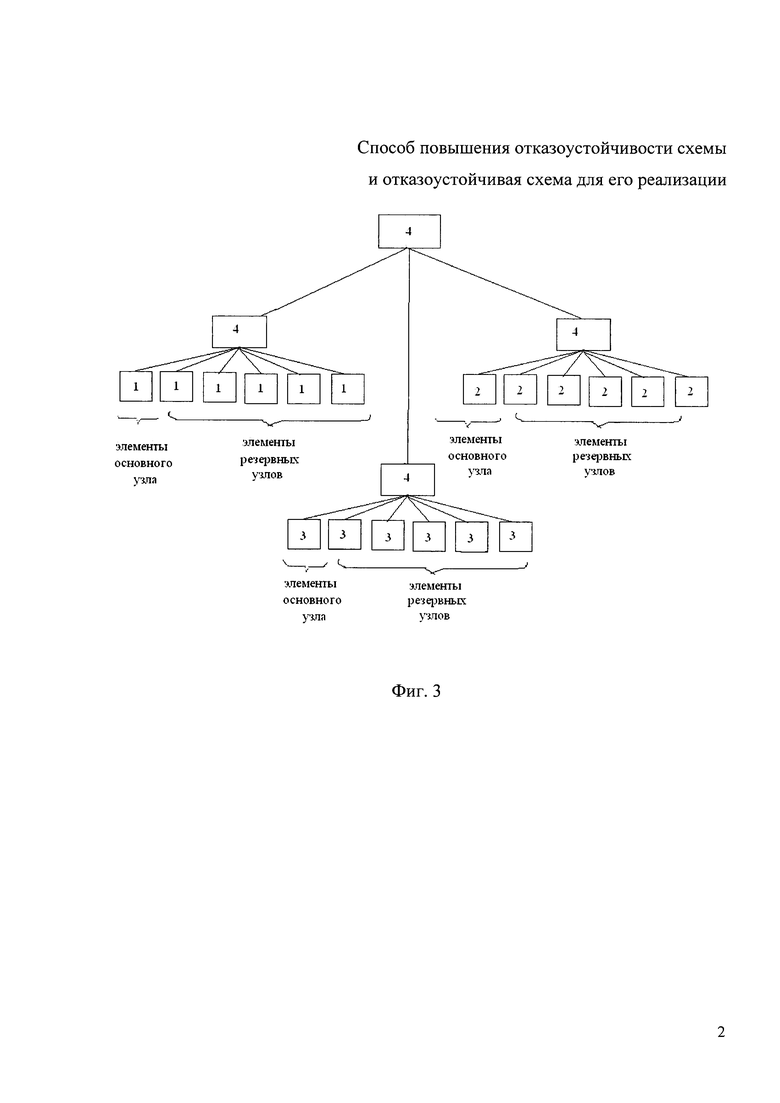

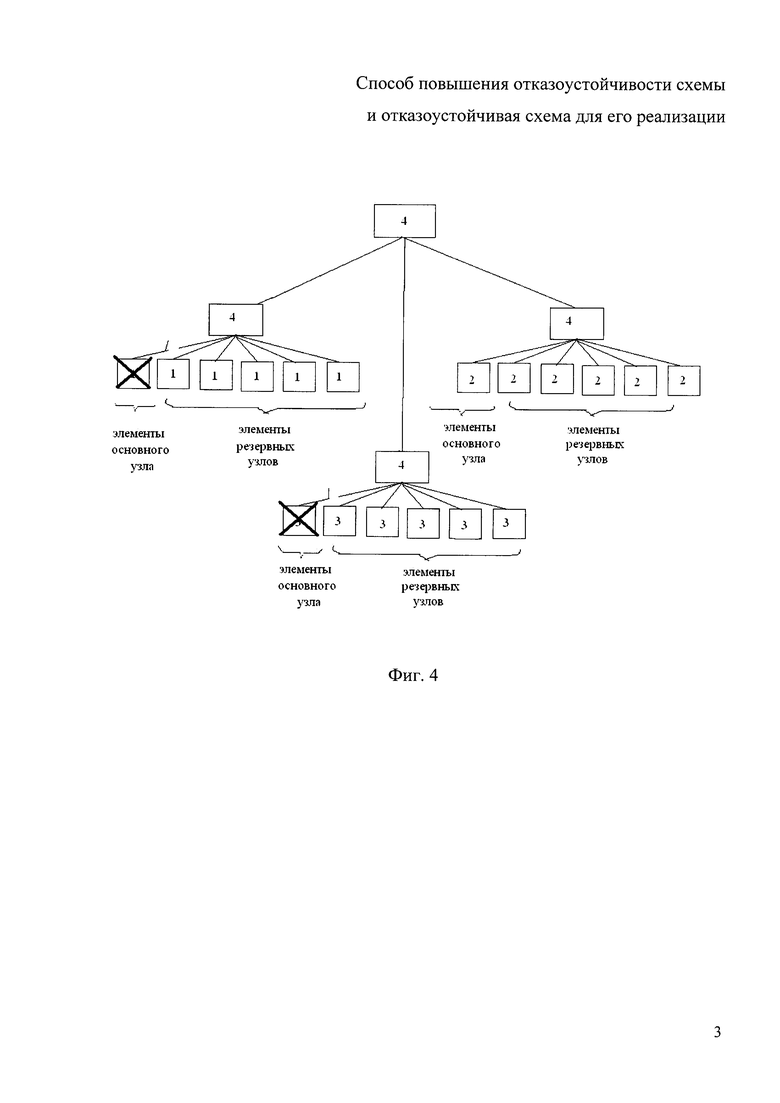

Заявленный способ повышения отказоустойчивости иллюстрируется графическими материалами, см. фиг. 1-3.

На фиг. 1-3 показан пример последовательности действий, составляющих заявленный способ повышения отказоустойчивости схемы.

На фиг. 3 показан результат реализации способа - разработанная отказоустойчивая схема.

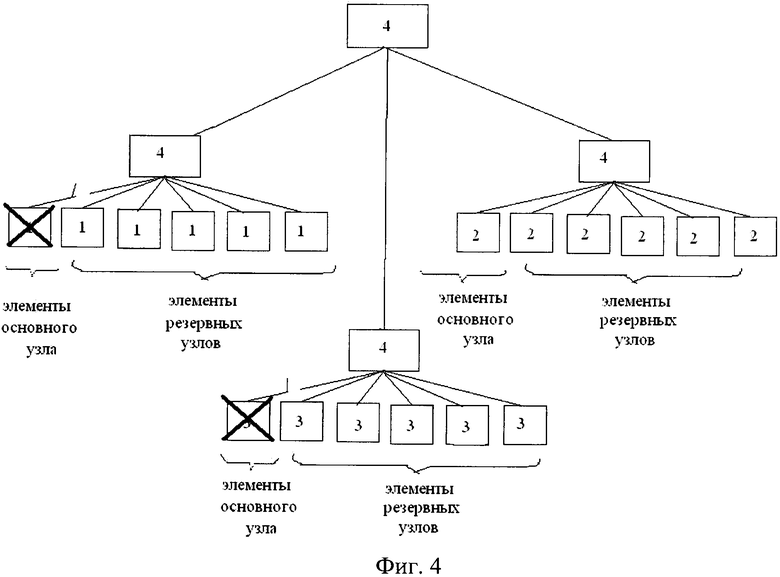

На фиг. 4 показан пример реконфигурации заявленной схемы при отказе ее основного узла.

Заявленный способ повышения отказоустойчивости состоит в следующем.

1. Проводят декомпозицию схемы и выделяют узлы, состоящие из унифицированных элементов. После этого добавляют один или несколько резервных узлов или элементов. На фиг. 1 показан пример схемы, где проведена декомпозиция и выделены основные и резервные узлы. Каждый узел состоит из трех разных элементов 1-3.

Новизна изобретения состоит в том, что в схему добавляют коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов. На фиг. 2 показан пример схемы, где добавлены коммутаторы 4. Эти коммутаторы реализуют связи элементов и узлов схемы.

2. Элементы одного типа объединяют в группу и подсоединяют к входам и выходам коммутаторов, которые соединяются друг с другом. На фиг. 2 показан пример схемы, где элементы одного типа (1-3) объединены в три группы и подсоединены к коммутаторам 4. Коммутаторы 4 соединяются друг с другом и образуют древовидную архитектуру. На фиг. 3 показан результат - отказоустойчивая схема.

3. Коммутаторы контролируют работоспособность элементов и узлов путем подачи одинаковых сигналов на входы элементов и сравнения сигналов на одноименных выходах. На входы основного и нескольких резервных элементов или узлов подают одинаковые сигналы и сравнивают сигналы на их выходах. Если сигналы совпали, то все элементы или узлы работоспособны. Если сигналы не совпали, то определяют, какие элементы или узлы неработоспособны. При отказах элементов или узлов коммутатор производит реконфигурацию схемы. Вместо основного он подключает резервный узел или элемент из той же группы, меняет таблицу взаимных связей и выполняет контроль работоспособности элементов отказавшего узла. Коммутатор отключает неработоспособные элементы, а избыточные работоспособные элементы переводит в резерв.

На фиг. 4 показан пример реконфигурации схемы при отказе ее основного узла. В узле отказали элементы 1 и 3. Коммутаторы 4 обнаружили отказы и отключили неработоспособные элементы.

Технический результат заявленного способа состоит в повышении отказоустойчивости схемы, которое достигается за счет соединения унифицированных элементов через коммутаторы и реконфигурации схемы при отказе элементов.

Технический результат, состоящий в повышении отказоустойчивости схемы, обеспечивается за счет того, что проводят декомпозицию схемы и выделяют узлы, состоящие из унифицированных элементов, после чего добавляют один или несколько резервных узлов или элементов, согласно заявленному изобретению, в схему добавляют коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, после чего элементы одного типа объединяют в группу и подсоединяют к входам и выходам коммутаторов, которые соединяются друг с другом и контролируют работоспособность элементов и узлов путем подачи одинаковых сигналов на входы элементов и сравнения сигналов на одноименных выходах, причем при отказах элементов или узлов коммутатор производит реконфигурацию схемы и вместо основного подключает резервный узел или элемент из той же группы, меняет таблицу взаимных связей, выполняет контроль работоспособности элементов отказавшего узла, после чего неработоспособные элементы отключает, а избыточные работоспособные элементы переводит в резерв.

Технический результат обеспечивается отказоустойчивой схемой, которая включает узлы, состоящие из унифицированных элементов, согласно заявленному изобретению, в ней имеются дополнительные коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, причем элементы одного типа объединены в группу и подсоединены к входам и выходам коммутаторов, которые, в свою очередь, соединяются друг с другом.

1. Способ повышения отказоустойчивости схемы, при котором проводят декомпозицию схемы и выделяют узлы, состоящие из унифицированных элементов, после чего добавляют один или несколько резервных узлов или элементов, отличающийся тем, что в схему добавляют коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, после чего элементы одного типа объединяют в группу и подсоединяют к входам и выходам коммутаторов, которые соединяются друг с другом и контролируют работоспособность элементов и узлов путем подачи одинаковых сигналов на входы элементов и сравнения сигналов на одноименных выходах, причем при отказах элементов или узлов коммутатор производит реконфигурацию схемы и вместо основного подключает резервный узел или элемент из той же группы, меняет таблицу взаимных связей, выполняет контроль работоспособности элементов отказавшего узла, после чего неработоспособные элементы отключает, а избыточные работоспособные элементы переводит в резерв.

2. Отказоустойчивая схема для реализации способа по п. 1, которая включает узлы, состоящие из унифицированных элементов, отличающаяся тем, что в ней имеются дополнительные коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, причем элементы одного типа объединены в группу и подсоединены к входам и выходам коммутаторов, которые, в свою очередь, соединяются друг с другом.

Коммутатор может быть реализован на базе патентов на полезную модель (№66831 Нейронная сеть, авторы Кабак И.С., Суханова Н.В. и №72084 Доменная нейронная сеть, авторы Кабак И.С., Суханова Н.В).

Заявленные в изобретении способ повышения отказоустойчивости и отказоустойчивая схема могут быть реализованы аппаратными или аппаратно-программными средствами, на базе контроллеров, компьютеров с установленным на них программным обеспечением и обученных нейронных сетей.

Указанные в независимом пункте формулы признаки являются существенными и взаимосвязаны между собой с образованием устойчивой совокупности необходимых признаков, достаточной для получения требуемого технического результата.

Свойства, регламентированные в заявленном способе отдельными признаками, общеизвестны из уровня техники и не требуют дополнительных пояснений.

Следует отметить, что заявленная совокупность существенных признаков обеспечивает в соединении синергетический (сверхсуммарный результат).

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного способа следующей совокупности условий:

- заявленный способ имеет практическое применение, предназначен для использования в вычислительных устройствах и системах управления;

- для заявленного способа в том виде, как он охарактеризован в независимом пункте нижеизложенной формулы, подтверждена возможность его осуществления с помощью указанных в заявке или известных из уровня техники на дату приоритета средств и методов;

- при осуществлении способа достигается усматриваемый заявителем технический результат.

На основании изложенного, заявленный способ повышения отказоустойчивости схем соответствуют требованию условия патентоспособности «новизна» и «изобретательский уровень».

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОБЕСПЕЧЕНИЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2664404C2 |

| СПОСОБ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И СХЕМА КОНТРОЛЯ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2669509C2 |

| ОТКАЗОУСТОЙЧИВАЯ НЕЙРОННАЯ СЕТЬ, СПОСОБ ОБНАРУЖЕНИЯ ОТКАЗОВ НЕЙРОННОЙ СЕТИ, СПОСОБ ОБЕСПЕЧЕНИЯ ОТКАЗОУСТОЙЧИВОСТИ НЕЙРОННОЙ СЕТИ | 2018 |

|

RU2760636C2 |

| МНОГОСЛОЙНАЯ МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2008 |

|

RU2398281C2 |

| СПОСОБ ИСПЫТАНИЙ ЭЛЕКТРОННОЙ СХЕМЫ НА ОТКАЗОУСТОЙЧИВОСТЬ И СТЕНД ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2664493C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| СПОСОБ ПОСТРОЕНИЯ СИСТЕМ НЕЧЕТКОЙ ЛОГИКИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2008 |

|

RU2417442C2 |

| Способ формирования отказоустойчивой комплексной системы управления (КСУ) и отказоустойчивая КСУ | 2016 |

|

RU2629454C2 |

| СПОСОБ КОНТРОЛЯ ДЛЯ РЕКОНФИГУРАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2022 |

|

RU2801202C1 |

Изобретение относится к области вычислительной техники и систем управления. Технический результат заключается в повышении отказоустойчивости схемы, которое достигается за счет соединения унифицированных элементов через коммутаторы и реконфигурации схемы при отказе элементов. Способ повышения отказоустойчивости состоит в следующем. Проводят декомпозицию схемы и выделяют ряд узлов. Каждый узел состоит из унифицированных элементов. В схему добавляют один или несколько избыточных резервных узлов, которые используют при отказе основных узлов. В схему добавляют коммутаторы, которые обеспечивают взаимные связи элементов в узле и узлов между собой. Коммутатор содержит таблицу коммутации входов и выходов, устройство для приема и передачи информации, схему для сравнения выходных сигналов. Элементы из одного или разных узлов объединяют в группы и подсоединяют к коммутаторам. Коммутаторы соединяют друг с другом. В процессе работы схемы коммутатор контролируют работоспособность элементов. Для этого на входы основного и нескольких резервных элементов или узлов подают одинаковые сигналы и сравнивают сигналы на их выходах. Если сигналы совпали, то все элементы или узлы работоспособны. Если сигналы не совпали, то определяют, какие элементы или узлы неработоспособны. При отказе элемента схемы происходит реконфигурация, когда вместо основного элемента подключается резервный элемент. При реконфигурации меняется таблица связей в коммутаторе, к которому подсоединен отказавший элемент. С помощью коммутатора отключают неработоспособные элементы или узлы, вместо них подключают работоспособные резервные элементы или узлы. Затем контролируют исправность элементов отказавшего узла, и все исправные элементы переводят в резерв. Заявленный способ реализован в устройстве отказоустойчивой схемы. Отказоустойчивая схема разработана на основе коммутаторной архитектуры и реализует древовидную структуру, где ветви образованы взаимными соединениями коммутаторов 4, а листья образованы подсоединенными к коммутаторам основными и резервными элементами 1,2,3. 2 н.п. ф-лы, 4 ил.

1. Способ повышения отказоустойчивости схемы, при котором проводят декомпозицию схемы и выделяют узлы, состоящие из унифицированных элементов, после чего добавляют один или несколько резервных узлов или элементов, отличающийся тем, что в схему добавляют коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, после чего элементы одного типа объединяют в группу и подсоединяют к входам и выходам коммутаторов, которые соединяются друг с другом и контролируют работоспособность элементов и узлов путем подачи одинаковых сигналов на входы элементов и сравнения сигналов на одноименных выходах, причем при отказах элементов или узлов коммутатор производит реконфигурацию схемы и вместо основного подключает резервный узел или элемент из той же группы, меняет таблицу взаимных связей, выполняет контроль работоспособности элементов отказавшего узла, после чего неработоспособные элементы отключает, а избыточные работоспособные элементы переводит в резерв.

2. Отказоустойчивая схема для реализации способа по п. 1, которая включает узлы, состоящие из унифицированных элементов, отличающаяся тем, что в ней имеются дополнительные коммутаторы, которые содержат таблицу взаимных связей входов и выходов, устройство для приема и передачи сигналов, а также схему с функциональной возможностью сравнения выходных сигналов, причем элементы одного типа объединены в группу и подсоединены к входам и выходам коммутаторов, которые, в свою очередь, соединяются друг с другом.

| Устройство для управления стрелкой в системе электрической централизации | 1939 |

|

SU66831A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| УСТРОЙСТВО МАЖОРИТАРНОГО РЕЗЕРВИРОВАНИЯ (ВАРИАНТЫ) | 2005 |

|

RU2298823C2 |

| US 5423024 A, 06.01.1995. | |||

Авторы

Даты

2017-09-29—Публикация

2016-02-01—Подача