Заявленное устройство нейронной сети относится к вычислительной технике и может использоваться для создания систем управления с искусственным интеллектом. Искусственный интеллект реализован в виде обученной искусственной нейронной сети (ИНС).

Известно устройство ИНС, состоящих из элементов одного типа - нейронов [1-5]. Нейрон имеет много входов и много выходов для связи с другими нейронами. Нейрон выполняет две основные функции:

1. Прием, обработку и хранение информации. Информационные сигналы с выходов других нейронов поступают на входы нейрона. Нейрон суммирует входные сигналы с учетом коэффициентов взаимных связей и вычисляет результат. Результат сравнивается с функцией активации и по результатам сравнения формируется состояние нейрона и соответствующий ему выходной сигнал.

2. Передачу информации между нейронами. С выхода одного нейрона сигнал передается на соответствующие входы других нейронов.

С ростом количества нейронов увеличивается число их взаимных связей, усложняется структура и работа нейронной сети. В больших нейронных сетях не решены проблемы масштабирования, подключения дополнительных нейронов и фрагментов сети. Время обучения большой ИНС зависит от числа нейронов.

Известна нейронная сеть особой структуры, где использованы элементы двух типов - нейроны и коммутаторы [6]. Эта нейронная сеть позволяет решить выше названные проблемы реализации больших нейронных сетей, но она имеет существенный недостаток - низкую, недостаточную надежность древовидного взаимного соединения коммутаторов. Большая ИНС будет функционировать ненадежно, т.к. в ней отсутствуют средства для контроля ее работоспособности и восстановления при отказах. Для обеспечения отказоустойчивости устройств используют резервные избыточные элементы, которые подключают при отказах основных элементов [7].

Наиболее близким по технической сущности к заявляемой отказоустойчивой нейронной сети является нейронная сеть [6]. Она принята в качестве прототипа.

В изобретении заявлено новое устройство отказоустойчивой нейронной сети. Отказоустойчивая нейронная сеть состоит из элементов двух типов, из нейронов и коммутаторов. Нейроны выполняют функции обработки информации и принятия решения. Коммутаторы выполняют функции передачи информации. Коммутатор состоит из таблицы взаимных связей входов и выходов и устройства, передающего информацию между его входами и выходами на основе этой таблицы. Входы и выходы коммутатора соединены с входами и выходами других коммутаторов и входами и выходами нейронов сети. Нейроны сети имеют один вход и один выход. Входы и выходы нейрона соединены с входами и выходами коммутатора.

Согласно изобретению, в отказоустойчивой нейронной сети имеются избыточные элементы, которые подключаются при отказах основных элементов. Отказоустойчивость обеспечивается структурными методами за счет отключения неисправных элементов и подключения избыточных резервных элементов. К каждому коммутатору подсоединен по крайней мере один избыточный нейрон. Коммутаторы соединены между собой по входам и выходам и образуют многосвязную сеть, в которой имеется хотя бы один избыточный путь между каждой парой коммутаторов и имеется по крайней мере один избыточный коммутатор. Кроме того, имеется хотя бы один избыточный коммутатор верхнего уровня, который соединен с входами и выходами нейронной сети и входами и выходами других коммутаторов.

Отказоустойчивая нейронная сеть формируется из фрагментов, соединенных между собой посредством коммутаторов. Фрагменты имеют такую же структуру, как и вся отказоустойчивая ИНС.

Согласно изобретению, имеется хотя бы один избыточный фрагмент нейронной сети, в котором количество коммутаторов и нейронов не меньше, чем в любом другом фрагменте нейронной сети. Этот фрагмент используется для замены других, неисправных фрагментов при отказах.

Нейронная сеть обучается по фрагментам, с использованием одного из известных методов обучения. Общие принципы обучения нейронных сетей описаны в [4]. При обучении ИНС формируются значения коэффициентов взаимных связей нейронов друг с другом. Сначала коэффициенты взаимных связей нейронов объединяют в строки, а затем строки - в таблицу.

Результат обучения нейронной сети записан в форме коэффициентов взаимных связей в соответствующих строках таблицы в коммутаторах. Для избыточных нейронов, коммутаторов и фрагментов в соответствующих строках таблицы записаны нулевые значения.

Заявлен новый способ обнаружения отказов отказоустойчивой нейронной сети. Способ обнаружения отказов отказоустойчивой нейронной сети состоит из следующей последовательности действий.

1. Используют два одинаковых устройства ИНС, основное и избыточное. Избыточное устройство ИНС является эталоном для контроля работоспособности основного устройства ИНС.

2. Согласно изобретению, сначала в соответствующие коммутаторы основного и избыточного устройства записывают одинаковую информацию. Информация, записанная в коммутаторы, формируется при обучении ИНС и представляет собой таблицу коэффициентов взаимных связей нейронов.

3. Потом на одноименные входы основного и избыточного устройств ИНС подают одинаковые тестовые сигналы. При этом на выходах коммутаторов верхнего уровня формируются выходные сигналы ИНС, которые должны соответствовать тестовым значениям.

4. Затем последовательно сравнивают сигналы в двух устройствах ИНС на входах и выходах коммутаторов верхнего уровня. При отказах основного устройства имеются расхождения в одноименных входных и выходных сигналах двух коммутаторов. При расхождении в значениях одноименных входных и выходных сигналах в коммутаторах основной и избыточной ИНС принимается решение об отказе в основной ИНС.

Заявлен новый способ обеспечения отказоустойчивости нейронной сети. Способ обеспечения отказоустойчивости нейронной сети состоит из следующей последовательности действий.

1. Согласно изобретению, сначала все элементы и фрагменты в нейронной сети разделяют на две группы - основные и избыточные.

2. Затем проводят обучение нейронной сети, используя основные нейроны. Потом результаты обучения нейронов в форме строк таблицы коэффициентов взаимных связей записывают в коммутаторы. В строки таблицы взаимных связей избыточных элементов записывают нулевые значения.

3. Для обнаружения отказа основных элементов используют способ, описанный выше.

4. Если обнаруживают отказ в основных элементах и фрагментах нейронной сети, то в коммутатор записывают новую информацию. Строки и столбцы таблицы взаимных связей коммутатора, соответствующие неисправным основным элементам и фрагментам нейронной сети копируют в соответствующие строки и столбцы таблицы, соответствующие избыточным элементам и фрагментам. После этого в строки и столбцы таблицы взаимных связей неисправных элементов записывают нулевые значения. Избыточные элементы и фрагменты заменяют неисправные основные элементы и фрагменты. Подсоединение избыточных и отсоединение неисправных основных элементов и фрагментов происходит путем записи информации в таблицу взаимных связей коммутаторов. Подсоединение избыточных элементов и фрагментов обеспечивает восстановление работоспособного состояния нейронной сети.

Технический результат изобретения заключается в обеспечении отказоустойчивой нейронной сети.

Сущность заявленного изобретения состоит в следующем.

Отказоустойчивая нейронная сеть, состоящая из элементов двух типов, из нейронов, которые выполняют функции обработки информации и принятия решения и коммутаторов для передачи информации, причем коммутатор состоит из таблицы взаимных связей входов и выходов и устройства, передающего информацию между его входами и выходами на основе этой таблицы, где входы и выходы коммутатора соединены с входами и выходами других коммутаторов и входами и выходами нейронов сети, причем нейроны сети имеют один вход и один выход, входы и выходы нейрона соединены с входами и выходами коммутатора,

согласно изобретению, к каждому коммутатору подсоединен по крайней мере один избыточный нейрон, коммутаторы соединены между собой по входам и выходам и образуют многосвязную сеть, в которой имеется хотя бы один избыточный путь между каждой парой коммутаторов и имеется по крайней мере один избыточный коммутатор, а также имеется хотя бы один избыточный коммутатор верхнего уровня, который соединен с входами и выходами нейронной сети и входами и выходами других коммутаторов.

Отказоустойчивая нейронная сеть, которая формируется из фрагментов, соединенных между собой посредством коммутаторов, согласно изобретению, имеется хотя бы один избыточный фрагмент нейронной сети, в котором количество коммутаторов и нейронов не меньше, чем в любом другом фрагменте нейронной сети.

Отказоустойчивая нейронная сеть, где согласно изобретению, результат обучения нейронной сети записан в форме коэффициентов взаимных связей в соответствующих строках таблицы в коммутаторах, причем для избыточных нейронов, коммутаторов и фрагментов в соответствующих строках таблицы записаны нулевые значения.

Способ обнаружения отказов отказоустойчивой нейронной сети, когда используют два одинаковых устройства нейронной сети, основное и избыточное, причем избыточное устройство является эталоном для контроля работоспособности основного, согласно изобретению, сначала в соответствующие коммутаторы основного и избыточного устройств нейронной сети записывают одинаковую информацию, потом на одноименные входы двух устройств нейронной сети подают одинаковые тестовые сигналы, затем последовательно сравнивают сигналы в двух устройствах нейронной сети на входах и выходах коммутаторов верхнего уровня, причем при отказах основного устройства имеются расхождения в одноименных входных и выходных сигналах упомянутых двух коммутаторов.

Способ обеспечения отказоустойчивости нейронной сети, при котором согласно изобретению, сначала все элементы и фрагменты в нейронной сети разделяют на две группы - основные и избыточные, затем проводят обучение нейронной сети, используя основные нейроны, потом результаты обучения в форме строк таблицы коэффициентов взаимных связей записывают в коммутаторы, причем в строки таблицы взаимных связей избыточных элементов записывают нулевые значения, после чего обнаруживают отказ в основных элементах и фрагментах нейронной сети, затем строки и столбцы таблицы взаимных связей коммутатора, соответствующие неисправным основным элементам и фрагментам нейронной сети копируют в соответствующие строки и столбцы таблицы, соответствующие избыточным элементам и фрагментам, после чего в строки и столбцы таблицы взаимных связей неисправных элементов записывают нулевые значения.

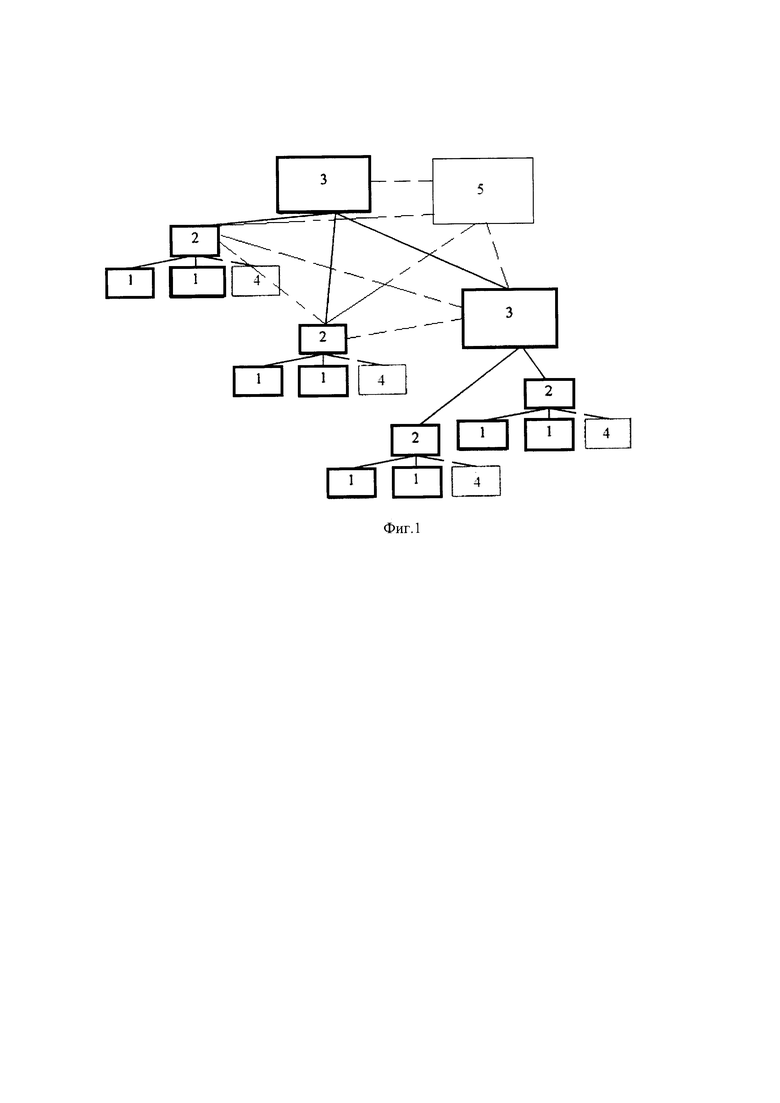

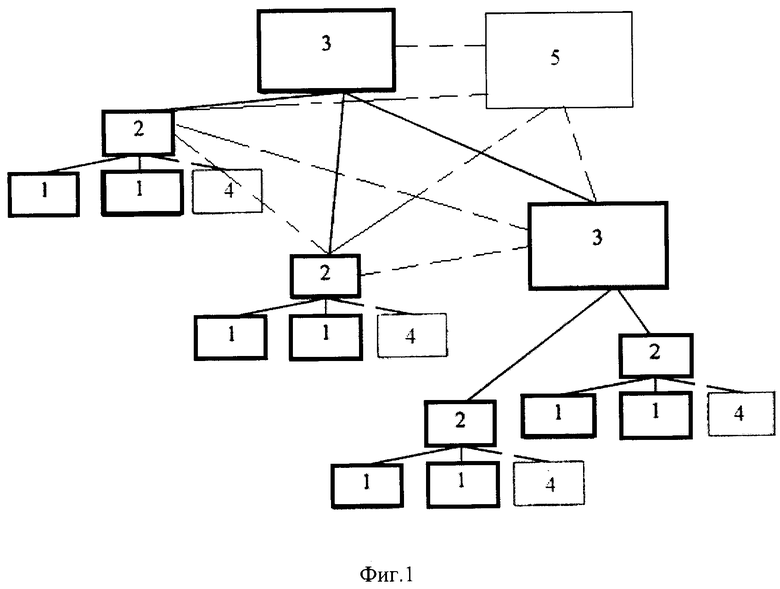

Схема заявленного устройства отказоустойчивой нейронной сети представлена на фиг. 1.

Заявленная нейронная сеть содержит два типа элементов - основные и резервные (см. фиг. 1), в том числе:

- основные нейроны 1, которые обрабатывают информацию;

- основные коммутаторы нижнего уровня 2, которые обеспечивают передачу информации между нейронами 1;

- коммутаторы верхнего уровня 3, входы и выходы которых соединены с коммутаторами нижнего уровня 2.

- резервные избыточные нейроны 4, которые подключаются при отказах основных нейронов 1,

- резервные избыточные коммутаторы 5, которые подключаются при отказах основных коммутаторов нижнего уровня 2 или верхнего уровня 3.

К коммутатору нижнего уровня 2 можно подключить ограниченное количество нейронов, которые образуют фрагмент нейронной сети. Масштабирование нейронной сети, увеличение числа нейронов может осуществляться путем увеличения количества коммутаторов нижнего уровня. Для взаимного соединения коммутаторов нижнего уровня в многосвязную сеть используются коммутаторы верхнего уровня 3. В многосвязной сети имеются резервные избыточные пути между каждой парой коммутаторов. Для упрощения информационного обмена между нейронами взаимные избыточные связи переведены в резерв, а основные связи между коммутаторами приведены к виду древовидной структуры, узлами которой являются коммутаторы, а листьями - нейроны (фиг. 1).

Отказоустойчивая нейронная сеть может быть реализована аппаратными, программными или аппаратно- программными средствами. При программной реализации нейронной сети нейроны и коммутаторы могут быть реализованы как программные средства, например с применением методов объектно-ориентированного программирования. При аппаратной реализации нейроны и коммутаторы реализованы как устройства, например с применением микроконтроллеров, микропроцессоров, программируемых логических интегральных микросхем и нейрочипов. При аппаратно-программной реализации нейроны и коммутаторы могут быть реализованы как программируемые устройства например, микроконтроллеры, микропроцессоры, программируемые логические интегральные микросхемы, нейрочипы.

Указанные в независимом пункте формулы признаки новизны отказоустойчивой нейронной сети являются существенными и взаимосвязаны между собой с образованием требуемого технического результата.

Свойства, регламентированные в заявленных способах обнаружения отказов и обеспечения отказоустойчивости отдельными признаками, общеизвестны из уровня техники и не требуют дополнительных пояснений.

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного способа обнаружения отказов и обеспечения отказоустойчивости следующей совокупности условий:

- заявленный способ обнаружения отказов имеет практическое применение, предназначен для контроля работоспособности нейронной сети;

- заявленный способ обеспечения отказоустойчивости имеет практическое применение, предназначен для восстановления работоспособности при отказах нейронной сети;

- для заявленных способов обнаружения отказов и обеспечения отказоустойчивости подтверждена возможность осуществления с помощью указанных в заявке или известных из уровня техники на дату приоритета средств и методов;

- при осуществлении способов обнаружения отказов и обеспечения отказоустойчивости нейронной сети достигается усматриваемый заявителем технический результат.

На основании изложенного, устройство отказоустойчивой нейронной сети и заявленные способы обнаружения отказов и обеспечения отказоустойчивости соответствуют требованию условия патентоспособности «новизна» и «изобретательский уровень».

Источники информации, принятые во внимание при составлении описания изобретения:

1. Уоссермен Ф. Нейрокомпьютерная техника. - М.: Мир, 1992. - С. 52-69. /Л.-1/.

2. Розенблатт Ф. Принципы нейродинамики. - М.: Мир, 1965. - С. 242-247. /Л.-3/.

3. Хайкин Саймон, «Нейронные сети: полный курс», 2-е изд.: Пер. с англ. - М.: Издательский дом «Вильямс», 2006. - 1104 с. /Л.-4/.

4. Каллан Роберт, «Основные концепции нейронных сетей»: Пер. с англ. - М.: Издательский дом «Вильямс», 2001. - 288 с. /Л.-5/.

5. Эндрю А. Искусственный интеллект. - М.: Мир, 1985. - 246 с. /Л.-6/.

6. Патент на полезную модель 66831 G06G 7/66 РФ Нейронная сеть. Заявитель и патентообладатель Кабак И.С., Суханова Н.В. Заявка: 2007111998/22, приоритет 02.04.2007 Опубликовано: 27.09.2007 Бюл. №27.

7. Надежность технических систем. Справочник под ред. Ушакова И.А. М.: Радио и связь, 1985 - 606 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОВЫШЕНИЯ ОТКАЗОУСТОЙЧИВОСТИ СХЕМЫ И ОТКАЗОУСТОЙЧИВАЯ СХЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2631987C2 |

| СПОСОБ ОБЕСПЕЧЕНИЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2664404C2 |

| СПОСОБ ИСПЫТАНИЙ ЭЛЕКТРОННОЙ СХЕМЫ НА ОТКАЗОУСТОЙЧИВОСТЬ И СТЕНД ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2664493C1 |

| СПОСОБ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И СХЕМА КОНТРОЛЯ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2669509C2 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| ИСКУССТВЕННАЯ НЕЙРОННАЯ СЕТЬ | 2014 |

|

RU2573766C1 |

| Способ обучения искусственной нейронной сети | 2019 |

|

RU2723270C1 |

| СПОСОБ И ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ОТКАЗОУСТОЙЧИВОЙ ОБРАБОТКИ ИНФОРМАЦИИ КРИТИЧЕСКИХ ФУНКЦИЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2008 |

|

RU2413975C2 |

| СПОСОБ ИНТЕРПРЕТАЦИИ ИСКУССТВЕННЫХ НЕЙРОННЫХ СЕТЕЙ | 2018 |

|

RU2689818C1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО | 2004 |

|

RU2297031C2 |

Изобретение относится к области вычислительной техники. Технический результат изобретения заключается в обеспечении отказоустойчивой нейронной сети. Раскрыта отказоустойчивая нейронная сеть, состоящая из элементов двух типов, из нейронов, которые выполняют функции обработки информации и принятия решения, и коммутаторов для передачи информации, причем коммутатор состоит из таблицы взаимных связей входов и выходов и устройства, передающего информацию между его входами и выходами на основе этой таблицы, где входы и выходы коммутатора соединены с входами и выходами других коммутаторов и входами и выходами нейронов сети, причем нейроны сети имеют один вход и один выход, входы и выходы нейрона соединены с входами и выходами коммутатора, при этом к каждому коммутатору подсоединен по крайней мере один избыточный нейрон, коммутаторы соединены между собой по входам и выходам и образуют многосвязную сеть, в которой имеется хотя бы один избыточный путь между каждой парой коммутаторов и имеется по крайней мере один избыточный коммутатор, а также имеется хотя бы один избыточный коммутатор верхнего уровня, который соединен с входами и выходами нейронной сети и входами и выходами других коммутаторов. 3 н. и 2 з.п. ф-лы, 1 ил.

1. Отказоустойчивая нейронная сеть, состоящая из элементов двух типов, из нейронов, которые выполняют функции обработки информации и принятия решения, и коммутаторов для передачи информации, причем коммутатор состоит из таблицы взаимных связей входов и выходов и устройства, передающего информацию между его входами и выходами на основе этой таблицы, где входы и выходы коммутатора соединены с входами и выходами других коммутаторов и входами и выходами нейронов сети, причем нейроны сети имеют один вход и один выход, входы и выходы нейрона соединены с входами и выходами коммутатора,

отличающаяся тем, что к каждому коммутатору подсоединен по крайней мере один избыточный нейрон, коммутаторы соединены между собой по входам и выходам и образуют многосвязную сеть, в которой имеется хотя бы один избыточный путь между каждой парой коммутаторов и имеется по крайней мере один избыточный коммутатор, а также имеется хотя бы один избыточный коммутатор верхнего уровня, который соединен с входами и выходами нейронной сети и входами и выходами других коммутаторов.

2. Отказоустойчивая нейронная сеть по п. 1, где нейронная сеть формируется из фрагментов, соединенных между собой посредством коммутаторов, отличающаяся тем, что имеется хотя бы один избыточный фрагмент нейронной сети, в котором количество коммутаторов и нейронов не меньше, чем в любом другом фрагменте нейронной сети.

3. Отказоустойчивая нейронная сеть по п. 1, отличающаяся тем, что результат обучения нейронной сети записан в форме коэффициентов взаимных связей в соответствующих строках таблицы в коммутаторах, причем для избыточных нейронов, коммутаторов и фрагментов в соответствующих строках таблицы записаны нулевые значения.

4. Способ обнаружения отказов в отказоустойчивой нейронной сети по п. 1, когда используют два одинаковых устройства нейронной сети, основное и избыточные, причем избыточное устройство нейронной сети является эталоном для контроля работоспособности основного, отличающийся тем, что сначала в соответствующие коммутаторы основного и избыточного устройств нейронной сети записывают одинаковую информацию, потом на одноименные входы двух упомянутых устройств нейронной сети подают одинаковые тестовые сигналы, затем последовательно сравнивают сигналы в двух устройствах нейронной сети на входах и выходах коммутаторов верхнего уровня, причем при отказах основного устройства нейронной сети имеются расхождения в одноименных входных и выходных сигналах двух упомянутых коммутаторов.

5. Способ обеспечения отказоустойчивости нейронной сети по п. 1, отличающийся тем, что сначала все элементы и фрагменты в нейронной сети разделяют на две группы - основные и избыточные, затем проводят обучение нейронной сети, используя основные нейроны, потом результаты обучения в форме строк таблицы коэффициентов взаимных связей записывают в коммутаторы, причем в строки таблицы взаимных связей избыточных элементов записывают нулевые значения, после чего обнаруживают отказ в основных элементах и фрагментах нейронной сети, затем строки и столбцы таблицы взаимных связей коммутатора, соответствующие неисправным основным элементам и фрагментам нейронной сети, копируют в соответствующие строки и столбцы таблицы, соответствующие избыточным элементам и фрагментам, после чего в строки и столбцы таблицы взаимных связей неисправных элементов записывают нулевые значения.

| СПОСОБ ОБЕСПЕЧЕНИЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2664404C2 |

| СПОСОБ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И СХЕМА КОНТРОЛЯ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2669509C2 |

| СПОСОБ ПОВЫШЕНИЯ ОТКАЗОУСТОЙЧИВОСТИ СХЕМЫ И ОТКАЗОУСТОЙЧИВАЯ СХЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2631987C2 |

| US 5706400 A, 06.01.1998 | |||

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

Авторы

Даты

2021-11-29—Публикация

2018-12-19—Подача