Изобретение относится к области вычислительной техники, к цифровым вычислительным системам.

Технический результат - обеспечение работоспособности вычислительных систем, оперативное обнаружение отказов в процессе их работы, автоматическое восстановление при отказах.

В работоспособном состоянии все параметры, описывающие работу вычислительной системы и ее способность выполнять заданные функции, находятся в установленных диапазонах значений. В неработоспособном состоянии хотя бы один из параметров, описывающих работу системы и ее способность выполнять заданные функции, вышел за пределы установленного диапазона значений (Надежность технических систем. Справочник под ред. Ушакова И.А. М.: Радио и связь, 1985. - 606 с.).

При контроле работоспособности выполняют измерения сигналов, характеризующих состояние вычислительной системы, сравнивают результат с интервалом допустимых значений или с заданной величиной с учетом допуска.

В сложных вычислительных системах количество контролируемых сигналов измеряется сотнями и тысячами. Для каждого сигнала требуется реализовать устройство контроля, что увеличивает сложность и затраты, снижает эффективность работы вычислительной системы.

В заявленном изобретении предложен новый способ для обеспечения работоспособности вычислительных систем.

Сначала вычислительную систему разделяются на составные части в соответствии с заданными функциями. Затем к вычислительной системе добавляют резервные составные части и коммутаторы. Основные и резервные составные части соединяют между собой с помощью коммутаторов. Вычислительная система приводится к виду системы с коммутаторной архитектурой.

Коммутаторные вычислительные системы были разработаны и описаны в книгах Каляева А.В. и Каляева И.А. (Каляев А.В. Многопроцессорные системы с программируемой архитектурой [Текст] / А.В. Каляев. - М.: Радио и связь. 1984. - 240 с., Каляев И.А., Левин И.И., Семериков Е.А., Шмойлов В.И. Реконфигурируемые мультиконвейерные вычислительные структуры [Текст] / И.А. Каляев, И.И. Левин, Е.А. Семериков, В.И. Шмойлов. - Ростов-на-Дону: Издательство ЮНЦ РАН, 2008. - 393 с.).

В известных многопроцессорных системах коммутаторная архитектура использовалась для адаптации структуры вычислительной системы к решаемой задаче при потоковой обработке данных. В заявленном изобретении коммутаторная архитектура используется по-новому для обеспечения работоспособного состояния вычислительной системы.

Для контроля работоспособного состояния вычислительной системы предлагается использовать искусственную нейронную сеть (ИНС). ИНС состоит из фрагментов. Контроль входных и выходных сигналов для каждой составной части вычислительной системы выполняет отдельный фрагмент ИНС, реализованный как слой. Таким образом, ИНС будет состоять из множества слоев. Фрагменты ИНС обучают. Обучающая выборка содержит значения входных и выходных сигналов ИНС. При обучении на входы фрагмента ИНС подают значения входных и выходных сигналов составной части вычислительной системы. На выходах фрагмента ИНС формируют сигналы работоспособного состояния или команды реконфигурации при отказах составных частей вычислительной системы.

Обученные фрагменты объединяют в многослойную ИНС. Число нейронов входного слоя ИНС равно суммарному числу контролируемых входных и выходных сигналов составных частей вычислительной системы. Число нейронов выходного слоя ИНС равно числу составных частей вычислительной системы без учета их резервирования.

В работоспособном состоянии вычислительной системы на всех выходах ИНС формируются сигналы «1». В неработоспособном состоянии неисправна хотя бы одна составная часть вычислительной системы. В неработоспособном состоянии вычислительной системы хотя бы на одном выходе ИНС формируется сигнал «0». Эти сигналы поступают на вход соответствующего коммутатора и являются командой реконфигурации.

При реконфигурации коммутатор отключает неисправные составные части и вместо них подключает резервные составные части. При реконфигурации изменяются взаимные связи между входами и выходами коммутатора.

Коммутатор содержит оперативную память, в ячейках которой записана таблица коммутации. Взаимные связи между входными и выходными сигналами коммутатора определяются информацией, которая хранится в ячейках оперативной памяти. Таким образом, при реконфигурации изменяется таблица взаимных связей, которая хранится в памяти коммутатора.

Наиболее близкий аналог (прототип) изобретения - это коммутаторная нейронная сеть (Кабак И.С., Суханова Н.В. Нейронная сеть. Заявители Кабак И.С., Суханова Н.В. Патент на полезную модель №66831 приоритет 27.09.2007). Коммутаторная нейронная сеть включает нейроны и коммутаторы. Нейрон имеет один вход и один выход. Вход и выход нейрона подсоединены к коммутатору. Коммутаторы соединены с нейронами и с другими коммутаторами. Коммутаторы реализуют взаимные связи между нейронами. Коммутатор содержит таблицу коэффициентов взаимных связей нейронов и устройство для приема и передачи сигналов на основе этой таблицы. При обучении коммутаторной ИНС в память коммутаторов записывают таблицу взаимных связей нейронов. Путем формирования и загрузки таблицы взаимных связей нейронов можно реализовать ИНС с разными функциями. Коммутаторы позволяют отключать и подключать нейроны без необходимости переключения контактов.

Заявленный способ обеспечения работоспособного состояния вычислительной системы иллюстрируется графическими материалами, см. фиг. 1-7.

На фиг. 1-4 показан пример последовательности действий, составляющих заявленный способ обеспечения работоспособности вычислительной системы.

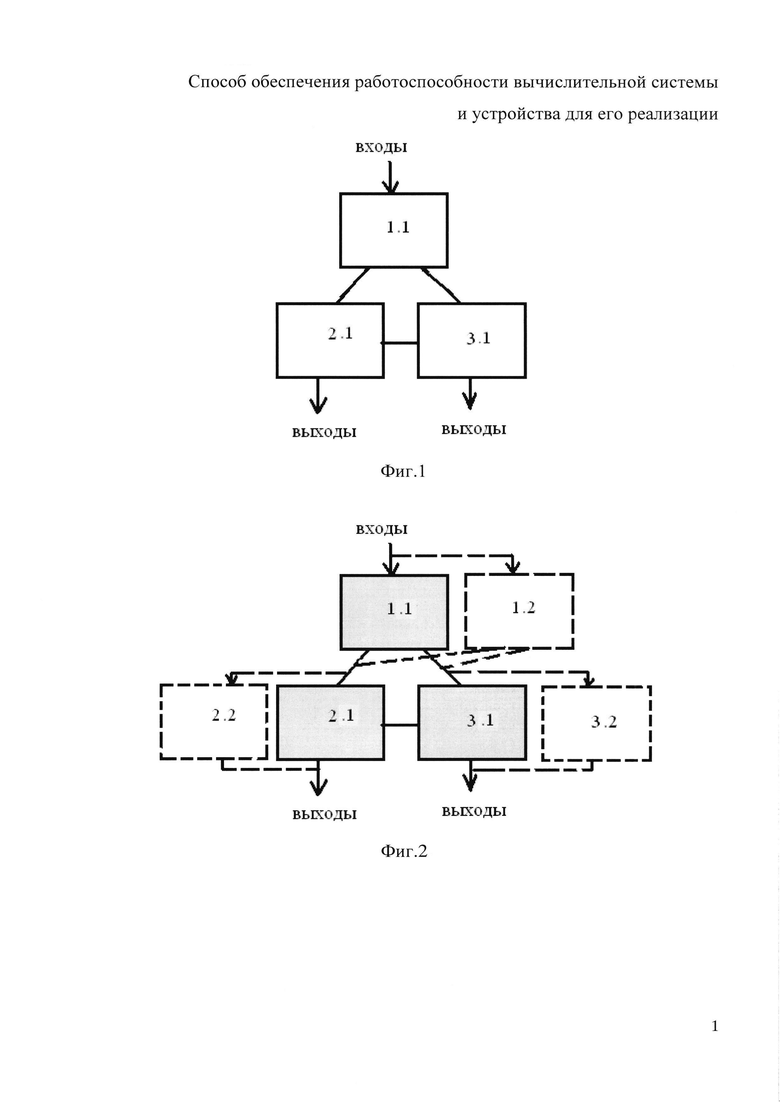

На фиг. 1 показана схема вычислительной системы, где выделены составные части в соответствии с выполняемыми функциями (блоки 1.1, 2.1, 3.1).

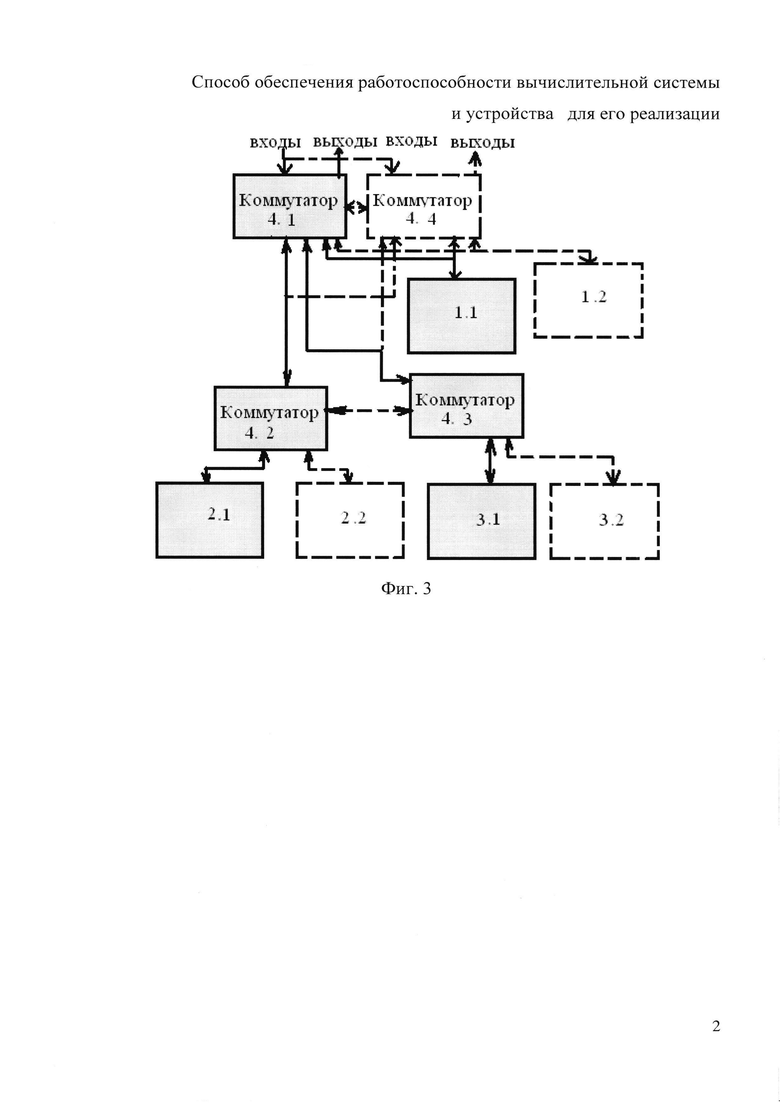

На фиг. 2 в схему вычислительной системы добавлены резервные составные части (1.2, 2.2, 3.2). Основные части выделены серым цветом (блоки 1.1, 2.1, 3.1). Резервные части показаны пунктирной линией (1.2, 2.2, 3.2).

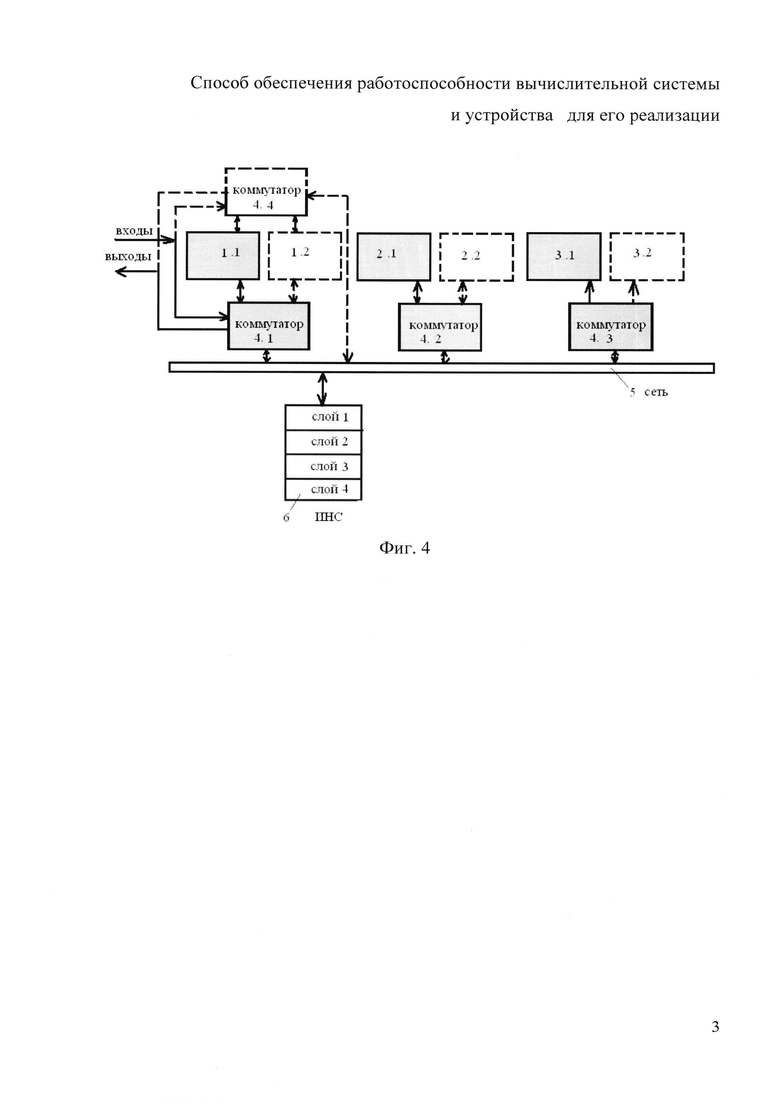

На фиг. 3 в схему вычислительной системы добавлены коммутаторы (4.1, 4.2, 4.3, 4.4). Показана схема коммутаторной вычислительной системы, где основные и резервные составные части соединены между собой через коммутаторы. Основные коммутаторы выделены серым цветом (4.1, 4.2, 4.3). Избыточные резервные коммутаторы и связи показаны пунктирной линией (4.4).

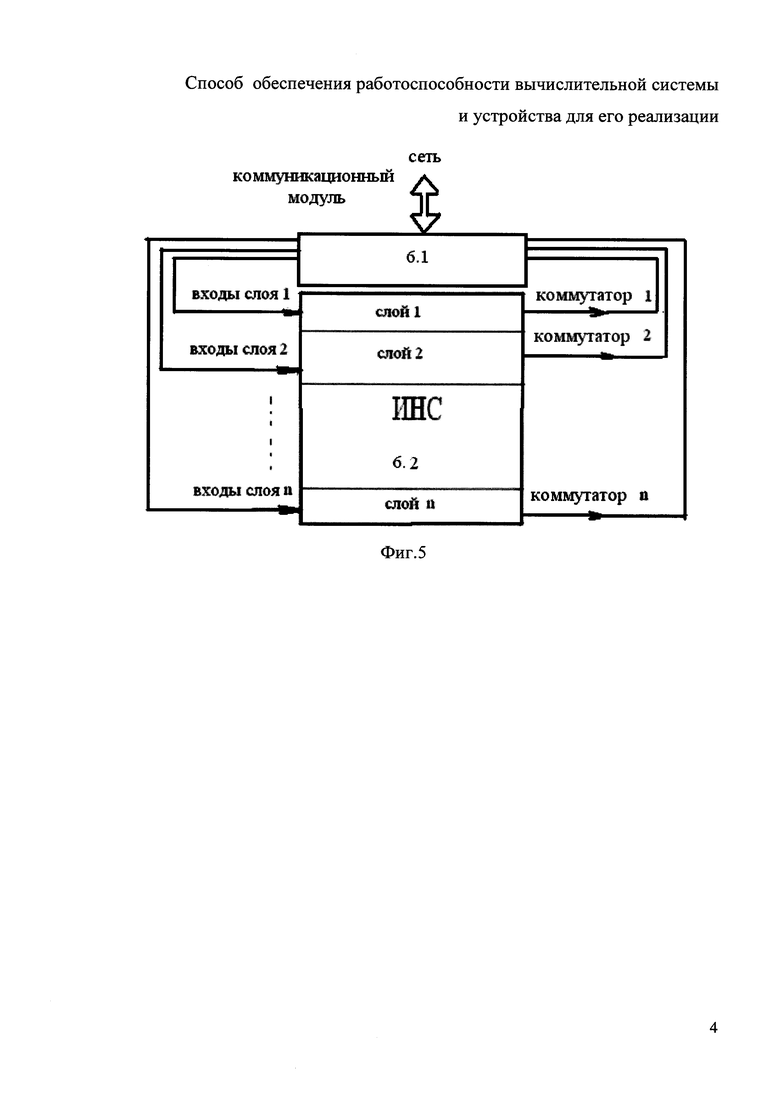

На фиг. 4 показана схема коммутаторной вычислительной системы, где основные и резервные коммутаторы соединены сетью передачи данных 5. К сети подключена схема контроля на базе ИНС 6.

На фиг. 5 показана схема контроля. Схема контроля содержит коммуникационный модуль 6.1 и ИНС 6.2. По сети на входы схемы контроля поступают сигналы с входов и выходов составных частей вычислительной системы. Схема контроля реализована на базе многослойной ИНС. Выделены слои, которые контролируют работоспособное состояние составных частей вычислительной системы. Каждый слой имеет входные, промежуточные и выходные нейроны, соединенные между собой. Информация поступает по сети передачи данных на входные нейроны i-го слоя ИНС с входов и выходов i-й составной части системы, подключенной к входам и выходам i-го коммутатора. Сигналы с выходных нейронов i-го слоя ИНС передаются по сети на входы i-го коммутатора. В работоспособном состоянии i-й составной части системы на выходах нейронов i-го слоя ИНС формируются сигналы «1». В неработоспособном состоянии i-й составной части системы на выходах нейронов i-го слоя ИНС формируются команды реконфигурации, которые включают сигналы «1» и «0».

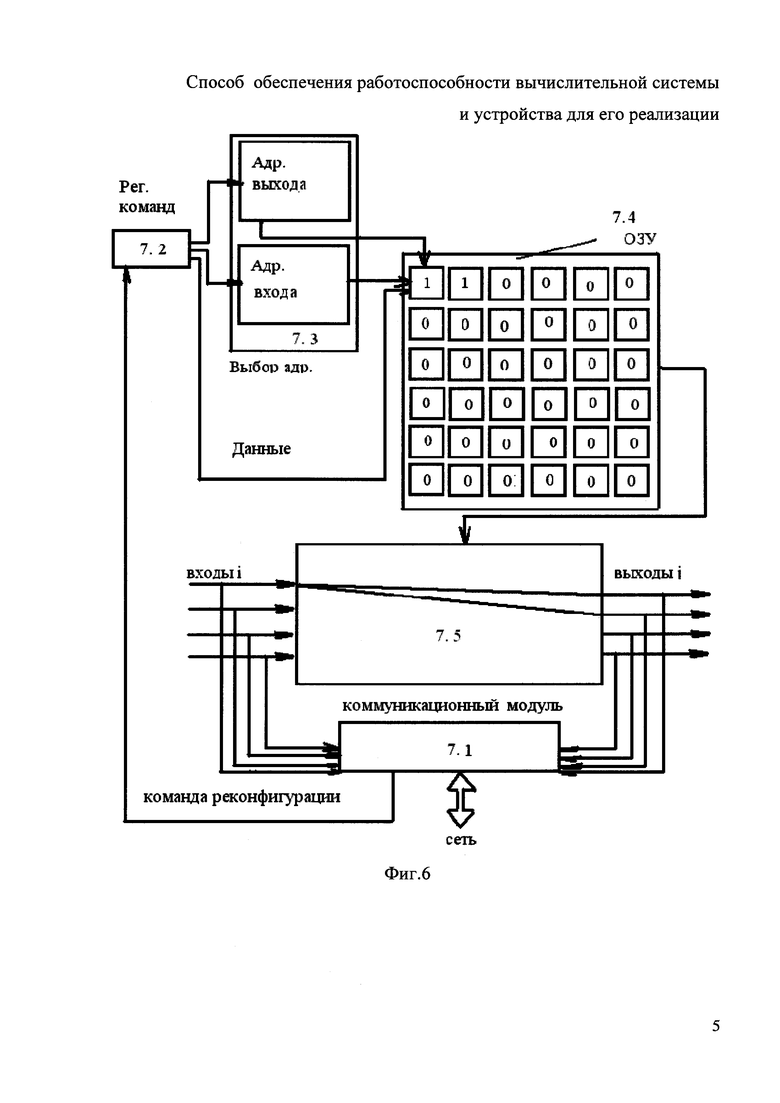

На фиг. 6 показана схема коммутатора. Коммутатор включает коммуникационный модуль 7.1, память ОЗУ 7.4 и коммутационное поле 7.5. На фиг. 6 показана память ОЗУ, в ячейках которой записана таблица коммутации входов и выходов. Информация из таблицы коммутации управляет взаимными соединениями входов и выходов коммутатора.

При отказе составной части вычислительной системы в коммуникационный модуль поступает команда реконфигурации, которая заносится в регистр команд 7.2, управляет схемой выбора адреса 7.3 и заносит новую информацию в ячейки ОЗУ 7.4.

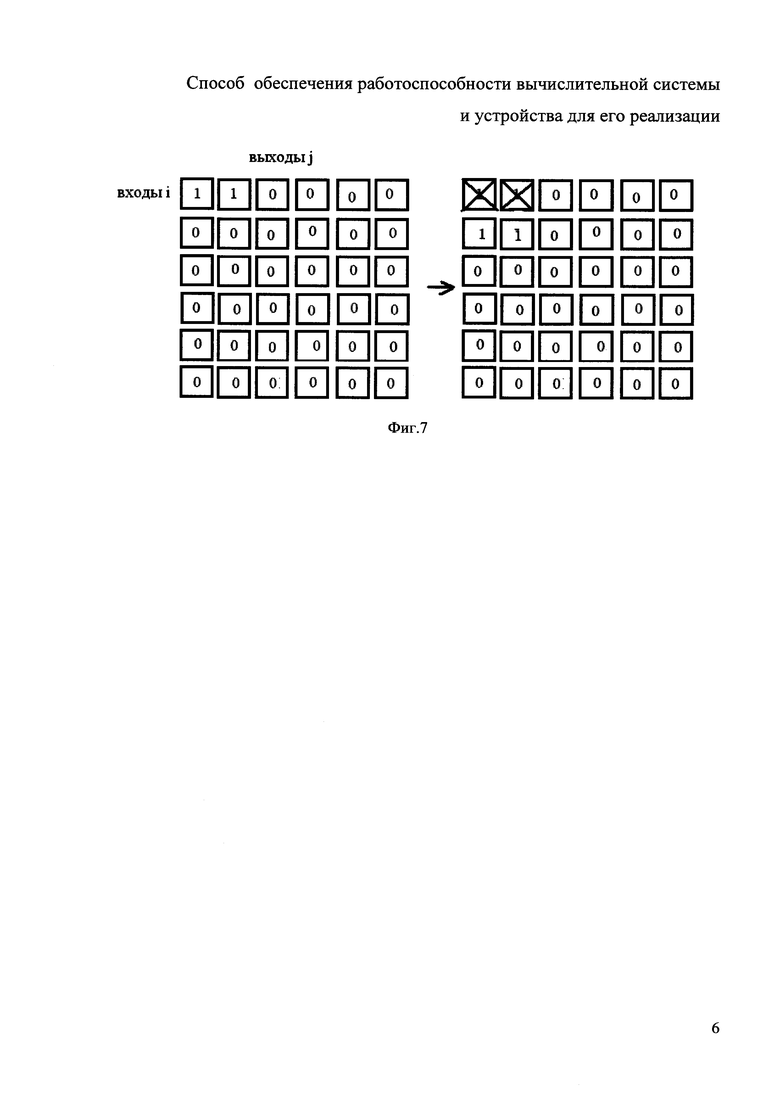

На фиг. 7 приведена таблица коммутации до и после реконфигурации. Информация из первой строки скопирована во вторую строку. В таблице перечеркнуты ячейки, соответствующие связям с неисправной составной частью вычислительной системы.

Заявленный способ обеспечения работоспособности состояния вычислительной системы состоит в следующем.

1. Проводят декомпозицию вычислительной системы и в ней выделяют составные части, выполняющие заданные функции, см. блоки 1.1-3.1, фиг. 1. Уровни входных и выходных сигналов составных частей характеризуют способность вычислительной системы выполнять заданные функции.

2. В вычислительную систему добавляют резервные составные части, см. фиг. 2, блоки 1.2-3.2.

3. В вычислительную систему добавляют основные и резервные коммутаторы 4.1-4.4, выполненные с возможностью передачи данных по сети и взаимного соединения составных частей, см. фиг. 3. Выделяют основные и резервные коммутаторы. Число коммутаторов, подсоединенных к каждой составной части, зависит от количества входных и выходных сигналов составных частей и количества входов и выходов коммутатора. Входные и выходные сигналы составных частей подключают к входам и выходам коммутаторов.

4. Коммутаторы соединяют друг с другом по сети. К сети передачи данных подключают внешнюю схему контроля, см. фиг. 4.

5. Внешняя схема контроля включает коммуникационный модуль для обмена информацией по сети и обученную ИНС, см. фиг. 5. ИНС выполнена с функциональной возможностью контроля значения входных сигналов. ИНС строится по слоям, где каждый слой выполняет контроль входных и выходных сигналов одной из составных частей вычислительной системы. ИНС принимает решение о работоспособном состоянии или отказе составных частей и вычислительной системы.

6. При отказе составной части вычислительной системы схема контроля формирует и передает по сети команду реконфигурации. Команда реконфигурации поступает на вход соответствующего коммутатора, подсоединенного к неисправной составной части. Коммутатор получает команду реконфигурации и меняет таблицу коммутации в ОЗУ. Вместо неисправной составной части коммутатор подсоединяет резервную составную часть.

7. Коммутаторы содержат входы и выходы, а также память, где хранится таблица взаимных связей входов и выходов. Элемент таблицы коммутации равен 0, если отсутствует связь между i-м входом и j-м выходом, и равен 1, если имеется связь между i-м входом и j-м выходом.

Преимуществами заявленного способа обеспечения работоспособности вычислительных систем являются:

1) исключение технологических перерывов в работе вычислительной системы для проведения периодических проверок работоспособности;

2) оперативное обнаружение отказов в процессе работы вычислительной системы;

3) автоматическое восстановление при отказах составных частей вычислительной системы.

Достигаемым техническим результатом является непрерывный контроль работоспособности, оперативное обнаружение отказов в процессе работы, автоматическое восстановление работоспособного состояния вычислительных систем. Экономическим результатом является сокращение эксплуатационных затрат, предотвращение ущерба от отказа вычислительной системы.

Технический результат заявленного изобретения обеспечивается за счет того, что сначала проводят декомпозицию вычислительной системы и в ней выделяют составные части, выполняющие заданные функции, причем уровни входных и выходных сигналов составных частей характеризуют способность вычислительной системы выполнять заданные функции, после чего в вычислительную систему добавляют резервные составные части, согласно изобретению в вычислительную систему добавляют коммутаторы, выполненные с возможностью взаимного соединения составных частей, а также приема и передачи данных по сети, затем входные и выходные сигналы вычислительной системы, а также входные и выходные сигналы ее основных и резервных составных частей подключают к входам и выходам коммутаторов, коммутаторы соединяют друг с другом посредством сети передачи данных, после чего к сети подсоединяют схему контроля, которая получает по сети и обрабатывает входные и выходные сигналы от коммутаторов и принимает решение о работоспособном состоянии или отказе составных частей вычислительной системы, после чего схема контроля формирует команду реконфигурации и передает ее по сети на вход соответствующего коммутатора, а затем коммутатор отключает входные и выходные сигналы, поступающие от неисправной составной части, и вместо них подключает соответствующие входные и выходные сигналы резервной составной части вычислительной системы.

Технический результат заявленного изобретения обеспечивается за счет того, что согласно изобретению схема контроля включает соединенные между собой коммуникационный модуль и обученную искусственную нейронную сеть, состоящую из слоев, причем число слоев определяется количеством составных частей вычислительной системы без учета их резервирования, где i-й слой имеет входные, промежуточные и выходные нейроны, связанные друг с другом, на входные нейроны i-го слоя по сети поступают входные и выходные сигналы i-й составной части, на выходных нейронах i-го слоя формируются и передаются по сети сигналы «1», если i-я составная часть работоспособна, или сигналы «0», если i-я составная часть неработоспособна.

Технический результат заявленного изобретения обеспечивается за счет того, что коммутатор имеет входы и выходы, являющиеся входами и выходами коммутационного поля, причем коммутатор содержит память, к которой подсоединены регистр команд и схема формирования адреса, согласно изобретению он включает дополнительный коммуникационный модуль, выполненный с функциональной возможностью приема и передачи данных по сети и подключенный к входам и выходам коммутатора, к регистру команд и к схеме формирования адреса ячеек оперативной памяти, где ячейка с номером строки I и номером столбца j, a[I, j] равна 0, если между i-м входом и j-м выходом нет связи, или равна 1, если такая связь установлена, причем при отказе составной части вычислительной системы в коммуникационный модуль по сети поступает команда реконфигурации, которая заносится в регистр команд, управляет схемой формирования адреса ячеек оперативной памяти и записывает в ячейки памяти информацию, которая задает новые связи между входами и выходами коммутатора.

Коммутатор может быть реализован на базе патента «Многофункциональный коммутатор» (Патент на изобретение 2139567, МПК G06F 15/163. Многофункциональный коммутатор [Текст] / B.C. Князьков, Л.А. Васин: заявитель и патентообладатель Пензенский технологический институт (ВТУЗ), заявлен 11.06.1997, опубликован 10.10.1999), см. фиг. 9, 10. Вместо постоянной памяти ПЗУ в схеме коммутатора использована оперативная память ОЗУ. В схему коммутатора добавлен коммуникационный модуль для обмена данными по сети.

Внешняя схема контроля может быть реализована на базе патента «Многослойная модульная вычислительная система» (Патент на изобретение 2398281, Российская Федерация, МПК 7 G06N 3/06. Многослойная модульная вычислительная система [Текст] / Соломенцев Ю.М., Шептунов С.А., Кабак И.С., Суханова Н.В.: заявитель и патентообладатель Федеральное государственное бюджетное учреждение науки Институт конструкторско-технологической информатики Российской академии наук (ИКТИ РАН). - №2008143737; заявл. 07.11.2008; опубл. 27.08.2010, Бюл. №24. - 8 с.: ил.). В схему контроля добавлен коммуникационный модуль для обмена данными по сети.

Схема контроля и коммутатор охарактеризованы в независимых пунктах формулы изобретения, как устройства для реализации заявленного способа обеспечения работоспособности вычислительной системы.

Заявленные в изобретении способ обеспечения работоспособного состояния вычислительной системы и схема контроля могут быть реализованы аппаратными или аппаратно-программными средствами на базе микропроцессоров, микроконтроллеров, нейрочипов.

Указанные в независимом пункте формулы признаки являются существенными и взаимосвязаны между собой с образованием устойчивой совокупности необходимых признаков, достаточной для получения требуемого технического результата.

Свойства, регламентированные в заявленном способе отдельными признаками, общеизвестны из уровня техники и не требуют дополнительных пояснений.

Следует отметить, что заявленная совокупность существенных признаков обеспечивает в соединении синергетический (сверхсуммарный результат).

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного способа следующей совокупности условий:

- заявленный способ имеет практическое применение, предназначен для обеспечения работоспособности вычислительных систем;

- для заявленного способа в том виде, как он охарактеризован в независимом пункте нижеизложенной формулы, подтверждена возможность его осуществления с помощью указанных в заявке или известных из уровня техники на дату приоритета средств и методов;

- при осуществлении способа достигается усматриваемый заявителем технический результат.

На основании изложенного, заявленный способ обеспечения работоспособности вычислительных систем соответствуют требованию условия патентоспособности «новизна» и «изобретательский уровень».

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ РАБОТОСПОСОБНОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И СХЕМА КОНТРОЛЯ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2669509C2 |

| СПОСОБ ПОВЫШЕНИЯ ОТКАЗОУСТОЙЧИВОСТИ СХЕМЫ И ОТКАЗОУСТОЙЧИВАЯ СХЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2631987C2 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ ИНФОРМАЦИОННО-ПРЕОБРАЗУЮЩИХ ЭЛЕМЕНТОВ БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНОГО СУДНА НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ | 2022 |

|

RU2802976C1 |

| СПОСОБ КОНТРОЛЯ ДЛЯ РЕКОНФИГУРАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2022 |

|

RU2801202C1 |

| СПОСОБ КОНТРОЛЯ ДЛЯ ФУНКЦИОНАЛЬНОЙ РЕКОНФИГУРАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2022 |

|

RU2792920C1 |

| УСТРОЙСТВО ТЕХНИЧЕСКОГО ДИАГНОСТИРОВАНИЯ КОМПЛЕКСА БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНЫХ СУДОВ НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ | 2024 |

|

RU2831917C1 |

| АДАПТИВНЫЙ СПОСОБ ФУНКЦИОНАЛЬНОЙ РЕКОНФИГУРАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2024 |

|

RU2839616C1 |

| ОТКАЗОУСТОЙЧИВАЯ НЕЙРОННАЯ СЕТЬ, СПОСОБ ОБНАРУЖЕНИЯ ОТКАЗОВ НЕЙРОННОЙ СЕТИ, СПОСОБ ОБЕСПЕЧЕНИЯ ОТКАЗОУСТОЙЧИВОСТИ НЕЙРОННОЙ СЕТИ | 2018 |

|

RU2760636C2 |

| СПОСОБ ИСПЫТАНИЙ ЭЛЕКТРОННОЙ СХЕМЫ НА ОТКАЗОУСТОЙЧИВОСТЬ И СТЕНД ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2664493C1 |

Изобретение относится к области вычислительной техники. Техническим результатом является обеспечение бесперебойной работы вычислительной системы. Способ обеспечивает декомпозицию вычислительной системы схемы путем выделения составных частей, которые реализуют заданные функции. В вычислительную систему добавляют резервные составные части и коммутаторы, которые обеспечивают взаимные связи составных частей между собой. Коммутаторы соединяют друг с другом посредством сети передачи данных. Коммутатор содержит оперативную память, где записана таблица коммутации входов и выходов. К сети коммутаторов подсоединяют внешнюю схему контроля, которая обрабатывает входные и выходные сигналы от составных частей и принимает решение о работоспособном состоянии или отказе составных частей и вычислительной системы. Схема контроля включает обученную искусственную нейронную сеть, которая состоит из слоев. Число слоев нейронной сети определяется количеством составных частей вычислительной системы без учета их резервирования. При отказах составных частей и вычислительной системы схема контроля формирует команду реконфигурации, по которой коммутатор формирует новую таблицу коммутации и заносит ее в оперативную память. Коммутатор отключает неисправную и подключает резервную составную часть вычислительной системы. Отключение неисправных и подключение резервных составных частей выполняется без переключения контактов. 3 н.п. ф-лы, 7 ил.

1. Способ обеспечения работоспособного состояния вычислительной системы, когда сначала проводят декомпозицию вычислительной системы и в ней выделяют составные части, выполняющие заданные функции, причем уровни входных и выходных сигналов составных частей характеризуют способность вычислительной системы выполнять заданные функции, после чего в вычислительную систему добавляют резервные составные части, отличающийся тем, что в вычислительную систему добавляют коммутаторы, выполненные с возможностью взаимного соединения составных частей, а также приема и передачи данных по сети, затем входные и выходные сигналы вычислительной системы, а также входные и выходные сигналы ее основных и резервных составных частей подключают к входам и выходам коммутаторов, коммутаторы соединяют друг с другом посредством сети передачи данных, после чего к сети подсоединяют схему контроля, которая получает по сети и обрабатывает входные и выходные сигналы от коммутаторов и принимает решение о работоспособном состоянии или отказе составных частей вычислительной системы, после чего схема контроля формирует команду реконфигурации и передает ее по сети на вход соответствующего коммутатора, а затем коммутатор отключает входные и выходные сигналы, поступающие от неисправной составной части, и вместо них подключает соответствующие входные и выходные сигналы резервной составной части вычислительной системы.

2. Схема контроля для реализации способа по п. 1, отличающаяся тем, что она включает соединенные между собой коммуникационный модуль и обученную искусственную нейронную сеть, состоящую из слоев, причем число слоев определяется количеством составных частей вычислительной системы без учета их резервирования, где i-й слой имеет входные, промежуточные и выходные нейроны, связанные друг с другом, на входные нейроны i-го слоя по сети поступают входные и выходные сигналы i-й составной части, на выходных нейронах i-го слоя формируются и передаются по сети сигналы «1», если i-я составная часть работоспособна, или сигналы «0», если i-я составная часть неработоспособна.

3. Коммутатор для реализации способа по п. 1, имеющий входы и выходы, являющиеся входами и выходами коммутационного поля, причем коммутатор содержит память, к которой подсоединены регистр команд и схема формирования адреса, отличающийся тем, что он включает дополнительный коммуникационный модуль, выполненный с функциональной возможностью приема и передачи данных по сети и подключенный к входам и выходам коммутатора, к регистру команд и к схеме формирования адреса ячеек оперативной памяти, где ячейка с номером строки I и номером столбца j, a [I, j] равна 0, если между i-м входом и j-м выходом нет связи, или равна 1, если такая связь установлена, причем при отказе составной части вычислительной системы в коммуникационный модуль по сети поступает команда реконфигурации, которая заносится в регистр команд, управляет схемой формирования адреса ячеек оперативной памяти и записывает в ячейки памяти информацию, которая задает новые связи между входами и выходами коммутатора.

| МНОГОСЛОЙНАЯ МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2008 |

|

RU2398281C2 |

| Устройство для управления стрелкой в системе электрической централизации | 1939 |

|

SU66831A1 |

| ПЫЛЕСОС | 2009 |

|

RU2442525C1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

Авторы

Даты

2018-08-17—Публикация

2016-12-21—Подача