Изобретение относится к-вычислительной технике и может быть использовано в арифметических устройствах для суммирования чисел, представленных в параллельном двоичном коде.

Целью изобретения является сокращение аппаратурных затрат и повыпе- ние быстродействия устройства.

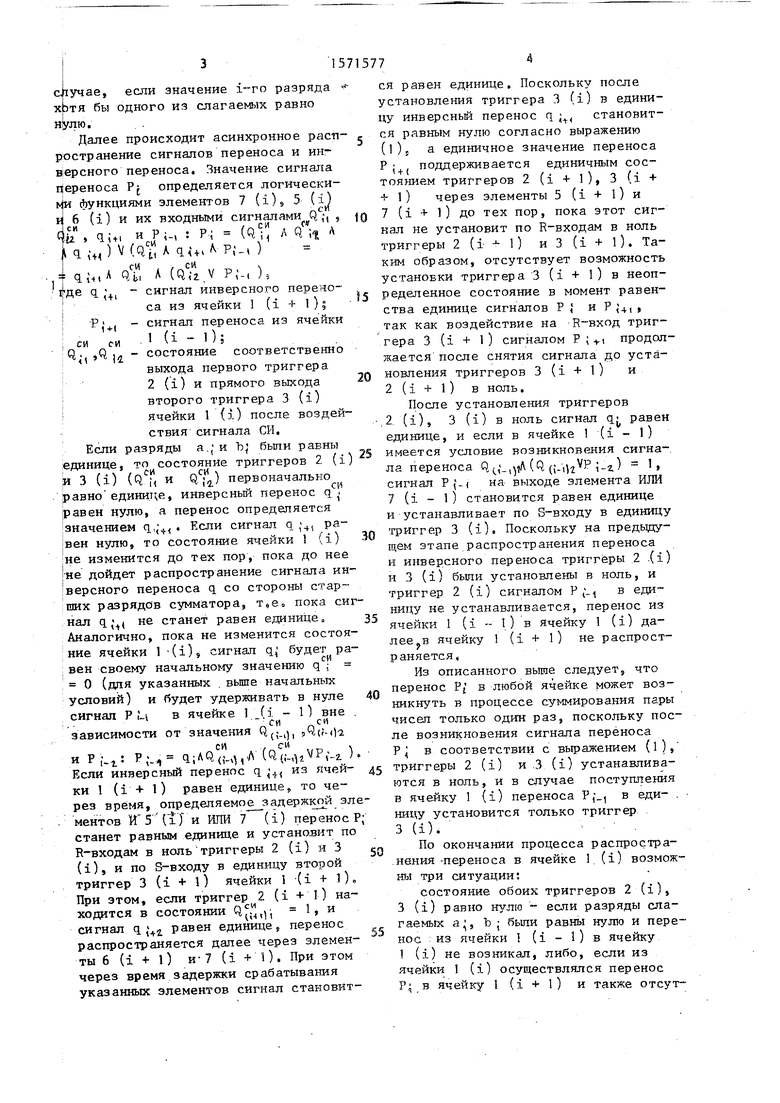

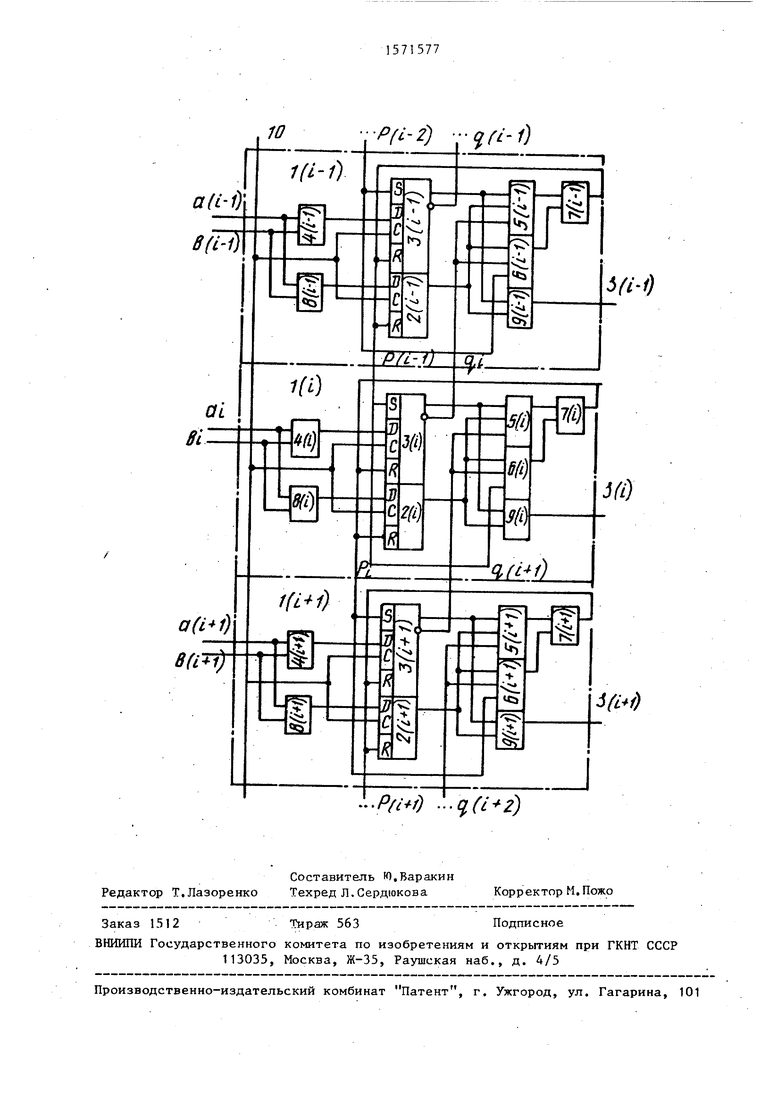

На чертеже представлена функциональная схема трех соседних ячеек параллельного двоичного сумматора.

Ячейки 1 (i - 1) - 1 (i + 1) содержат первые 2(1 - 1) - 2(1 + 1) и вторые 3 (1 - I) - 3 (1 + 1) триггеры, первые элементы И 4 (i - 1) -4 (i + l), вторые 5(i - l)

-5 (i + l) и третьи 6 (i - 1) -6 (i + l), а также первые 7 (i-1)- -7 (i + 1), вторые 8 (i - 1) - 8 (i+ +l) и третьи 9 (i - 1) - 9 (i + 1 ) элементы ИЛИ. Сумматор содержит также шину 10 синхронизации.

Работу сумматора опишем на примере работы ячеек 1 (а - l), I (i) и 1 (i + 1), изображенных на чертеже. На первьй и второй информационные входы каждой ячейки подаются значения соответствующих разрядов слагаемых А и В, например разряды аЈ и Ъ подаются на первый и второй входы элемента И 4 (i), являющиеся первым и вторым информационными входами ячейки 1 (i), а также на соединенные с ними первый и второй входы второго элемента ИЛИ 8 (i). По синхроимпульсу СИ, поступающему с шины 10 синхронизации одновременно на С-входы всех триггеров сумматора, триггеры -- устанавливаются в состояние,соответствующее состоянию их D-входов,

Инверсный выход второго триггера 3%(i), являющийся выходом инверсного переноса q, равен в начальный момент после сигнала СИ единице в том

СП

ч

СП

1 J

случае, если значение 1-го разряда хэтя бы одного из слагаемых равно нулю.

Далее происходит асинхронное растт- ространение сигналов переноса и инверсного переноса. Значение сигнала Переноса Р опредатяется логически- Ми функциями элементов 7 (i)9 5 (i) и 6 (i) и их входными сигналами Q,-, , 4b q; + , и Р;., : Р; (Q; Л Q jt Л А 1,Ч) VteCtl Л qU Р, - )

. q{4i QCL. (Q°;z V Р,1-, ), ij-де q +1 - сигнал инверсного пере-юса из ячейки 1 (i + l)| - сигнал переноса из ячейки

1(i - О;

соответственно выхода первого триггера

2(i) и прямого выхода второго триггера 3 (i) ячейки 1 О) после воздействия сигнала СИ.

Если разряды а и Ъ} были равны единице то состояние триггеров 2 (i)

си 1«Ч

1+1 си 11

Q , ,Q |Л - состояние

,си

и 3 (i) (Q ;, и Q ;г) первоначально равно единице, инверсный перенос q равен нулю, а перенос определяется значением q ;+ . Если сигнал q ,-4, равен нулю, то состояние ячейки 1 (1) не изменится до тех пор, пока до нее не дойдет распространение сигнала инверсного переноса q со стороны сггар ших разрядов сумматора, т,е пока сигнал q( не станет равен единице, Аналогично, пока не изменится состояние ячейки 1 (1), сигнал q,1 будет равен своему начальному значению q , 0 (для указанных выше начальных условий) и будет удерживать в нуле

сигнал Р в ячейке 1 (i - 1) вне

си си зависимости от значения Ц,{,( ,

СИ., СИ.

и Р q;AQ(}.,A (, ) Если инверсный перенос q , + из ячей- ки 1 (i + l) равен единице, то через время, определяемое ад ержкой элементов Й 5 li) и ИЛИ 7 (1) перенос Р станет равным единице и установит по R-входам в ноль триггеры 2 (i) и 3 (i), и по S-входу в единицу втотюй триггер 3 (i + l) ячейки 1 (i + l), При этом, если триггер 2 (i + l) находится в состоянии Я ,i, 1, и сигнал q {+1 равен единице, перенос распространяется далее через элементы 6 (i + О и-7 (i + О. При этом через время задержки срабатывания указанных элементов сигнал становится равен единице. Поскольку после установления триггера 3 (i) в единицу инверсный перенос q становится равным нулю согласно выражению (1)s а единичное значение переноса Р; поддерживается единичным состоянием триггеров 2 (i + l), 3 (i + + 1) через элементы 5 (i + l) и 7 (i i- 1) до тех пор, пока этот сигнал не установит по R-входам в ноль триггеры 2 (i 1) и 3 (i + 1), Таким образом, отсутствует возможность установки триггера 3 (i + l) в неопределенное состояние в момент равенства единице сигналов Р J и Р ;41, так как воздействие на R-вход триггера 3 (1 + 1) сигналом Р ;+1 продолжается после снятия сигнала до установления триггеров 3 (i + l) и 2(1+1) в ноль.

После установления триггеров

2(i), 3 (i) в ноль сигнал q равен единице, и если в ячейке 1 (i - l) имеется условие возникновения сигнала переноса Q (,«,уЛ (Q (;,jtVp ) 1, сигнал Р(-( на выходе элемента ИЛИ 7 (i - 1) становится равен единице

и устанавливает по S-входу в единицу триггер 3 (1), Поскольку на предыдущем этапе распространения переноса и инверсного переноса триггеры 2 (1) и 3 (1) были установлены в ноль, и триггер 2 (i) сигналом в единицу не устанавливается, перенос из ячейки 1 (i -- I ) в ячейку 1 (i) да- лее.в ячейку 1 (1 + 1) не распространяется,

Из описанного выше следует, что перенос Рг1 в любой ячейке может возникнуть в процессе суммирования пары чисел только один раз, поскольку после возникновения сигнала переноса Р в соответствии с выражением (О, триггеры 2 (i) и 3 (i) устанавливаются в ноль, и в случае поступления в ячейку I (i) переноса ,, в единицу установится только триггер

3(1).

По окончании процесса распространения -переноса в ячейке 1 (1) возможны три ситуации:

состояние обоих триггеров 2 (i), 3 (i) равно нулю - если разряды слагаемых а, Ъ ; были равны нулю и перенос из ячейки I (i - 1) в ячейку 1 (i) не возникал, либо, если из ячейки 1 (i) осуществлялся перенос Г; в ячейку 1 (i + 1) и также отсутствовал после этого перенос Р , ,либо перенос Р,, привел к возникновению переноса Р,. и, как было доказано выше, вторично возникнуть не мог;

состояние триггера 2 (i) равно единице, а триггера З1(1) - нулю,если единице был равен только один из разрядов а; и Ъ; и перенос Р4-, не возникал;

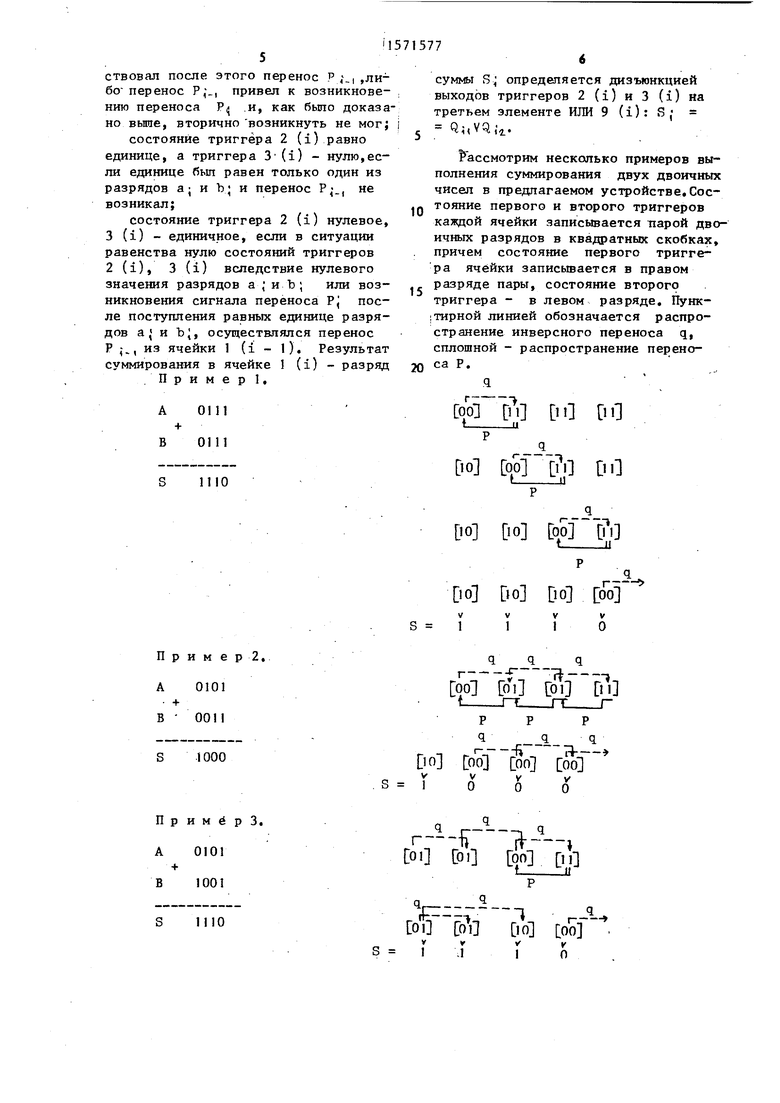

состояние триггера 2 (1) нулевое, 3 (i) - единичное, если в ситуации равенства нулю состояний триггеров 2 (i), 3 (i) вследствие нулевого значения разрядов а ; и Ъ ; или возникновения сигнала переноса PJ после поступления равных единице разрядов а и bj, осуществлялся перенос Р ;., из ячейки 1 (1 - 1). Результат суммирования в ячейке 1 (i) - разряд Пример 1.

А 0111

+ В 0111

1110

0

5

0

суммы S; определяется дизъюнкцией выходов триггеров 2 (i) и 3 (i) на третьем элементе ИЛИ 9 (i): S ,

,v

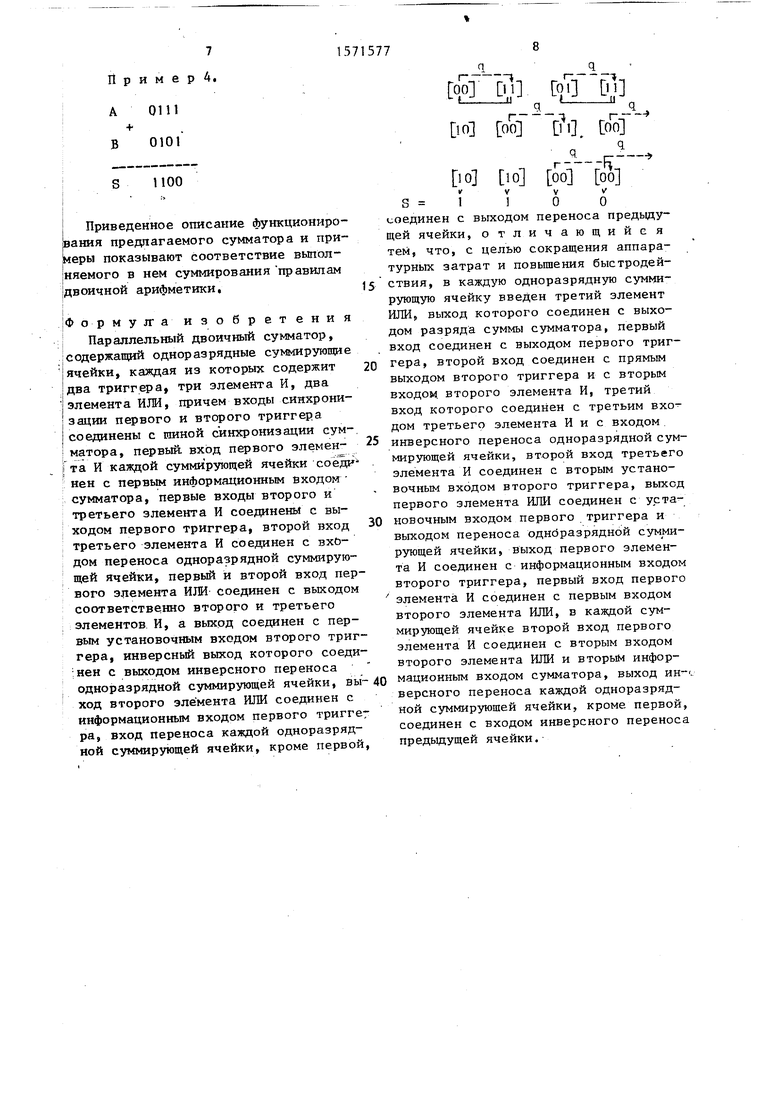

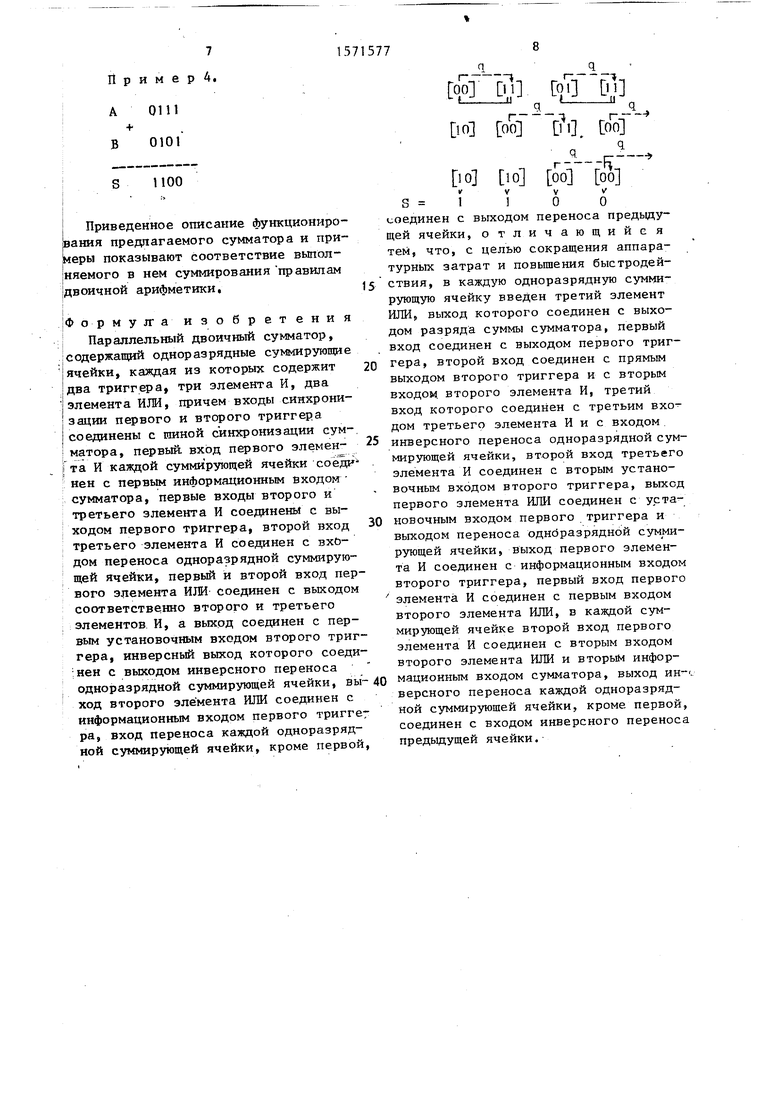

Рассмотрим несколько примеров выполнения суммирования двух двоичных чисел в предлагаемом устройстве.Состояние первого и второго триггеров каждой ячейки записывается ттарой двоичных разрядов в квадратных скобках, причем состояние первого триггера ячейки записывается в правом разряде пары, состояние второго триггера - в левом разряде. Пунк- тарной линией обозначается распространение инверсного переноса q, сплошной - распространение переноса Р.

0.

oof

0

П DO

q г--;т

оо Л п р

q i о оо п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Конвейерный сумматор | 1987 |

|

SU1427359A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для суммирования одноразрядных приращений | 1985 |

|

SU1251072A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для выделения экстремальных чисел | 1983 |

|

SU1109736A2 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах для суммирования чисел, представленных в параллельном двоичном коде. Целью изобретения является сокращение аппаратурных затрат и повышение быстродействия сумматора. Указанная цель достигается тем, что каждая ячейка двоичного сумматора, содержащая два триггера, три элемента И, два элемента ИЛИ, содержит третий элемент ИЛИ с соответствующими связями. 1 ил.

р и м е р 2,

0101

+ ООП

1000

р и м ё р 3.

0101

+ 1001

1110

q q q if7t-}

00 01 01 П

1

р р р

q q g

г -i t- -i-6-, «3- ю oo on oo

Vуу

о

о

о

q Г----1 q

J--1

01 01 00 П

01 01 10 oo

,1

V

0

7 А.

j Приведенное описание функциониро- вания предлагаемого сумматора и при- |меры показывают соответствие выпол- (няемого в нем суммирования правилам двоичной арифметики.

Формула изобретения

Параллельный двоичный сумматор, содержащий одноразрядные суммирующие ячейки, каждая из которых содержит два триггера, три элемента И, два элемента ИЛИ, причем входы синхронизации первого и второго триггера соединены с шиной синхронизации сумматора, первый вход первого элемента И каждой суммирующей ячейки соёди 1 нен с первым информационным входом сумматора, первые входы второго и третьего элемента И соединены с выходом первого триггера, второй вход третьего элемента И соединен с входом переноса одноразрядной суммирующей ячейки, первый и второй вход первого элемента ИЛИ соединен с выходом соответственно второго и третьего элементов И, а выход соединен с первым установочным входом второго триггера, инверсный выход которого соединен с выходом инверсного переноса одноразрядной суммирующей ячейки, вы- ход второго элемента ИЛИ соединен с информационным входом первого триггег ра, вход переноса каждой одноразрядной суммирующей ячейки, кроме первой,

1571577

D}

oi

00 1.

г

5

0

5

0

0

ю ю оо оо

V

о

V

о

j соединен с выходом переноса предыдущей ячейки, отличающийся тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия, в каждую одноразрядную суммирующую ячейку введен третий элемент ИЛИ, выход которого соединен с выходом разряда суммы сумматора, первый вход соединен с выходом первого триггера, второй вход соединен с прямым выходом второго триггера и с вторым входом второго элемента И, третий вход которого соединен с третьим входом третьего элемента И и с входом инверсного переноса одноразрядной суммирующей ячейки, второй вход третьего элемента И соединен с вторым установочным входом второго триггера, выход первого элемента ИЛИ соединен с установочным входом первого триггера и выходом переноса одноразрядной суммирующей ячейки, выход первого элемента И соединен с информационным входом второго триггера, первый вход первого элемента И соединен с первым входом второго элемента ИЛИ, в каждой суммирующей ячейке второй вход первого элемента И соединен с вторым входом второго элемента ИЛИ и вторым информационным входом сумматора, выход ин- версного переноса каждой одноразрядной суммирующей ячейки, кроме первой, соединен с входом инверсного переноса предыдущей ячейки.

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Самофалов К.Г., Корнейчук В4И,, Тарасенко В.П | |||

| Цифровые электронные вычислительные машины | |||

| Киев: Вища школа, 1983, с | |||

| Индукционная катушка | 1920 |

|

SU187A1 |

Авторы

Даты

1990-06-15—Публикация

1988-08-05—Подача