Изобретение относится к вычислительной технике и может быть использовано при построении устройств для контроля по модулю три.

Недостатком устройства является отсутствие возможности получения контрольных кодов частей сворачиваемого числа по мере его поступления.

Целью изобретения является получение контрольных кодов частей сворачиваемого числа по мере его поступления.

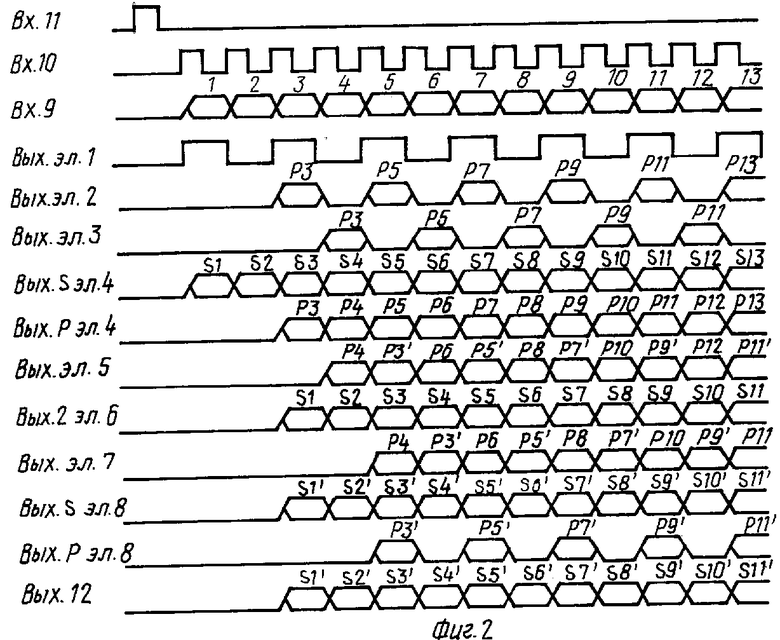

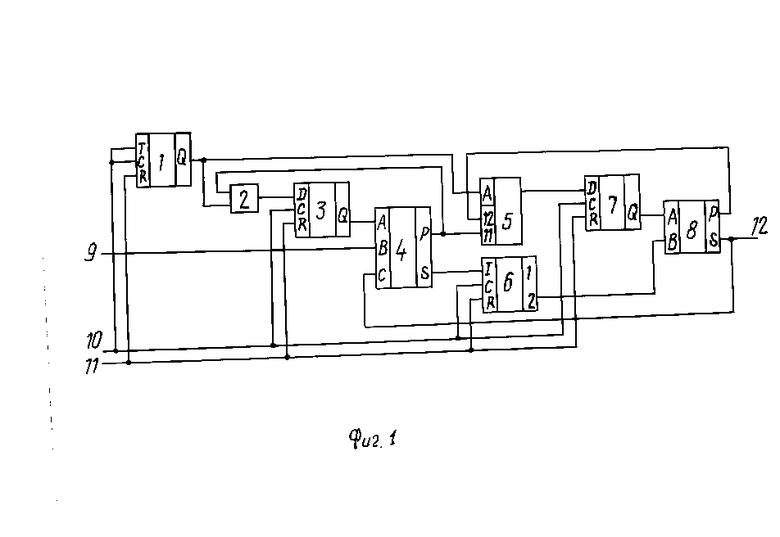

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы, иллюстрирующие работу устройства.

Устройство (фиг. 1) содержит управляющий триггер 1, элемент И 2, первый триггер 3, сумматор 4, мультиплексор 5, двухразрядный сдвиговый регистр 6, второй триггер 7, полусумматор 8, информационный вход 9 устройства, тактовый вход 10 устройства, вход 11 начальной установки устройства и выход 12 устройства.

Устройство работает следующим образом.

На вход 11 начальной установки устройства поступает импульс, определяющий начало работы. Этот импульс сбрасывает в нуль управляющий 1, первый 3 и второй 7 триггеры и двухразрядный сдвиговый регистр 6.

На тактовый вход 10 устройства поступают синхроимпульсы СИ типа "меандр", тактирующие работу устройства. Они подаются на информационный вход управляющего триггера 1, который является Т-триггером и формирует на прямом выходе значения управляющих сигналов. На вход 9 устройства с частотой следования синхроимпульсов поступают в последовательном коде разряды n-разрядного двоичного числа, начиная с первого - младшего (фиг. 2) (n - четное число).

Числа, указанные на временных диаграммах, обозначают номера разрядов двоичного числа. Парами Si и Pi, где i = 1-n, обозначены соответственно сумма в i-ом разряде и перенос из i-го разряда, получаемые на сумматоре 4. Парами Si' и Pi' обозначены соответственно сумма в i-ом разряде и перенос из i-го разряда, получаемые на полусумматоре 8.

В первом такте работы первый разряд числа поступает на второй вход сумматора 4. Поскольку значения на прямых выходах первого 3 и второго 7 триггеров и на втором выходе двухразрядного сдвигового регистра 6 равны нулю, то значение первого разряда числа в виде суммы S1 с выхода сумматора 4 поступает на информационный вход регистра 6.

Во втором такте по аналогичным соображениям поступивший на второй вход сумматора 4 второй разряд числа в виде суммы S2 с выхода сумматора 4 поступает на информационный вход регистра 6. Синхроимпульсы, поступившие на синхровход регистра 6, в каждом такте работы продвигают записанную в нем информацию на один разряд в сторону старших разрядов.

В третьем такте работы с выхода второго разряда регистра 6 значение суммы S1 поступает на второй вход полусумматора 8. Так как значение на прямом выходе второго триггера 7 равно нулю (фиг. 2), сумма S1 уже в виде суммы S11 с выхода суммы полусумматора 8 поступает на выход 12 устройства и на вход переноса сумматора 4, где суммируется с поступившим на второй вход значением третьего разряда числа. На выходах суммы и переноса сумматора 4 появляются значения суммы S3 и переноса Р3.

Управляющие сигналы поступают на вход элемента И2 и на адресный вход мультиплексора 5, разрешая запись переноса Р с выхода переноса сумматора 4 в первый триггер 3 в каждом нечетном такте и во второй триггер 7 - в каждом четном такте (первый 3 и второй 7 триггеры являются триггерами D-типа). Кроме того, в каждом нечетном такте во второй триггер 7 разрешена запись переноса Р1 с выхода переноса полусумматора 8.

Таким образом, все переносы, возникающие на сумматоре 4 в нечетных тактах, будут запоминаться в первом триггере 3 и в следующем четном такте будут учитываться на сумматоре 4, а все переносы, возникающие на сумматоре 4 в четных тактах, будут запоминаться во втором триггере 7 и в следующем нечетном такте будут учитываться на полусумматоре 8. Переносы, возникающие в нечетном такте на полусумматоре 8, запоминаются также во втором триггере 7 и в следующем четном такте будут учитываться на полусумматоре 8 (в четных тактах на полусумматоре 8 переносы не возникают).

Начиная с третьего такта работы, на выход 12 устройства поступает первый (младший) разряд контрольного кода по модулю три результата свертки первого и второго разрядов сворачиваемого числа, а в четвертом такте работы на выход 12 устройства поступает второй (старший) разряд контрольного кода. В процессе функционирования устройства в (i + 1)-ом и (i + 2)-ом тактах работы (i = 1-n, n - четное число) на выход 12 устройства поступают соответственно первый и второй разряды контрольного кода по модулю три результата свертки разрядов числа с 1-го по n-й. (56) Ф. Селлерс. Методы обнаружения ошибок в работе ЭЦВМ. М. : Мир, 1972, с. 94, фиг. 4.28.

Ф. Селлерс. Методы обнаружения ошибок в работе ЭЦВМ, М. : Мир, 1972, с. 94, фиг. 4.29.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для возведения в квадрат | 1987 |

|

SU1451686A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Пирамидальная свертка по модулю три | 1989 |

|

SU1695308A2 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для контроля по модулю три. Целью изобретения является получение контрольных кодов частей сворачиваемого числа по мере его поступления в последовательном коде. Устройство содержит управляющий триггер 1, управляющий работой элемента И 2 и мультиплексора 5, элемент И 2, пропускающий в нечетном такте на информационный вход первого триггера 3 значение переноса из сумматора 4, первый триггер 3, служащий для хранения переносов из нечетных разрядов результата сумматора 4 и задержания их на один такт, сумматор 4, суммирующий очередной разряд сворачиваемого числа с содержанием первого триггера 3 и разрядом суммы, вычисляемой на полусумматоре 8, мультиплексор 5, коммутирующий на информационный вход второго триггера 7 в четном такте - значение переноса из сумматора 4, а в нечетном такте - значение переноса из полусумматора 8, двухразрядный сдвиговый регистр 6, служащий для хранения разрядов суммы, вычисляемой на сумматоре 4, и задержки их на два такта, второй триггер 7, запоминающий значения на выходе мультиплексора 5 и задерживающий их на один такт, полусумматор 8, суммирующий задержанный на два такта разряд суммы из сумматора 4 и содержимое второго триггера 7 и выдающий на выходе суммы в (i + 1)-м и (i + 2)-м тактах соответственно первый и второй разряды контрольного кода по модулю три, поступивших на вход устройства i разрядов сворачиваемого числа (двоичного), i = 1, n, n - четное число - разрядность двоичного числа. 2 ил.

УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ, содержащее первый триггер, сумматор и двухразрядный сдвиговый регистр, причем прямой выход первого триггера соединен с входом первого слагаемого сумматора, выход суммы которого соединен с информационным входом двухразрядного сдвигового регистра, синхровход и вход сброса которого соединены соответственно с синхровходом и входом сброса первого триггера и тактовым входом и входом начальной установки устройства, отличающееся тем, что, с целью получения контрольного кода частей сворачиваемого числа по мере его поступления, в него введены управляющий триггер, элемент И, мультиплексор, второй триггер и полусумматор, причем прямой выход управляющего триггера соединен с первым входом элемента И и адресным входом мультиплексора, выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с входом первого слагаемого полусумматора, выход переноса которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом переноса сумматора и вторым входом элемента И, выход которого соединен с информационным входом первого триггера, выход второго разряда двухразрядного сдвигового регистра соединен с входом второго слагаемого полусумматора, выход суммы которого соединен с выходом устройства и входом переноса сумматора, вход второго слагаемого которого соединен с информационным входом устройства, тактовый вход которого соединен с информационным входом и синхровходом управляющего триггера и синхровходом второго триггера, вход сброса которого соединен с входом сброса управляющего триггера и входом начальной установки устройства.

Авторы

Даты

1994-04-15—Публикация

1991-03-25—Подача