Изобретение относится к телемеханике и вычислительной технике и может быть использовано в адаптивных системах передачи и обработки дискретнсзй информации для коррекции сшибок при многократном дублировании сообщений.

Известно устройство для гшаптивного мажоритарного декодирования, содержащее регистры сдвига и логические элементы и позволяющие подвергать мажоритарной обработке три,пять и более повторений сообщения без потери промежуточных результатов С 1

Недостатком этого устройства является ограниченность функциональных возможностей, проявляющаяся в том, что анализируются не все возможные сочетания повторений сообщения.

Наиболее близкое к предлагаемому по технической сущности устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов содержит последовательно включенные ключ и счетчик, параллельные выходы которого через соответствующие элементы И и регистр сдвига подключены к входам решаквдего блока и ксвоим установочным входам, при этом выходы элементов И подключены к дополнительным входам решающего

блока, выход которого соединен с управляющим входом ключа, сбросовый вход которого объединен с вторыми входами элементов И Г 2.

Недостатком известного устройстве является невысокая достоверность, проявляющаяся в том, что подвергая мажоритарной обработке первые три и в целом пять повторений сообщения,

10 устройство не анализирует третье, четвертое и пятое повторения и не осуществляет их мажоритарной обработки. Если интенсивному воздействий помех подвергаются первые три повто15рения, то с большой вероятностью можно утверждать, что известным устройством будут исправлены не все ошибки после приема пяти повторений.

Цель изобретения - повышение до20стоверности устройства.

Поставленная цель достигается тем, что в устройство для приема и мажоритарного декодирования инфор ации, содержащее ключ, вход которого

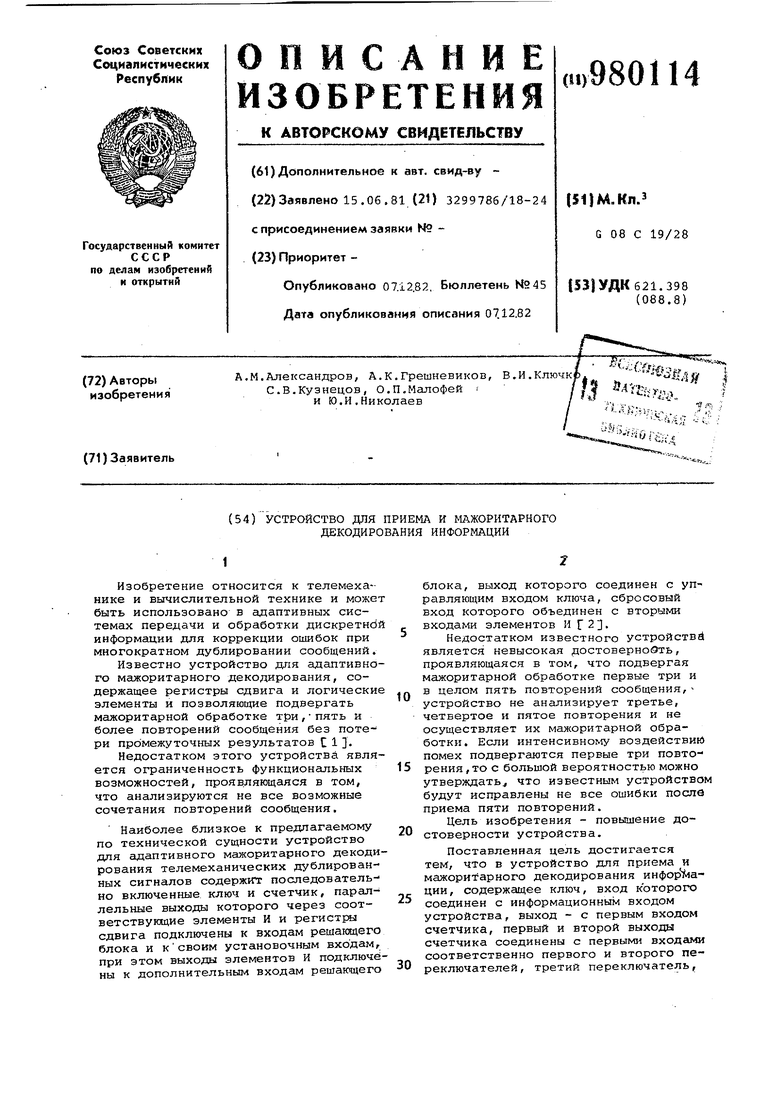

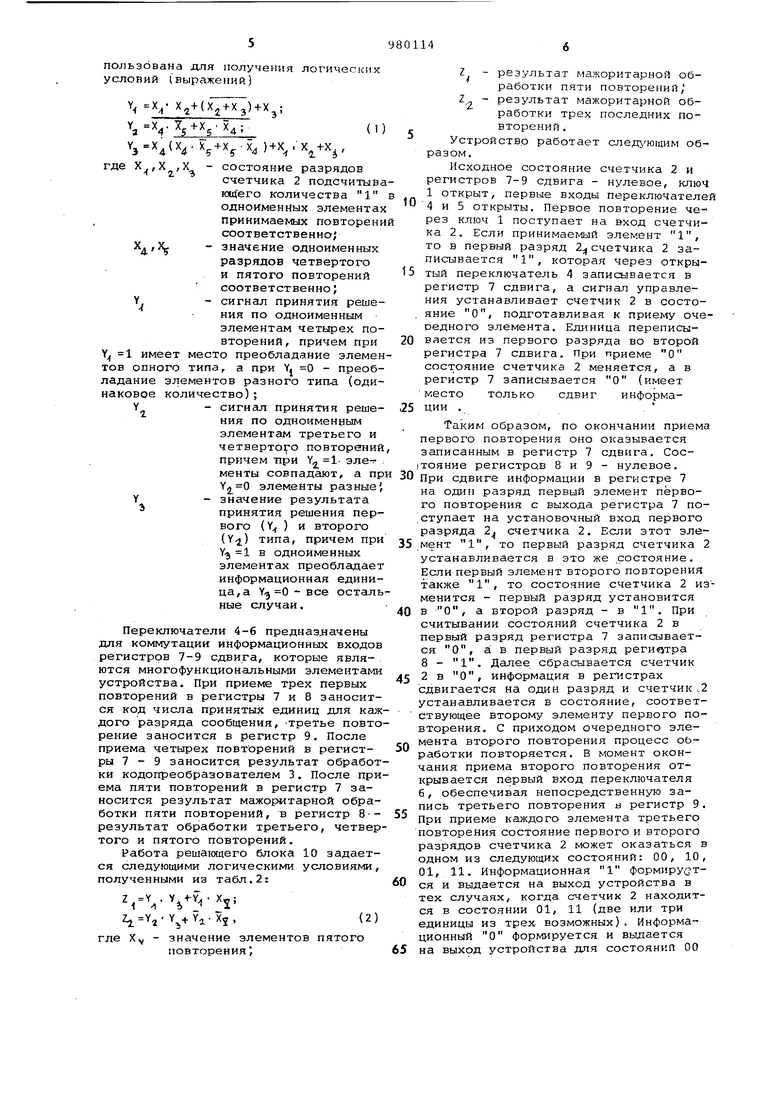

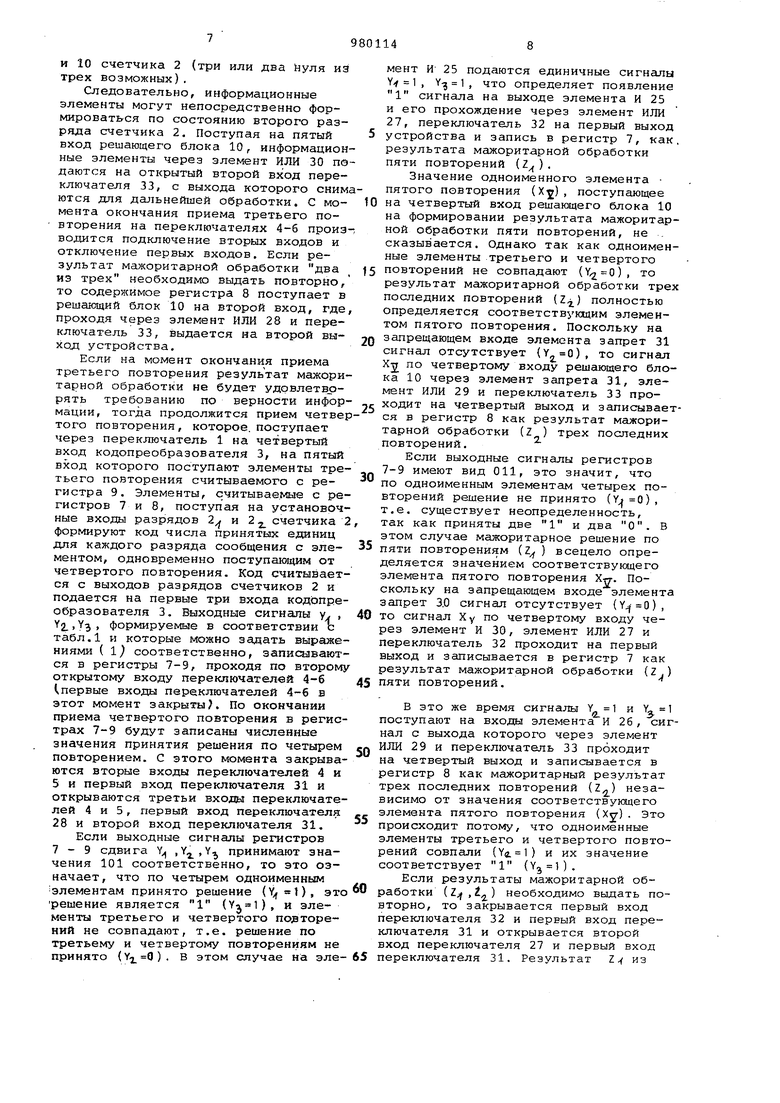

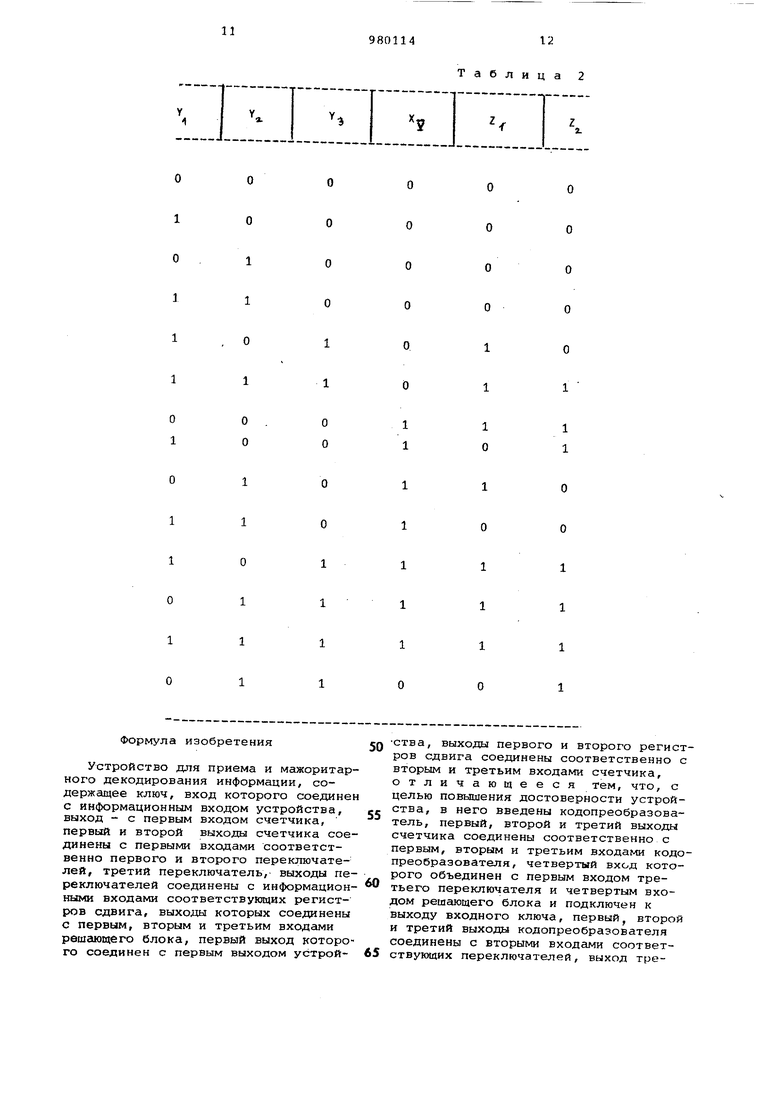

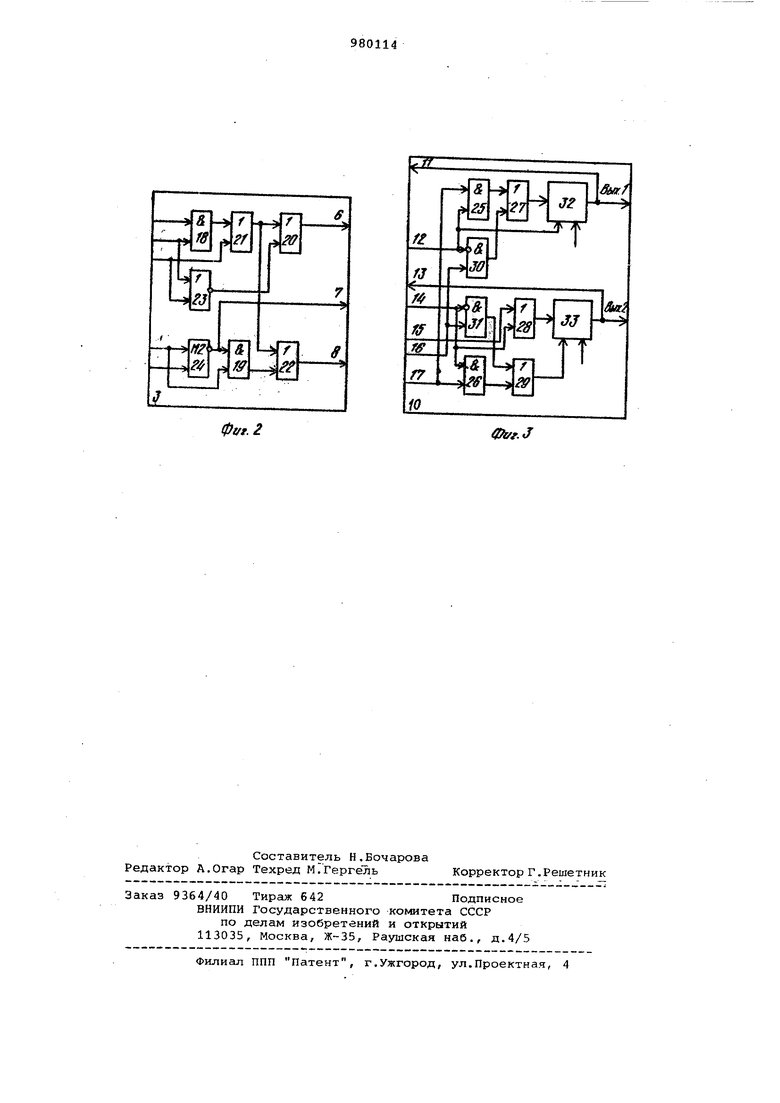

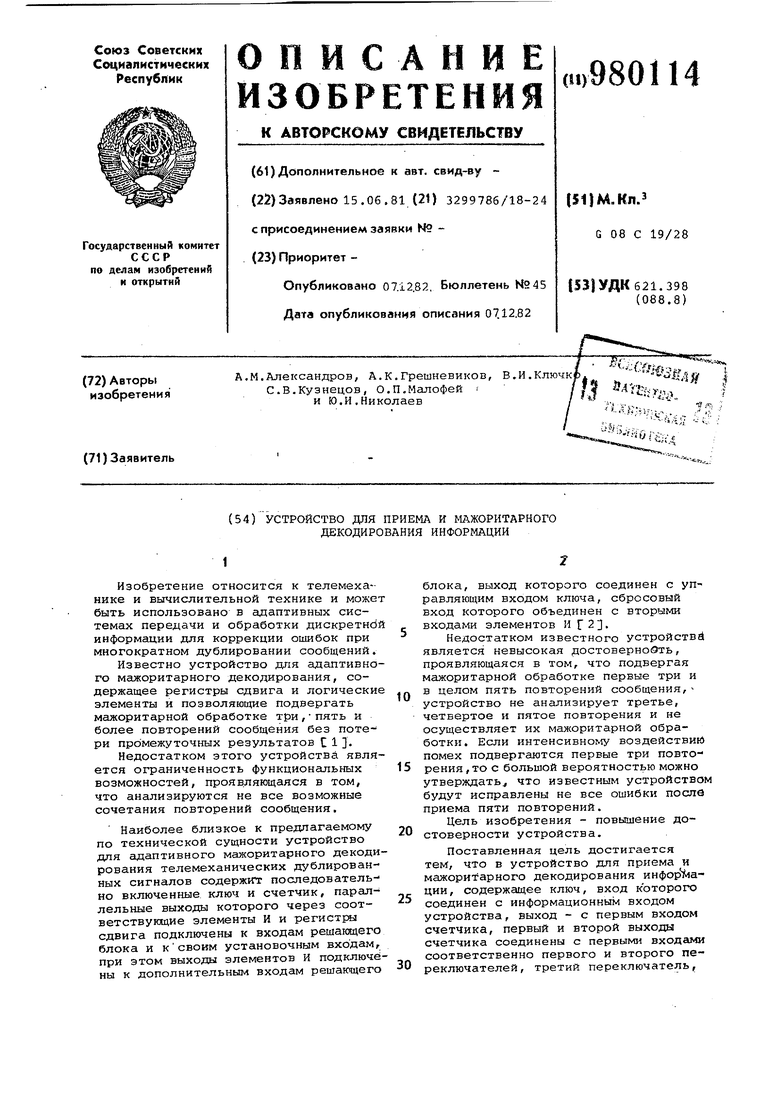

25 соединен с информационным входом устройства, выход - с первым входом счетчика, первый и второй выходы счетчика соединены с первыми входами соответственно первого и второго пе30реключателей, третий переключатель. выходы переключателей соединены с ин формационными входами соответствуклдн регистров сдвига, выходы которых сое динены с первым, вторым и третьим входами решающего блока, первый выход которого соединён с первым выходом устройства, выходы первого и вто рого регистров сдвига соединены сооз ветственно с вторым и третьим входам счетчика, введен кодопреобразователь первый, второй и третий выходыг счетчика соединены соответственно с первым, вторым и третьим входами -кодо-. преобразователя, четвертый вход которого объединен с первым входом третьего переключателя и четвертым входом решающего блока и подключен к выходу входного ключа, первый, вто рой и третий выходы кодопреобразователя соединены с вторыми входами соответствующих переключателей, выход третьего регистра сдвига соединен с пятым входом кодопреобразователя, пятый вход решающего блок подключен к второму выходу счетчика, второй и четвертый выходы решаквдего блока сое динены соответственно с третьими вхо дами первого и второго переключателе и вторым выходом устройства. Кроме того, кодопреобразователь выполнен на cyNCMaTope, элементах И, ИЛИ и ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ, выход сумматора соединен с первым входом второго элемента -И, выход которого соединен с вторым входом третьего элемента ИЛ первый вход первого элемента И соеди нен с первым входом кодопреобразователя, второй вход первого элемента И объединен с первым входом элемента ИЛИ-НЕ и подключен к второму входу кодопреобразователя, первый вход сум матора объединен с вторым входом вто pord элемента И и подключен к четвер тому входу кодопреобразователя, пяты вход которого соединен с вторьнч входом сумматора, выходы второго элемен та ИЛИ, сумматора и третьего элемента ИЛИ соединены соответственно с первым, .вторым и третьим выходами ко допреобразователя. Кроме того, решающий блок выполнен на переключателях, элементах запрета. И, ИЛИ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход ко торого соединен с выходом первого элемента запрета, выход - с первым входом первого переключателя, выход второго элемента запрета и выход вто рого элемента И соединены с первым 1и вторым входами второго элемента ИЛ :выход которого соединен с первым входом второго переключателя, второй вход которого соединен с выходом третьего элемента ИЛИ, первые входы первого элемента И, первого элемента запрета и второй вход первого переключателя подключены к первому входу решающего блока, первые входы второго элемента запрета, второго элемента И и третьего элемента ИЛИ подключены к второму входу решающего блока, вторые входы первого и второго элементов и подключены к третьему входу решающего блока, вторые входы элементдв запрета и второй вход третьего элемента ИЛИ подключены соответственно к четвертому и пятому входам решающего блока, выход первого переключателя соединен с первым и вторьлм входами решающего блока, выход второго переключателя соединен с третьим и четвертым входами решающего блока. Этим достигается анализ и мажоритарная обработка первых трех повторений, пяти повторений в целом и трех последних повторений (третье, четвертое и пятое). Если интенсивному воздействию помех повергаются первые три повторения то с большой вероятностью правильный прием будет осуществлен после мажоритарной обработки трех последних повторений сообщения. На фиг.1 представлена структурная схема устройства для приема и мажоритарного декодирования информации-, на фиг. 2 - схема кодопреобразователя, на фиг. 3 - схема решающего блока. Устройство содержит (фиг.1) ключ 1, счетчик 2, кодопреобразователь 3, переключатели 4-6, регистры 7-9 сдвига и решающий блок 10, содержащий первый выход 11, вход 12, второй выход 13 и входы 14-17. Кодопреобразователь 3 содержит (фиг.2) элементы И 18 и 19, элементы ИЛИ 20-22, элемент ИЛИ-НЕ 23 и сумматор 24 по модулю два с отрицанием. Решающий -блок 10 содержит также элементы И 25 и 2.6, элементы ИЛИ 27-29, элементы запрета 30 и 31 и переключатели 32 и 33. Ключ 1 предназначен для ввода информации в устройство. Счетчик 2 содержит три двоичных разряда 2,2 и 2 и предназначен для подсчетачисла принятых 1 для одноименных элементов принимаег-йлх повторений. Кодопреобразователь 3, включаясь в работу в момент начала приема четвертого повторения, преобразует коды входных сигналов, своим воздействием меняя Первоначальное функциональное назначение регистров сдвига. Работа кодопреобразователя задается с помощью табл.1, которая может быть использована для получения логических: условий (выражений) Y (Х + Хз)+Х . .x7T 4(), х,,х,х состояние разрядов счетчика 2 подсчитыв ющего количества 1 одноименных элемента принимаемых повторен соответственно; Хд,) - значение одноименных разрядов четвертого и пятого повторений соответственно; Y - сигнал принятия решения по одноименным элементам четырех повторений, причем при Y 1 имеет место преобладание элемен тов опного типа, а при Yj 0 - преобладание элементов разного тиаа (одинаковое количество); Y - сигнал принятия решения по одноименным элементс1М третьего и четвертого повторений причем при эле-:менты совпадают, а пр элементы разные У - значение результата принятия решения первого (Y, ) и второго (Y) типа, причем при Y 1 в одноименных элементах преобладает информационная единиY 0 - все осталь ца, а ные случаи. Переключатели 4-6 предназначены для коммутации информационных входов регистров 7-9 сдвига, которые являются многофункциональными элементами устройства. При приеме трех первых повторений в регистры 7 и 8 заносится код числа принятых единиц для каж дого разряда сообщения, -третье повто рение заносится в регистр 9. После приема четырех повторений в регистры 7-9 заносится результат обработ ки кодопреобразователем 3. После при ема пяти повторений в регистр 7 заносится результат мажоритарной обработки пяти повторений, в регистр 8-результат обработки третьего, четвер того и пятого повторений. Работа решающего блока 10 задается следующими логическими условиями, полученными из табл.2: Y, где Х - значение элементов пятого повторения. Z - результат мажоритарной обработки пяти повторений/ Z, - результат мажоритарной обработки трех последних повторений , Устройство работает след ющим образом. Исходное состояние счетчика 2 и регистров 7-9 сдвига - нулевое, ключ 1 открыт, первые входы переключателей 4 и 5 открыты. Первое повторение че-рез ключ 1 поступает на вход счегчика 2. Если принимаемый элемент 1, то в первый разряд 2. счетчика 2 записывается 1, которая через открытый переключатель 4 записывается в регистр 7 сдвига, а сигнал управления устанавливает счетчик 2 в состояние О, подготавливая к приему очередного элемента. Единица переписывается из первого разряда во второй регистра 7 сдвига. При приеме О состояние счетчика 2 меняется, а в регистр 7 записывается О (имеет место только сдвиг информации . Таким образом, по окончании приема первого повторения оно оказывается записанным в регистр 7 сдвига. Состояние регистров 8 и 9 - нулевое. При сдвиге информации в регистре 7 на один разряд первый элемент первого повторения с выхода регистра 7 поступает на установочный вход первого разряда 2 счетчика 2. Если этот элемент 1, то первый разряд счетчика 2 устанавливается в это же состояние. Если первый элемент второго повторения также 1, то состояние счетчика 2 изменится - первый разряд установится в О, а второй разряд - в 1. При считывании состояний счетчика 2 в первый разряд регистра 7 записывается О, а в первый разряд регистра 8 - 1. Далее сбрасывается счетчик 2 в О, информация в регистрах сдвигается на один разряд и счетчик „2 устанавливается в состояние, соответствующее второму элементу первого повторения, С приходом очередного элемента второго повторения процесс оьработки повторяется. В момент окончания приема второго повторения открывается первый вход переключателя 6, обеспечивая непосредственную запись третьего повторения а регистр 9. При приеме каждого элемента третьего повторения состояние первого и второго разрядов счетчика 2 может оказаться в одном из следующих состояний: 00, 10, 01, 11. Информационная 1 формируется и выдается на выход устройства в тех случаях, когда счетчик 2 находится в состоянии 01, 11 (две или три единицы из трех возможных). Информационный О формируется и вьщается на выход устройства для состояний 00

и 10 счетчика 2 (три или два йуля из трех возможных).

Следовательно, информационные элементы могут непосредственно формироваться по состоянию второго разряда счетчика 2. Поступая на пятый вход решающего блока 10, информационные элементы через элемент ИЛИ 30 подаются на открытый второй вход переключателя 33, с выхода которого снимаются для дальнейшей обработки. С момента окончания приема третьего повторения на переключателях 4-6 проиэг водится подключение вторых входов и отключение первых входов. Если результат мажоритарной обработки два из трех необходимо выдать повторйо, то содержимое регистра 8 поступает в решающий блок 10 на второй вход, где, проходя через элемент ИЛИ 28 и переключатель 33, выдается на второй выход устройства.

Если на момент окончания приема третьего повторения результат мажоритарной обработки не будет удрвлетвррять требованию по верности информации, тогда продолжится прием четвертого повторения, которое, поступает через переключатель 1 на четвертый вход кодопреобразователя 3, на пятый вход которого поступают элементы третьего повторения считываемого с регистра 9. Элементы, считывае.мые с регистров 7 и В, поступая на установочные входы разрядов 2 и 22 счетчика 2 формируют код числа принятых единиц для каждого разряда сообщения с элементом, одновременно поступающим от четвертого повторения. Код считывается с выходов разрядов счетчиков 2 и подается на первые три входа кодопреобразователя 3. Выходные сигналы у. , Y2., УЗ , формируемые в соответствии с табл.1 и которые можно задать выражениями ( 1) соответственно, запиолваются в регистры 7-9, проходя по второму открытому входу переключателей 4-6 (первые входы переключателей 4-6 в этот момент закрыты. По окончании приема четвертого повторения в регистрах 7-9 будут записаны численные значения принятия решения по четырем повторением. С этого момента закрываются вторые входы переключателей 4 и 5 и первый вход переключателя 31 и открываются третьи входы переключателей 4 и 5, первый вход переключателя 28 и второй вход переключателя 31.

Если выходные сигналы регистров 7-9 сдвига Y .YI принимают значения 101 соответственно, то это означает, что по четырем одноименным элементам принято решение (Xj 1), это решение является 1 (), и элементы третьего и четвертого повторений не совпадают, т.е. решение по третьему и четвертому повторениям не принято (). в этом случае на элемент И 25 подаются единичные сигналы Y 1 , Y-J 1 , что определяет появление 1 сигнала на выходе элемента и 25 и его прохождение через элемент ИЛИ 27, переключатель 32 на первый выход устройства и запись в регистр 7, как результата мажоритарной обработки пяти повторений (Z).

Значение одноименного элемента пятого повторения (Xj), поступающее на четвертый вход решающего блока 10 на формировании результата мажоритарной обработки пяти повторений, не , сказывается. Однако так как одноименные элементы третьего и четвертого повторений не совпадают (), то результат мажоритарной обработки тре последних повторений (Z) полностью определяется соответствующим элементом пятого повторения. Поскольку на запрещающем входе элемента запрет 31 сигнал отсутствует (У 0), то сигнал X-j по четвертому входу решающего блока 10 через элемент запрета 31, элемент ИЛИ 29 и переключатель 33 проходит на четвертый выход и записываеся в регистр 8 как результат мажоритарной обработки (Z ) трех последних повторений.

Если выходные сигналы регистров 7-9 имеют вид 011, это значит, что по одноименным элементам четырех повторений решение не принято (), т.е. существует неопределенность, так как приняты две 1 и два О. В этом случае мажоритарное решение по пяти повторениям (Z ) всецело определяется значением соответствующего элемента пятого повторения Хтт. Поскольку на запрещающем входе элемент запрет 3.0 сигнал отсутствует ), то сигнал Ху по четвертому входу через элемент И 30, элемент ИЛИ 27 и переключатель 32 проходит на первый выход и записывается в регистр 7 как результат мажоритарной обработки (Z. пяти повторений.

В это же время сигна.лы У,2 1 и V поступают на входы элемента И 26, синал с выхода которого через элемент ИЛИ 29 и переключатель 33 проходит на четвертый выход и записывается в регистр 8 как мажоритарный результат трех последних повторений (Z) независимо от значения соответствующего элемента пятого повторения (Ху) Это происходит потому, что одноименные элементы третьего и четвертого повторений совпали () и их значение соответствует 1 ).

Если результаты мажоритарной обработки (Zjf ,t.) необходимо выдать повторно, то закрывается первый вход переключателя 32 и первый вход переключателя 31 и открывается второй вход переключателя 27 и первый вход переключателя 31. Результат Z из

регистра 7 через переключатель 27 поступает на первый выход устройства. Результат Z из регистра 8 через элемент ИЛИ 28 и переключатель 33 проходит на второй выход устройства. В табл,2 приведены все варианты решения, которые могут быть получены решающим блоком 10. Логические элементы блока 10 при этом работают аналогично рассмотренному выше.

Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное. Известное устройство позволяет подвергать мажоритарной обработке только первые три или. пять повторений в целом. Предлагаемое устройство позволяет вести дополнительно мажоритарную обработку третьего, четвертого и пятого повторений, что повышает его достоверность. Эквивешентная вероят ность ошибок для способа мажоритарно обработки пяти повторений равна .1 „ ,-

0

где Р - вероятность искажения одноф, элемента.

Для известного устройства при полвлен и трехкратных ошибок в семи и девяти возможных случаев ошибки неправлены не будут, что ведет к потере информации

Ри.-Р94 где Р сс7-Ро/

п - число элементов в одном повторении. В предлагаемом устройстве

.,. где Р-.:4-Р.,

91 о

tTo достигается исправлением трех ва риантов ошибок при мажор1Ргарной o6pafботке трех последних повторений. Следовательно ,

.

т.е. потери информации уменьшаются почти в два раза.

Таблица 1

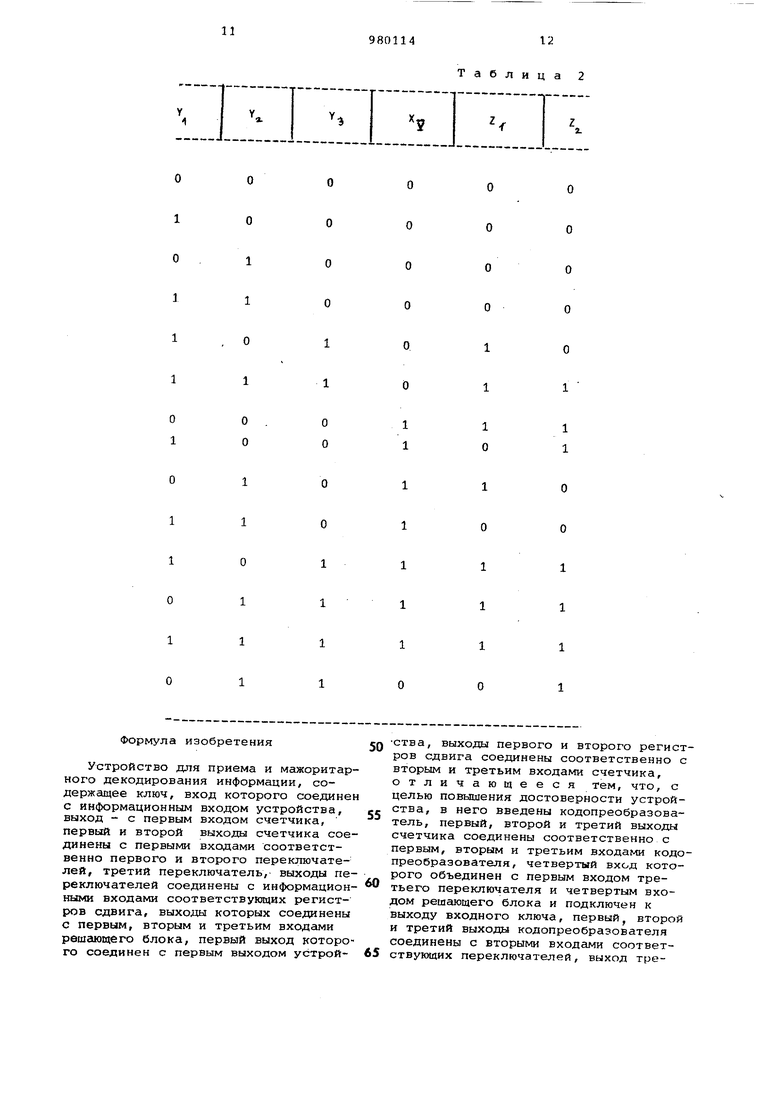

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования | 1982 |

|

SU1073788A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Модифицированное устройство коррекции ошибок | 2016 |

|

RU2635253C1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Модифицированное устройство коррекции ошибок с учетом сигнала стирания | 2019 |

|

RU2711035C1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1978 |

|

SU884163A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Устройство для приема и мажоритарного декодирования информации | 1987 |

|

SU1439750A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ | 1998 |

|

RU2152129C1 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

О 1 О

О 1

О О

о о

о 1

Формула изобретения

Устройство для приема и мажоритарного декодирования информации, содержащее ключ, вход которого соединен с информационным входом устройства, выход - с первым входом счетчика, первый и второй выходы счетчика соединены с первыми входами соответственно первого и второго переключателей, третий переключатель, выходы переключателей соединены с информационными входами соответствующих регистЕюв сдвига, выходы которых соединены с первым, вторым и третьим входами решающего блока, первый выход которого соединен с первым выходом устрой1 1

О

1

1 1

1 о

1 1 1 1

о 1 1

о 1 1

ства, выходы первого и второго регистров сдвига соединены соответственно с вторым и третьим входами счетчика, отличающееся тем, что, с целью повышения достоверности устройства, в него введены кодопреобразователь, первый, второй и третий выходы счетчика соединены соответственно с первым, вторым и третьим входами кодопреобразователя, четвертый вход которого объединен с первым входом третьего переключателя и четвертым входом решающего блока и подключен к выходу входного ключа, первый, второй и третий выходы кодопреобразователя соединены с вторыми входами соответствующих переключателей, выход третьего регистра сдвига соединен с пя тым входом кодопреобразователя, пяты вход решающего блока подключен к второму выходу счетчика, второй и четвертый выходы решающего блока со единены соответственно с третьими входами первого и второго переключа телей и вторым выходом устройства. 2.Устройство ПОП.1, отличающееся тем,что кодопреоб разователь выполнен на сумматоре, элементах И, ИЛИ и ИЛИ-НЕ, выход пер вого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, выход элемента ИЛИ-НЕ соединен с вто рым входом второго элемента ИЛИ, выход сумматора соединен с паркам входом второго элемента И, выход которо соединен с вторым входом третьего элемента ИЛИ, первый вход первого элемента И соединен с первым входом кодопреобразователя, второй вход пер вого элемента И объединен с первым входом элемента ИЛИ-НЕ и подключен к второму входу кодопреобразователя, первый вход сумматора объединен с вт рым входом второго элемента И и подключен к четвертому входу кодопреобразователя, пятый вход которого соединен с вторым входом сумматора, выходы второго элемента ИЛИ, сумматора и третьего элемента ИЛИ соединены соответственно с первым, вторым и третьим выходами кодопреобразователя . 3.Устройство ПОП.1, отличающееся тем, что решающий блок выполнен на переключателях.

Фг/г./ элементах Запрета, И, ИЛИ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй Вход которого соединен с выходом первого элемента запрета, выход - с первым входом первого переключателя,выход второго элемента запрета и выход второго элемента И соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом второго переклю- чателя, второй вход которого соединен с выходом третьего элемента №ЛИ, первые входы первого элемента И, первого элемента запрета и второй вход пер- : вого переключателя подключены к первому входу решающего блока, первые , входы второго элемента запрета, второго элемента И и третьего элемента ИЛИ подключены к второму входу решающего блока, вторые входы первого и второго элементов И подключены к третьему входу решающего блока, вторые входы элементов запрета и второй вход третьего элемента ИЛИ подключены соответственно к четверто) и пятому входам решающего блока, выхо; первого переключателя соединен с первым и вторым входами решающего блока, выход второго переключателя соединен . с Третьим и четвертым входами решающего блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 767989, кл. Н 04 L 1/10, 1978. 2.Авторское свидетельство СССР по заявке 2718711/18-09, 1978 (прототип).

фу1.2

0tff.J

Авторы

Даты

1982-12-07—Публикация

1981-06-15—Подача