Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии.

Известен элемент памяти в составе ячейки матрицы энергонезависимой электрически перепрограммируемой памяти (Мордвинцев В.М., Кудрявцев С.Е. Ячейка энергонезависимой памяти. Патент РФ №2302058), включающий проводящий слой первого уровня в виде локальной области с высокой концентрацией носителей из полупроводника n+- или р+-типа, проводящий слой второго уровня, расположенный непосредственно под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью.

Такую конструкцию изолирующей щели называют открытой «сэндвич»-структурой. Она получается из традиционной «сэндвич»-структуры путем локального травления проводящего слоя второго (верхнего) уровня и слоя диэлектрика, в качестве которого обычно используется аморфный оксид (например, SiO2). Образующийся при этом открытый торец слоя диэлектрика, располагающийся между двумя проводящими слоями, и является изолирующей щелью. Далее в открытой «сэндвич»-структуре выполняется операция электроформовки, представляющая собой экспозицию структуры под напряжением, превышающим некоторое пороговое значение. Поскольку ширина изолирующей щели мала (она определяется толщиной слоя диэлектрика), в структуре достигаются высокие электрические поля, и по ее поверхности начинает протекать ток. Локальное прохождение тока через изолирующую щель вызывает деструкцию молекул диэлектрика на ее поверхности при столкновении с электронами, кислород удаляется в газовую фазу, и поверхность изолирующей щели обогащается атомами соответствующего металла или полупроводника (например, Si, в случае использования в качестве диэлектрика SiO2), которые играют роль частиц проводящей фазы (ЧПФ). Накопление ЧПФ приводит сначала к образованию проводящей среды (материала с переменной проводимостью), а затем, за счет частичного, термически активируемого при увеличении тока, ее исчезновения (окисления кислородом, поступающим из газовой среды, т.е. «выгорания»), к формированию в ней изолирующего зазора нанометровой ширины. Этот процесс называется электроформовкой. В результате его выполнения в изолирующей щели происходит самоформирование проводящей наноструктуры, включающей проводящую среду и нанометровый изолирующий зазор. Баланс процессов возникновения ЧПФ при электронном ударе и их термически активируемого «выгорания» приводит к установлению равновесной ширины h изолирующего зазора, которая зависит от приложенного напряжения.

Работа такого элемента памяти основана на изменении ширины h изолирующего зазора, которая определяет состояние проводимости элемента памяти, при приложении импульсов напряжения с различной амплитудой и длительностью. В случае использования импульса со средним значением напряжения (но превышающим пороговое напряжения образования ЧПФ) и относительно большой длительностью, прохождение тока через изолирующую щель вызывает дополнительное накопление ЧПФ, нарастание проводящей среды и уменьшение ширины изолирующего зазора. Элемент памяти при этом переключается в высокопроводящее состояние. При приложении короткого импульса напряжения с повышенной амплитудой проводящая среда частично выгорает (за счет разогрева при прохождении тока и термического окисления ЧПФ адсорбированным из газовой среды кислородом), увеличивая тем самым ширину изолирующего зазора и уменьшая проводимость элемента памяти. Элемент памяти переключается при этом в низкопроводящее состояние. Переключения между низко- и высокопроводящим состояниями возможны многократно. Оба состояния могут сохраняться неограниченно долго при отключении питания. Неразрушающее считывание состояния элемента памяти обеспечивается путем измерения тока при использовании импульса напряжения с низким значением амплитуды, не превышающим порогового напряжения образования ЧПФ.

Недостатком такого элемента памяти является то, что область с высокой концентрацией носителей из полупроводника n+- или р+-типа выполняет сразу две разнородные функции: она является и нижним электродом изолирующей щели, и эмиттером транзистора, который располагается ниже в полупроводниковой подложке. Поскольку требования к этим функциям не полностью совпадают, такой элемент памяти не может обеспечить оптимальное выполнение каждой из них. В частности, конструкция является нетехнологичной при изготовлении ее методами традиционной кремниевой технологии, из-за того, что элемент памяти оказывается жестко «привязан» к поверхности кремниевой пластины. Поэтому, чтобы обеспечить контакт изолирующей щели со средой (например, газообразным кислородом), необходимо предусматривать глубокие и узкие «колодцы» в многослойной металлизации, создаваемой над полупроводниковой структурой.

Предложен элемент памяти в составе ячейки матрицы энергонезависимой электрически перепрограммируемой памяти (Мордвинцев В.М., Кудрявцев С.Е. Ячейка энергонезависимой электрически перепрограммируемой памяти. Патент РФ №2436190), включающий проводящие слои первого и второго уровня, расположенный между ними и непосредственно под проводящим слоем второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью. В таком элементе памяти проводящий слой первого уровня может быть выполнен из материала (металла), отличного от слоя полупроводника с высокой концентрацией носителей, который используется в качестве эмиттера транзистора ячейки памяти, а изолирующая щель представляет собой открытую «сэндвич»-МИМ(металл-диэлектрик-металл)-структуру. Это позволяет распределить функции нижнего электрода изолирующей щели и эмиттера транзистора между различными слоями и тем самым оптимизировать характеристики конструкции. В частности, такой элемент памяти можно «оторвать» от поверхности полупроводниковой пластины и вынести его на поверхность многослойной металлизации, предусмотрев электрическое соединение его с эмиттером транзистора, что исключает необходимость создания в многослойной металлизации узких глубоких колодцев к изолирующей щели. По совокупности признаков этот элемент памяти наиболее близок к предлагаемым техническим решениям.

Основным недостатком такого элемента памяти является то, что в процессе электроформовки, т.е. накопления ЧПФ и формирования в образующейся проводящей среде изолирующего зазора нанометровой ширины, существует заметная вероятность электрического пробоя, который выводит элемент памяти из строя. Включение внешнего ограничительного сопротивления (или другой способ ограничения тока за счет внешних схем) не дает уверенного эффекта, поскольку заряда, накапливающегося в паразитных емкостях, расположенных между внешними схемами и элементом памяти, достаточно для электрического пробоя проводящей наноструктуры в случае резкого увеличения ее проводимости.

В предлагаемом элементе памяти, включающем проводящие слои первого и второго уровня, расположенный между ними и непосредственно под проводящим слоем второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью, между изолирующей щелью и проводящим слоем первого уровня расположен дополнительный диэлектрический слой толщиной от 1,3 до 3 нм.

Достигаемый при этом основной технический результат состоит в следующем. Дополнительный диэлектрический слой включается последовательно образующейся при электроформовке проводящей наноструктуре, причем в непосредственной близости от нее, фактически они находятся в соприкосновении. Поэтому дополнительный диэлектрический слой может эффективно ограничивать ток через наноструктуру, даже тот который протекает при разрядке паразитных емкостей, а значит, гарантированно предотвращать электрический пробой элемента памяти. Чтобы ограничение тока было на необходимом уровне, исключающем электрический пробой, толщина дополнительного диэлектрического слоя должна быть более 1,3 нм. В то же время, чтобы он не подавлял процесс электроформовки, который развивается тем быстрее, чем выше значения тока через наноструктуру, толщина дополнительного электрического слоя не должна превышать 3 нм. В целом, в таком устройстве резко, на много порядков, уменьшается вероятность электрического пробоя при выполнении электроформовки. Это позволяет увеличить эффективность выполнения операции электроформовки при изготовлении такой памяти.

В частности, дополнительный диэлектрический слой может быть выполнен из оксида материала проводящего слоя первого уровня. Достигаемый при этом основной технический результат состоит в следующем. Такой диэлектрический слой может быть легко получен - путем контролируемой термической обработки в кислородсодержащей среде, а выращенные таким образом окисные пленки толщиной порядка нескольких нанометров, как правило, обладают высоким качеством.

В частности, слой диэлектрика и дополнительный диэлектрический слой могут быть выполнены из различных материалов. Достигаемый при этом основной технический результат состоит в следующем. Различие материалов двух слоев позволяет обеспечить сохранность дополнительного диэлектрического слоя во время травления слоя диэлектрика (при формировании открытой «сэндвич»-структуры) за счет селективного воздействия травителя на различные материалы (значительно большей скорости травления слоя диэлектрика, чем дополнительного диэлектрического слоя).

В источниках информации не обнаружено сведений, аналогичных предложенному элементу памяти, что позволяет сделать вывод о его новизне.

Кроме того, предлагаемое устройство для специалиста явным образом не следует из уровня техники, что подтверждает соответствие предлагаемого технического решения критерию «изобретательский уровень».

Обоснование предлагаемого устройства вместе со сведениями, подтверждающими возможность его осуществления, приводятся ниже с использованием графических материалов.

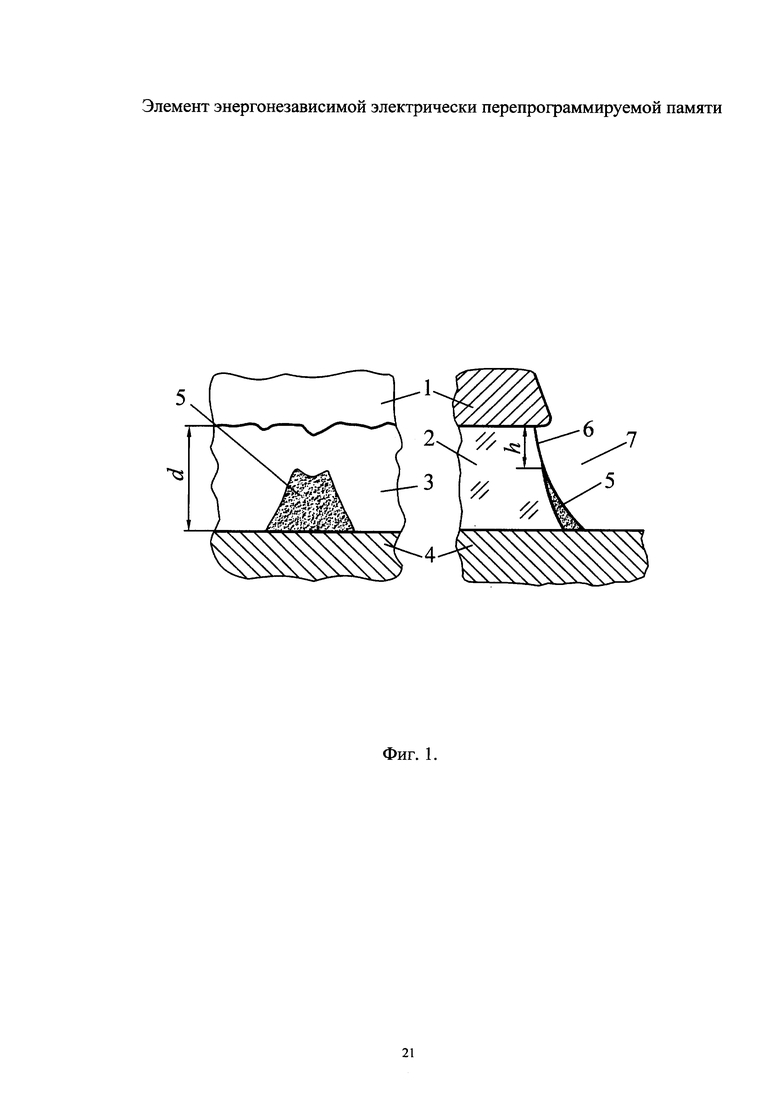

На фиг. 1 схематически показан элемент памяти в соответствии с решением, выбранным в качестве прототипа - открытая «сэндвич»-МДМ-структура после выполнения электроформовки. 1 - проводящий слой второго уровня - верхний электрод изолирующей щели (катод); 2 - слой диэлектрика (SiO2) толщиной d около 20 нм; 3 - изолирующая щель в форме открытого торца слоя диэлектрика; 4 - проводящий слой первого уровня - нижний электрод изолирующей щели (анод); 5 - проводящая среда (материал с переменной проводимостью) на поверхности изолирующей щели; 6 - изолирующий зазор переменной ширины h; 7 - газовая среда (среда, контактирующая с поверхностью изолирующей щели и обеспечивающая обмен частицами материала с переменной проводимостью).

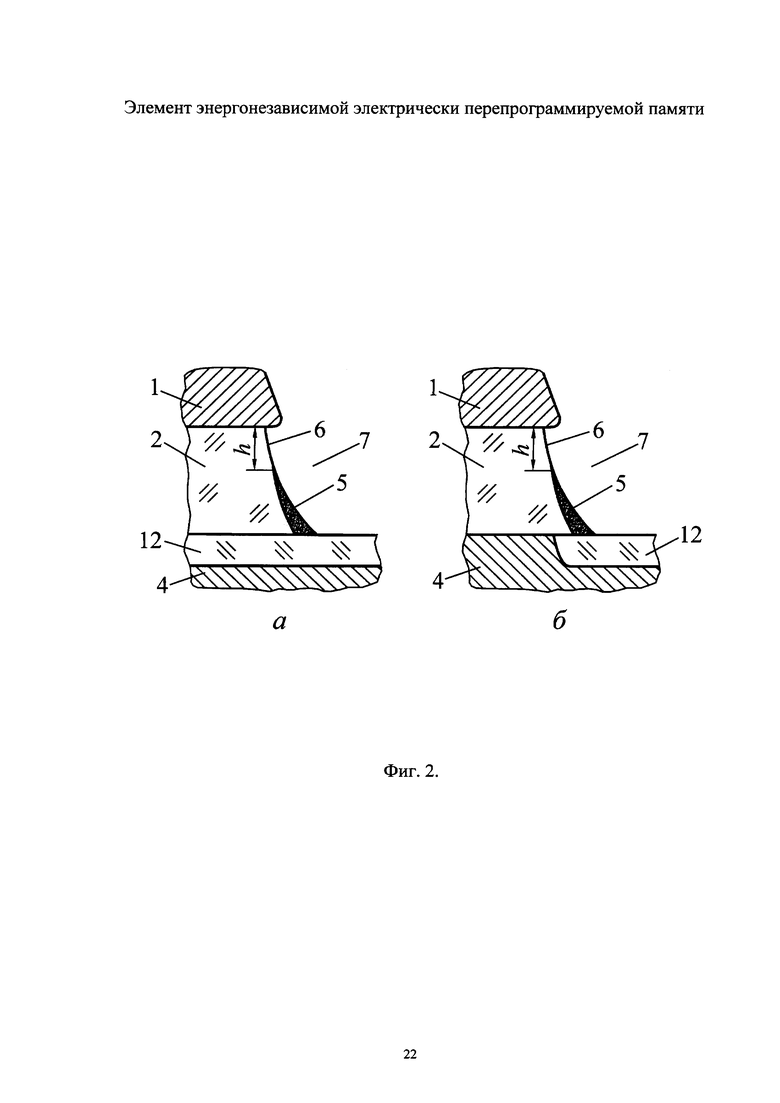

На фиг. 2 схематически показаны поперечные сечения предлагаемого элемента памяти для двух вариантов расположения дополнительного диэлектрического слоя: (а) - по всей поверхности нижнего электрода, слой формируется до осаждения слоя диэлектрика (SiO2); (б) - только на открытой части поверхности нижнего электрода, слой формируется после изготовления открытой «сэндвич»-структуры окислением поверхности материала нижнего электрода. 1 - проводящий слой второго уровня - верхний электрод изолирующей щели (катод); 2 - слой диэлектрика (SiO2) толщиной около 20 нм; 4 - проводящий слой первого уровня - нижний электрод изолирующей щели (анод); 5 - проводящая среда (материал с переменной проводимостью) на поверхности изолирующей щели; 6 - изолирующий зазор переменной ширины h; 7 - газовая среда (среда, контактирующая с поверхностью изолирующей щели и обеспечивающая обмен частицами материала с переменной проводимостью); 12 - дополнительный диэлектрический слой.

На фиг. 3 схематически показаны фрагмент экспериментального образца матрицы в плане и поперечное сечение ячейки памяти с биполярным n-p-n-транзистором, обеспечивающим электрическую развязку ячеек в матрице. 1 - проводящая шина второго уровня (проводящий слой второго уровня) - верхний электрод изолирующей щели (W); 2 - слой диэлектрика (SiO2) толщиной около 20 нм; 3 - изолирующая щель в форме открытого торца слоя диэлектрика; 4 - проводящий слой первого уровня - нижний электрод изолирующей щели (TiN); 7 - газовая среда; 8 - область кремния р-типа - проводящая шина первого уровня и база транзистора; 9 - подложка кремния n-типа, коллектор транзистора; 10 - слой толстого (0,5 мкм) диоксида кремния; 11 - область кремния n+-типа, эмиттер транзистора; 12 - дополнительный диэлектрический слой (TiO2). Размеры приведены в микрометрах.

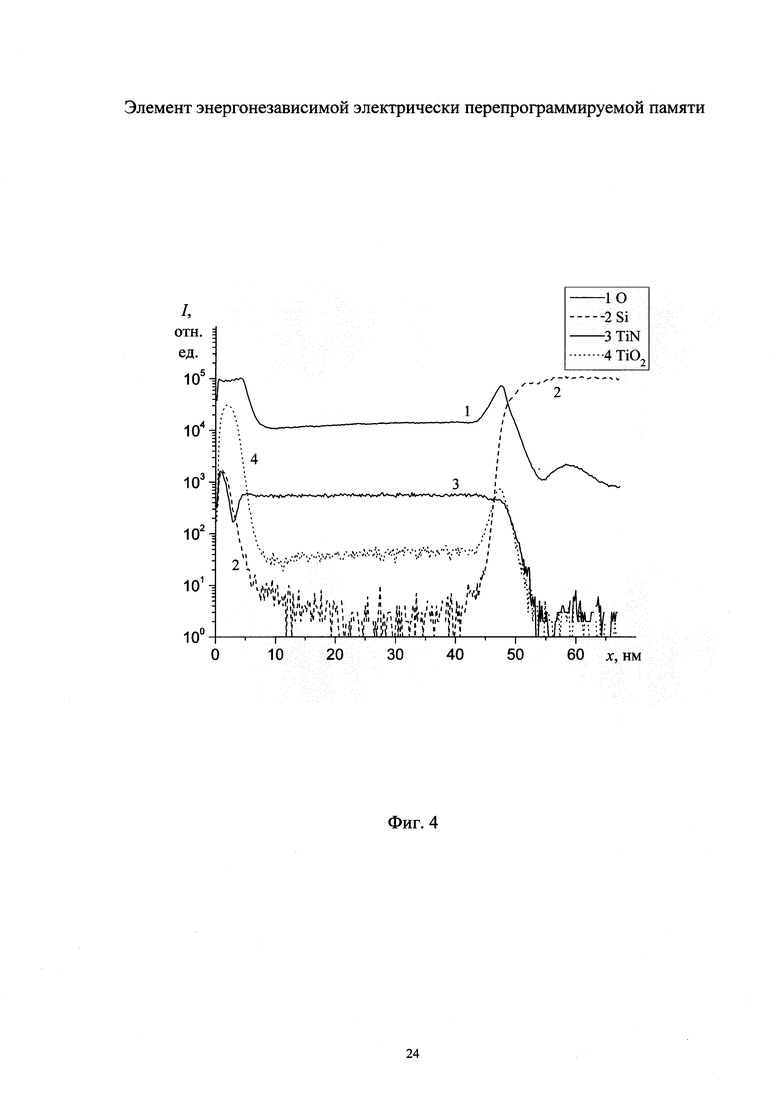

На фиг. 4 представлены типичные профили по глубине (зависимости интенсивности I выхода иона от глубины x травления образца) в слое TiN на Si подложке для отрицательных однозарядных ионов, показанных на вставке, полученные с помощью ВИМС. Образец после образования поверхностного слоя TiO2 путем отжига в течение 7 минут при температуре 440°С с «горящей» плазмой в смеси аргона и кислорода (мощность разряда 200 Вт, давление аргона в камере 0,9 Па, парциальное давление кислорода 0,06 Па).

На фиг. 5 представлены типичные профили по глубине (зависимости интенсивности I выхода иона от глубины x травления образца) на поверхности слоя TiN для отрицательных однозарядных ионов, показанных на вставке, полученные с помощью ВИМС. Образец тот же, что на фиг. 4, данные приведены на глубину до 14 нм от внешней поверхности слоя. Показана методика определения толщины s слоя TiO2.

На фиг. 6 приведена типичная ВАХ для случая успешного выполнения электроформовки треугольным импульсом со скоростью изменения напряжения 4 В/с. Использовалось ограничение тока на уровне 190 мкА.

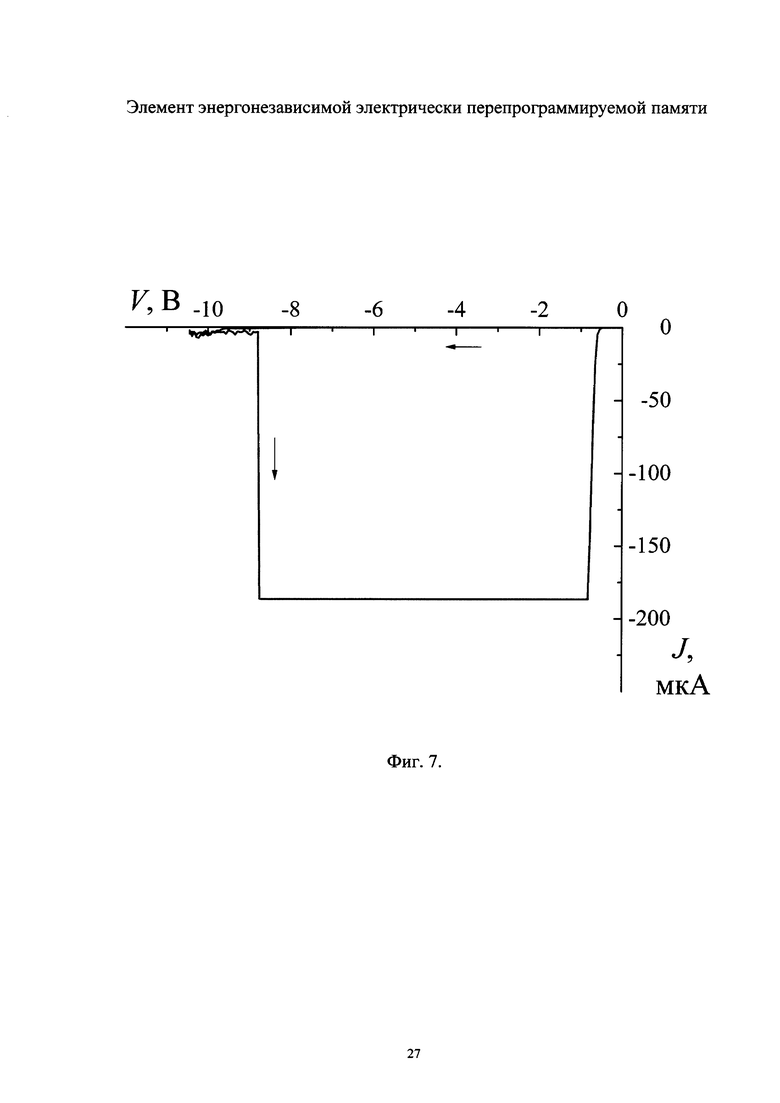

На фиг. 7 приведена типичная ВАХ для случая возникновения электрического пробоя при выполнении электроформовки треугольным импульсом со скоростью изменения напряжения 4 В/с. Использовалось ограничение тока на уровне 190 мкА.

На фиг. 8 приведены экспериментально полученные зависимости вероятности  успешной электроформовки и толщины s дополнительного диэлектрического слоя TiO2 от температуры T отжига слоя TiN. «Кружками» и «крестами» показаны данные для образцов со временем отжига 3 минуты. «Треугольниками» показаны данные для образцов со временем отжига 9 минут. Толщина d слоя диэлектрика (SiO2) 19,8±2 нм.

успешной электроформовки и толщины s дополнительного диэлектрического слоя TiO2 от температуры T отжига слоя TiN. «Кружками» и «крестами» показаны данные для образцов со временем отжига 3 минуты. «Треугольниками» показаны данные для образцов со временем отжига 9 минут. Толщина d слоя диэлектрика (SiO2) 19,8±2 нм.

На фиг. 9 представлены типичные профили по глубине (зависимости интенсивности 7 выхода иона от глубины х травления образца) на поверхности слоя n+-Si (концентрация фосфора 3⋅1020 см-3) для отрицательных однозарядных ионов, показанных на вставке, полученные с помощью ВИМС. Образец хранился в комнатных условиях 2 года после обработки в травителе, содержащем плавиковую кислоту (стравливания диоксида кремния). Показана методика определения толщины s образовавшегося слоя «естественного» SiO2, аналогичная фиг. 5.

Принципы работы элементов памяти: предлагаемого и реализованных ранее в аналоге и прототипе (фиг. 1), - совпадают. Близки и их конструкции (сравнить фиг. 1 и 2), которые используют открытые «сэндвич»-структуры n+-Si-SiO2-W и TiN-SiO2-W. Во всех случаях в качестве проводящего слоя 1 второго уровня (верхнего электрода) применен вольфрам (W), а в качестве слоя диэлектрика 2 - диоксид кремния (SiO2) толщиной d около 20 нм. Проводящий слой 4 первого уровня (нижний электрод) может быть выполнен из высоколегированного кремния n-типа (n+-Si) либо из нитрида титана (TiN). В то же время в предложенном устройстве добавлен новый элемент - дополнительный диэлектрический слой 12 (фиг. 2), который обеспечивает ограничение тока через проводящую наноструктуру в ходе выполнения электроформовки, когда проводимость наноструктуры резко увеличивается. Тем самым, в сравнении с прототипом, существенно уменьшается вероятность электрического пробоя элемента памяти, который может сопровождаться необратимым разрушением открытой «сэндвич»-структуры в микрометровом масштабе и выходом элемента памяти из строя. Возможны два различных варианта расположения дополнительного диэлектрического слоя 12 (фиг. 2), которые могут отличаться и способами его формирования. В первом случае (фиг. 2а) слой 12 создается на всей поверхности нижнего электрода 4 до момента осаждения слоя диэлектрика 2 (SiO2), способ его формирования может быть любой, например окисление материала нижнего электрода или осаждение другого диэлектрического материала. Во втором случае (фиг. 2б) дополнительный диэлектрический слой 12 создается после изготовления всей отрытой «сэндвич»-структуры путем окисления материала нижнего электрода 4, например, кислородом из газовой фазы. Из-за боковой диффузии кислорода под открытый торец слоя SiO2 дополнительный окисный слой 12 распространяется и под поверхность изолирующей щели. Поэтому при образовании проводящей наноструктуры в процессе электроформовки (верхний проводящий слой 1 является катодом, а нижний 4 - анодом) дополнительный диэлектрический слой 12 и в этом случае тоже оказывается включенным последовательно проводящей среде 5, как и на фиг. 2а.

Для подтверждения возможности реализации предложенного устройства и заявленных технических результатов образцы элемента памяти изготавливались в виде матрицы памяти (фиг. 3) размерностью 3×3 ячейки. Каждая ячейка, кроме элемента памяти, содержала биполярный n-p-n-транзистор (элементы 8, 9, 11 на фиг. 3), который обеспечивал электрическую развязку ячеек при их объединении в матрицу. Слой 2 тонкого (около 20 нм) SiO2 располагался только над n+-областью 11 кремния. Над остальными областями ячейки находился слой 10 толстого (0,5 мкм) диоксида кремния, что позволяло исключить образование инверсных проводящих слоев на поверхности слабо легированных областей полупроводника при подаче управляющих импульсов напряжения, которые могли бы привести к паразитному закорачиванию элементов ячейки памяти. Проводящими шинами первого уровня матрицы (фиг. 3 вид сверху) являются области 8 кремния p-типа, участки которых под эмиттерами выполняют одновременно функцию базы биполярных транзисторов. Проводящие шины второго уровня матрицы 1 перекрещиваются (фиг. 3 вид сверху) с шинами первого уровня. Они выполнены из вольфрама толщиной 0,1-0,12 мкм, а их участки над элементом памяти являются одновременно верхними электродами изолирующих щелей 3. Электрическая изоляция шин 8 p-кремния в матрице друг от друга и от подложки 9 кремния n-типа осуществляется обратно смещенными коллекторными p-n-переходами транзисторов. Для первого варианта ячеек присутствовал слой 4 нитрида титана толщиной 40-50 нм (проводящий слой первого уровня элемента памяти). В этом случае элемент памяти создавался в открытой «сэндвич»-структуре TiN-SiO2-W. На слое TiN 4 располагался дополнительный диэлектрический слой 12 диоксида титана (TiO2) толщиной 2,0-3,0 нм. Для второго варианта ячеек слой из нитрида титана отсутствовал, а роль проводящего слоя первого уровня (нижнего электрода изолирующей щели) играла область высоколегированного n+-кремния 11. Элемент памяти создавался в открытой «сэндвич»-структуре n+-Si-SiO2-W. В этом случае дополнительный диэлектрический слой формировался после изготовления открытой «сэндвич»-структуры за счет образования естественного окисла (SiO2) на поверхности области кремния n+-типа (фиг. 2б). Оба варианта конструкции ячеек располагались на одной кремниевой пластине. В качестве токоподвода к шинам матрицы обоих уровней, к n-подложке, а также для формирования контактных площадок к чипу с матрицей памяти использовались тонкопленочные проводники (на фиг. 3 не показаны) из сплава алюминий-кремний (1% кремния) толщиной 0,5-0,6 мкм.

Ячейки памяти обоих вариантов конструкции изготавливались на одной пластине и в едином технологическом цикле, для формирования открытой «сэндвич»-структуры n+-Si-SiO2-W в соответствующей области слой нитрида титана просто удалялся. В качестве подложки 9 использовались пластины монокристаллического кремния n-типа, легированного фосфором до удельного сопротивления 4,5 Ом⋅см, диаметром 100 мм. Области 8 р-кремния и 11 n+-кремния создавались последовательным локальным (через маску диоксида кремния) легированием исходной подложки сначала бором до слоевого сопротивления 600-900 Ом/□, а затем фосфором до слоевого сопротивления 18-22 Ом/□. Слой 10 толстого диоксида кремния выращивался термическим окислением подложки. Слой 4 нитрида титана осаждался методом реактивного магнетронного распыления титана в атмосфере азота, и в нем методом фотолитографии создавался необходимый рисунок. Затем, непосредственно перед осаждением слоя диоксида кремния в той же вакуумной установке, пластина подвергалась отжигу в среде кислорода, что приводило к окислению нитрида титана и образованию на его поверхности дополнительного диэлектрического слоя 12 (TiO2) нужной толщины (см. ниже). После этого методом реактивного магнетронного распыления кремния в атмосфере кислорода сразу осаждался слой диэлектрика 2 (SiO2) толщиной d 17-23 нм. Изолирующая щель 3 в форме открытого торца слоя диэлектрика 2 формировалась прецизионным жидкостным травлением диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Проводящий слой (и шины) 1 второго уровня создавались магнетронным распылением сплава вольфрам-титан (10% титана). Для обеспечения омического контакта к подложке n-типа при легировании пластин фосфором формировались и соответствующие n+-области. Рисунок во всех слоях создавался методами контактной фотолитографии.

Дополнительный электрический слой 12 на поверхности нижнего проводящего слоя первого уровня 4 (нижнего электрода) из нитрида титана создавался методом его окисления в газообразном кислороде. При этом, как известно, образуется слой диоксида титана (TiO2), а азот удаляется через поверхность в газовую фазу. Окисление проводилось путем проведения предварительного отжига в той же вакуумной установке, в которой в дальнейшем осаждался слой SiO2, и непосредственно перед этим осаждением. Использовались следующие условия отжига. В вакуумную камеру напускались аргон до давления 0,9 Па и кислород с парциальным давлением 0,06 Па. Между кремниевой мишенью и корпусом установки зажигалась высокочастотная плазма, мощность разряда составляла 200 Вт. В таких условиях одновременно происходило распыление мишени, необходимое для ее предварительной очистки (для последующего осаждения диоксида кремния), при этом пластина с изготавливаемыми образцами располагалась на нагреваемом подложкодержателе и была закрыта от мишени механической заслонкой. Толщина образующегося слоя TiO2 варьировалась за счет температуры подложкодержателя (менялась в диапазоне от 300 до 440°С) и времени отжига (менялось в диапазоне от 3 до 12 минут).

Измерение толщины слоя TiO2 выполнялось с использованием предварительных экспериментов, в которых с применением вторично-ионного масс-спектрометра (ВИМС) TOF.SIMS5 снимались профили, в частности, кислородсодержащих ионов по глубине слоя TiN. Начальная толщина слоя нитрида титана на кремнии предварительно контролировалась с помощью механического профилометра, измерявшего высоту ступеньки после локального стравливания слоя, и в дальнейшем использовалась для калибровки (по максимуму кислородсодержащих ионов на границе раздела TiN-Si) глубины полученных профилей ионов (фиг. 4). На фиг. 5 показана методика определения толщины слоя TiO2 по профилю соответствующего иона: толщиной s считалась та глубина от поверхности образца, на которой интенсивность сигнала иона TiO2- падала в 2 раза от значения Imax в максимуме кривой.

При формировании изолирующей щели 3 (открытого торца слоя диэлектрика открытой «сэндвич»-структуры TiN-SiO2-W) слой диоксида кремния 2 удалялся в травителе, содержащем плавиковую кислоту и фтористый аммоний. Скорость растворения SiO2 в таком травителе была на порядок выше, чем скорость растворения TiO2. С учетом точного определения момента стравливания слоя диоксида кремния с использованием методики контроля емкости структуры электролит (травитель) - оставшийся слой SiO2 - слой TiN, специально создававшейся на пластине, это обеспечивало надежную сохранность слоя TiO2, лежавшего ниже, и в дальнейшем использовавшегося в качестве дополнительного диэлектрического слоя 12.

Чипы с матрицами памяти разваривались в металлостеклянные корпуса, которые не герметизировались. В дальнейшем корпуса без крышки помещались в высокий вакуум для последующего выполнения операции электроформовки. Газовая среда, включая кислородсодержащие молекулы, с остаточным давлением около 10-2 Па (высокий вакуум) и была той средой, которая контактировала с поверхностью изолирующей щели и обеспечивала обмен частицами материала с переменной проводимостью.

Операция электроформовки состояла в подаче на открытую «сэндвич»-структуру напряжения в диапазоне от 0 до 10÷12 В по определенному алгоритму. В простейшем, но и наиболее «жестком» варианте, это были треугольные импульсы напряжения, подаваемые на выбираемую ячейку матрицы между слоем вольфрама и р-областью транзистора (минус на W), со скоростью изменения порядка 1 В/с. При этом практически все приложенное напряжение падало на элементе памяти. Невыбираемые ячейки матрицы находились под запирающим обратным напряжением, когда практически все оно падало на обратно смещенном эмиттерном р-n-переходе транзистора, а токи утечки не превышали нескольких наноампер. Одновременно фиксировалась вольтамперная характеристика (ΒΑΧ) для выбираемой ячейки. Электроформовка проводилась с помощью прибора ИППП-1, использовалось ограничение тока на заданном уровне с целью уменьшения вероятности электрического пробоя. В случае успешного выполнения электроформовки ΒΑΧ выглядела так, как показано на фиг. 6. Протекание небольших токов при напряжениях от 5 до 11 В соответствует стадии накопления ЧПФ, а резкое увеличение тока, которое всегда имеет место на обратном ходе напряжения (т.е. возникает N-образная кривая) обычно в диапазоне от 4,5 до 7 В, соответствует образованию проводящей среды и формированию в ней изолирующего зазора нанометровой ширины. Критерием успешности электроформовки является, во-первых, возникновение N-образной ΒΑΧ, и во-вторых, возможность «отключения» (переключения в низкопроводящее состояние с уменьшением токов на 2-4 порядка) возникшего высокопроводящего состояния импульсом напряжения амплитудой до 10 В (длительность отключающего импульса обычно составляла от 0,1 до 1 мкс). На фиг. 7 показана ΒΑΧ, которая возникает в случае электрического пробоя элемента памяти. Резкий скачок тока при этом происходит в диапазоне напряжений от 7 до 11 В (на прямом или обратном ходе напряжения), и возникает состояние с очень высокой проводимостью, которое невозможно отключить импульсом напряжения с любым приемлемым значением амплитуды (вплоть до 14 В). В этом случае элемент памяти не может функционировать, а при протекании слишком больших токов (без ограничения внешними схемами) возникают разрушения открытых «сэндвич»-структур в микрометровом масштабе, которые хорошо видны в микроскоп.

Мог использоваться и другой, более «мягкий», алгоритм выполнения электроформовки. В соответствии с ним ячейка памяти сначала выдерживается при постоянном напряжении около 10 В до начала протекания небольшого тока (порядка 0,5 мкА), затем напряжение резко сбрасывается, и далее подается такой же треугольный импульс напряжения, но с амплитудой 5-6 В. При достижении значения около 4 В (пороговое напряжение образования частиц проводящей фазы) происходит резкое увеличение тока, ячейка переходит в высокопроводящее состояние, которое по-прежнему можно отключить коротким импульсом напряжения амплитудой до 10 В. Поскольку в таком алгоритме исключается экспозиция элемента памяти в наиболее опасном с точки зрения возникновения электрического пробоя диапазоне напряжений (7-11 В), вероятность успешной электроформовки увеличивается приблизительно на порядок.

Результаты выполнения электроформовки для образцов элементов памяти на основе открытой «сэндвич»-структуры TiN-(TiO2)-SiO2-W (она соответствует варианту конструкции на фиг. 2а), изготовленных при различных температурах Τ отжига слоя TiN, а значит, при разных толщинах s слоя TiO2, представлены на фиг. 8. Приведена вероятность  успешной электроформовки, не закончившейся электрическим пробоем элемента памяти. Как видно,

успешной электроформовки, не закончившейся электрическим пробоем элемента памяти. Как видно,  остается высокой при толщинах s, равных 2,5 нм (температура отжига 400°С) и больше, и резко падает при s около 2 нм (температура отжига 350°С). При температурах отжига ниже 350°С (толщинах слоя TiO2, меньших 2 нм), все попытки электроформовки, даже с применением более «мягкого» алгоритма (см. выше), приводят к электрическому пробою, т.е. вероятность

остается высокой при толщинах s, равных 2,5 нм (температура отжига 400°С) и больше, и резко падает при s около 2 нм (температура отжига 350°С). При температурах отжига ниже 350°С (толщинах слоя TiO2, меньших 2 нм), все попытки электроформовки, даже с применением более «мягкого» алгоритма (см. выше), приводят к электрическому пробою, т.е. вероятность  практически равна нулю. Для того чтобы исключить влияние на вероятность электрического пробоя воздействия температуры осаждения слоя SiO2 (и отжига, поскольку эти температуры совпадают) через электрические свойства собственно слоя диоксида кремния, были исследованы образцы, полученные при температуре 350°С, но времени отжига 9 минут, т.е. в 3 раза большем, чем во всех других случаях. При этом толщина s слоя TiO2 составила 2,5 нм («треугольник» на фиг. 8). Видно, что существенным фактором оказывается именно толщина слоя TiO2, а не возможное изменение электрических характеристик слоя SiO2 с изменением температуры. Использование толщин дополнительного диэлектрического слоя TiO2, больших 3 нм, нерационально, поскольку чрезмерное ограничение тока приводит к излишнему замедлению скорости образования ЧПФ, а значит, к замедлению процесса электроформовки.

практически равна нулю. Для того чтобы исключить влияние на вероятность электрического пробоя воздействия температуры осаждения слоя SiO2 (и отжига, поскольку эти температуры совпадают) через электрические свойства собственно слоя диоксида кремния, были исследованы образцы, полученные при температуре 350°С, но времени отжига 9 минут, т.е. в 3 раза большем, чем во всех других случаях. При этом толщина s слоя TiO2 составила 2,5 нм («треугольник» на фиг. 8). Видно, что существенным фактором оказывается именно толщина слоя TiO2, а не возможное изменение электрических характеристик слоя SiO2 с изменением температуры. Использование толщин дополнительного диэлектрического слоя TiO2, больших 3 нм, нерационально, поскольку чрезмерное ограничение тока приводит к излишнему замедлению скорости образования ЧПФ, а значит, к замедлению процесса электроформовки.

Ячейки с элементами памяти в виде открытой «сэндвич»-структуры n+-Si-SiO2-W изготавливались одновременно, на одной кремниевой пластине и в едином технологическом цикле, с ячейками в виде структуры TiN-(TiO2)-SiO2-W. Отличие состояло не только в том, что в первых не было слоя TiN, но и в том, что в них травление слоя диэлектрика (SiO2) при изготовлении изолирующей щели приводило к полному удалению диэлектрического материала с поверхности нижнего электрода (n+-Si). Затем, при хранении образцов в комнатных условиях, происходило окисление поверхности кремния. Толщина такого, «естественного», окисла на n+-Si, образовавшегося после хранения в течение 2 лет, как показало локальное травление (до момента нарушения смачивания образца травителем, что означало открытие чистой поверхности кремния) и измерение высоты ступеньки с помощью профилометра, составляла 1,6±0,6 нм. Профили кислородсодержащих ионов по глубине структуры: нараставший в течение 2 лет в комнатных условиях естественный SiO2 - n+-Si, - снятые с помощью ВИМС, показаны на фиг. 9. Величина s составляла 1,8 нм. Видно, что толщины диоксида кремния, измеренные двумя методами (профилометром и ВИМС), хорошо согласуются между собой. В случае хранения образцов в комнатных условиях в течение 22 дней после изготовления величина s, определенная из графиков, аналогичных фиг. 9, составила 1,3 нм. Операция электроформовки в изготовленных открытых «сэндвич»-структурах n+-Si-SiO2-W выполнялась обычно через 20-180 дней после их изготовления (операции травления слоя SiO2 с целью формирования изолирующей щели) и хранения образцов в комнатных условиях. Таким образом, можно утверждать, что в случае элемента памяти в виде открытой «сэндвич»-структуры n+-Si-SiO2-W реализуется вариант конструкции, соответствующий фиг. 2б, причем всегда, вне зависимости от того, какие технологические режимы обработки кремниевой пластины (при изготовлении структур TiN-(TiO2)-SiO2-W и n+-Si-SiO2-W) были использованы, толщина дополнительного диэлектрического слоя находилась в диапазоне от 1,3 до 1,8 нм. Как показало исследование электроформовки в открытых «сэндвич»-структурах n+-Si-SiO2-W, ее выполнение практически всегда оказывалось успешным, т.е. электрических пробоев в элементах памяти не происходило при любых сроках хранения образцов, больших 20 дней. Это означает, что даже толщины s=1,3 нм дополнительного диэлектрического слоя из SiO2 достаточно для эффективного ограничения токов и предотвращения электрических пробоев, в то время как для слоя из TiO2 требуются толщины более 2,5 нм. Лучшая эффективность слоя из диоксида кремния по сравнению со слоем из диоксида титана связана, очевидно, с более высоким качеством (прежде всего, с меньшей удельной проводимостью) слоя естественного SiO2. Следует подчеркнуть также, что поверхность TiN в комнатных условиях (и вообще, при температурах менее 200°С, которые может выдержать слой вольфрама в среде кислорода) практически не окисляется. Поэтому для элемента памяти в виде открытой «сэндвич»-структуры TiN-SiO2-W, где образование достаточно толстого слоя TiO2 требует нагрева в кислороде до температур выше 400°С, реализация варианта конструкции фиг. 2б требует специальных усилий, например существенного изменения технологического маршрута изготовления ячеек памяти.

Таким образом, приведенные данные демонстрируют для предложенного элемента памяти достижение всех заявленных технических задач.

Предлагаемый элемент энергонезависимой электрически перепрограммируемой памяти апробирован в Ярославском Филиале ФТИАН.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| Способ электроформовки при изготовлении элемента памяти | 2020 |

|

RU2769536C1 |

| ЯЧЕЙКА МАТРИЦЫ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2005 |

|

RU2302058C2 |

| ЯЧЕЙКА МАТРИЦЫ ПАМЯТИ | 2004 |

|

RU2263373C1 |

| ЯЧЕЙКА ПАМЯТИ СО СТРУКТУРОЙ ПРОВОДЯЩИЙ СЛОЙ-ДИЭЛЕКТРИК-ПРОВОДЯЩИЙ СЛОЙ | 2007 |

|

RU2376677C2 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

| СПОСОБ ФОРМИРОВАНИЯ ПРОВОДЯЩЕГО ЭЛЕМЕНТА НАНОМЕТРОВЫХ РАЗМЕРОВ | 2001 |

|

RU2194334C1 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| СПОСОБ ФОРМИРОВАНИЯ МНОГОУРОВНЕВЫХ МЕДНЫХ МЕЖСОЕДИНЕНИЙ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ С ИСПОЛЬЗОВАНИЕМ ВОЛЬФРАМОВОЙ ЖЕСТКОЙ МАСКИ | 2013 |

|

RU2523064C1 |

Использование: для создания элемента памяти. Сущность изобретения заключается в том, что элемент памяти включает проводящие слои первого и второго уровня, расположенный между ними и непосредственно под проводящим слоем второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью, между изолирующей щелью и проводящим слоем первого уровня расположен дополнительный диэлектрический слой толщиной от 1,3 до 3 нм. Технический результат: обеспечение возможности уменьшения вероятности электрического пробоя элемента памяти. 2.з.п. ф-лы, 9 ил.

1. Элемент памяти, включающий проводящие слои первого и второго уровня, расположенный между ними и непосредственно под проводящим слоем второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью, отличающийся тем, что между изолирующей щелью и проводящим слоем первого уровня расположен дополнительный диэлектрический слой толщиной от 1,3 до 3 нм.

2. Элемент памяти по п. 1, отличающийся тем, что дополнительный диэлектрический слой выполнен из оксида материала проводящего слоя первого уровня.

3. Элемент памяти по п. 1, отличающийся тем, что слой диэлектрика и дополнительный диэлектрический слой выполнены из различных материалов.

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032945C1 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

| ЯЧЕЙКА МАТРИЦЫ ПАМЯТИ | 2004 |

|

RU2263373C1 |

| ЯЧЕЙКА МАТРИЦЫ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2005 |

|

RU2302058C2 |

| KR 2013015694 A, 14.02.2013. | |||

Авторы

Даты

2017-11-30—Публикация

2016-03-25—Подача