Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии.

Известен элемент устройства энергонезависимой электрически перепрограммируемой памяти со структурой металл-изолятор-металл (Мордвинцев В.М., Левин В.Л. Элемент устройства памяти со структурой металл-изолятор-металл // Патент РФ, №2072591, 1997), который включает металлический электрод первого уровня, расположенный на изолирующей подложке, металлический электрод второго уровня, разделяющий электроды двух уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания электродов первого и краев электрода второго уровней, находящийся в изолирующей щели углеродистый активный материал, проводимость которого меняется при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую поступление исходного углеродсодержащего (органического) материала и возможность удаления частиц углеродистого материала с поверхности изолирующей щели. В случае подачи на металлические электроды достаточного напряжения и прохождения через изолирующую щель электрического тока из органического вещества за счет деструкции его молекул при электронном ударе образуется углеродистый активный материал (процесс электроформовки), проводимость которого меняется в широких пределах в зависимости от его состава и структуры, зависящих от значений тока и прошедшего заряда. При этом элемент может переводиться в высокопроводящее состояние. Подача импульса напряжения большей амплитуды приводит к термическому удалению образовавшегося углеродистого проводящего материала и переводу элемента в низкопроводящее состояние. Оба состояния сохраняются неограниченно долго при отключенном питании, и переключения между ними возможны многократно. Такой элемент может служить основой для построения устройства энергонезависимой электрически перепрограммируемой памяти.

Предложена (Валиев К.А., Кудрявцев С.Е., Левин В.Л., Мордвинцев В.М., Савасин В.Л. Память на основе нано-МИМ-диода с углеродистой активной средой II Микроэлектроника. 1997. Т.26. №1. С.3-11) конструкция элементов матрицы энергонезависимой электрически перепрограммируемой памяти на базе описанных выше элементов. Соответствующий элемент матрицы памяти включает металлическую (проводящую) шину первого уровня, расположенную на подложке, электрически изолирующей ее от других металлических шин первого уровня матрицы, перекрещивающуюся с ней металлическую шину второго уровня, разделяющий шины двух (первого и второго) уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели углеродистый активный материал, проводимость которого меняется при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую поступление исходного углеродсодержащего (органического) материала и возможность удаления частиц углеродистого материала с поверхности изолирующей щели (обмен частицами материала с переменной проводимостью). В случае подачи между металлическими шинами электрического напряжения и прохождения через изолирующую щель электрического тока за счет деструкции молекул органического вещества при электронном ударе образуется углеродистый активный материал и в нем в результате процесса самоорганизации (самоформирования) формируется изолирующий зазор шириной несколько нанометров (процесс электроформовки), которая зависит от приложенного напряжения. Проводимость элемента определяется шириной изолирующего зазора и поэтому может меняться в широких пределах в зависимости от напряжения между шинами. При этом элемент памяти при отключенном питании находится либо в низко-, либо в высокопроводящем состоянии, а переключения между ними возможны за счет подачи импульсов напряжения различной амплитуды. Недостатком таких элементов памяти является невозможность прямого объединения их в матрицу. Для функционирования матрицы памяти каждая ячейка должна быть электрически развязана с другими ячейками, чтобы была обеспечена возможность ее независимой выборки при считывании и записи информации. Это может быть реализовано, например, для ячеек, каждая из которых имеет выпрямляющую вольт-амперную характеристику (ВАХ). Но ВАХ элемента памяти со структурой металл - изолятор - металл практически симметрична.

Предложена ячейка матрицы памяти (см. RU 2004100899, опубликованная 20.06.2005), включающая проводящую шину первого уровня, выполненную из полупроводника р- или n-типа, расположенную на подложке, электрически изолирующей ее от других проводящих шин первого уровня матрицы, перекрещивающуюся с ней проводящую шину второго уровня, разделяющий шины первого и второго уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью. При этом ячейка обладает и свойствами элемента энергонезависимой электрически перепрограммируемой памяти и выпрямляющими свойствами с характеристиками, обеспечивающими электрическую развязку ячейки в матрице. Это обеспечивается тем, что в областях перекрещивания шин первого и краев шин второго уровней после подачи между ними напряжения и выполнения электроформовки (накопления проводящего материала в изолирующей щели и самоформирования в нем изолирующего зазора) формируется интегральный прибор, имеющий структуру: металлическая шина - проводящий материал, образовавшийся в изолирующей щели, с изолирующим зазором - полупроводник, которая аналогична структуре барьера Шоттки с переменной шириной нанометрового изолирующего зазора между проводящим электродом и полупроводником. По совокупности признаков эта ячейка матрицы памяти наиболее близка к предлагаемым техническим решениям.

Такая ячейка имеет следующие недостатки. Во-первых, это плохие выпрямляющие характеристики (низкие напряжения пробоя и большие обратные токи), что связано с повышенной локальной напряженностью электрического поля в обедненном поверхностном слое полупроводника шины первого уровня из-за малого радиуса кривизны области проводящего материала в изолирующей щели. Во-вторых, это возможность существенной нестабильности электрических характеристик ячейки, что связано с наличием открытых в газовую среду (незащищенных) участков поверхности слаболегированного полупроводника (р- или n-типа) шины первого уровня вблизи изолирующей щели, на которых может происходить образование поверхностных состояний и неконтролируемое накопление заряда. В-третьих, это большие токи, которые протекают по полупроводниковым шинам первого уровня, сопротивление которых принципиально нельзя сделать таким же низким, как для металлических проводящих шин второго уровня, что из-за значительных падений напряжения на них ограничивает максимальную размерность матрицы по координате вдоль шин первого уровня.

В предлагаемой ячейке матрицы памяти, включающей проводящую шину первого уровня, выполненную из полупроводника р- или n-типа, расположенную на подложке, электрически изолирующей ее от других проводящих шин первого уровня матрицы, перекрещивающуюся с ней проводящую шину второго уровня, расположенный под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью, в отличие от известной ячейки, между слоем диэлектрика и шиной первого уровня под изолирующей щелью расположен слой с высокой концентрацией носителей тока из полупроводника n+ или р+-типа, противоположного типу полупроводника шины первого уровня, а его размеры в плоскости подложки таковы, что не нарушается электрическая изоляция шин первого уровня матрицы друг от друга.

Достигаемые при этом технические результаты состоят в следующем. Во-первых, улучшаются выпрямляющие свойства ячейки, в частности, увеличивается напряжение пробоя и уменьшаются обратные токи. Это происходит из-за того, что при обратном напряжении на ячейке переход "проводящий материал в изолирующей щели с нанометровым изолирующим зазором - слой из полупроводника с высокой концентрацией носителей тока" смещается в прямом направлении и локальное падение напряжения электрического поля в поверхностном слое полупроводника практически отсутствует. Почти все приложенное напряжение падает на обратно смещенном р-n-переходе, образованном между слоем из полупроводника с высокой концентрацией носителей тока и полупроводниковой шиной первого уровня, р-n-переход имеет обычную пространственно распределенную форму, что исключает локальное усиление напряженности электрического поля в обедненном слое, характерное для прототипа, поэтому могут обеспечиваться высокие напряжения пробоя и малые обратные токи. При прямом напряжении на ячейке, как показали эксперименты, несмотря на обратное смещение перехода "проводящий материал в изолирующей щели с нанометровым изолирующим зазором - слой из полупроводника с высокой концентрацией носителей тока", эффекты переключений и памяти работают обычным образом. Такой технический результат решает следующие задачи. Уменьшение обратных токов позволяет увеличить допустимое количество ячеек в матрице, что увеличивает плотность записи информации. А повышение напряжения пробоя позволяет увеличить скорость записи информации на несколько порядков, поскольку индивидуальная выборка ячейки становится возможной при больших напряжениях, подаваемых на нее, а значит, для записи можно использовать более быстрый процесс переключения элемента памяти из высокопроводящего в низкопроводящее состояние. Во-вторых, уменьшается нестабильность электрических характеристик ячейки, что связано с тем, что участки поверхности слаболегированного полупроводника (р- или n-типа) шины первого уровня вблизи изолирующей щели закрываются от контакта с газовой средой слоем из полупроводника с высокой концентрацией носителей тока (n+- или р+-типа), электрическая активность поверхности которого не влияет на свойства нижележащих слоев из-за малой глубины проникновения электрического поля в полупроводник с высокой концентрацией носителей. Наряду с достижением всех этих результатов предложенные технические решения позволяют площадь ячейки памяти в сравнении с прототипом увеличить незначительно, а негативное влияние последнего фактора на плотность записи информации в устройстве памяти в целом будет с избытком компенсировано возможностью увеличения количества ячеек в матрице.

Кроме того, подложка, изолирующая проводящую шину первого уровня от других проводящих шин первого уровня матрицы, выполнена из полупроводника n- или р-типа, противоположного типу полупроводника шины первого уровня.

Достигаемый при этом технический результат состоит в уменьшении на несколько порядков токов, протекающих по полупроводниковым шинам первого уровня, что связано с возникновением транзисторного эффекта в структуре: слой с высокой концентрацией носителей тока из полупроводника n+- или р+-типа (эмиттер) - шина первого уровня из полупроводника р- или n-типа (база) - подложка из полупроводника n- или р-типа (коллектор), и почти весь ток из проводящей шины второго уровня, проходя узкий участок базы под изолирующей щелью, сразу попадает в подложку, в которой эффективно растекается. Изоляция шин первого уровня друг от друга обеспечивается обедненным слоем коллекторного р-n-перехода, который располагается, в основном, в материале подложки. Такой технический результат позволяет увеличить размерность матрицы вдоль длины шины первого уровня и, тем самым, увеличить объем и плотность записи информации.

В источниках информации не обнаружено сведений, аналогичных предложенной ячейке матрицы памяти, что позволяет сделать вывод о ее новизне.

Кроме того, предлагаемое устройство для специалиста явным образом не следует из уровня техники, что подтверждает соответствие предлагаемого технического решения критерию "изобретательский уровень".

Обоснование предлагаемого устройства вместе со сведениями, подтверждающими возможность его осуществления, приводится ниже с использованием графических материалов.

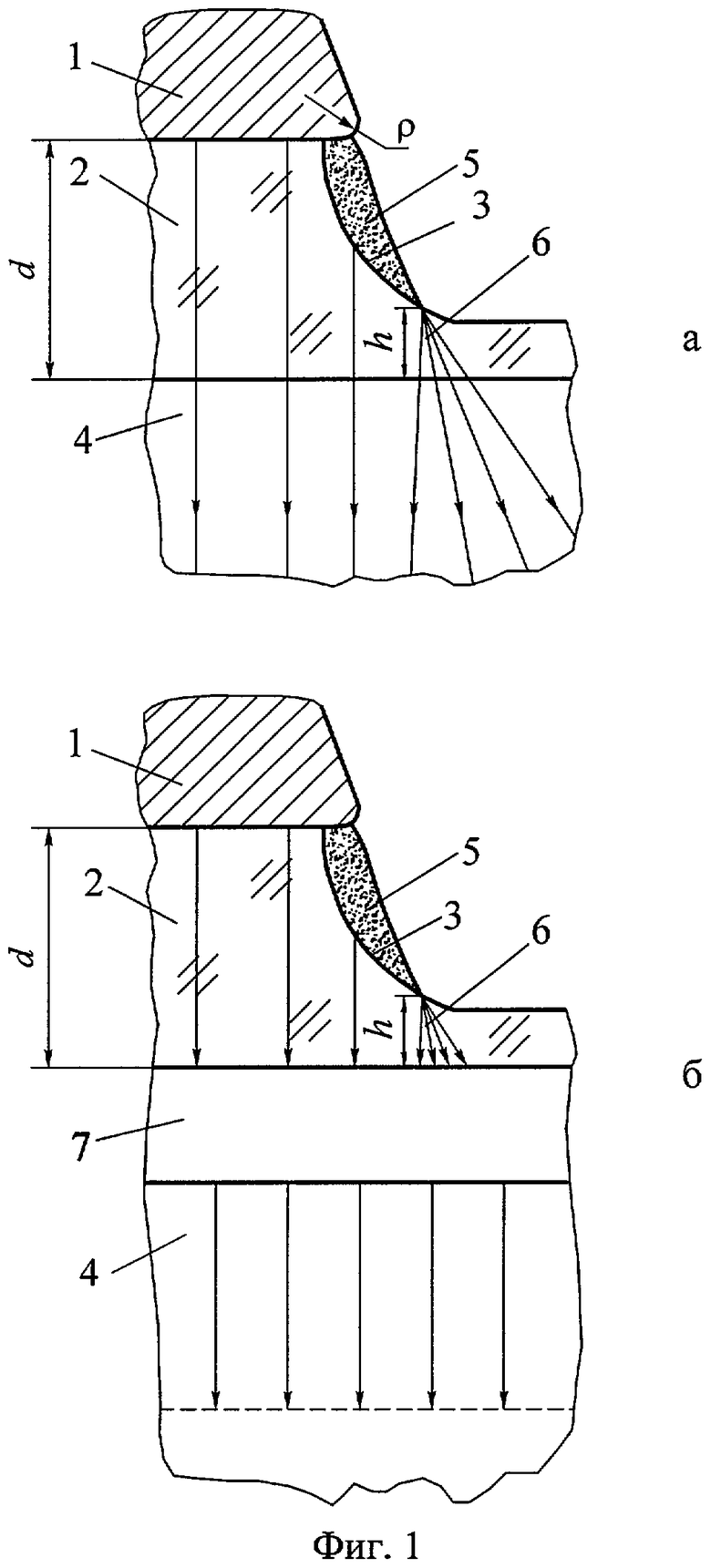

На фиг.1 показано схематичное изображение поперечных сечений фрагмента ячейки матрицы памяти, включающего изолирующую щель после выполнения электроформовки: (а) - для прототипа, (б) - для предлагаемой ячейки. 1 - проводящая (металлическая) шина второго уровня, 2 - слой диэлектрика (SiO2) толщиной d=3 - 100 нм, расположенный под шиной второго уровня, 3 - изолирующая щель в форме открытого торца слоя диэлектрика, 4 - проводящая шина первого уровня из полупроводника р-типа (кремний), 5 - материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, находящийся в проводящем состоянии (проводящий материал), 6 - самосформировавшийся изолирующий зазор переменной нанометровой ширины h, заполненный диоксидом кремния (остаточный диэлектрик), 7 - слой с высокой концентрацией носителей тока из полупроводника n+-типа (кремния). Показаны также силовые линии электрического поля при обратной полярности на ячейках.

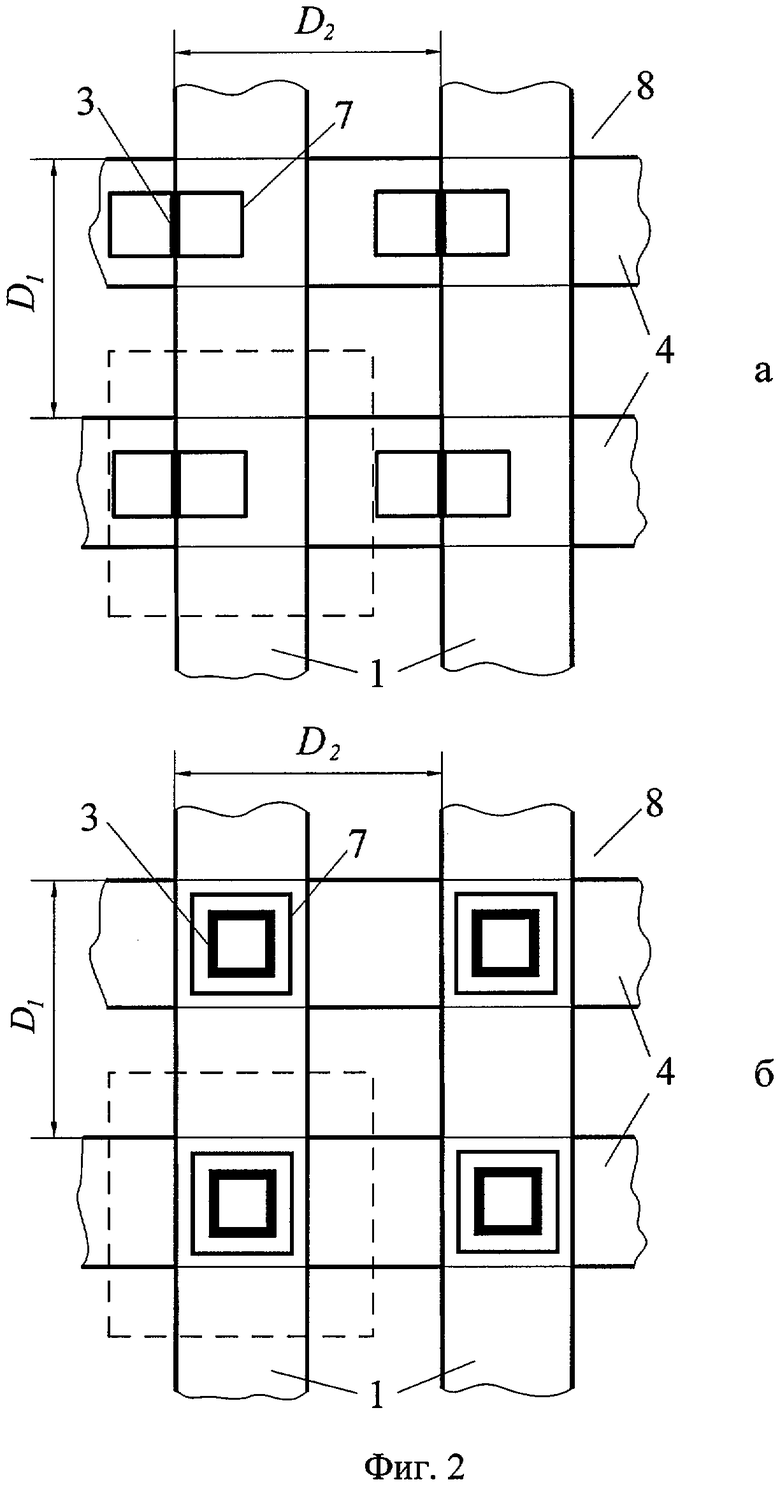

На фиг.2 схематично показаны фрагменты матрицы памяти в плане (топология). Форма периметра открытого торца диэлектрической пленки: а - по внешнему краю проводящей шины второго уровня, б - внутри области перекрещивания проводящих шин двух уровней. 1 - проводящие (металлические) шины второго уровня, 3 - открытые торцы слоя диэлектрика (изолирующие щели), 4 - проводящие шины первого уровня (полупроводник р-типа), 7 - слой с высокой концентрацией носителей тока из полупроводника n+-типа, 8 - подложка, электрически изолирующая друг от друга проводящие шины первого уровня матрицы. Пунктиром выделена ячейка матрицы памяти.

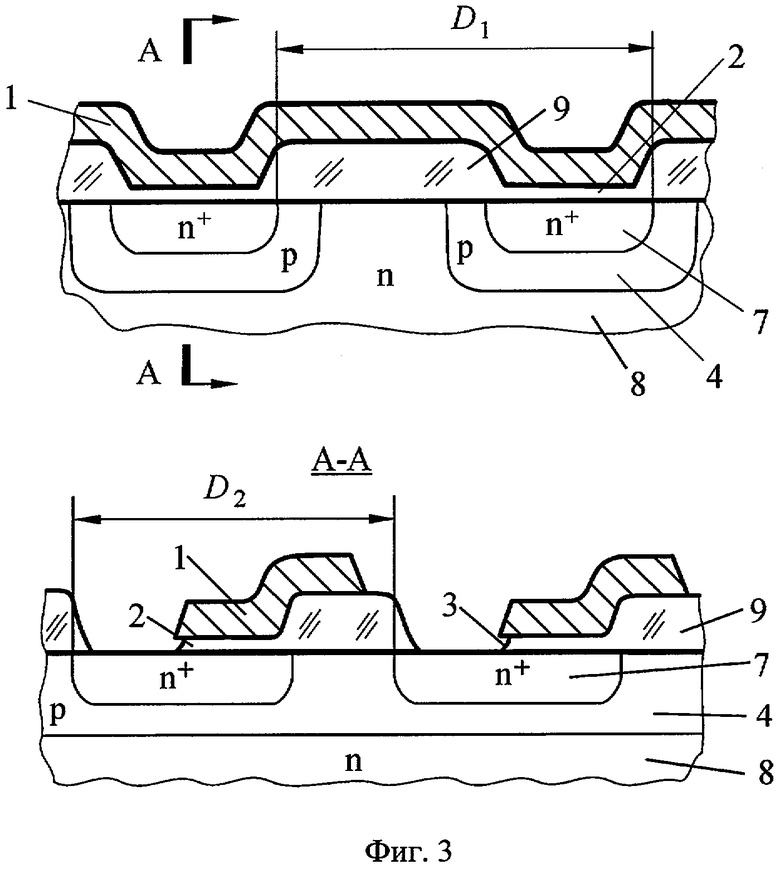

На фиг.3 приведены поперечные сечения фрагмента матрицы памяти для варианта топологии фиг.2,а при использовании в качестве подложки, изолирующей шины первого уровня друг от друга, полупроводника n-типа проводимости. 1 - проводящая (металлическая) шина второго уровня, 2 - слой тонкого диэлектрика (SiO2), расположенный под шиной второго уровня, 3 - изолирующие щели в форме открытого торца слоя тонкого диэлектрика, 4 - проводящие шины первого уровня из полупроводника (кремния) р-типа, 7 - слой с высокой концентрацией носителей тока из полупроводника (кремния) n+-типа, 8 - подложка из полупроводника (кремния) n-типа проводимости, 9 - слой толстого диэлектрика (SiO2) над областями полупроводника р- и n-типа.

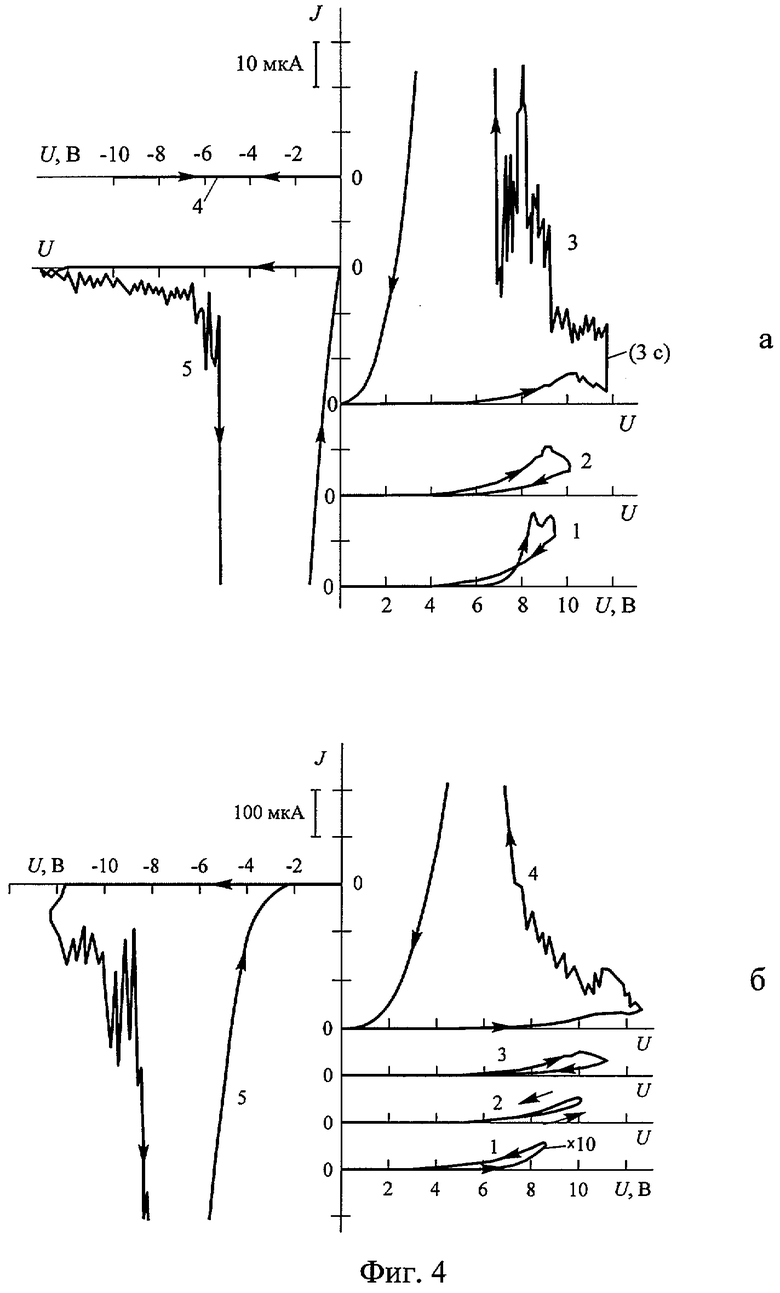

На фиг.4 показаны ВАХ, отражающие процесс электроформовки в ячейках, имеющих слой с высокой концентрацией носителей тока из кремния различного типа проводимости: (а) - n+-типа, с концентрацией фосфора 8·1019 см-3; (б) - р+-типа, с концентрацией бора 1,2·1019 см-3. Толщина тонкого слоя SiO2, расположенного под шиной второго уровня - 17-19 нм. Периметр открытого торца (длина изолирующей щели) - 32 мкм. Скорость развертки напряжения 0,5 В/с. Электроформовка выполнялась для обеих полярностей напряжения U между n+-слоем и металлической шиной (положительные значения U соответствуют минусу на металле) на разных структурах. Порядок проходов: для (а) 1 - первый, 2 - второй, 3 - третий, 4 - первый, 5 - второй; для (б) 1 - первый, 2 - второй, 3 - третий, 4 - четвертый, 5 - первый.

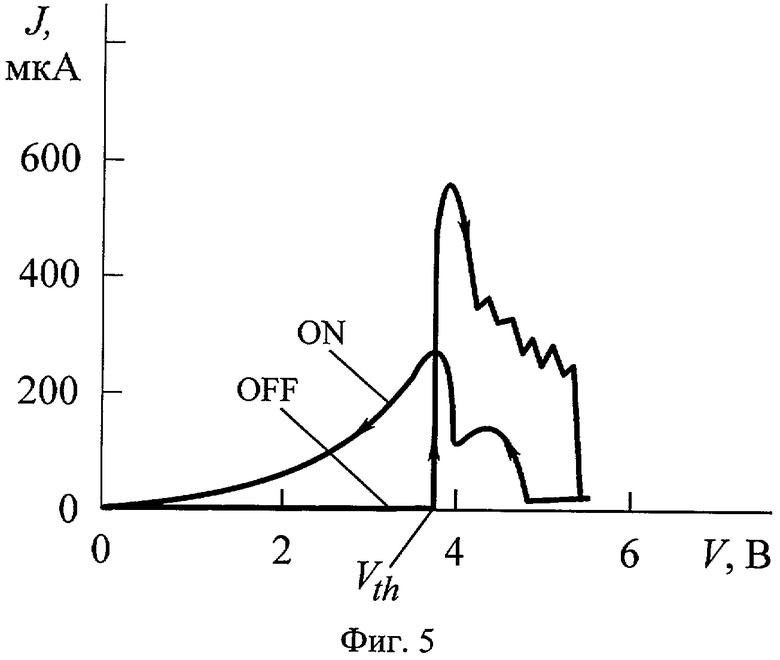

На фиг.5. приведены квазистатические ВАХ ячейки, имеющей слой с высокой концентрацией носителей тока из кремния n-типа (концентрация фосфора 8·1019 см-3), для тока J в цепи металлической шины и напряжений V между шиной р-кремния и металлической шиной прямой полярности (минус на металлической шине) после выполнения электроформовки, иллюстрирующие эффекты переключения и памяти. Периметр открытого торца 32 мкм. Скорость изменения напряжения 0,5 В/с.

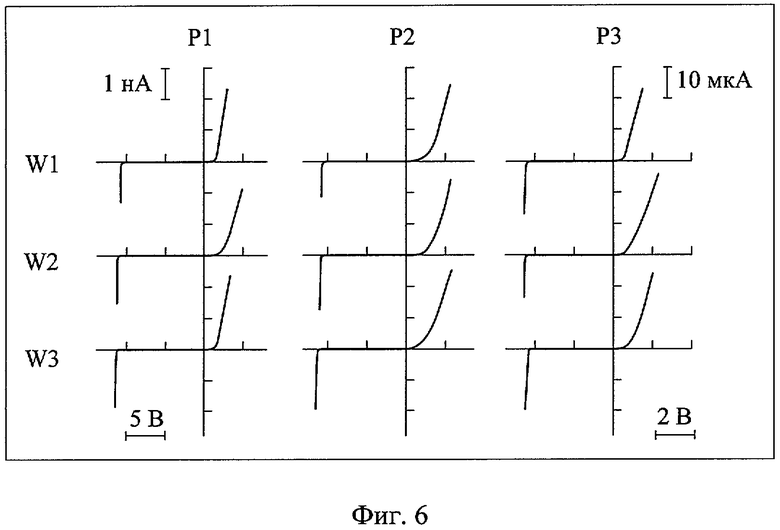

На фиг.6 приведены ВАХ 9 ячеек, имеющих слой с высокой концентрацией носителей тока из кремния n+-типа (концентрация фосфора 8·1019 см-3), для конкретного экспериментального образца матрицы памяти (3×3 ячейки), соответствующие начальному состоянию после ее изготовления и выполнения электроформовки (состояние ON). Измерялся ток в металлической шине в зависимости от напряжения между шинами p-Si и металла. Масштабы по осям для обратной полярности приведены слева, для прямой - справа. Толщина тонкого диоксида кремния - 16 нм. Периметр открытого торца - 32 мкм.

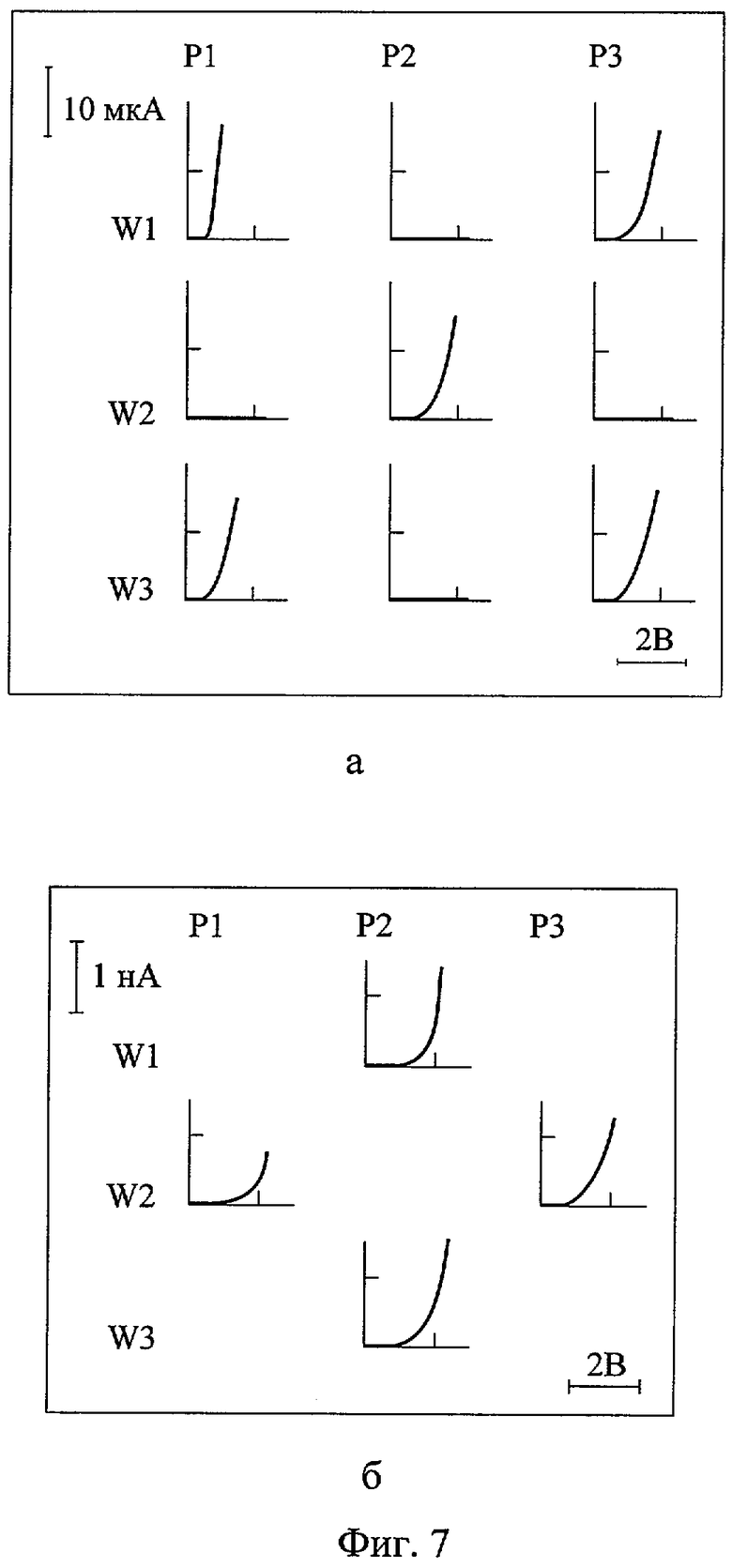

На фиг.7 приведены ВАХ ячеек матрицы для того же экспериментального образца матрицы памяти, после выполнения операции "запись", а - в диапазоне больших токов (для всех 9 ячеек), б - в диапазоне малых токов (для 4 элементов, переключенных в состояние OFF).

Изолирующая щель 3 (фиг.1) в форме торца слоя диэлектрика 2 создается путем локального травления металлической пленки проводящей шины 1 второго уровня и диэлектрической пленки 2. При этом ширина изолирующей щели определяется толщиной d диэлектрической пленки.

После подачи электрического напряжения между проводящими шинами второго 1 и первого 4 уровней и выполнения электроформовки в изолирующей щели 3 образуется проводящий материал 5, который может занимать часть или весь периметр открытого торца. Формирование проводящего материала (материала с переменной проводимостью) происходит из-за деструкции молекул исходно диэлектрического вещества на поверхности изолирующей щели за счет электронного удара при прохождении потока электронов и приложенном напряжении, большем некоторого порогового значения Ufr≈2÷3 В, что приводит к образованию частиц проводящей фазы. В оптимальных условиях электроформовки электроны эмитируются с катода, функцию которого выполняет край проводящей шины 1 второго уровня, с малым радиусом кривизны ρ, что облегчает процесс эмиссии.

В качестве исходного вещества для образования находящегося в изолирующей щели материала с переменной проводимостью, меняющейся при прохождении через него потока электронов, могут служить, например, адсорбированные на поверхности изолирующей щели из газовой фазы органические молекулы, либо собственно диэлектрик поверхности изолирующей щели. В первом случае электроформовка приводит к разложению органического вещества и образованию материала, обогащенного углеродом (углеродистого проводящего материала), а средой над поверхностью изолирующей щели, обеспечивающей обмен частицами материала с переменной проводимостью, является газовая фаза, содержащая органические молекулы. При этом она обеспечивает как поступление новых органических молекул, так и удаление с поверхности продуктов реакции. Во втором случае частицы проводящей фазы образуются за счет разложения диэлектрического материала, например, аморфного оксида металла, поверхности изолирующей щели. При этом средой над ней может быть просто вакуум, что обеспечивает удаление продуктов реакции в виде избыточного кислорода, а поверхностный материал обогащается атомами металла, что и ведет к увеличению его проводимости. В случае диоксида кремния поверхность изолирующей щели обогащается атомами кремния. Существенно, что изолирующая щель должна быть открыта для обмена молекулами вещества со средой.

При выполнении электроформовки происходит образование проводящего материала 5 в изолирующей щели 3 и автоматическое, т.е. за счет самоформирования, определяемого балансом процессов накопления и удаления частиц проводящего материала, установление ширины h изолирующего зазора 6. Равновесное значение h составляет несколько нанометров, оно определяет величину проводимости структуры и само зависит от приложенного напряжения, что и позволяет электрически переключать состояние элемента. Фактически, из-за пологого профиля травления тонкой пленки SiO2, этот зазор оказывается заполненным оставшимся диоксидом кремния (остаточный диэлектрик 6). Проводящий материал, располагающийся вдоль поверхности изолирующей щели, имеет форму "нанолезвия", упирающегося в поверхность кремния (через остаточный диэлектрик), т.е. радиус кривизны в его нижней части очень мал.

На фиг.1 условно показаны также силовые линии электрического поля в случае приложения к ячейке напряжения обратной полярности ("плюс" на металлической шине второго уровня). В прототипе (фиг.1,а) электрическое поле проникает в обедненный поверхностный слой полупроводника шины первого уровня, причем под "нанолезвием" проводящего материала из-за его малого радиуса кривизны, что является неустранимым фактором, происходит локальное усиление напряженности поля. Это приводит к уменьшению напряжения пробоя обедненного слоя полупроводника и увеличению обратных токов. В частности, при приемлемых концентрациях бора в кремниевой шине первого уровня не удается получить напряжения пробоя более 4 В. В предлагаемой ячейке (фиг.1,б) при обратной полярности напряжения переход "проводящий материал в изолирующей щели с нанометровым изолирующим зазором - слой из полупроводника с высокой концентрацией носителей тока (n+-Si)" смещается в прямом направлении и локальное падение напряжения электрического поля в поверхностном слое полупроводника практически отсутствует. Почти все (за исключением падения напряжения на нанометровом изолирующем зазоре) приложенное напряжение падает на обратно смещенном р-n-переходе, образованном между слоем из n+-кремния и полупроводниковой шиной первого уровня (p-Si). р-n-переход имеет обычную для получаемого легированием n+-слоя пространственно распределенную форму, что исключает локальное усиление напряженности электрического поля в обедненном слое, как это принципиально имеет место для прототипа. Поэтому подбором концентрации примеси в р-кремнии можно обеспечить достаточно высокие напряжения пробоя и малые обратные токи ячейки.

При прямом напряжении на ячейке обедненный слой в р-n-переходе отсутствует, однако переход "проводящий материал в изолирующей щели с нанометровым изолирующим зазором - слой из полупроводника с высокой концентрацией носителей тока" смещается в запирающем направлении. Из-за высокой концентрации носителей в n+-слое ширина обедненного слоя в нем будет очень малой, однако она может быть сравнимой с шириной нанометрового изолирующего зазора 6 (1-4 нм), поэтому нельзя было без соответствующих экспериментов предсказать, как будет проходить в таких структурах процесс электроформовки и будут ли работать эффекты переключений и памяти. Приведенные ниже результаты демонстрируют, что в таких условиях процесс электроформовки, несмотря на некоторые количественные отличия, качественно протекает так же, как и при антизапирающей полярности напряжения, а эффекты переключения и памяти работают обычным образом, что позволяет нормально функционировать предлагаемой структуре в качестве ячейки памяти. Это справедливо для слоев полупроводника и n+- и р+-типа, под которыми, как принято, понимаются слои с концентрацией легирующей примеси, в случае кремния, большей 1019 см-3.

Одним из результатов увеличения напряжения пробоя ячейки является возможность увеличения на несколько порядков скорости записи информации в ячейку. В прототипе, где напряжение пробоя лежит в диапазоне 2-4 В, для записи можно использовать, поскольку при этом необходим индивидуальный доступ к каждой ячейке матрицы, только относительно медленный (сотни микросекунд) процесс переключения элемента памяти из низкопроводящего состояния (OFF) в высокопроводящее (ON), который возможен при амплитуде импульса напряжения всего 5 В. Обратный относительно быстрый процесс переключения из ON в OFF (десятки наносекунд) требует амплитуд 8-10 В, поэтому при напряжении пробоя 2-4 В индивидуальная выборка ячейки невозможна. В предлагаемой ячейке напряжение пробоя легко может быть получено более 10 В, и это ограничение снимается.

Уменьшение на несколько порядков обратного тока ячейки позволяет пропорционально увеличить количество ячеек в матрице. Это связано с тем, что при выборке одной ячейки обратные токи других ячеек суммируются, и этот паразитный ток мешает различению состояний ON и OFF при считывании ее состояния. В свою очередь увеличение количества ячеек в матрице позволяет увеличить плотность записи информации на чипе в целом, поскольку уменьшает долю площади чипа, занятую вспомогательными схемами.

Открытость изолирующей щели в атмосферу является принципиальной особенностью конструкции элемента памяти. В прототипе одновременно открытой при этом оказывается (фиг.1,а) и часть поверхности низколегированного полупроводника (р- или n-типа) шины первого уровня рядом с изолирующей щелью. Из-за низкой проводимости полупроводника электрическая активность открытой его поверхности приводит к нестабильности объемных свойств и характеристик ячейки в целом. В предлагаемой ячейке памяти поверхность шины первого уровня вблизи изолирующей щели закрывается от контакта с газовой средой слоем из полупроводника с высокой концентрацией носителей тока (n+- или р+-типа), электрическая активность поверхности которого не влияет на свойства нижележащих слоев из-за малой глубины проникновения электрического поля в полупроводник с высокой концентрацией носителей. Это увеличивает стабильность электрических характеристик ячейки.

Фрагменты матрицы памяти в плане приведены на фиг.2. Выполнение требования к размерам n+-слоя 7 в плоскости подложки, чтобы не нарушалась электрическая изоляция шин первого уровня матрицы друг от друга, в данном случае обеспечивается тем, что он целиком находится внутри полупроводниковой р-шины 4. Это принципиально для случая выполнения подложки 8 из полупроводника n-типа, поскольку, если бы слой 7 выходил за пределы шины 4, n+-слои ячеек, находящиеся на различных шинах первого уровня матрицы, оказывались бы закороченными через подложку 8, а значит, нарушилась бы и изоляция шин первого уровня. В случае диэлектрической подложки n+-слой может выходить и за пределы р-шины, однако он не должен соединяться с соседней шиной первого уровня, либо с ее n+-слоем. При этом для некоторой специальной организации матрицы слой с высокой проводимостью может быть единым для нескольких соседних ячеек по шине первого уровня, что может уменьшить среднюю площадь ячейки, однако в общем случае он должен быть отдельным для каждой ячейки, как это показано на фиг.2. Открытые торцы 3 диэлектрической пленки, разделяющей проводящие шины двух уровней, могут формироваться по внешним краям шины второго уровня (фиг.2,а) либо внутри области перекрещивания проводящих шин двух уровней (фиг.2,б). В первом случае могут быть обеспечены наименьшие размеры (D1 и D2) ячейки матрицы и минимальная длина изолирующей щели, а значит, минимальные рабочие токи через ячейку. Во втором - ячейка обладает большей симметрией.

Если подложку, изолирующую проводящую р-шину первого уровня от других проводящих шин первого уровня матрицы, выполнить из полупроводника n-типа, т.е. противоположного типу полупроводника шины первого уровня, то в образовавшейся структуре: слой с высокой концентрацией носителей тока из полупроводника n+-типа (эмиттер) - шина первого уровня из полупроводника р-типа (база) - подложка из полупроводника n-типа (коллектор), можно обеспечить транзисторный эффект. Он проявляется в том, что почти весь ток из проводящей шины второго уровня, проходя эмиттер и узкий участок базы под изолирующей щелью, сразу попадает в подложку, в которой эффективно растекается. При этом ток, протекающий по полупроводниковым шинам первого уровня, уменьшается на несколько порядков (пропорционально коэффициенту передачи тока транзисторной структуры). Поперечное сечение фрагмента матрицы с такой конструкцией ячейки показано на фиг.3. Изоляция шин первого уровня 4 друг от друга обеспечивается обедненным слоем коллекторного р-n-перехода (р-шина - n-подложка), который из-за асимметричности перехода располагается, в основном, в материале подложки. Для исключения образования инверсных слоев на поверхности р-шины и n-подложки под шиной второго уровня, которые при определенных напряжениях на шинах ячейки могут приводить к закорачиванию элементов транзисторных структур, под соответствующими участками шины второго уровня расположен толстый (порядка десятых долей микрометра) диоксид кремния 9. Этот элемент конструкции может быть изготовлен и сразу в составе исходной подложки. Уменьшение токов в полупроводниковых шинах первого уровня позволяет решить проблему ограничения размерности матрицы вдоль этих шин, связанную с высоким удельным сопротивлением полупроводника и возникающими поэтому значительными падениями напряжения на шинах при больших токах. Поскольку коэффициент передачи тока в транзисторной структуре можно легко сделать порядка 102-103, то увеличение размера матрицы тоже составит несколько порядков.

Показанная на фиг.3 конструкция ячейки обеспечивает максимально простую технологию ее изготовления: р-шины и n+-слой могут быть сформированы последовательным локальным легированием исходной подложки сначала бором (формирование р-шин), а затем фосфором (формирование n+-слоя), все слои SiO2 могут быть выращены термическим окислением кремния исходной подложки. По этой технологии были изготовлены экспериментальные образцы матрицы памяти размерностью 3×3 (9 ячеек) с вариантом топологии в плане, показанном на фиг.2,б и конструкцией, аналогичной фиг.3. Рисунок во всех слоях создавался методами контактной фотолитографии. Размеры ячейки памяти составляли D1=D2=40 мкм, что было связано с необходимостью минимизировать все второстепенные технологические проблемы. При этом периметр открытого торца ячейки составлял 32 мкм. В качестве подложки 7 использовались пластины монокристаллического кремния n-типа, легированного фосфором до удельного сопротивления 4,5 Ом·см, диаметром 100 мм. Проводящие шины 4 первого уровня формировались путем диффузии бора через маску SiO2 до удельного слоевого сопротивления 500-700 Ом/ , а слоя 7 с высокой концентрацией носителей тока - диффузией фосфора, содержание которого варьировалось в диапазоне 1019-2·1020 см-3. В случае структур p+-n-p использовалась подложка р-кремния, легированного бором до удельного сопротивления 10 Ом·см, а порядок диффузий был обратный. В качестве толстого 9 (0,3-0,5 мкм) и тонкого 2 (17-19 нм) диэлектрика использовался термически выращенный диоксид кремния. Проводящие шины 1 второго уровня создавались из тонкой пленки сплава вольфрам-титан (10% титана) толщиной 0,12 мкм со слоевым сопротивлением около 9 Ом/

, а слоя 7 с высокой концентрацией носителей тока - диффузией фосфора, содержание которого варьировалось в диапазоне 1019-2·1020 см-3. В случае структур p+-n-p использовалась подложка р-кремния, легированного бором до удельного сопротивления 10 Ом·см, а порядок диффузий был обратный. В качестве толстого 9 (0,3-0,5 мкм) и тонкого 2 (17-19 нм) диэлектрика использовался термически выращенный диоксид кремния. Проводящие шины 1 второго уровня создавались из тонкой пленки сплава вольфрам-титан (10% титана) толщиной 0,12 мкм со слоевым сопротивлением около 9 Ом/ . Изолирующие щели 3 формировались прецизионным жидкостным травлением тонкого слоя диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Для обеспечения омического контакта к подложке n-типа диффузией фосфора формировались n+-области. В качестве токоподвода как к р-шинам, так и к n-подложке использовались тонкопленочные проводники из сплава алюминий-кремний (1% кремния). Чипы, содержащие экспериментальные образцы матрицы памяти, разваривались в металлостеклянные корпуса, которые герметизировались в контролируемом вакууме. Остаточный вакуум (1-10 Па) в корпусе и был той средой над поверхностью изолирующей щели, которая обеспечивала обмен частицами материала с переменной проводимостью. В качестве последнего использовались поверхностные слои диоксида кремния изолирующей щели 3, в которых могло меняться содержание кислорода, что соответственно приводило к увеличению концентрации кремния.

. Изолирующие щели 3 формировались прецизионным жидкостным травлением тонкого слоя диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Для обеспечения омического контакта к подложке n-типа диффузией фосфора формировались n+-области. В качестве токоподвода как к р-шинам, так и к n-подложке использовались тонкопленочные проводники из сплава алюминий-кремний (1% кремния). Чипы, содержащие экспериментальные образцы матрицы памяти, разваривались в металлостеклянные корпуса, которые герметизировались в контролируемом вакууме. Остаточный вакуум (1-10 Па) в корпусе и был той средой над поверхностью изолирующей щели, которая обеспечивала обмен частицами материала с переменной проводимостью. В качестве последнего использовались поверхностные слои диоксида кремния изолирующей щели 3, в которых могло меняться содержание кислорода, что соответственно приводило к увеличению концентрации кремния.

На фиг.4 приведены ВАХ, отражающие процесс электроформовки в ячейках памяти для слоев с высокой концентрацией носителей различного типа проводимости. Измерялся ток j в металлической шине в зависимости от напряжения U между слоем с высокой концентрацией носителей и металлической шиной, которое подавалось в форме треугольного импульса с небольшой скоростью развертки. При этом для n+-кремния при положительной полярности напряжения (минус на металле) в нем формируется запирающий слой, для отрицательной - антизапирающий. В случае p+-кремния - ситуация обратная. Признаком выполнения электроформовки является резкое увеличение тока и появление N-образной формы ВАХ. Это происходит на обратном ходе в случае достаточно большой амплитуды треугольного импульса напряжения либо в случае достаточной выдержки при максимальном напряжении (3 с для кривой 3 на фиг.4,а). Как видно, для обоих типов кремния электроформовка имеет место не только для антизапирающей полярности, но и для запирающей, причем характеристики ее близки, т.е. в предлагаемой ячейке памяти при прямом напряжении (минус на металле) обеспечивается возможность выполнения электроформовки.

На фиг.5 показаны типичные квазистатические ВАХ ячейки после выполнения электроформовки для напряжений прямой полярности (когда переход "проводящий материал в изолирующей щели с нанометровым изолирующим зазором - слой из полупроводника с высокой концентрацией носителей тока" смещается в запирающем направлении), которые иллюстрируют эффекты переключения и памяти. Первоначально ячейка находилась в низкопроводящем состоянии (OFF), которому соответствуют относительно большие (около 4 нм) значения ширины h изолирующего зазора. После достижения порогового напряжения Vth, находящегося в диапазоне 3,8-4,0 В, происходит быстрое накопление проводящего материала и переключение ячейки в высокопроводящее состояние (ON), которому соответствуют малые (около 1 нм) значения h. Максимум N-образной кривой наблюдается около 5 В, что на 1 вольт меньше, чем в прототипе. При обратном ходе напряжения прорисовывается N-образная кривая, и структура остается в состоянии ON. Таким образом, в предлагаемой ячейке эффекты переключения и памяти качественно обычны для электроформованных структур, а существующие количественные отличия от прототипа имеют даже дополнительные преимущества, поскольку позволяют несколько уменьшить напряжения переключения из состояния ON в OFF, которое должно быть на несколько вольт выше напряжения максимума ВАХ.

Когда в слое полупроводника с высокой концентрацией легирующей примеси ее значения превышают 1020 см-3, процессы электроформовки и переключений для запирающей полярности напряжения будут тем более проходить обычным образом, поскольку при этом ширина обедненного слоя в полупроводнике уменьшается, а сам он приближается по своим электрическим свойствам к металлу.

Данные о функционировании экспериментальных образцов матрицы памяти, демонстрирующие достижение упомянутых выше технических результатов, приведены ниже и иллюстрируются фиг.6 и 7, на которых показаны ВАХ всех ячеек матрицы в различных состояниях. Символами W1, W2, W3 обозначены металлические (вольфрамовые) шины матрицы, a P1, P2, Р3 - перпендикулярные им шины р-кремния. Каждая ВАХ соответствует ячейке, находящейся на пересечении одной из вольфрамовых шин с одной из кремниевых шин. Измерялись токи в цепи металлических шин в зависимости от напряжения между шинами р-кремния и вольфрама, которое менялось со скоростью 0,5 В/с. В процессе измерений и переключений на коллекторном р-n-переходе поддерживалось постоянное обратное напряжение, равное 2 В.

После изготовления и выполнения электроформовки ВАХ ячеек матрицы имели вид, показанный на фиг.6, т.е. все ячейки находятся в высокопроводящем состоянии (ON). Все они имеют качественную выпрямляющую ВАХ, которая определяется, в основном, концентрацией бора в кремниевой шине первого уровня. Обратные напряжения составляют 11-12 В, что в 4 раза больше, чем в прототипе, и позволяет даже электроформовку выполнять для каждой ячейки независимо от других. Обратные токи не превышают долей наноампера и меньше, чем в прототипе, минимум на 4 порядка. Для прямой полярности напряжения коэффициент передачи тока в транзисторной структуре составляет около 100, это означает, что токи, протекающие по шинам р-кремния, на два порядка меньше показанных на фиг.6 токов в вольфрамовых шинах.

Поскольку напряжения пробоя ячеек выше 11 В, выборка индивидуальной ячейки при записи может быть без проблем реализована для импульса переключения из состояния ON в OFF, амплитуда которого должна быть 7-10 В. В специальных экспериментах было показано, что длительность такого импульса может составлять десятки нс, однако в данном случае, из-за аппаратурных ограничений, его длительность составляла 1 мкс, использовалась амплитуда 8 В. При записи из девяти ячеек матрицы осуществлялась индивидуальная выборка четырех: W1-P2, W2-P1, W2-P3, W3-P2.

На фиг.7,а показано состояние матрицы (в виде соответствующих ВАХ) после выполнения записи. Для считывания информации использовался треугольный импульс напряжения с амплитудой, меньшей порогового Vth, что гарантировало его неразрушающий характер. На фиг.7,б отдельно приведены ВАХ элементов матрицы, находящихся в состоянии OFF, в другом масштабе токов. Как видно, проводимости ячеек в состояниях ON и OFF отличаются на 4-5 порядков, что на порядок больше, чем в прототипе.

Таким образом, приведенные данные демонстрируют для предложенной ячейки матрицы энергонезависимой памяти достижение всех заявленных технических результатов.

Предлагаемая ячейка матрицы энергонезависимой памяти апробирована в Институте микроэлектроники и информатики РАН.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА МАТРИЦЫ ПАМЯТИ | 2004 |

|

RU2263373C1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| ЭЛЕМЕНТ ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2016 |

|

RU2637175C2 |

| Способ электроформовки при изготовлении элемента памяти | 2020 |

|

RU2769536C1 |

| ЯЧЕЙКА ПАМЯТИ СО СТРУКТУРОЙ ПРОВОДЯЩИЙ СЛОЙ-ДИЭЛЕКТРИК-ПРОВОДЯЩИЙ СЛОЙ | 2007 |

|

RU2376677C2 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

| УСТРОЙСТВО ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2008 |

|

RU2374704C1 |

| СПОСОБ ФОРМИРОВАНИЯ ПРОВОДЯЩЕГО ЭЛЕМЕНТА НАНОМЕТРОВЫХ РАЗМЕРОВ | 2001 |

|

RU2194334C1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии. Сущность изобретения: ячейка включает полупроводниковую шину первого уровня, расположенную на подложке, электрически изолирующей ее от других шин первого уровня, перекрещивающуюся с ней металлическую шину второго уровня, расположенный под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью. Между слоем диэлектрика и шиной первого уровня под изолирующей щелью расположен слой с высокой концентрацией носителей тока из полупроводника n+- или p+-типа проводимости, противоположного типу проводимости полупроводника шины первого уровня, а его размеры в плоскости подложки таковы, что не нарушается электрическая изоляция шин первого уровня матрицы друг от друга. Техническим результатом изобретения является улучшение выпрямляющих свойств ячейки и в резкое уменьшение токов по полупроводниковой шине. 1 з.п. ф-лы, 7 ил.

| RU 2004100899 A, 20.06.2005 | |||

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ - ИЗОЛЯТОР - МЕТАЛЛ | 1994 |

|

RU2072591C1 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

| Валиев К.А | |||

| и др | |||

| Память на основе нано-МИМ-диода с углеродистой активной средой | |||

| Микроэлектроника | |||

| Электрическое сопротивление для нагревательных приборов и нагревательный элемент для этих приборов | 1922 |

|

SU1997A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

Авторы

Даты

2007-06-27—Публикация

2005-06-28—Подача