Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии.

Известна ячейка матрицы ППЗУ (программируемого постоянного запоминающего устройства) на основе резисторных элементов памяти [1], включающая перекрещивающиеся проводящие шины, между которыми подключены плавкие перемычки, пережигаемые в режиме программирования матрицы (записи информации) за счет выделения в них джоулева тепла при подаче между парой выбранных перекрещивающихся шин достаточного для этого напряжения. В режиме считывания информации состояние выбранного элемента (ON или OFF) определяется величиной протекающего тока при подаче относительно небольшого напряжения считывания. Последовательно каждой пережигаемой перемычке включают диод, что обеспечивает электрическую развязку запоминающих элементов в матрице. В качестве плавких перемычек используют элементы из тонких пленок проводящих материалов, например нихрома, поликремния, алюминия, с электрическим сопротивлением, обеспечивающим выделение в них мощности, достаточной для пережигания. В такой ячейке матрицы памяти возможно только однократное программирование (запись информации).

Известен элемент устройства энергонезависимой электрически перепрограммируемой памяти со структурой металл-изолятор-металл [2], который включает металлический электрод первого уровня, расположенный на изолирующей подложке, металлический электрод второго уровня, разделяющий электроды двух уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания электродов первого и краев электрода второго уровней, находящийся в изолирующей щели углеродистый активный материал, проводимость которого меняется при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую поступление исходного углеродсодержащего (органического) материала и возможность удаления частиц углеродистого материала с поверхности изолирующей щели. В случае подачи на металлические электроды достаточного напряжения и прохождения через изолирующую щель электрического тока из органического вещества за счет деструкции его молекул при электронном ударе образуется углеродистый активный материал (процесс электроформовки), проводимость которого меняется в широких пределах в зависимости от его состава и структуры, зависящих от значений тока и прошедшего заряда. При этом элемент переводится в высокопроводящее состояние. Подача импульса напряжения большей амплитуды приводит к термическому удалению образовавшегося углеродистого проводящего материала и переводу элемента в низкопроводящее состояние. Оба состояния сохраняются неограниченно долго при отключенном питании, и переключения между ними возможны многократно. Такой элемент может служить основой для построения устройства электрически перепрограммируемой энергонезависимой памяти. Поскольку все процессы происходят в изолирующей щели шириной порядка единиц и десятков нанометров, размеры элемента памяти могут быть чрезвычайно малы, а значит, плотность записи информации в соответствующем устройстве - очень велика.

В [3] предложена конструкция элементов матрицы энергонезависимой электрически перепрограммируемой памяти на базе описанных выше элементов. Соответствующий элемент матрицы памяти включает металлическую (проводящую) шину первого уровня, расположенную на подложке, электрически изолирующей ее от других металлических шин первого уровня матрицы, перекрещивающуюся с ней металлическую шину второго уровня, разделяющий шины двух (первого и второго) уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели углеродистый активный материал, проводимость которого меняется при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую поступление исходного углеродсодержащего (органического) материала и возможность удаления частиц углеродистого материала с поверхности изолирующей щели (обмен частицами материала с переменной проводимостью). В случае подачи между металлическими шинами электрического напряжения и прохождения через изолирующую щель электрического тока за счет деструкции молекул органического вещества при электронном ударе образуется углеродистый активный материал и в нем в результате процесса самоорганизации (самоформирования) формируется изолирующий зазор шириной несколько нанометров (процесс электроформовки), которая зависит от приложенного напряжения. Проводимость элемента определяется шириной изолирующего зазора и поэтому может меняться в широких пределах в зависимости от напряжения между шинами. При этом элемент памяти при отключенном питании находится либо в низко-, либо в высокопроводящем состоянии, а переключения между ними возможны за счет подачи импульсов напряжения различной амплитуды. По совокупности признаков такой элемент матрицы памяти наиболее близок к предлагаемым техническим решениям.

Недостатком таких элементов памяти является невозможность прямого объединения их в матрицу. Для функционирования матрицы памяти каждая ячейка должна быть электрически развязана с другими ячейками, чтобы была обеспечена возможность ее независимой выборки при считывании и записи информации. Это может быть реализовано, например, для ячеек, каждая из которых имеет выпрямляющую вольт-амперную характеристику (ВАХ). Но ВАХ элемента памяти со структурой металл-изолятор-металл практически симметрична. Включение последовательно каждому элементу памяти отдельно сформированного диода может решить эту проблему, но это уменьшит плотность записи информации в матрице.

В предлагаемой ячейке матрицы памяти, включающей проводящую шину первого уровня, расположенную на подложке, электрически изолирующей ее от других проводящих шин первого уровня матрицы, перекрещивающуюся с ней проводящую шину второго уровня, разделяющий шины первого и второго уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью, шина одного из уровней выполнена из полупроводника р- или n-типа. Отличие предлагаемого изобретения заключается в том, что шина одного из уровней выполнена из полупроводника р- или n-типа.

Достигаемый при этом технический результат состоит в том, что предлагаемая ячейка обладает и свойствами элемента энергонезависимой электрически перепрограммируемой памяти, и выпрямляющими свойствами с характеристиками, обеспечивающими электрическую развязку ячейки в матрице, причем размеры ячейки не увеличиваются в сравнении с элементом памяти прототипа. Это обеспечивается тем, что в областях перекрещивания шин первого и краев шин второго уровней после подачи между ними напряжения и выполнения электроформовки (накопления проводящего материала в изолирующей щели и самоформирования в нем изолирующего зазора) формируется новый интегральный прибор наноэлектроники, имеющий структуру: металлическая шина - проводящий материал, образовавшийся в изолирующей щели, с изолирующим зазором - полупроводник. По своей структуре он близок к барьеру Шоттки с переменной шириной нанометрового изолирующего зазора между проводящим электродом и полупроводником, причем элементы конструкции, которые независимо составляли бы последовательно соединенные барьер Шоттки (выпрямляющие свойства) и нанометровый изолирующий зазор между проводящими электродами (свойства памяти), разделить невозможно. Такая «интегральность» прибора позволяет сохранить размеры в сравнении с элементом памяти прототипа и в то же время обеспечить ему электрические свойства, позволяющие соединить такие ячейки памяти в матрицу.

Кроме того, проводящая шина именно первого уровня выполняется из полупроводника именно р-типа.

Достигаемый при этом технический результат состоит в улучшении качественных характеристик ячейки матрицы памяти. Во-первых, для полупроводниковой шины может использоваться высококачественный монокристаллический полупроводниковый материал подложки, в случае же выполнения из полупроводника шины второго уровня он должен получаться в виде тонкой пленки после формирования металлической шины первого уровня, а значит, качество его будет значительно ниже, что может сказаться на всех существенных электрических характеристиках ячейки, в частности на напряжениях пробоя. Во-вторых, при выполнении нижней шины из полупроводника р-типа для прямой (антизапирающей) полярности напряжения на ячейке (минус на металлической шине) электроны будут эмитироваться из края металлической шины, который имеет малый радиус кривизны, а значит, потребуются меньшие напряжения при проведении электроформовки. В случае же выполнения нижней шины из полупроводника n-типа потребовалась бы противоположная полярность напряжения, и эмиссия электронов шла бы с плоской поверхности нижней шины. Таким образом, выполнение проводящей шины именно первого уровня из полупроводника именно р-типа является оптимальным вариантом из возможных.

Кроме того, проводящая шина первого уровня отделена от других проводящих шин первого уровня матрицы областями полупроводника n-типа, а толщина слоя диэлектрика над областями полупроводника n-типа выбирается такой, чтобы было исключено образование на их поверхности каналов с инверсной проводимостью.

Достигаемый при этом технический результат состоит в упрощении технологии изготовления матрицы памяти. В этом случае не требуется применение дорогой изолирующей подложки, а может использоваться просто пластина низколегированного монокристаллического полупроводника n-типа. При этом шины первого уровня матрицы из полупроводника р-типа могут получаться путем локального легирования подложки акцепторной примесью, а их электрическая изоляция от подложки и друг от друга осуществляется образующимися обратно смещенными р-n-переходами.

Кроме того, полупроводниковая шина выполнена из кремния. Получаемый при этом технический результат состоит в достижении высокой стабильности характеристик ячейки матрицы памяти. Кремний имеет относительно высокую температуру плавления, поэтому структура кремниевого электрода (шины первого уровня) обладает высокой устойчивостью в нанометровом масштабе даже при повышенных температурах (до 1000 К), возникающих при электроформовке и переключениях между состояниями ячейки, что обеспечивает хорошую стабильность самоформирующегося изолирующего зазора нанометровой ширины между проводящей средой и поверхностью кремния, определяющего ВАХ элемента памяти, а также стабильность свойств самой кремниевой шины.

Кроме того, ячейка матрицы памяти дополнительно включает проводящую металлическую шину третьего уровня, параллельную проводящей шине, выполненной из полупроводника, и разделяющий шины второго и третьего уровня слой диэлектрика, причем шина третьего уровня имеет омические контакты к шине, выполненной из полупроводника.

Достигаемый при этом технический результат состоит в уменьшении сопротивления подводящих к каждой ячейке матрицы шин. Высокое удельное сопротивление полупроводника ограничивает длину соответствующей проводящей шины, а значит, и размерность матрицы по одной координате. Наличие дополнительной проводящей шины третьего уровня, выполненной из материала с низким удельным сопротивлением (металла), позволяет при выборке заданной ячейки обеспечить низкое сопротивление подводящих шин даже при большой их длине, а значит, снять жесткие ограничения на размерность матрицы памяти.

Кроме того, поверхность изолирующей щели выполнена из диоксида кремния.

Достигаемый при этом технический результат заключается в реализации назначения диоксида кремния как материала с переменной проводимостью, меняющейся при прохождении через него потока электронов. Поверхностные слои диоксида кремния выполняют функцию проводящей среды, в которой при электроформовке самоформируется нанометровый изолирующий зазор, и обеспечивает хорошие характеристики ячейки как элемента памяти.

В источниках информации не обнаружено сведений, аналогичных предложенной ячейке матрицы памяти, что позволяет сделать вывод о ее новизне.

Кроме того, связь совокупности признаков предлагаемого устройства с достижением указанных технических результатов для специалиста явным образом не следует из существующего уровня техники, что подтверждает соответствие предлагаемых технических решений критерию «изобретательский уровень».

Обоснование предлагаемого устройства вместе со сведениями, подтверждающими возможность его осуществления, приводятся ниже с использованием графических материалов.

На фиг.1 показано схематичное изображение поперечного сечения фрагмента ячейки матрицы памяти, включающего изолирующую щель после выполнения электроформовки. 1 - проводящая (металлическая) шина второго уровня, 2 - слой диэлектрика (SiO2) толщиной d=3-100 нм, разделяющий шины первого и второго уровней, 3 - изолирующая щель в форме открытого торца слоя диэлектрика, 4 - проводящая шина первого уровня из полупроводника р-типа (кремний), 5 - материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, находящийся в проводящем состоянии (проводящий материал) 6 - самосформировавшийся изолирующий зазор переменной нанометровой ширины h, заполненный диоксидом кремния (остаточный диэлектрик).

На фиг.2 схематично показаны фрагменты матрицы памяти в плане. Форма периметра открытого торца диэлектрической пленки: а - по внешним краям проводящей шины второго уровня, б - внутри области перекрещивания проводящих шин двух уровней. 1 - проводящие (металлические) шины второго уровня, 3 - открытые торцы диэлектрической пленки (изолирующие щели), 4 - проводящие шины первого уровня (полупроводник р-типа), 7 - подложка, электрически изолирующая друг от друга проводящие шины первого уровня матрицы. Пунктиром выделена ячейка матрицы памяти.

На фиг.3 показана принципиальная электрическая схема фрагментов матрицы памяти, приведенных на фиг.2. 1 - проводящие шины второго уровня, 4 - проводящие шины первого уровня, 8 - элемент матрицы, обладающий выпрямляющей ВАХ и имеющий два состояния (высоко- и низкопроводящее). Пунктиром выделена ячейка матрицы памяти.

На фиг.4 показана типичная форма сглаженных ВАХ структуры металл-изолятор-металл после выполнения электроформовки, поясняющих бистабильность и эффект памяти.

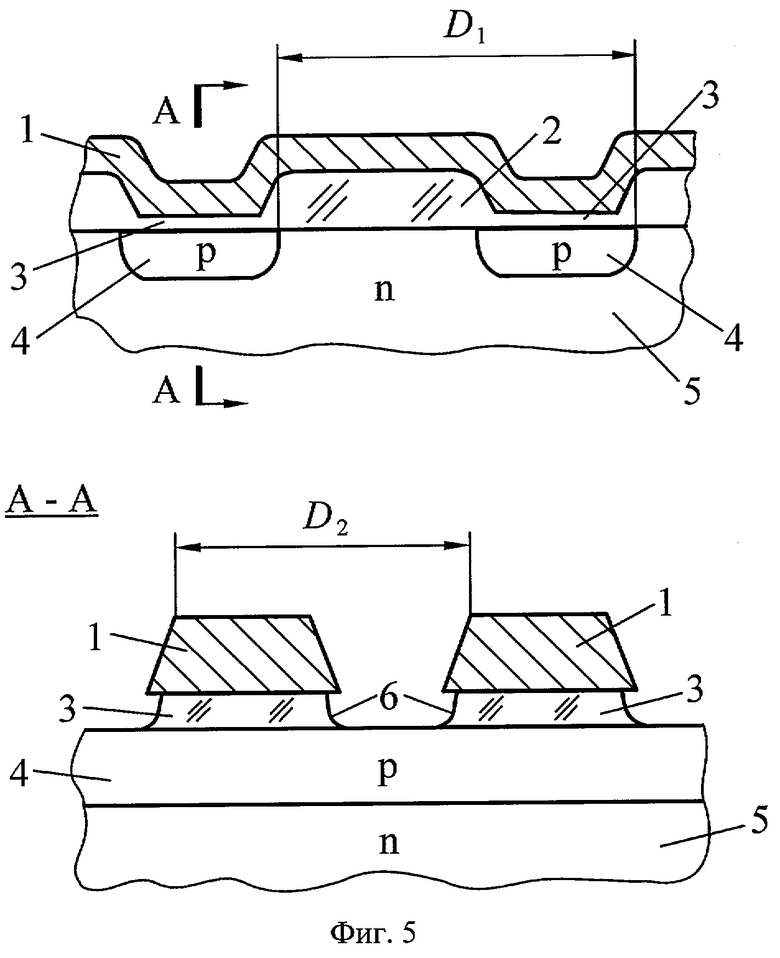

На фиг.5 приведены поперечные сечения фрагмента матрицы памяти при использовании в качестве подложки, изолирующей шины первого уровня друг от друга, полупроводника n-типа проводимости. 1 - проводящая (металлическая) шина второго уровня, 2 - слой тонкого диэлектрика (SiO2), разделяющий шины первого и второго уровней, 3 - изолирующие щели в форме открытого торца слоя тонкого диэлектрика, 4 - проводящие шины первого уровня из полупроводника (кремния) р-типа, 7 - подложка из полупроводника (кремния) n-типа проводимости, 9 - слой толстого диэлектрика (SiO2) над областями полупроводника n-типа.

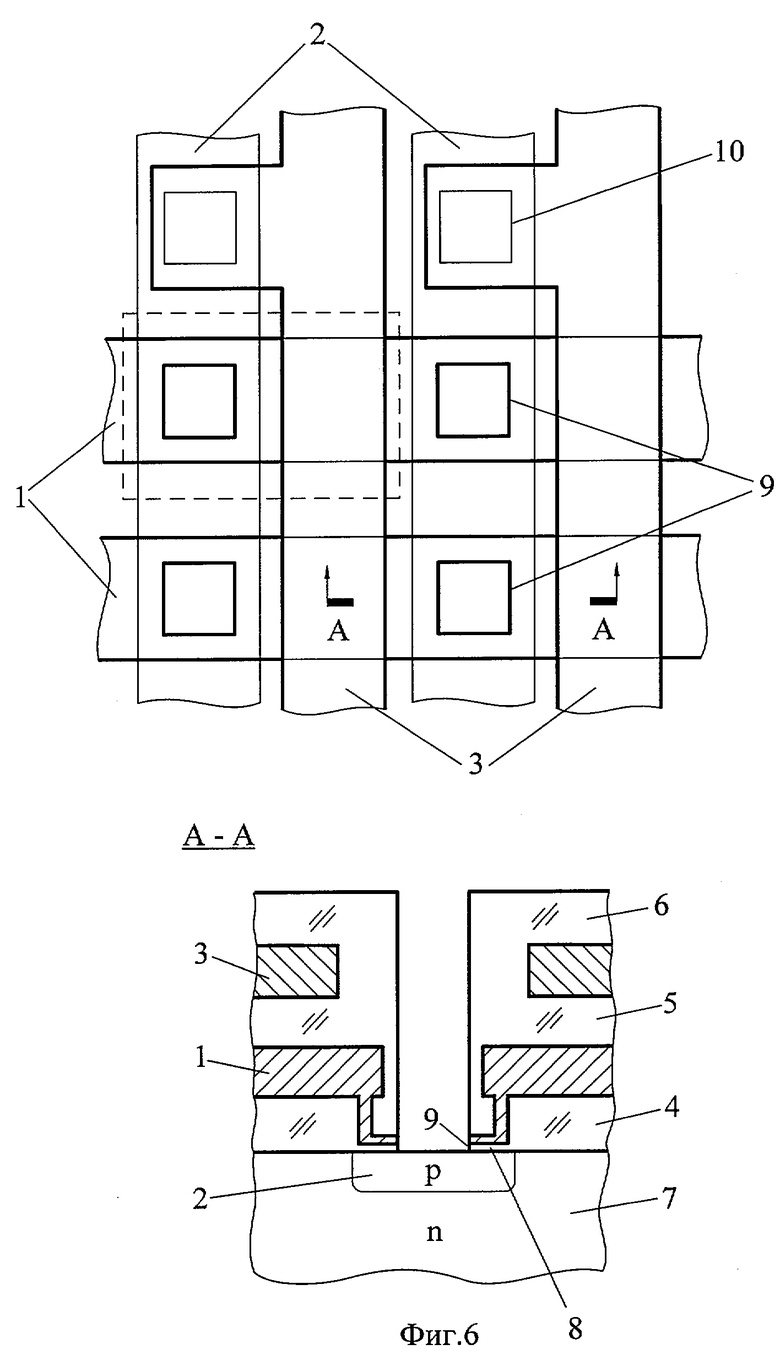

На фиг.6 показан фрагмент матрицы памяти с использованием проводящих шин трех уровней. 1 - проводящая (металлическая) шина второго уровня, 2 - слой тонкого диэлектрика (SiO2), разделяющий шины первого и второго уровней, 3 - изолирующие щели в форме открытого торца слоя тонкого диэлектрика, 4 - проводящие шины первого уровня из полупроводника (кремния) р-типа, 7 - подложка из полупроводника (кремния) n-типа проводимости, 9 - слой толстого диэлектрика (SiO2) над областями полупроводника n-типа, 10 - проводящие металлические шины третьего уровня, 11 - слой диэлектрика, разделяющий проводящие шины второго и третьего уровней, 12 - защитный слой, 13 - области омического контакта между металлическими шинами третьего уровня и полупроводниковыми шинами первого уровня. Пунктиром выделена ячейка матрицы памяти.

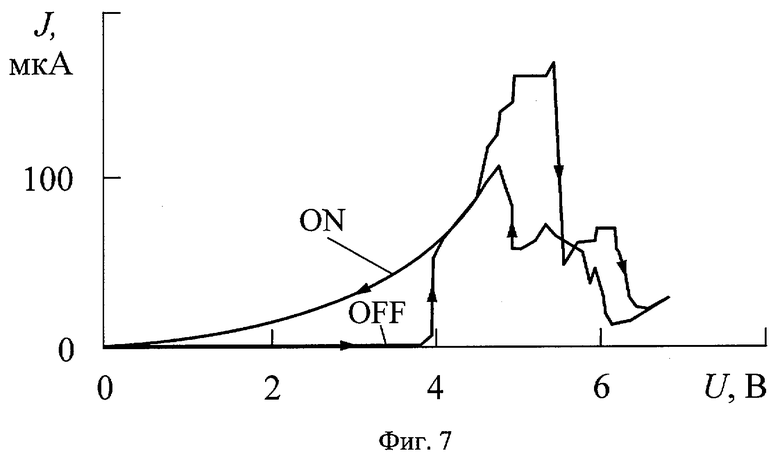

На фиг.7. приведены реальные ВАХ одного из элементов матрицы для напряжений прямой полярности после выполнения электроформовки. Первоначально элемент находился в низкопроводящем состоянии (OFF). Периметр открытого торца (длина изолирующей щели) 32 мкм. Скорость изменения напряжения 0,5 В/с.

На фиг.8 приведены ВАХ 9 элементов матрицы для конкретного экспериментального образца матрицы памяти (3×3), соответствующие начальному состоянию после ее изготовления и выполнения электроформовки (состояние ON).

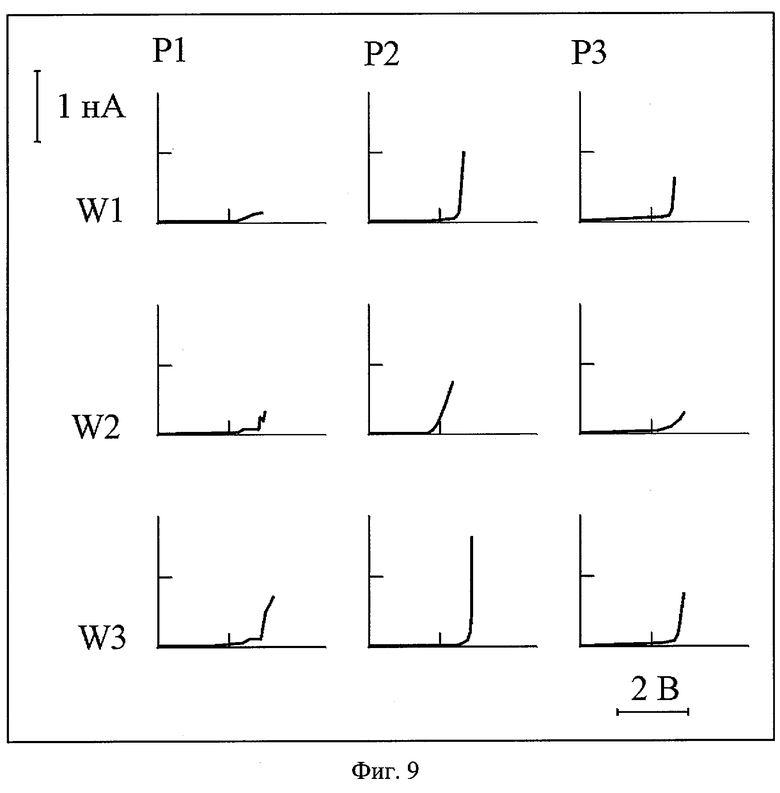

На фиг.9 приведены ВАХ 9 элементов матрицы для того же экспериментального образца матрицы памяти, после параллельного их переключения в состояние OFF («стирание»).

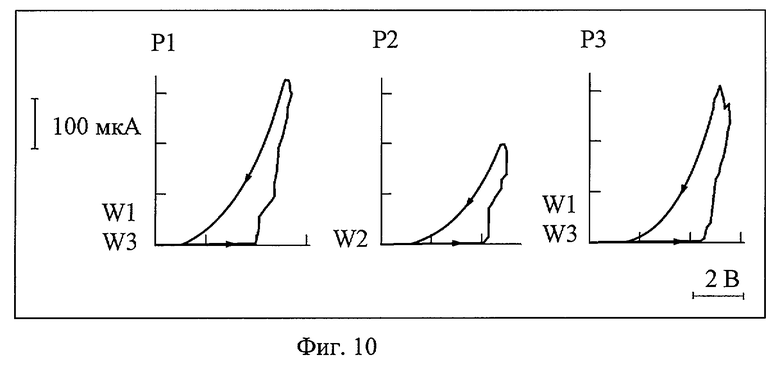

На фиг.10 приведены ВАХ для того же экспериментального образца матрицы памяти, отражающие процесс переключения выбранных пяти элементов матрицы в состояние ON («запись»).

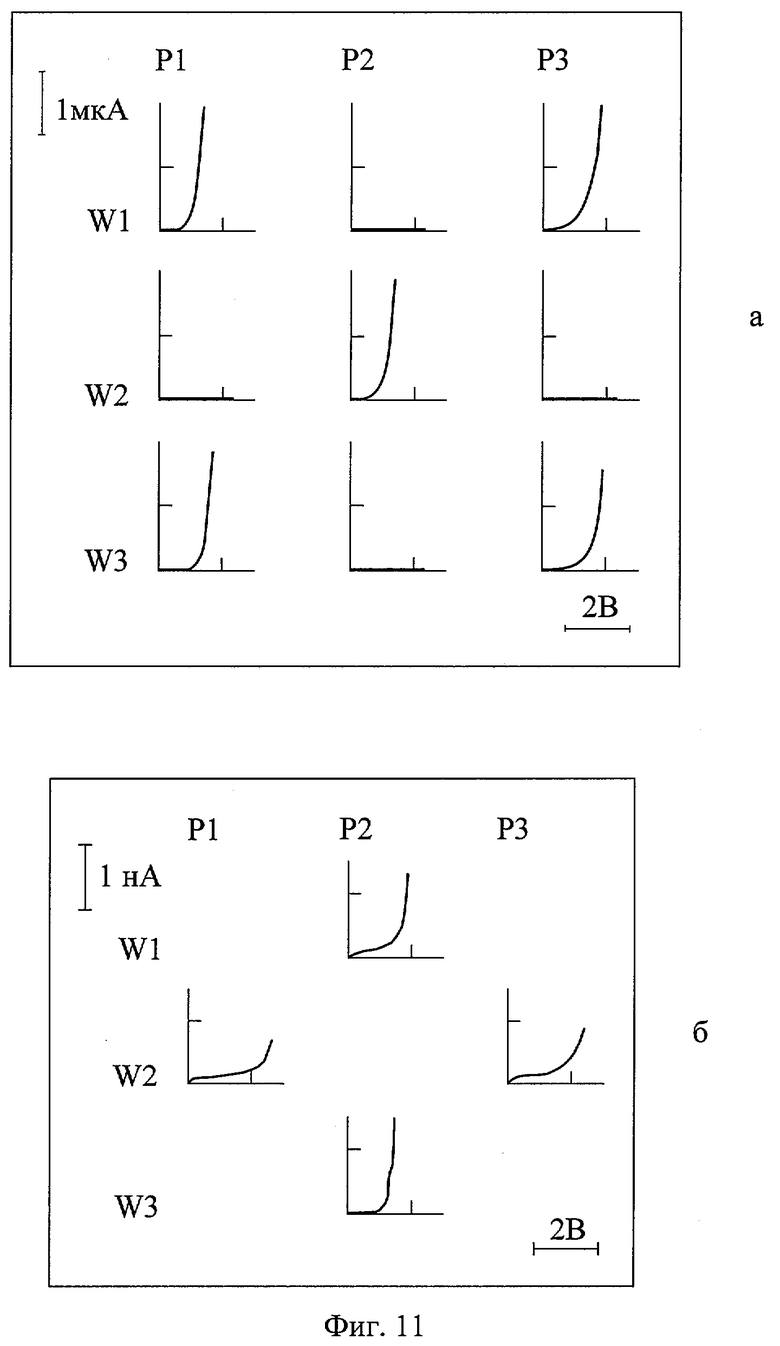

На фиг.11 приведены ВАХ элементов матрицы (считывание) для того же экспериментального образца матрицы памяти, после выполнения операции «запись», а - в диапазоне больших токов (для всех 9 элементов), б - в диапазоне малых токов (для 4 элементов, оставшихся в состоянии OFF).

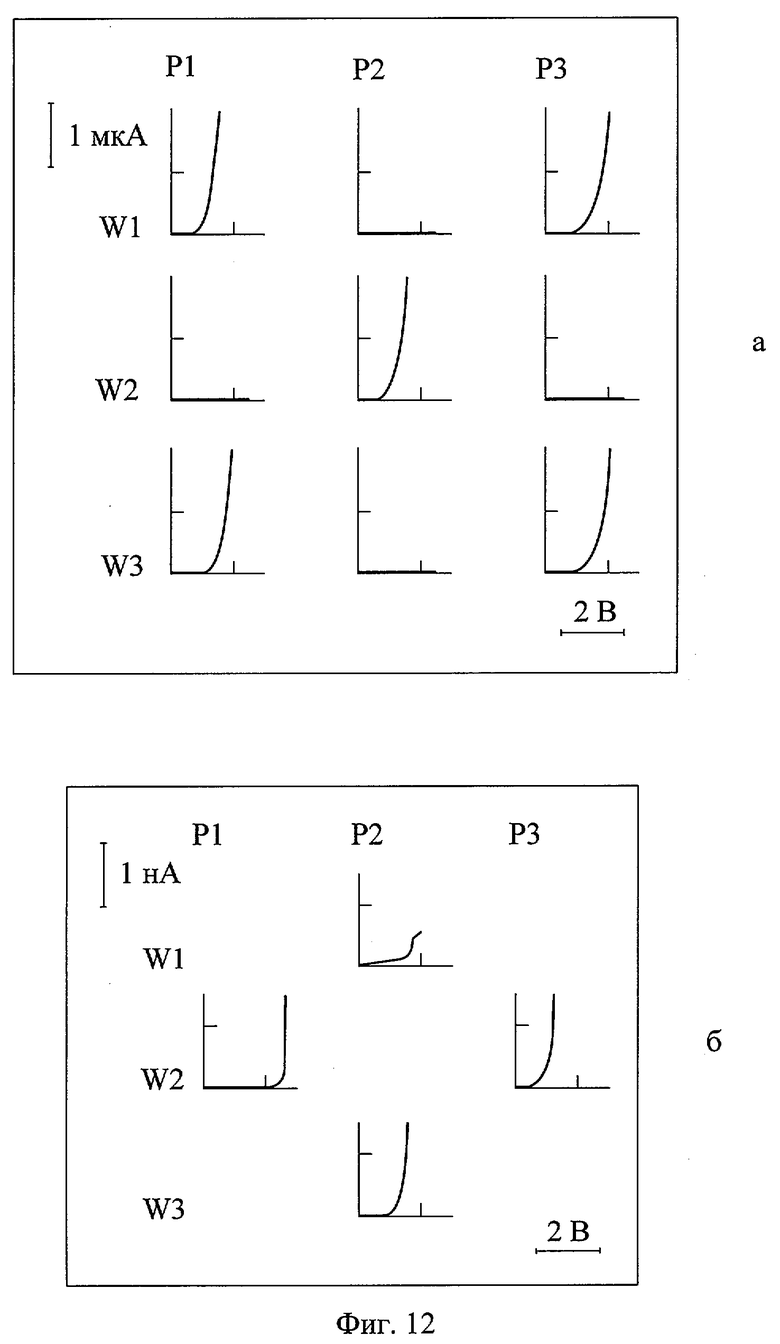

На фиг.12 приведены ВАХ, аналогичные фиг.11, после выполнения 5 таких же циклов считывания.

Изолирующая щель 3 (фиг.1) в форме торца диэлектрической пленки 2 создается путем локального травления металлической пленки проводящей шины 1 второго уровня и диэлектрической пленки 2. При этом ширина изолирующей щели определяется толщиной d диэлектрической пленки, которая лежит в диапазоне 3-100 нм.

После подачи электрического напряжения между проводящими шинами второго 1 и первого 4 уровней (минус на шине второго уровня) и выполнения электроформовки в изолирующей щели 3 образуется проводящий материал 5, который может занимать часть или весь периметр открытого торца. Формирование проводящего материала (материала с переменной проводимостью) происходит из-за деструкции молекул исходно диэлектрического вещества на поверхности изолирующей щели за счет электронного удара [4] при прохождении потока электронов и приложенном напряжении, большем некоторого порогового значения Ufr≈2-3 В, что приводит к образованию частиц проводящей фазы. Электроны эмитируются с катода, функцию которого в данном случае выполняет край проводящей шины 1 второго уровня, с малым радиусом кривизны ρ.

В качестве исходного вещества для образования находящегося в изолирующей щели материала с переменной проводимостью, меняющейся при прохождении через него потока электронов, могут служить, например, адсорбированные на поверхности изолирующей щели из газовой фазы органические молекулы [5] либо собственно диэлектрик поверхности изолирующей щели. В первом случае электроформовка приводит к разложению органического вещества и образованию материала, обогащенного углеродом (углеродистого проводящего материала), а средой над поверхностью изолирующей щели, обеспечивающей обмен частицами материала с переменной проводимостью, является газовая фаза, содержащая органические молекулы. При этом она обеспечивает как поступление новых органических молекул, так и удаление с поверхности продуктов реакции. Во втором случае частицы проводящей фазы образуются за счет разложения диэлектрического материала, например аморфного оксида металла [6], поверхности изолирующей щели. При этом средой над ней может быть просто вакуум, что обеспечивает удаление продуктов реакции в виде избыточного кислорода, а поверхностный материал обогащается атомами металла, что и ведет к увеличению его проводимости. Существенно, что изолирующая щель должна быть открыта для обмена молекулами вещества со средой.

При выполнении электроформовки происходит накопление проводящего материала 5 в изолирующей щели 3 и автоматическое, т.е. за счет самоформирования, установление ширины h (она составляет несколько нанометров и зависит от величины приложенного напряжения) изолирующего зазора 6. Фактически этот зазор оказывается заполнен диоксидом кремния, оставшимся после локального стравливания тонкой пленки SiO2 (остаточный диэлектрик). Именно изолирующий зазор шириной h в основном определяет проводимость ячейки для прямой полярности (минус на проводящей шине 1 второго уровня) приложенного напряжения.

Таким образом, после выполнения электроформовки формируется новый интегральный прибор наноэлектроники, который имеет структуру:

металлическая шина 1 - проводящий материал 5, образовавшийся в изолирующей щели, с изолирующим зазором 6 - полупроводник 4. По своей структуре он близок к барьеру Шоттки, но имеет следующие существенные особенности. Во-первых, в нем присутствует специфический материал, выполняющий функцию проводящего электрода, - это образовавшийся при электроформовке проводящий материал 5. Во-вторых, - это малая площадь контакта проводящего электрода с полупроводником - только по торцу диэлектрической пленки, фактически получается, что в полупроводник упирается (через изолирующий зазор) проводящее «нанолезвие». В-третьих, это переменная (зависящая от напряжения) толщина h диэлектрика на поверхности полупроводника. При этом можно было рассчитывать, что такой прибор будет проявлять и свойства элемента энергонезависимой электрически перепрограммируемой памяти и выпрямляющие свойства барьера Шоттки, хотя на уровне элементов конструкции невозможно разделить (как последовательно соединенные) нанометровый изолирующий зазор, который должен отвечать за свойства прибора как элемента памяти, и переход проводящий материал - полупроводник (т. е. барьер Шоттки), который может иметь выпрямляющие свойства.

Предсказать свойства и тем более приемлемость значений технических характеристик такого интегрального прибора наноэлектроники из имеющегося уровня техники было невозможно, поэтому потребовалось проведение специальных экспериментальных работ. Ниже приведены их результаты, которые продемонстрировали, что на его базе может быть создана ячейка матрицы энергонезависимой электрически перепрограммируемой памяти, свойства которой, в том числе выпрямляющие, обеспечивают электрическую развязку и возможность выборки ячейки в режимах считывания и записи.

Возможны варианты использования для шины первого уровня и полупроводника n-типа, а также выполнения из полупроводника проводящей шины второго уровня. Однако оптимальным с точки зрения достижения качественных характеристик ячейки памяти является именно вариант, показанный на фиг.1. В этом случае для шины первого уровня может использоваться высококачественный монокристаллический полупроводниковый материал, сформированный на технологических операциях изготовления полупроводниковых подложек. Кроме того, в этом случае прямая полярность для полупроводника р-типа именно такова, что катодом, эмитирующим электроны, необходимые для электроформовки и переключения состояний ячейки, должна быть проводящая шина второго уровня, край которой имеет малый радиус кривизны, что облегчает эмиссию и позволяет уменьшить значения прикладываемых к шинам напряжений.

Фрагменты матрицы памяти в плане приведены на фиг.2. Открытые торцы 3 диэлектрической пленки, разделяющей проводящие шины двух уровней, могут формироваться по внешним краям шины второго уровня (фиг.2,а), либо внутри области перекрещивания проводящих шин (фиг.2,б).

В первом случае могут быть обеспечены наименьшие размеры (D1 и D2) ячейки матрицы, но существуют особые точки (на перекрещивании краев шин двух уровней), в которых трудно контролировать профиль травления диэлектрической пленки. Во втором - все точки открытого периметра находятся в одинаковых условиях, которые можно контролировать при формировании открытого торца.

Принципиальная электрическая схема таких фрагментов матрицы памяти показана на фиг.3. Между проводящими шинами первого 4 и второго 1 уровней включены предложенные интегральные приборы наноэлектроники, обозначенные как элементы 3 матрицы, обладающие выпрямляющей ВАХ и имеющие два состояния (высоко- и низкопроводящее), переключения между которыми возможны при подаче соответствующих импульсов напряжения.

На фиг 4. в качестве пояснения эффекта памяти приведена типичная форма сглаженных ВАХ электроформованной структуры металл-изолятор-металл и возможные переключения ее состояний. Для предлагаемой ячейки матрицы памяти при прямой полярности напряжения (минус на металлической шине), когда на поверхности полупроводника образуется обогащенный слой, качественно ситуация может быть аналогична. При медленном изменении напряжения наблюдается N-образная ВАХ (кривая а), которую в первом приближении можно считать обратимой (фактически существует некоторый гистерезис, а ветвь с отрицательным дифференциальным сопротивлением сильно зашумлена). Механизм и модель, объясняющие такую форму ВАХ, приведены в [7]. С ростом напряжения одновременно с уменьшением тока меняется (увеличивается) и ширина h (фиг.1) изолирующего зазора. При малых напряжениях кривой а соответствует высокопроводящее состояние (ON) структуры и малые значения h. Величина тока в максимуме ВАХ зависит от длины открытого периметра и режимов выполнения электроформовки. Если в некоторой точке, например точке А, ветви с отрицательным дифференциальным сопротивлением напряжение резко (за время меньшее приблизительно 10-3 с) сбрасывается (кривая b), то структура переходит в низкопроводящее состояние (OFF), поскольку из-за инерционности процесса накопления проводящего материала фиксируется («замораживается») состояние с большим значением h. Сопротивление в этом состоянии зависит от положения точки А (чем она правее, тем выше сопротивление), но оно легко может быть получено на 2 - 3 порядка больше, чем в состоянии ON. Если структура находится в состоянии OFF, то при напряжениях ниже порогового значения Uth≈Ufr это состояние не изменяется, поскольку невозможно образование частиц проводящей фазы. Однако в случае превышения Uth происходит быстрый рост проводимости (повторное накопление проводящего материала в изолирующей щели и уменьшение h) и переключение структуры в состояние ON (кривая с). Для структур металл-изолятор-металл значения порогового напряжения Uth обычно лежат в диапазоне 2-3 В, а напряжение Umax максимума N-образной ВАХ - в диапазоне 3-4 В.

При функционировании матрицы памяти каждая ячейка может находиться в следующих режимах.

1. Режим хранения информации. При отключенном питании ячейка сохраняет одно из двух состояний: высоко- (ON) или низкопроводящее (OFF) в зависимости от того (фиг.4), каким была амплитуда последнего переключающего импульса напряжения. Высокопроводящему состоянию соответствует малая ширина h (фиг.1) изолирующего зазора (1-2 нм), низкопроводящему - относительно большая (более 4 нм).

2. Режим считывания. На выбранную ячейку подается импульс напряжения прямой полярности с амплитудой, меньшей порогового значения Uth≈Ufr (фиг.4). Это обеспечивает неразрушающий характер считывания. Состояние ячейки (ON или OFF) определяется путем измерения тока через нее. Длительность импульса считывания ограничивается снизу задержками в соответствующих электрических цепях.

3. Режим переключения из состояния OFF в состояние ON. На выбранную ячейку подается импульс напряжения прямой полярности с амплитудой вблизи значения Umax (фиг.3). Поскольку это напряжение превышает пороговое значение Uth, идет интенсивный процесс образования и накопления частиц проводящей фазы, приводящий к зарастанию изолирующего зазора и уменьшению его ширины h. Однако из-за того, что процесс накопления частиц проводящей фазы - относительно медленный, длительность импульса напряжения должна быть относительно велика.

4. Режим переключения из состояния ON в состояние OFF. На выбранную ячейку подается импульс напряжения прямой полярности с амплитудой в диапазоне от 7 до 12 В в зависимости от желаемого сопротивления ячейки в состоянии OFF, которое растет с увеличением амплитуды импульса. При этом происходит удаление («выжигание») части проводящего материала с поверхности изолирующей щели и увеличение ширины изолирующего зазора h. Процесс удаления проводящего материала - относительно быстрый и требует малых длительностей соответствующего импульса напряжения.

5. Пассивный режим. На невыбираемую ячейку попадают напряжения обратной полярности с амплитудой, близкой к амплитуде прямого напряжения, подаваемого на выбираемую ячейку. При этом большая часть приложенного напряжения падает на обедненном слое, образующемся на поверхности полупроводниковой проводящей шины, который и ограничивает ток через ячейку, а состояние проводящего материала в изолирующей щели не меняется. Чтобы прикладываемые к ячейке обратные напряжения падали в основном на обедненном слое, концентрация легирующей примеси в полупроводнике должна выбираться из следующих условий: во всех состояниях ячейки ширина обедненного слоя должна быть много больше ширины h изолирующего зазора, а обратный ток обедненного слоя должен быть много меньше тока изолирующего зазора, измеряемого в прямом направлении.

Проводящие шины 4 (фиг.2) первого уровня из полупроводника р-типа могут располагаться на диэлектрической подложке 4, которая надежно изолирует их друг от друга, либо на полупроводниковой подложке с использованием известных приемов диэлектрической изоляции полупроводниковых областей (в данном случае - р-шин). Однако технологически проще всего (фиг.5) изготовить проводящие шины 4 первого уровня из полупроводника р-типа путем локального легирования полупроводниковой подложки 7 n-типа акцепторной примесью. При этом электрическая изоляция их друг от друга и от подложки возможна образующимися р-n-переходами, на которые подается небольшое обратное смещение. Для этой же цели необходимо избежать возможности образования инверсного слоя на поверхности областей полупроводника n-типа, разделяющих р-шины, который будет электрически перемыкать р-шины и может формироваться при подаче на шины второго уровня отрицательных (прямых) напряжений. Величина напряжения, при котором возникает инверсный слой, зависит от концентрации донорной примеси в полупроводнике, толщины слоя диэлектрика между проводящей шиной второго уровня и n-подложкой, а также величины заряда в диэлектрике. Путем увеличения толщины слоя диэлектрика можно добиться условия, что во всем диапазоне напряжений, прикладываемых между шиной второго уровня и подложкой, инверсный слой образовываться не будет.

Использование кремния в качестве полупроводникового материала и хорошо разработанной кремниевой технологии для изготовления как самой матрицы памяти, так и электронных схем управления ею (они должны быть расположены на одном чипе с матрицей памяти), также значительно упрощает технологические проблемы. В то же время применение кремния как материала проводящей шины первого уровня имеет принципиальное самостоятельное значение для качественного функционирования ячейки матрицы памяти, прежде всего в части надежного хранения информации. Первоначально элемент памяти изготавливался [2] с проводящей шиной первого уровня из алюминия. Помимо прочих недостатков, такая структура демонстрировала низкую стабильность высокопроводящего состояния: уже через несколько суток его проводимость существенно уменьшалась. Алюминиевый электрод был самым слабым местом этой конструкции, поскольку его структура в нанометровом масштабе может изменяться уже при комнатных температурах, а значит, самопроизвольно и случайным образом может меняться ширина h изолирующего зазора, которая определяет электрические характеристики элемента памяти. Поверхность монокристаллического кремния, имеющего относительно большую температуру плавления, является высоко стабильной даже при повышенных локальных температурах (до 1000 К), имеющих место при эксплуатации элемента памяти. Этот вывод подтверждается экспериментальными данными, приведенными ниже.

Для того чтобы сопротивление проводящей р-шины не было слишком большим и не приводило к значительным падениям напряжения на ней, концентрация акцепторной примеси в шине должна быть высокой. В то же время слишком большая концентрация примеси ухудшит запирающие характеристики (уменьшит напряжение пробоя) элемента матрицы при обратной полярности напряжения. Баланс этих требований приводит к существованию области оптимальных концентраций акцепторной примеси. Значительно улучшить соотношение сопротивления проводящих шин р-кремния и напряжения пробоя элемента матрицы можно использованием специального профиля акцепторной примеси по глубине в кремний: низких концентраций вблизи поверхности полупроводника, которая определяет напряжения пробоя (до глубины около 0,3 мкм) и высокой концентрации на большей глубине, которая определяет сопротивление шины. Такой профиль можно сформировать, например, применением для легирования процесса ионной имплантации.

Из-за относительно высокого удельного сопротивления кремния даже для больших концентраций легирующей примеси (оно на несколько порядков больше удельного сопротивления металлов) допустимая длина р-шин существенно меньше длины металлических шин второго уровня при одинаковом значении их сопротивления и является основным фактором, ограничивающим размерность матрицы. Малая же размерность матрицы не позволит реализовать потенциально высокую плотность записи информации. Эта проблема может быть решена применением металлических проводящих шин 10 третьего уровня (фиг.6), параллельных проводящим шинам 4 первого уровня, выполненным из полупроводника. Они отделяются от проводящих шин 1 второго уровня слоем диэлектрика 11 и через соответствующие окна (аналогичные показанному на сечении, но заполненные металлом) имеют омические контакты 13 к проводящей шине первого уровня. Такие омические контакты могут располагаться на полупроводниковой шине рядом с каждым элементом памяти, при этом сопротивление подводящих шин к ячейке матрицы будет минимальным. Однако в этом случае область омических контактов фактически должна быть включена в состав ячейки памяти, площадь, занимаемая ячейкой и всей матрицей, увеличится приблизительно в два раза, а плотность записи информации соответственно уменьшится. Один омический контакт может приходиться и на несколько (например, на восемь) элементов памяти. В этом случае сопротивление подводящих шин будет больше, но уменьшение плотности записи информации в сравнении с вариантом без шин третьего уровня может быть незначительным.

Были изготовлены экспериментальные образцы матрицы памяти размерностью 3×3 (9 ячеек) с вариантом топологии в плане, показанном на фиг.2,а, и конструкцией, приведенной на фиг.5. Рисунок во всех слоях создавался методами контактной фотолитографии. Размеры ячейки памяти составляли D1=D2=32 мкм, что было связано с необходимостью минимизировать все второстепенные технологические проблемы. При этом периметр открытого торца составлял 2(D1/2)=32 мкм. В качестве подложки 7 использовались пластины монокристаллического кремния n-типа, легированного фосфором до удельного сопротивления 4,5 Ом·см, диаметром 100 мм. Проводящие шины 4 первого уровня формировались путем двухстадийной диффузии бора через маску SiO2 до удельного слоевого сопротивления  В качестве толстого 9 (0,3-0,5 мкм) и тонкого 2 (17-19 нм) диэлектрика использовался термически выращенный диоксид кремния. Проводящие шины 1 второго уровня создавались из тонкой пленки сплава вольфрам-титан (10% титана) толщиной 0,16 мкм со слоевым сопротивлением около

В качестве толстого 9 (0,3-0,5 мкм) и тонкого 2 (17-19 нм) диэлектрика использовался термически выращенный диоксид кремния. Проводящие шины 1 второго уровня создавались из тонкой пленки сплава вольфрам-титан (10% титана) толщиной 0,16 мкм со слоевым сопротивлением около  Выбор именно вольфрама связан с высокой температурой его плавления, а также с тем, что в данном случае от шины второго уровня требуется выполнение традиционной для вольфрама функции - эмиттера электронов. Изолирующие щели 3 формировались прецизионным жидкостным травлением тонкого слоя диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Для обеспечения омического контакта к подложке n-типа диффузией фосфора формировались n+-области. В качестве токоподвода как к р-шинам, так и к n-подложке использовались тонкопленочные проводники из сплава алюминий-кремний (1% кремния). Чипы, содержащие экспериментальные образцы матрицы памяти, разваривались в металлостеклянные корпуса, которые не герметизировались (крышка корпуса могла свободно сниматься).

Выбор именно вольфрама связан с высокой температурой его плавления, а также с тем, что в данном случае от шины второго уровня требуется выполнение традиционной для вольфрама функции - эмиттера электронов. Изолирующие щели 3 формировались прецизионным жидкостным травлением тонкого слоя диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Для обеспечения омического контакта к подложке n-типа диффузией фосфора формировались n+-области. В качестве токоподвода как к р-шинам, так и к n-подложке использовались тонкопленочные проводники из сплава алюминий-кремний (1% кремния). Чипы, содержащие экспериментальные образцы матрицы памяти, разваривались в металлостеклянные корпуса, которые не герметизировались (крышка корпуса могла свободно сниматься).

Электроформовка и переключения состояний ячеек матрицы выполнялись в вакууме (10-4-10-3 Па), создаваемом паромасляным насосом, при этом молекулы вакуумного масла могли участвовать в образовании проводящей среды в изолирующих щелях элементов матрицы. В процессе электроформовки на ячейки матрицы подавались импульсы напряжения прямой полярности специальной формы, после чего проводимость каждой ячейки увеличивалась приблизительно на 4 порядка, а статические ВАХ для прямых напряжений были близки к показанным на фиг.7, и качественно аналогичны сглаженным кривым фиг.4. Как видно из фиг.7, пороговые напряжения Uth для переключения из состояния OFF в состояние ON составляли около 4 В, а напряжение Umax максимума N-образной ВАХ лежит около 5 В, т. е. эти параметры приблизительно на 1 В больше, чем для электроформованной структуры металл-изолятор-металл (фиг.4), что соответственно ужесточает требования к выпрямляющим свойствам ячейки.

Как показали специальные эксперименты по выполнению электроформовки для тех же ячеек матрицы памяти в безмасляном вакууме (в этом случае они помещались в рабочий объем сверхвысоковакуумной установки УСУ-4), электроформовка развивалась аналогичным образом, но происходила при несколько больших начальных напряжениях. При этом ВАХ, характеризующие конечное состояние ячеек, были аналогичны показанным на фиг.7. Поскольку в данном случае поступление в изолирующую щель органических молекул исключалось, материалом с переменной проводимостью могли служить только поверхностные слои диэлектрика изолирующей щели, т. е. диоксида кремния. Ясно, что эти же процессы должны происходить и в «масляном» вакууме, в этом случае в качестве материала с переменной проводимостью, меняющейся при прохождении через него потока электронов, служит некоторый композит диоксида кремния и поступающих из газовой фазы углеродсодержащих молекул вакуумного масла. Таким образом, в полученных и описанных ниже характеристиках ячейки матрицы памяти определенную роль играет тот факт, что поверхность изолирующей щели выполнена из диоксида кремния.

Данные о функционировании экспериментальных образцов матрицы памяти, демонстрирующие возможности записи, стирания, считывания, хранения информации и выборки произвольной ячейки в различных режимах, приведены ниже и иллюстрируются фиг.8-12, на которых показаны ВАХ всех ячеек матрицы в различных состояниях. Символами W1, W2, W3 обозначены вольфрамовые шины матрицы, a P1, P2, Р3 - перпендикулярные им шины р-кремния. Каждая ВАХ соответствует ячейке, находящейся на пересечении одной из вольфрамовых шин с одной из кремниевых шин. Измерялись токи в цепи вольфрамовых шин в зависимости от напряжения между шинами р-кремния и вольфрама, которое менялось со скоростью 0,5 В/с. В процессе измерений и переключений на р-n-переходе поддерживалось постоянное обратное напряжение, равное 2 В. Во время измерений образцы размещались в «масляном» вакууме (давление 5·10-4 Па) всегда, кроме специально оговоренных случаев.

1. Начальные состояния элементов матрицы. После изготовления и выполнения электроформовки, ВАХ ячеек матрицы имели вид, показанный на фиг.8, т. е. все ячейки находились в высокопроводящем состоянии (ON). Все ВАХ имеют хорошо выраженный вентильный характер, причем обратные напряжения, соответствующие значительному увеличению обратного тока (напряжения пробоя), находятся в диапазоне от 2 до 4 В. Эти напряжения слабо зависят от концентрации бора в шине р-кремния, а низкие их значения связаны, очевидно, с локальным усилением электрического поля в обедненном поверхностном слое кремния 4 (фиг.5) под «нанолезвием» проводящего материала 5, которое и приводит к преждевременному пробою в сравнении с обычным барьером Шоттки. Тем не менее этих напряжений хватило для реализации индивидуальной выборки ячейки в режиме записи (см. ниже).

2. Параллельное переключение в состояние OFF (стирание). Эта операция, выполняющая функцию стирания информации, возможна только параллельно сразу для всех ячеек столбца (строки) матрицы, поскольку требует приложения напряжения более 10 В, в то время как обратные напряжения пробоя каждой ячейки не превышают 2-4 В. В данном случае переключение осуществлялось прямоугольным импульсом напряжения прямой полярности амплитудой 13,7 В и длительностью 100 мкс с длительностью фронтов 1 мкс.

3. Считывание информации. При неразрушающем считывании информации амплитуда подаваемых напряжений не должна быть более 2-3 В, поскольку она не должна превышать пороговое напряжение образования проводящей среды Ufr≈Uth (фиг.4). Практически достаточно величины 1-2 В. Поэтому индивидуальная выборка ячейки матрицы в режиме считывания не представляет проблемы. ВАХ элементов в режиме считывания после выполнения операции стирания показаны на фиг.9. Как видно, все ячейки находятся в состоянии OFF.

4. Индивидуальное переключение в состояние ON (запись). При записи информации должна обеспечиваться индивидуальная выборка каждой ячейки матрицы. Несмотря на низкие обратные напряжения пробоя, выборка любого элемента матрицы становится возможной, поскольку переключение в высокопроводящее состояние требует приложения напряжения Umax величиной всего 5 В. На фиг.10 показаны ВАХ, отражающие процесс такого переключения как индивидуального (элемент W2-P2), так и попарного (элементы W1-P1, W3-P1 и W1-P3, W3-P3). При этом на шины матрицы подавались следующие напряжения:

- выбираемая шина р-кремния - треугольный импульс положительного напряжения UPW с амплитудой 5 В и скоростью развертки 0,5 В/с;

- остальные шины р-кремния занулялись;

- выбираемые вольфрамовые шины - занулялись (в их цепях измерялся ток);

- остальные вольфрамовые шины - напряжение UWW=UPW-1,5 В;

- подложка n-кремния - напряжение USW=UPW+2 В.

При таком алгоритме на всех ячейках матрицы, кроме выбираемых, напряжения не превышают порогового напряжения Uth, поэтому переключений в них не происходит.

5. Считывание информации. На фиг.11,а показаны ВАХ всех ячеек матрицы в режиме считывания после выполнения записи. Состояние матрицы соответствует информации, записанной на предыдущей операции (пункт 4). На фиг.11,б отдельно приведены ВАХ элементов матрицы, находящихся в состоянии OFF, в другом масштабе токов. Как видно, проводимости ячеек в состояниях ON и OFF отличаются на 3-4 порядка.

На фиг.12 приведена аналогичная серия ВАХ той же матрицы после 5 циклов считывания в таком же режиме, как иллюстрация неразрушающего характера последнего.

6. Многократное считывание. Считывание информации выполнялось также на воздухе с использованием электронного блока контроля состояния структур. Последний представлял собой автономный блок, формирующий импульсы напряжения амплитудой 1,5 В и длительностью 100 мкс. При этом переключения невозможны, если образец находится не только в вакууме, но и на воздухе, поскольку разогрев проводящей среды в изолирующем зазоре элемента памяти недостаточен для ее окисления кислородом воздуха. Информация о состоянии ячеек матрицы индицировалась светодиодами, выведенными на переднюю панель блока. В качестве пороговой величины, разделяющей состояния ON и OFF, использовалось значение тока элемента 70 нА. Каждый элемент опрашивался с частотой 25 Гц.

Было выполнено более 107 циклов считывания. Состояния матрицы (101, 010, 101) при этом не изменились, что иллюстрирует как возможность надежной выборки каждого элемента при считывании, так и неразрушающий характер последнего даже на воздухе.

В приведенной серии экспериментов основной целью было продемонстрировать возможность выборки произвольной ячейки матрицы в различных режимах и не ставилась задача измерения максимального быстродействия матрицы при выполнении отдельных операций. Минимальные времена переключения были измерены на отдельных (не объединенных в матрицу) элементах такой же конструкции. Переключение из состояния OFF в состояние ON требовало длительности прямоугольного импульса напряжения не менее нескольких мкс при амплитуде 5-6 В. Для переключения из состояния ON в состояние OFF получены длительности вплоть до 50 нс при амплитуде 8-14 В, причем это значение было связано с ограничениями используемой аппаратуры, т. е. реально эти времена могут быть еще меньше.

Отдельно были выполнены испытания элементов матрицы памяти на стабильность ВАХ при длительном хранении с отключенным питанием. Элементы матрицы в состоянии ON и OFF хранились на воздухе в комнатных условиях, и через определенные промежутки времени снимались ВАХ в режимах, аналогичных п.3 «Считывание информации». В течение более двух лет наблюдений существенных изменений ВАХ для обоих состояний не было обнаружено.

Таким образом, приведенные данные демонстрируют для предложенной ячейки матрицы памяти полный набор функций, необходимых для ее использования в качестве энергонезависимого электрически перепрограммируемого запоминающего устройства.

Предлагаемая матрица памяти апробирована в Институте микроэлектроники и информатики РАН (г. Ярославль).

Источники информации, принятые во внимание:

1. Косарев Ю.А., Виноградов С.В. Электрически изменяемые ПЗУ. Л.: Энергоатомиздат. 1985. 80 с.

2. Мордвинцев В.М., Левин В.Л. Элемент устройства памяти со структурой металл-изолятор-металл // Патент РФ. №2072591. 1997.

3. Валиев К.А., Кудрявцев С.Б., Левин В.Л., Мордвинцев В.М., Савасин В.Л. Память на основе нано-МИМ-диода с углеродистой активной средой // Микроэлектроника. 1997. Т. 26. №1. С.3-11.

4. Мордвинцев В.М., Кудрявцев С.Е. Условия формирования единичной проводящей наноструктуры при электроформовке // ЖТФ. 2002. Т. 72. Вып.4. С.53-59.

5. Pagnia H., Sotnik N. Bistable Switching in Electroformed Metal-Insulator-Metal Devices // phys. stat. sol. (a). 1988. V. 108. N11. Р. 11-65.

6. Дирнлей Дж., Стоунхэм А., Морган Д. Электрические явления в аморфных пленках окислов // УФН. 1974. Т. 112. Вып.1. С.83-127.

7. Мордвинцев В. М., Левин В. Л. Модель проводимости нано-МИМ-диода с углеродистой активной средой с учетом эффектов перколяции // ЖТФ. 1999. Т. 69. Вып.11. С.66-73.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА МАТРИЦЫ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2005 |

|

RU2302058C2 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| ЭЛЕМЕНТ ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2016 |

|

RU2637175C2 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

| Способ электроформовки при изготовлении элемента памяти | 2020 |

|

RU2769536C1 |

| ЯЧЕЙКА ПАМЯТИ СО СТРУКТУРОЙ ПРОВОДЯЩИЙ СЛОЙ-ДИЭЛЕКТРИК-ПРОВОДЯЩИЙ СЛОЙ | 2007 |

|

RU2376677C2 |

| УСТРОЙСТВО ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2008 |

|

RU2374704C1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| СПОСОБ ФОРМИРОВАНИЯ ПРОВОДЯЩЕГО ЭЛЕМЕНТА НАНОМЕТРОВЫХ РАЗМЕРОВ | 2001 |

|

RU2194334C1 |

| Электрически перепрограммируемый запоминающий прибор | 2016 |

|

RU2618959C2 |

Использование: изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии. Сущность изобретения: ячейка матрицы памяти включает проводящую шину первого уровня, расположенную на подложке, электрически изолирующей ее от других проводящих шин первого уровня матрицы, перекрещивающуюся с ней проводящую шину второго уровня, разделяющий шины первого и второго уровней слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью. Проводящая шина одного из уровней выполнена из полупроводника р- или n-типа. Технический результат изобретения состоит в том, что ячейка обладает и свойствами элемента энергонезависимой электрически перепрограммируемой памяти, и выпрямляющими свойствами с характеристиками, обеспечивающими электрическую развязку ячейки в матрице, при этом размеры ячейки не увеличиваются. 5 з.п. ф-лы, 12 ил.

| ВАЛИЕВ К.А | |||

| и др | |||

| Память на основе нано-МИМ-диода с углеродистой активной средой | |||

| Микроэлектроника | |||

| Электрическое сопротивление для нагревательных приборов и нагревательный элемент для этих приборов | 1922 |

|

SU1997A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| Способ изготовления матричного накопителя для программируемого постоянного запоминающего устройства | 1977 |

|

SU765877A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

| Элемент памяти | 1988 |

|

SU1617458A1 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ - ИЗОЛЯТОР - МЕТАЛЛ | 1994 |

|

RU2072591C1 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ-ИЗОЛЯТОР-МЕТАЛЛ | 1997 |

|

RU2108629C1 |

Авторы

Даты

2005-10-27—Публикация

2004-01-09—Подача