Изобретение относится к вычислительной технике, а точнее к элементам памяти, и наиболее эффективно может быть использовано при создании статических запоминающих устройств большой информацион- ной емкости.

Известен элемент памяти, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены углубления, диэлектрические области, расположенные в углублениях в подложке, первый полупроводниковый слой второго типа проводимости, второй полупроводниковый слой первого типа проводимости, третий полупроводниковый слой второго типа проводимости, четвертый полупроводниковый слой первого типа проводимости, последовательно расположенные в приповерхностном слое полупроводниковой подложки между диэлектрическими областями [1]

Недостатком известного элемента памяти является низкое быстродействие, так как он реализует динамический принцип хранения информации. Для реализации этого принципа необходимы дополнительные затраты времени для регенерации информации.

Наиболее близким известным техническим решением к предложенному, принятым за прототип, является элемент памяти, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены углубления, первую и вторую диэлектрические области, расположенные в углублениях, первый полупроводниковый слой второго типа проводимости, расположенный в приповерхностной части полупроводниковой подложки, второй полупровод- никовый слой первого типа проводимости, расположенный в приповерхностной части первого полупроводникового слоя между первой и второй диэлектрическими областями с примыканием к ним, третий полупроводниковый слой второго типа проводимости, расположенный в приповерхностной части второго полупроводникового слоя с примыканием к первой диэлектрической области, четвертый полупроводниковый слой первого типа проводимости, расположенный на поверхности полупроводниковой подложки над третьим полупроводниковым слоем, пятый полупроводниковый слой второго типа проводимости, расположенный на поверхности четвертого полупроводникового слоя, причем, в четвертом и пятом полупроводниковых слоях выполнено отверстие, диэлектрический слой, расположенный на дне и стенках отверстия (электронная техника [2]

Недостатком известного элемента памяти является низкое быстродействие, так как данный элемент также является динамическим.

Целью изобретения является повышение быстродействия элемента памяти.

Поставленная цель достигается тем, что элемент памяти, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены первое и второе углубление, первую и вторую диэлектрические области, первый полупроводниковый слой второго типа проводимости, второй полупроводниковый слой первого типа проводимости, третий полупроводниковый слой второго типа проводимости, четвертый и пятый полупроводниковые слои соответственно первого и второго типов проводимости, диэлектрический слой, дополнительно содержит проводящий слой, размещенный в отверстиях на поверхности диэлектрического слоя, причем отверстия выполнены над границей второго и третьего полупроводниковых слоев, первый полупроводниковый слой расположен между первой и второй диэлектрическими областями, примыкая к ним, четвертый полупроводниковый слой расположен над вторым и третьим диэлектрическими слоями соответственно первого и второго типа проводимости. По сравнению с известным элементом памяти предложенный имеет следующие новые существенные признаки: наличие проводящего слоя на диэлектрическом слое в отверстии, расположение четвертого полупроводникового слоя на втором, выполнение отверстия над границей второго и третьего полупроводниковых слоев.

Расположение четвертого полупроводникового слоя над вторым позволяет осуществить контакт анода диода и базы тиристора, так как эти слои имеют один тип проводимости. Этот контакт необходим для выключения тиристора.

Наличие проводящего слоя и расположение отверстия над границей второго и третьего полупроводниковых слоев необходимо для формирования МДП-транзистора (сток третий полупроводниковый слой, исток пятый полупроводниковый слой с одной стороны от отверстия, подложка четвертый полупроводниковый слой с той же стороны от отверстия, затвор проводящий слой и МДП конденсатора (первая обкладка проводящий слой, вторая обкладка четвертый полупроводниковый слой с другой стороны от отверстия и второй полупроводниковый слой). МДП-транзистор необходим для управления током через тиристор в различных режимах работы, а МДП-конденсатор необходим для включения тиристора.

В совокупности эти признаки обеспечивают статический принцип хранения информации элементов памяти, а следовательно, и более высокое его быстродействие по сравнению с известным, так как не требуется время для регенерации информации.

Эти признаки не были обнаружены авторами в доступной патентной и технической литературе, поэтому авторы считают, что предложенное техническое решение соответствует критерию изобретения "неочевидность".

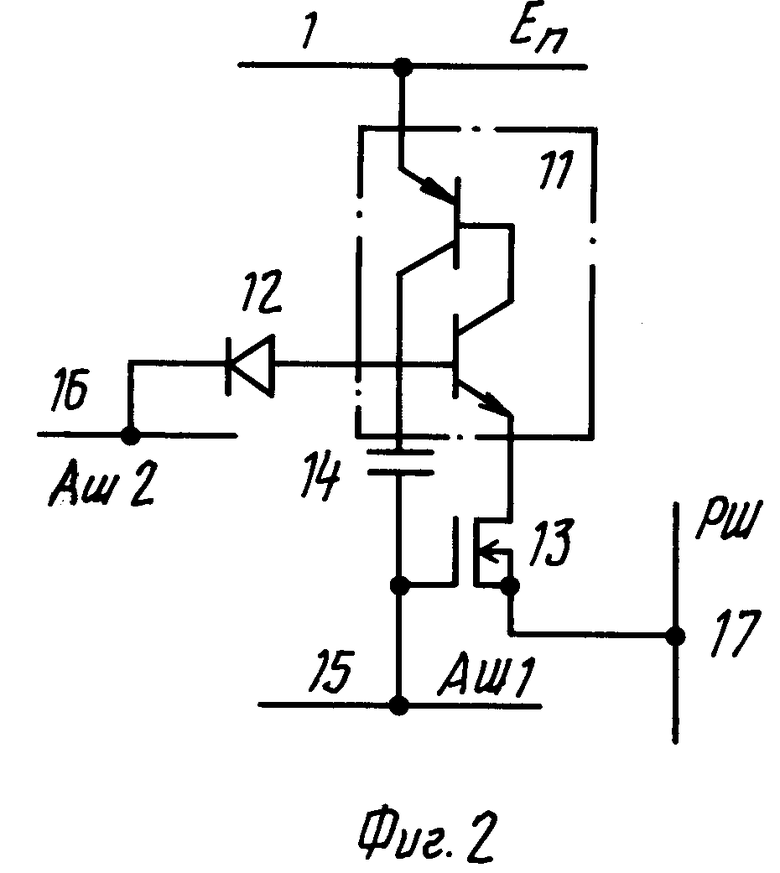

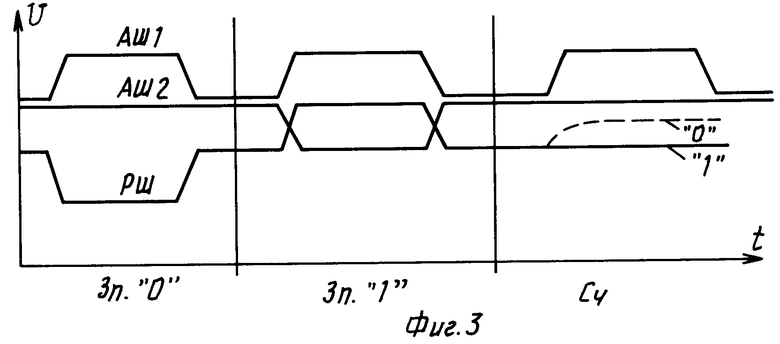

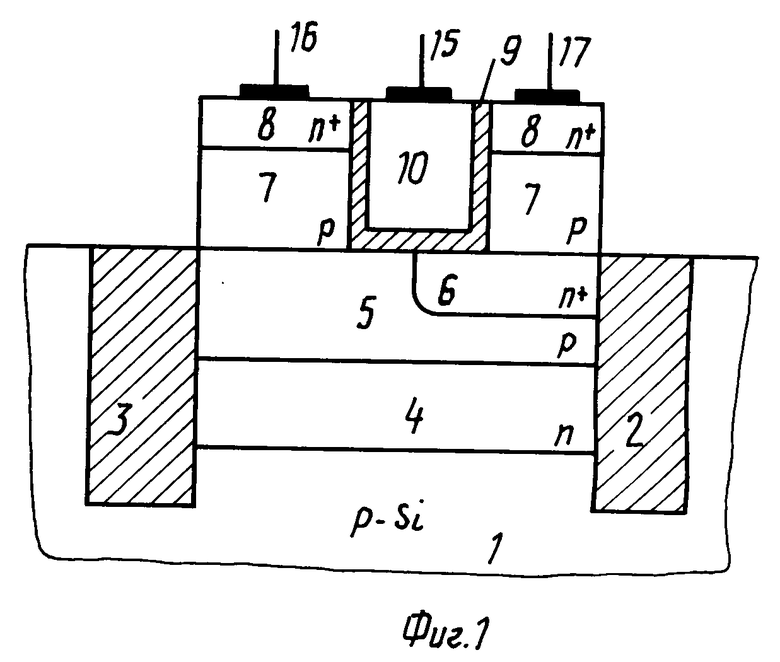

На фиг.1 представлена структура элемента памяти в разрезе; на фиг.2 его эквивалентная электрическая схема; на фиг.3 временные диаграммы его работы.

Элемент памяти содержит полупроводниковую подложку 1, первую и вторую диэлектрические области 2, 3, полупровод- никовые слои с первого по пятый 4-8, диэлектрический слой 9, проводящий слой 10.

На подложку 1 подается напряжение питания. Слои 1, 4, 5, 6 образуют тиристор 11, слои 7, 8, примыкающие к слою 5, образуют диод 12, слои 6, 7, 8, 9, 10 образуют МДП-транзистор 13, а слои 5, 7, 9, 10 МДП-конденсатор 14. Слой 10 является первой адресной шиной 15, катод диода 12 подключен к второй адресной шине 16, а исток транзистора 13 к разрядной шине 17.

Элемент памяти работает следующим образом.

Хранение информации осуществляется тиристором 11: "0" тиристор 11 включен, "1" выключен. На подложке 1 поддерживается напряжение питания Еn= 3-5 В.

В режиме хранения на адресных шинах 15, 16 поддерживается одинаковое напряжение на 1/2U* ниже напряжения питания Еn, где U* падение напряжения на прямосмещенном диоде 12. Напряжение  U* не достаточно для отпирания диода 12, если открыт тиристор 11, поэтому в этом случае через диод 12 ток не протекает. Тем более он не протекает, если тиристор 11 заперт. На разрядной шине 17 устанавливается потенциал U15-Uпор, где U15 потенциал шины 15, Uпор пороговое напряжение транзистора 13. Этим обеспечивается возможность протекания тока через тиристор 11, если он открыт.

U* не достаточно для отпирания диода 12, если открыт тиристор 11, поэтому в этом случае через диод 12 ток не протекает. Тем более он не протекает, если тиристор 11 заперт. На разрядной шине 17 устанавливается потенциал U15-Uпор, где U15 потенциал шины 15, Uпор пороговое напряжение транзистора 13. Этим обеспечивается возможность протекания тока через тиристор 11, если он открыт.

Для записи "0" (включение тиристора 11) по шине 17 подается отрицательный импульс, а по шине 15 положительный. При этом сопротивление канала транзистора 13 резко уменьшается, позволяя тем самым протекать большому току. Конденсатор 14 при этом разряжается в базу тиристора 11. Накопление в р-базе положительного заряда смещает в прямом направлении переход n-эмиттера тиристора 11, в результате чего последний включается. Увеличение тока через тиристор 11 в этот момент за счет снижения сопротивления канала транзистора 13 ускоряет процесс включения.

Для записи "1" (выключение тиристора 11) по шинам 16, 17 подаются импульсы положительной полярности, а по шине 15 отрицательной. При этом откроется диод 12, ток через него удалит заряд из р-базы тиристора 11. После этого переход n-эмиттера тиристора 11 закроется и он перейдет в запертое состояние.

Для считывания информации по шине 15 подается положительный импульс, повышающий ток через тиристор 11, если последний был открыт. В этом случае потенциал разрядной шины 17 повысится, что и должно быть зафиксировано усилителем считывания. Если же тиристор 11 был заперт, то импульс по шине 15 не вызовет изменений на шине 17. Это означает, что в элементе была записана "1".

Основным преимуществом предлагаемого элемента памяти по сравнению с известным является его более высокое быстродействие, так как он реализует статический принцип хранения информации. При этом не требуется затрат времени на регенерацию хранимой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1642888A1 |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1655242A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1983 |

|

SU1105055A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1989 |

|

SU1669307A1 |

| НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1053638A1 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2029393C1 |

| НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1987 |

|

SU1436735A3 |

| Элемент памяти | 1989 |

|

SU1600552A1 |

Изобретение относится к вычислительной технике, а точнее к элементам памяти и наиболее эффективно может быть использовано при создании статических запоминающих устройств большой информационной емкости. Элемент памяти содержит дополнительно проводящий слой 10, который совместно со слоями 6, 7, 8, 9 образует МДП-транзистор, обеспечивающий управление током, протекающим через элемент памяти. Совместно со слоями 5, 7, 8, 9 слой 10 образует МДП-конденсатор, обеспечивающий режим записи "0" в элементе памяти. Это позволяет реализовать элементом памяти статический принцип хранения информации. В результате нет необходимости тратить время на ее регенерацию. 3 ил.

ЭЛЕМЕНТ ПАМЯТИ, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены первое и второе углубления, первую и вторую диэлектрические области, расположенные в первом и втором углублениях соответственно, первый полупроводниковый слой второго типа проводимости, расположенный в приповерхностной части полупроводниковой подложки, второй полупроводниковый слой первого типа проводимости, расположенный в приповерхностной части первого полупроводникового слоя между первой и второй диэлектрическими областями с примыканием к ним, третий полупроводниковый слой второго типа проводимости, расположенный в приповерхностной части второго полупроводникового слоя с примыканием к первой диэлектрической области, четвертый и пятый полупроводниковые слои соответственно первого и второго типов проводимости, последовательно расположенные на полупроводниковой подложке, с отверстиями, выполненными соосно в четвертом и пятом полупроводниковых слоях, диэлектрический слой, расположенный на боковых поверхностях отверстий и поверхности полупроводниковой подложки, отличающийся тем, что элемент памяти содержит проводящий слой, размещенный в отверстиях на поверхности диэлектрического слоя, причем отверстия выполнены над границей второго и третьего полупроводниковых слоев, первый полупроводниковый слой расположен между первой и второй диэлектрическими областями, примыкая к ним, четвертый полупроводниковый слой расположен над вторым и третьим диэлектрическими слоями соответственно первого и второго типа проводимости.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электронная техника | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-04-10—Публикация

1992-10-20—Подача