ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Область техники, к которой относится изобретение

Описываемые здесь варианты воплощения изобретения, в общем, относятся к процессорам. В частности, описываемые здесь варианты воплощения изобретения, в общем, относятся к использованию регистров в процессорах.

Информация о предшествующем уровне техники

Многие процессоры имеют архитектуры с одним потоком команд и многими потоками данных (SIMD - архитектуры). В SIMD - архитектурах команда обработки упакованных данных (данных в упакованном формате), векторная команда или SIMD - команда могут оперировать множественными элементами данных (например, множественными парами элементов данных) одновременно (например, параллельно). Процессор может иметь аппаратное обеспечение для параллельного исполнения, отвечающее на команду обработки упакованных данных таким образом, что одновременно (например, параллельно) выполняет множественные операции.

Множественные элементы данных могут быть упакованы в пределах регистров или ячеек памяти как упакованные данные. В упакованных данных разряды регистров или других мест хранения информации могут быть логически разделены на последовательность элементов данных. Например, регистр для упакованных данных с разрядностью в 64 разряда может иметь два упакованных 32-разрядных элемента данных, четыре упакованных 16-разрядных элемента данных или восемь упакованных 8 - разрядных элементов данных.

В некоторых процессорах за эти годы имело место прогрессирующее увеличение разрядности операндов, состоящих из упакованных данных. Это увеличение разрядности операндов, состоящих из упакованных данных, вообще говоря, позволяет одновременно (например, параллельно) обрабатывать большее количество элементов данных, что, вообще говоря, ведет к повышению производительности. Например, в случае, когда используются 128-разрядные упакованные данные, одновременно может обрабатываться восемь 16-разрядных элементов данных вместо только четырех 16-разрядных элементов данных в случае 64-разрядных упакованных данных.

Однако один возможный недостаток такого использования упакованных данных с более высокой разрядностью заключается в возможном соответствующем увеличении размера регистров и регистровых файлов. Например, увеличение разрядности каждого регистра из набора 64-разрядных регистров, такое чтобы они каждый были 128-разрядными регистрами, вероятно, приблизительно удвоит размер регистров (например, площадь или занимаемое место, занимаемые регистрами на кристалле). Влияние этого, вероятно, будет даже больше в тех вариантах реализации, в которых физических регистров реализовано больше, чем архитектурных регистров, поскольку приблизительно удвоиться может размер большего количества регистров. Другой возможный недостаток такого рода увеличения размера регистров и регистровых файлов заключается в соответствующем увеличении количества данных (например, о состоянии или контексте), которые необходимо помещать в эти регистры и извлекать из них при переключениях контекста, сохранениях состояний в режимах электропитания и подобных переходах. Например, для каждого регистра может потребоваться помещать в него и извлекать из него 128 разрядов в случае регистра с разрядностью в 128 разрядов вместо только 64 разрядов в случае регистра с разрядностью в 64-разряда.

Краткое описание чертежей

Изобретение можно лучше всего понять, обратившись к нижеследующему описанию и прилагаемым к нему чертежам, которые используются для того, чтобы проиллюстрировать варианты воплощения изобретения. На чертежах:

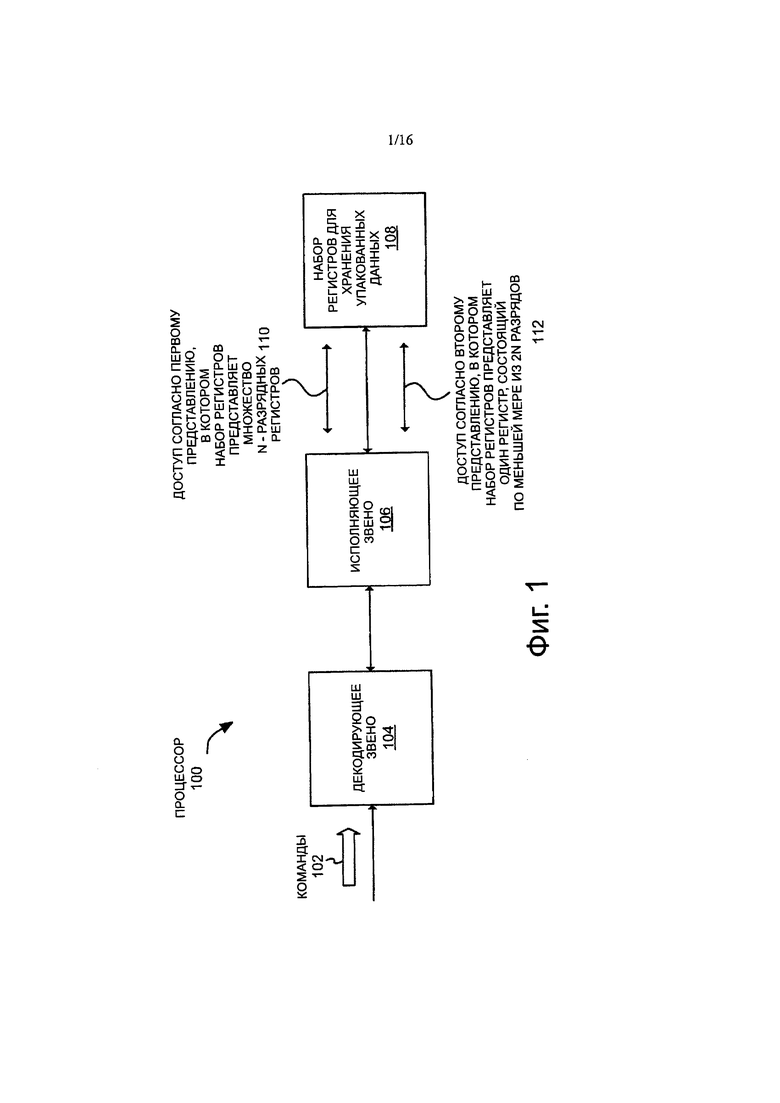

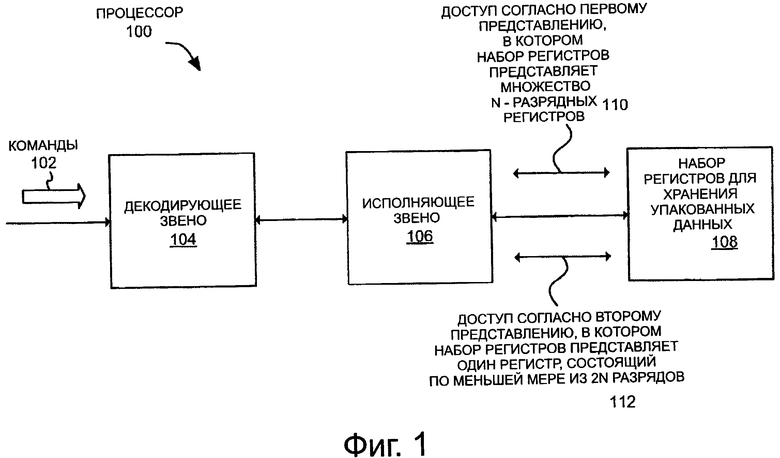

Фиг. 1 представляет собой блок-схему блок-схему одного варианта воплощения процессора.

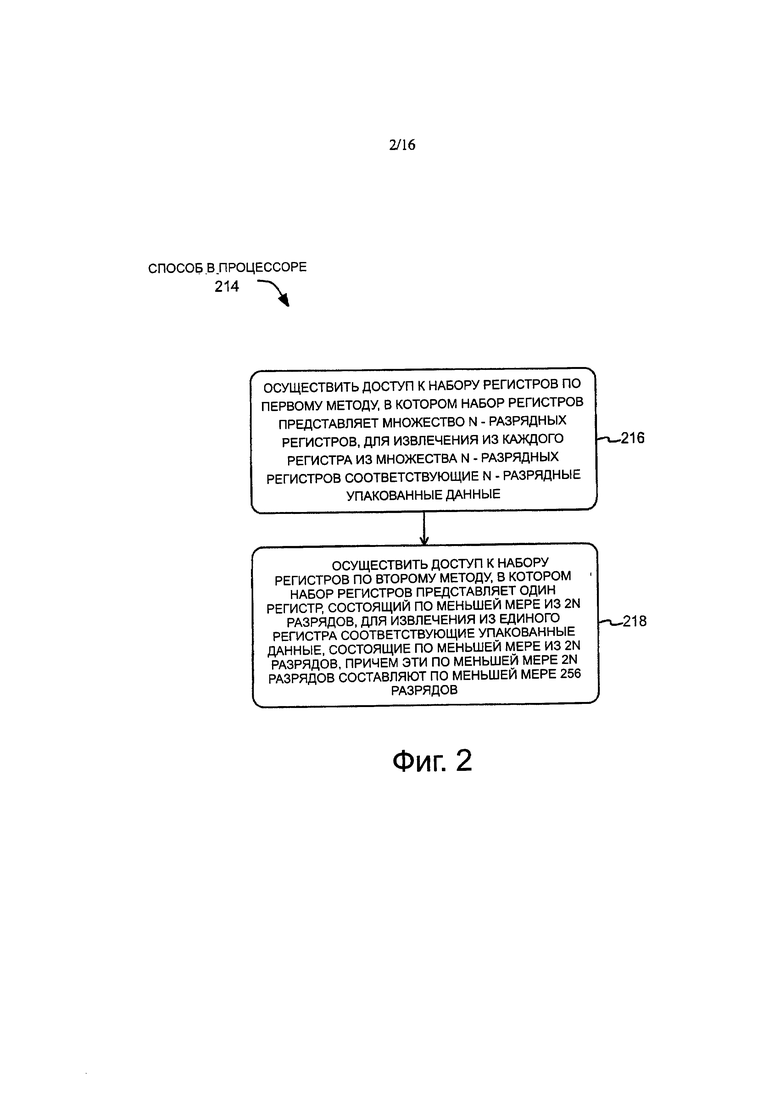

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа, выполняемого в процессоре и/или посредством процессора.

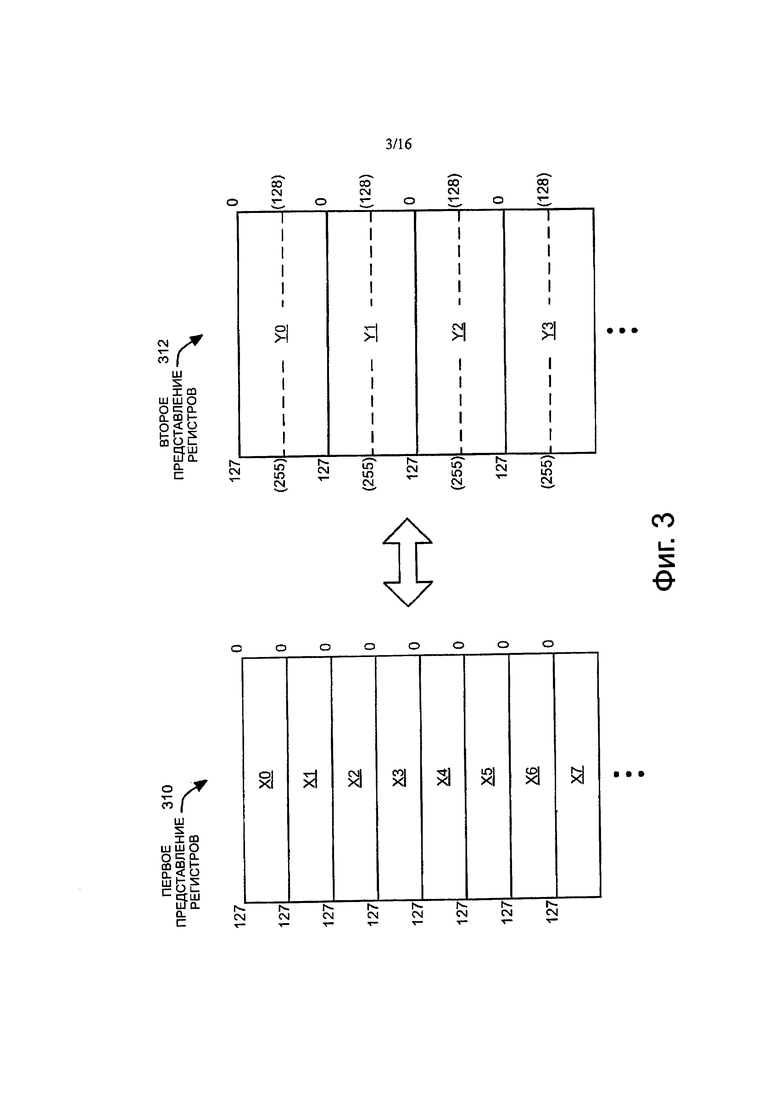

Фиг. 3 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении, и как к 256-разрядным регистрам для упакованных данных - на втором представлении.

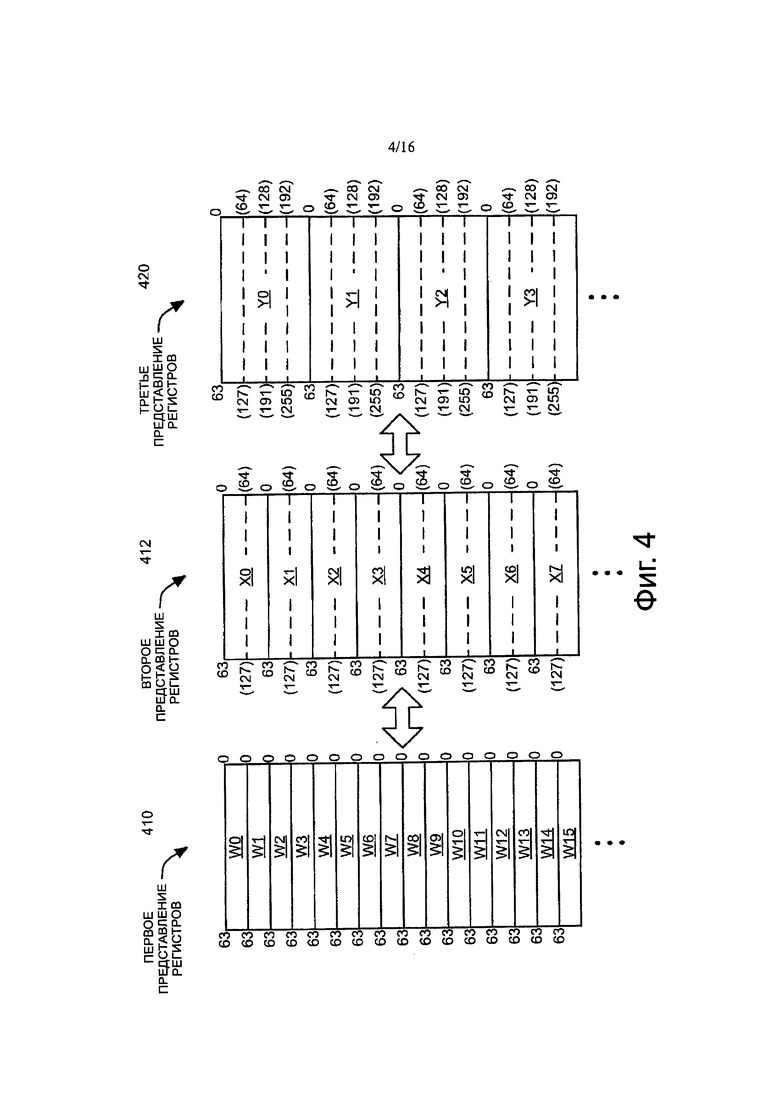

Фиг. 4 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 64-разрядным регистрам для упакованных данных - на первом представлении, как к 128-разрядным регистрам для упакованных данных - на втором представлении, и как к 256-разрядным регистрам для упакованных данных - на третьем представлении.

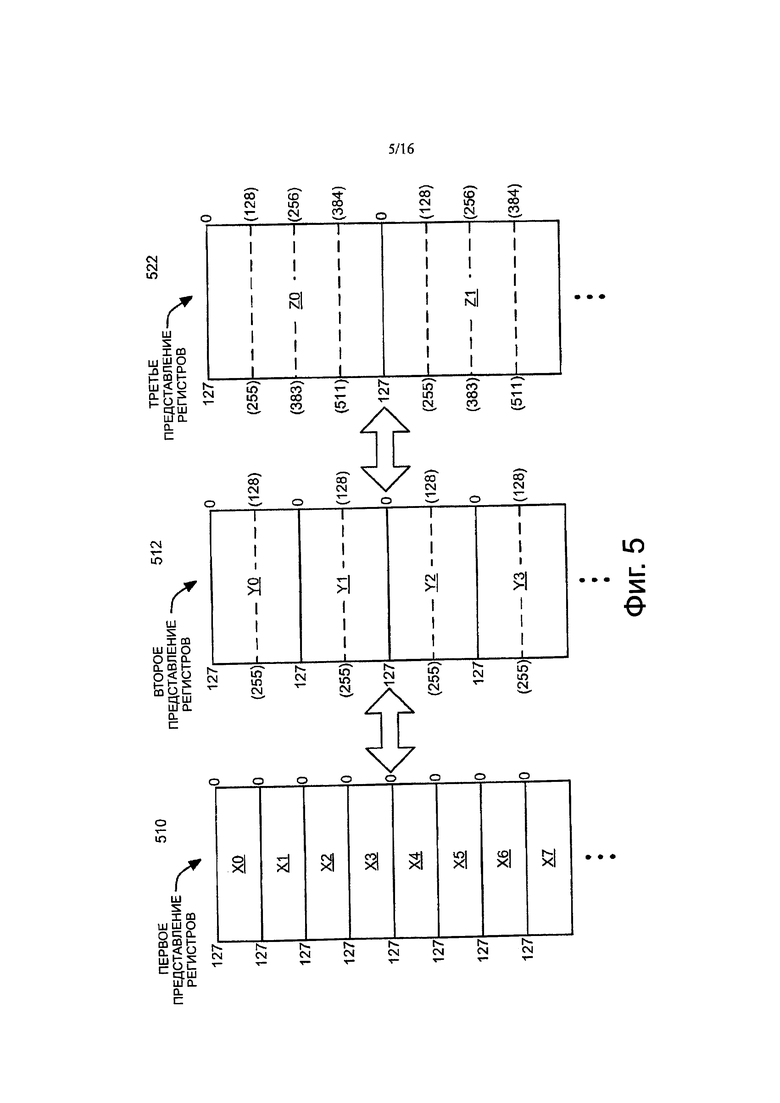

Фиг. 5 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении, как к 256-разрядным регистрам для упакованных данных - на втором представлении, и как к 512-разрядным регистрам для упакованных данных - на третьем представлении.

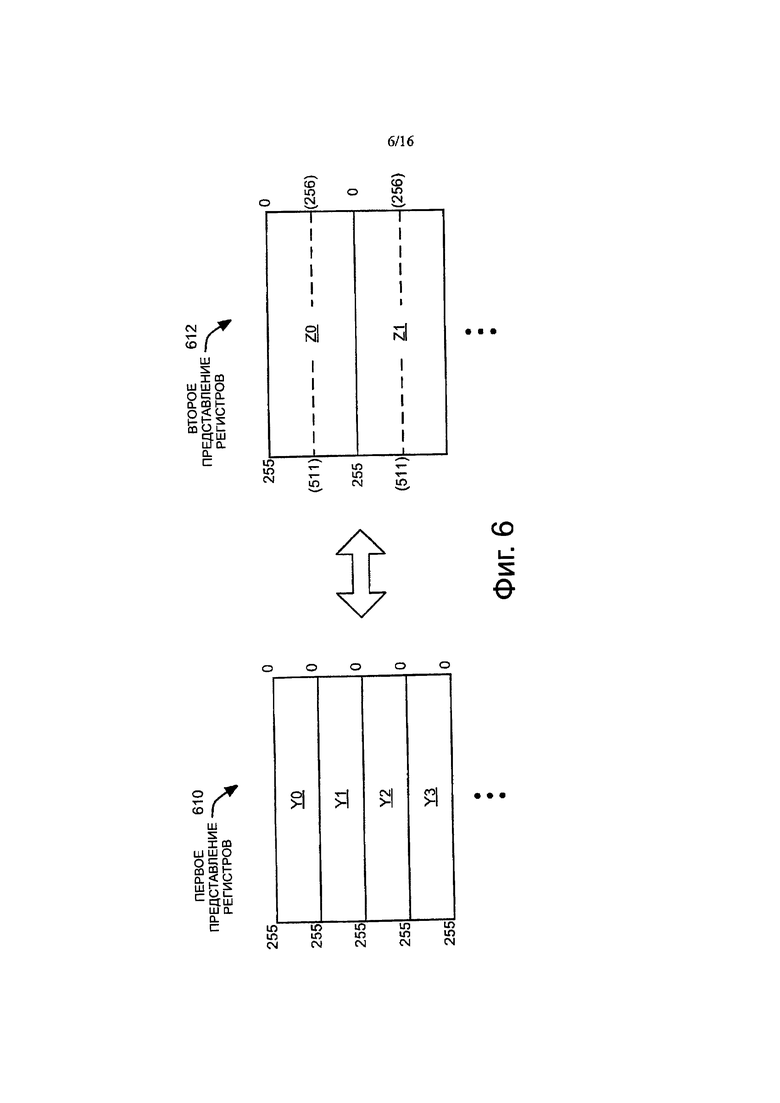

Фиг. 6 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 255-разрядным регистрам для упакованных данных - на первом представлении, и как к 512-разрядным регистрам для упакованных данных - на втором представлении.

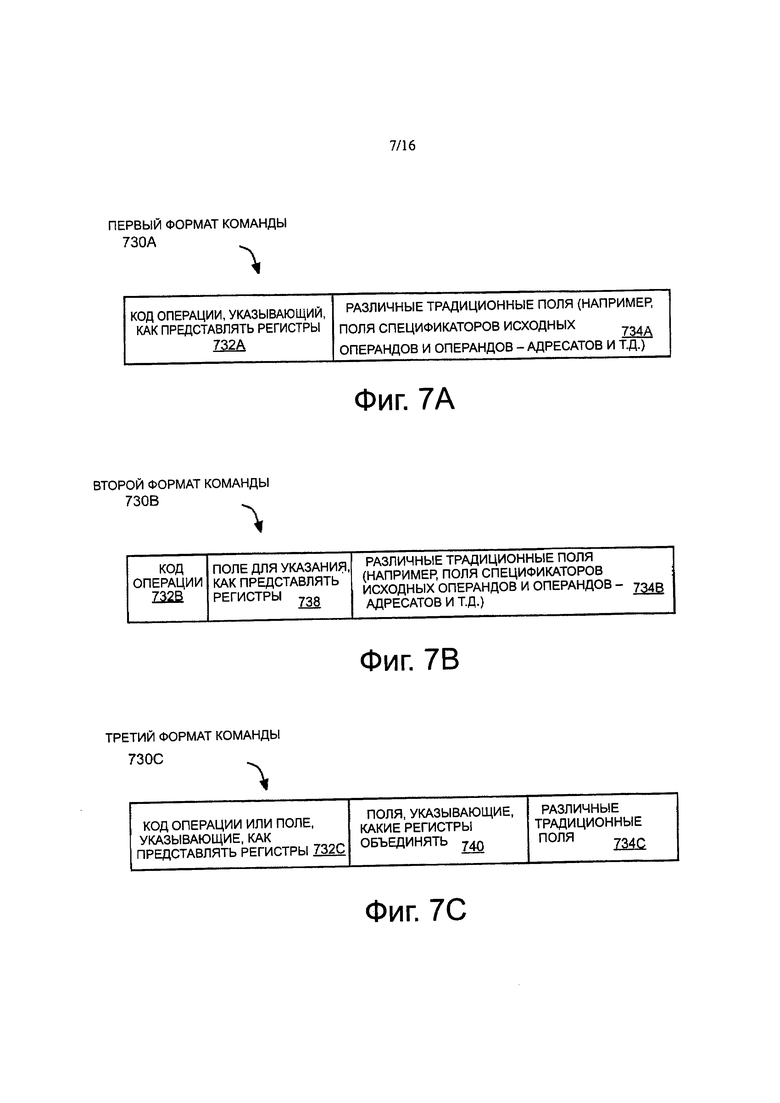

Фиг. 7А-С представляют собой блок-схемы вариантов воплощения подходящих форматов команды для использования различных представлений набора регистров.

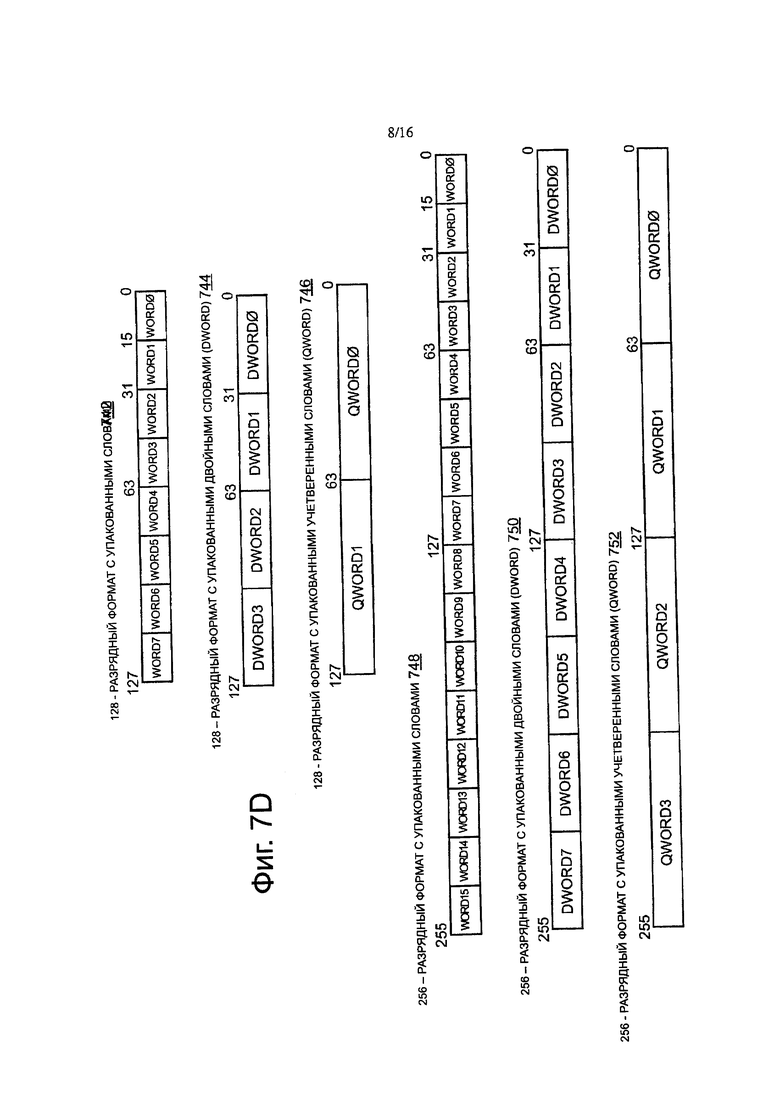

Фиг. 7D представляют собой блок-схемы примеров подходящих форматов упакованных данных.

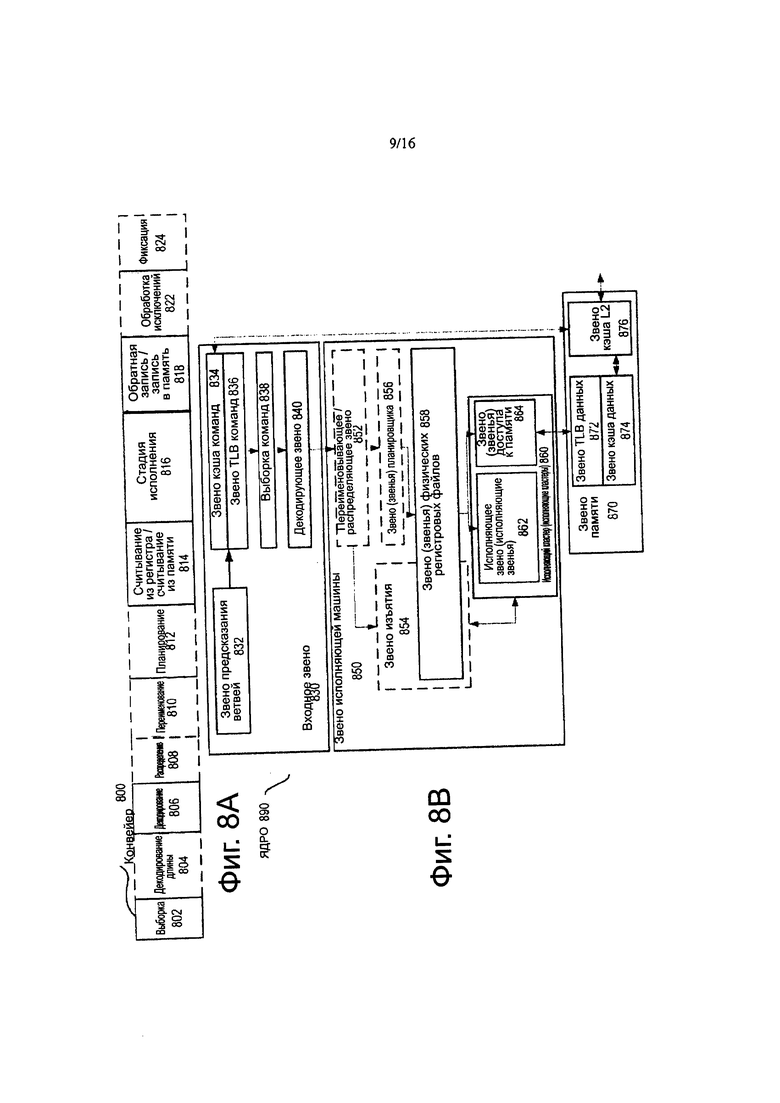

Фиг. 8А представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера конвейер без переупорядочения последовательности команд, так и приводимый в качестве примера конвейер с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, соответствующие вариантам воплощения изобретения.

Фиг. 8В представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера вариант воплощения ядра, имеющего архитектуру без переупорядочения последовательности команд, так и приводимое в качестве примера ядро, имеющее архитектуру с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, подлежащие включению в состав процессора, соответствующего вариантам воплощения изобретения.

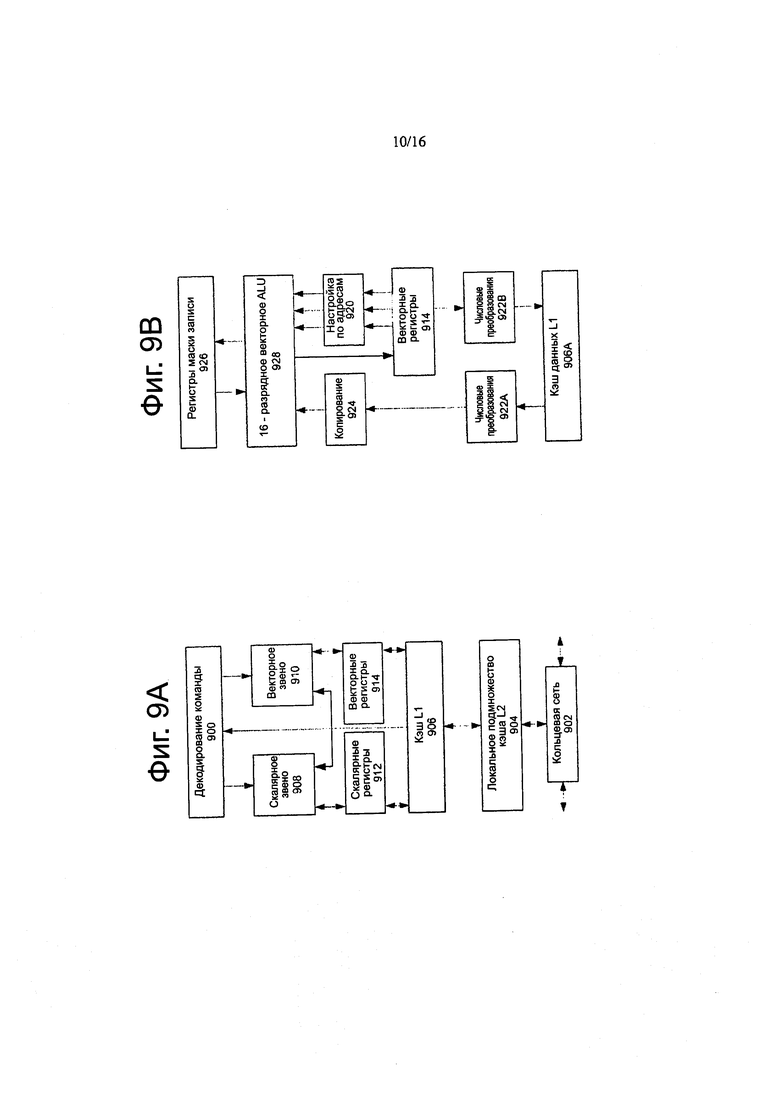

Фиг. 9А представляет собой блок-схему одиночного ядра процессора наряду с его соединением с расположенной на кристалле сетью межсоединений и с его локальным подмножеством кэша уровня 2 (L2), соответствующих вариантам воплощения изобретения.

Фиг. 9В представляет собой расширенное представление части ядра процессора, показанного на Фиг. 9А, соответствующего вариантам воплощения изобретения.

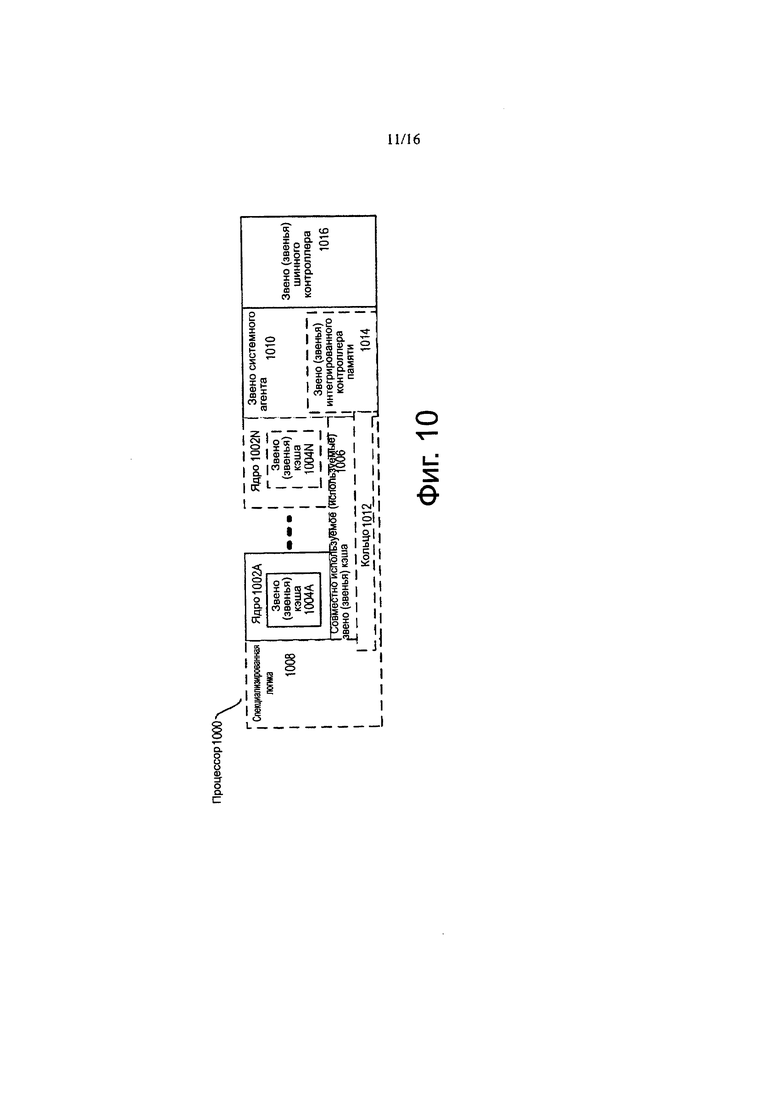

Фиг. 10 представляет собой блок-схему процессора, который может иметь больше чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированные графические средства, соответствующего вариантам воплощения изобретения.

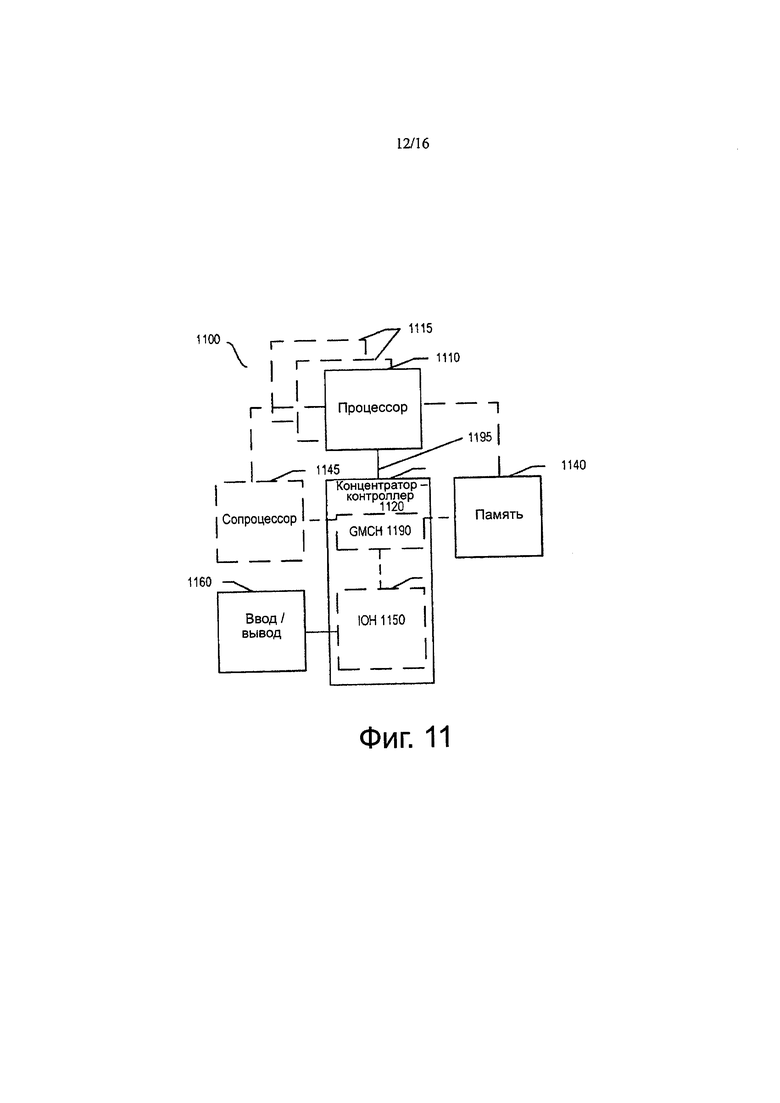

На Фиг. 11 показана блок-схема системы в соответствии с одним вариантом воплощения настоящего изобретения.

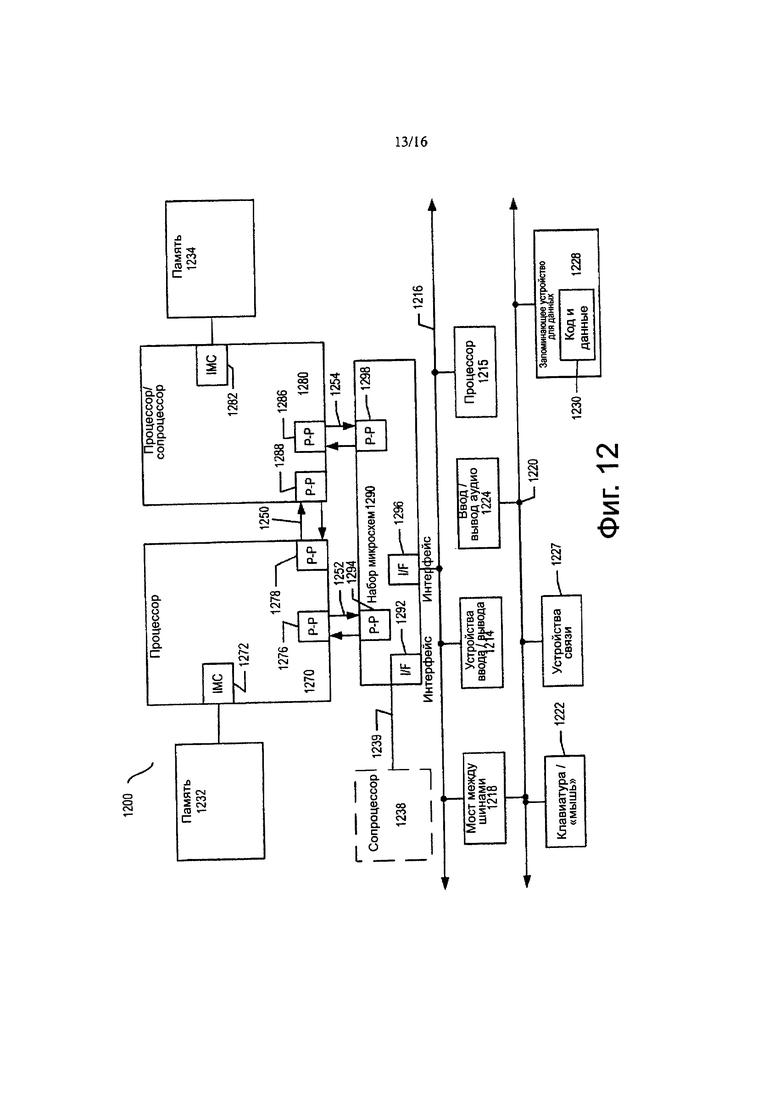

На Фиг. 12 показана блок-схема первой более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

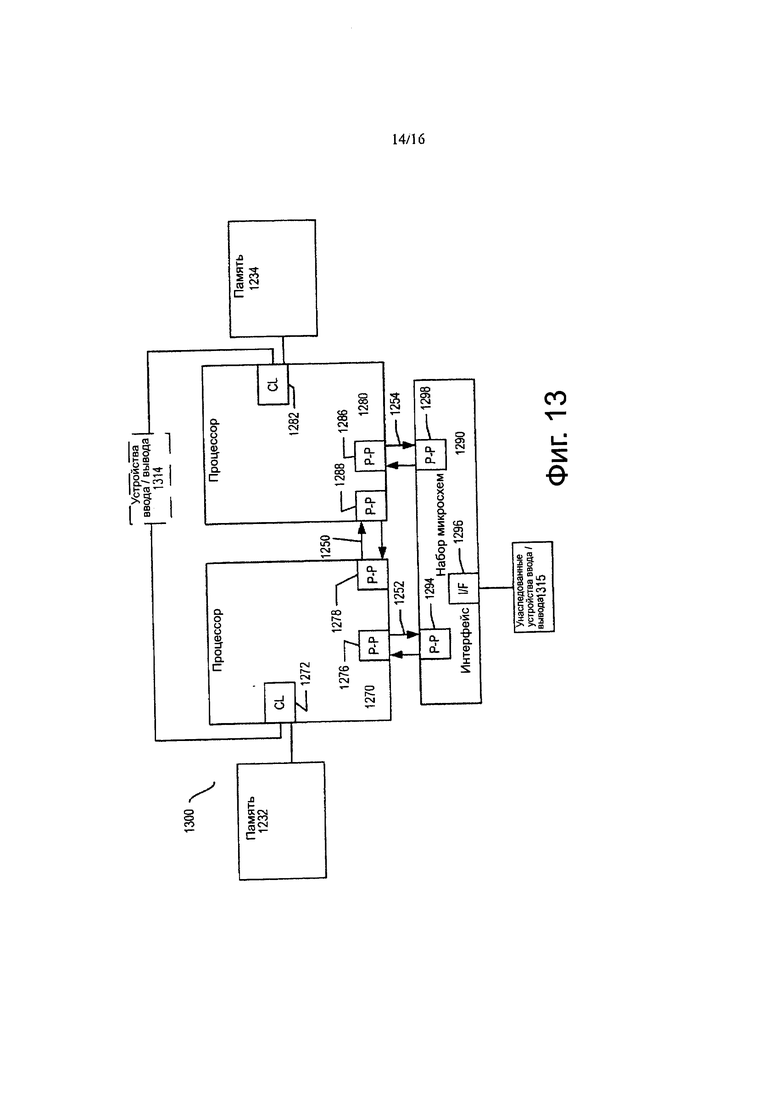

На Фиг. 13 показана блок-схема второй более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

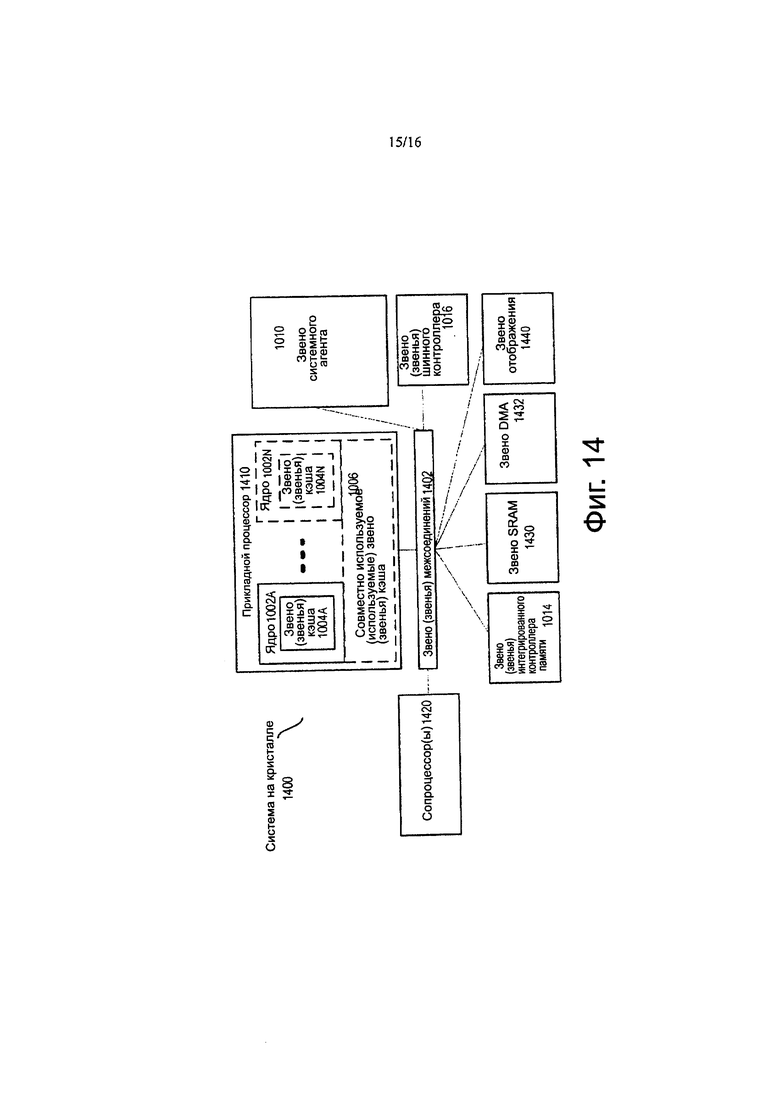

На Фиг. 14 показана блок-схема внутрикристальной системы (SoC) в соответствии с одним вариантом воплощения настоящего изобретения.

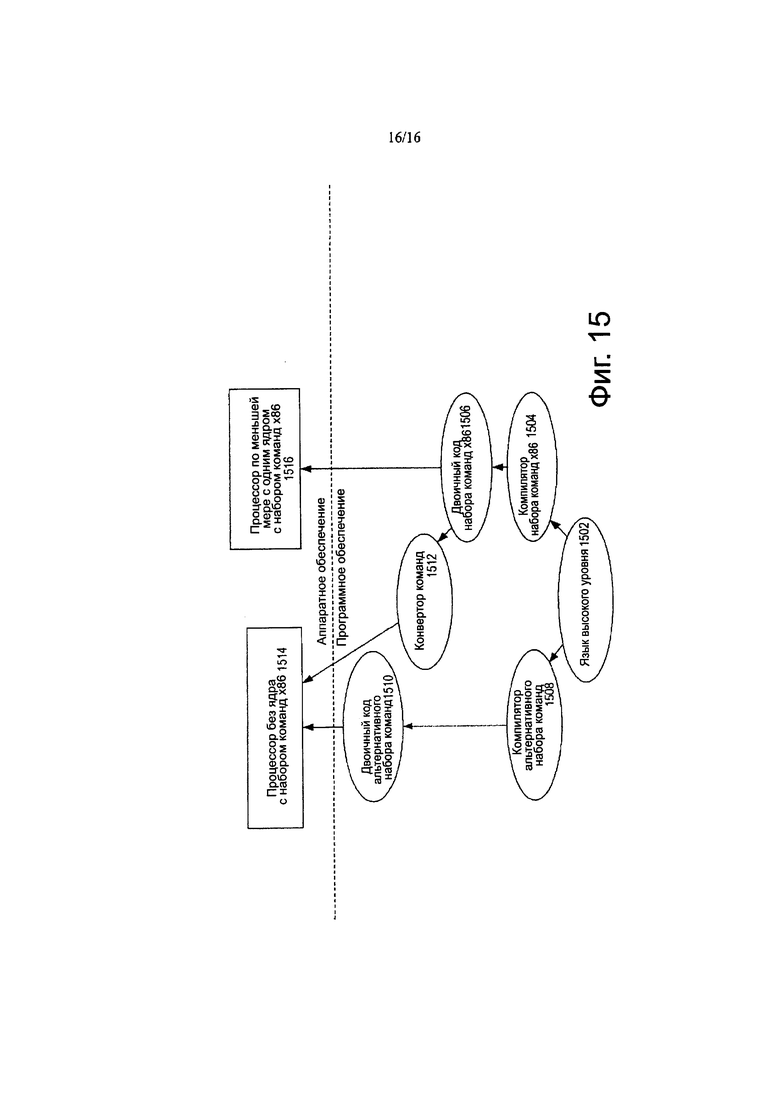

Фиг. 15 представляет собой блок-схему, на которой сравнивается использование конвертора команд, реализованного программными средствами, для того, чтобы конвертировать двоичные команды в некотором исходном наборе команд в двоичные команды в некотором заданном наборе команд в соответствии с вариантами воплощения изобретения.

Подробное описание вариантов осуществления изобретения

Здесь раскрываются процессоры, способы и системы, которые позволяют рассматривать или осуществлять доступ к набору регистров либо как к множеству относительно малых регистров, либо как к единому относительно большому регистру. В нижеследующем описании, излагаются многочисленные конкретные подробности (например, конкретные емкости регистров, количества регистров, команды и форматы, варианты реализации логики, конфигурации процессора, микроархитектурные подробности, последовательности операций, подробности разделения и интеграции логики и так далее). Однако следует понимать, что варианты воплощения изобретения могут быть осуществлены на практике без этих конкретных подробностей. В других случаях, хорошо известные схемы, конструкции и технологии не показаны подробно во избежание затруднения понимания этого описания.

Фиг. 1 представляет собой блок-схему блок-схему одного варианта воплощения процессора (100). Этот процессор представляет аппарат для обработки команд, который может быть приведен в действие для обработки команд. В некоторых вариантах воплощения изобретения, этот процессор может представлять собой универсальный процессор (например, универсальный микропроцессор, относящийся к типу, часто используемому в качестве центрального процессора (CPU) в настольном компьютере, переносном компьютере и подобных им компьютерах). В качестве альтернативы, этот процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя: сетевые процессоры, процессоры передачи данных, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровой обработки сигналов (DSP - процессоры) и контроллеры (например, микроконтроллеры), в качестве лишь нескольких примеров, но не ограничены ими. Процессор может представлять собой любой процессор из числа: разнообразных процессоров для вычислений со сложным набором команд (CISC - процессоров), разнообразных процессоров для вычислений с сокращенным набором команд (RISC - процессоров), разнообразных процессоров с командными словами сверхбольшой длины (VLIW - процессоров), разнообразных гибридов этих процессоров или других типов процессоров без каких бы то ни было исключений.

Процессор также включает в себя набор регистров (108). Каждый из регистров может представлять находящееся на процессоре и/или на кристалле место хранения информации. В некоторых вариантах воплощения изобретения, этот набор регистров может представлять регистры для упакованных данных или иным образом могут быть способны к хранению упакованных данных, векторных данных или данных для архитектуры с одним потоком команд и многими потоками данных (SIMD - данных). Регистры для упакованных данных могут быть реализованы различными методами в различных микроархитектурах с использованием хорошо известных технологий и не ограничены никаким конкретным типом схемы или механизма. Подходящими являются всевозможные различные типы регистров. Примеры подходящих типов регистров включают в себя: выделенные физические регистры, динамически распределяемые физические регистры с использованием переименования регистров и их сочетания, но не ограничены этим.

Процессор может принимать команду (102), которая указывает по меньшей мере один регистр, реализованный на наборе (108) регистров на или иным образом с ним связанный. Эта команда может представлять команду в машинном коде, команду на языке ассемблера, макрокоманду или управляющий сигнал набора команд процессора. Эта команда может явным образом специфицировать (например, посредством некоторого набора разрядов или одного или более полей), или иным образом указывать (например, неявно указывать) этот по меньшей мере один регистр (например по меньшей мере один исходный операнд и/или операнд - адресат (для занесения результата)). В качестве одного примера, команда может специфицировать единственный используемый регистр в качестве исходного операнда, и этот единственный регистр либо может также использоваться в качестве операнда - адресата, либо команда может дополнительно специфицировать отличный от него операнд - адресат. В качестве другого примера, команда может специфицировать некоторый первый регистр, используемый в качестве первого исходного операнда, и некоторый второй регистр, используемый в качестве второго исходного операнда, и один из этих регистров, специфицированных для исходных операндов, либо может также использоваться в качестве операнда-адресата, или команда может дополнительно специфицировать отличный от них операнд-адресат. Это только несколько иллюстративных примеров. Объем изобретения не ограничен конкретным типом команды, если эта команда указывает по меньшей мере один регистр, связанный с этим набором регистров. Примеры подходящих типов команд включают в себя: команды арифметических операций над упакованными данными (например, команды сложения упакованных данных, команды умножения упакованных данных и так далее), команды логических операций над упакованными данными (например, команды циклического сдвига упакованных данных, команды сдвига упакованных данных, команды сравнения упакованных данных, команды операции "логическое ИЛИ" над упакованными данными и так далее), команды доступа к памяти, относящиеся к упакованным данным, (например, команды сбора данных, команды на разнесение данных и так далее), в качестве лишь нескольких примеров, но не ограничены ими.

Процессор включает в себя звено (104) декодирования команд. Звено (104) декодирования команд может также упоминаться как декодирующее звено, декодер или декодирующая логика. Декодирующее звено может принимать и декодировать команды относительно более высокого уровня (например, команды в машинном коде, команды на языке ассемблера, макрокоманды), и выводить одну или более команд относительно более низкого уровня или управляющие сигналы (например, микрокоманды, микрооперации, точки входа в микрокод), которые отражают, представляют команды более высокого уровня и/или выведены из них. Эти одна или более команд более низкого уровня или управляющие сигналы могут реализовывать команду более высокого уровня посредством одной или более операций более низкого уровня (например, уровня схемы или уровня аппаратного обеспечения). Декодирующее звено может быть реализовано с использованием всевозможных различных механизмов, включающих в себя: постоянные запоминающие устройства для микрокода (ROM-устройства), таблицы поиска, аппаратные варианты реализации, программируемые логические матрицы (PLA-матрицы) и другие механизмы, используемые для реализации декодирующих звеньев, известные в данной области техники, но не ограниченных этими механизмами. В других вариантах воплощения изобретения, вместо декодирующего звена или в дополнение к нему могут быть использованы эмулятор, транслятор, блок трансформации, интерпретатор команд или другая логика конвертирования команд.

Вновь обратимся к Фиг. 1, на которой с декодирующим модулем (104) и с набором (108) регистров сопряжено исполняющее звено (106). В качестве примера, это исполняющее звено может включать в себя: арифметическое устройство, логическое устройство, арифметико-логическое устройство (ALU), цифровую схему или логику для того, чтобы выполнять арифметические и логические операции, исполняющее звено для памяти, или тому подобное. Исполняющее звено может принимать одну или более декодированных или иначе конвертированных команд или один или более управляющих сигналов, которые представляют команду (102) и/или выведены из нее. Исполняющее звено и/или процессор могут специальную или особую логику (например, транзисторы, схемы или другое аппаратное обеспечение, возможно, объединенное с микропрограммным обеспечением (например, командами, хранящимися в энергонезависимой памяти) и/или программным обеспечением), которая способна функционировать таким образом, чтобы выполнять операции в ответ на команду (102) (например, в ответ на одну или более команд или один или более управляющих сигналов, декодированных или иным образом выведенных из команды (102)).

В некоторых вариантах воплощения изобретения, исполняющее звено способно функционировать в ответ на команду (102) и/или в ее результате таким образом, чтобы осуществлять доступ к набору (108) регистров либо в одном, либо в обоих по меньшей мере из двух различных методов (доступа) или представлений регистров. В некоторых вариантах воплощения, эти, по меньшей мере два различных метода или представления могут включать в себя некоторый первый метод или представление (110), в котором набор (108) регистров должны рассматриваться в качестве множества N-разрядных регистров или иным образом представлять это множество. В некоторых вариантах воплощения изобретения, эти по меньшей мере два различных пути или представления могут включать в себя некоторый второй метод или представление (112), в котором этот набор регистров должны рассматриваться в качестве единого регистра, состоящего из по меньшей мере 2N разрядов или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, эти по меньшей мере 2N разрядов могут представлять собой по меньшей мере 256 разрядов. В других вариантах воплощения изобретения, этот набор регистров может представлять собой N-разрядные регистры (например, 128-разрядные регистры, 256-разрядные регистры и так далее). В некоторых вариантах воплощения изобретения, этот набор регистров может представлять собой N/2 - разрядные регистры (например, 64-разрядные регистры, 128-разрядные регистры и так далее).

В качестве одного конкретного примера, набор (108) регистров может состоять из двух N-разрядных регистров (например, 128-разрядных регистров). В первом методе или представлении (110), эти два N-разрядных регистра (например, 128-разрядных регистра) могут рассматриваться в качестве двух N-разрядных (например, 128-разрядных) регистров или иным образом представлять эти регистры. Во втором методе или представлении (112), эти два N-разрядных регистра (например, 128-разрядные регистры) могут рассматриваться в качестве единого регистра, состоящего по меньшей мере из 2N разрядов (например, 256 разрядов, 512 разрядов и так далее) или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, может иметься больше, чем только два различных представления или метода осуществления доступа к набору (108) регистров. Например, в некоторых вариантах воплощения изобретения, может иметься три, четыре или больше чем четыре различных метода осуществления доступа или представления набора (108) регистров. Например, в некоторых вариантах воплощения изобретения, в этом примере может дополнительно поддерживаться осуществление доступа к набору регистров как к четырем N/2-разрядным регистрам (например, 64-разрядным регистрам).

В качестве другого конкретного примера, набор (108) регистров может состоять из четырех N/2-разрядных регистры (например, 64-разрядных регистров). В первом методе или представлении (110), эти четыре N/2-разрядных регистра (например, 64-разрядных регистра) могут рассматриваться в качестве двух N-разрядных (например, 128-разрядных) регистров или иным образом представлять эти регистры. Во втором методе или представлении (112), эти четыре N/2-разрядных регистра (например, 64-разрядных регистра) могут рассматриваться в качестве единого регистра, состоящего по меньшей мере из 2N-разрядов (например, 256 разрядов, 512 разрядов, 1024 разрядов и так далее) или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, может иметься по меньшей мере третий метод осуществлять доступ к набору (108) регистров. Например, в некоторых вариантах воплощения изобретения, во втором представлении (112) исполняющее звено может рассматривать четыре N/2 - разрядных регистра (например, 64-разрядных регистра) или осуществлять к ним доступ как к единому регистру, состоящему по меньшей мере из 4N-разрядов (например, 512 разрядов, 1024 разрядов и так далее), и процессор может дополнительно поддерживать осуществления доступа или представление набора (108) регистров в качестве множества 2N-разрядных регистров (например, из 256 разрядов).

В некоторых вариантах воплощения изобретения, в каждом из представлений набора (108) регистров и/или методов осуществления доступа к набору (108) регистров, рассматриваемые или подвергающиеся доступу регистры для упакованных данных, могут быть видимыми для программного обеспечения и/или программиста и/или могут быть специфицированы командами из набора команд (например, макрокомандами, командами в машинном коде, командами на языке ассемблера и так далее) для идентификации операндов. Иногда регистры, специфицированные командами из набора команд, упоминаются в данных областях техники как архитектурно видимые регистры или архитектурные регистры, которые противопоставляются другим неархитектурным или архитектурно невидимым регистрам в некоторой заданной микроархитектуре (например, регистрам временного хранения, используемым для осуществления команды и так далее).

Как было показано в этих детализированных примерах, в некоторых вариантах воплощения изобретения, процессор может быть способным функционировать таким образом, чтобы распознавать, рассматривать и/или осуществлять доступ к набору (108) регистров либо как к множественным относительно малым регистрам (например, N-разрядным регистрам), или как к единому относительно большому регистру (например, регистру, имеющему по меньшей мере 2N разрядов). Например, в некоторых вариантах воплощения изобретения, смежная пара регистров может рассматриваться по отдельности в качестве 128-разрядные регистры или может быть логически "объединена" вместе и рассматриваться вся вместе как единый 256-разрядный регистр. Те же самые физические регистры и то же самое физическое суммарное количество разрядов могут входить в состав как этих двух 128-разрядных регистров, так и в единый 256-разрядный регистр, но они могут рассматриваться различными методами. Полезно, что в некоторых вариантах воплощения изобретения, такого рода подход может быть использован для того, чтобы избежать необходимости повышения разрядности этих регистров, в то же самое время позволяя все-таки повысить разрядность регистра для упакованных данных и/или разрядность операнда, состоящего из упакованных данных. Избегание повышения разрядности этих регистров может помочь избежать, или по меньшей мере уменьшить некоторые из возможных недостатков, упомянутых в разделе "Предшествующий уровень техники", например, увеличения площади или занимаемого места регистров на кристалле и/или увеличения количества данных, которое необходимо помещать в регистры и извлекать из них при переключениях контекста. В некоторых вариантах воплощения изобретения, такого рода подход может быть использован для реализации регистров для упакованных данных или операндов, состоящих по меньшей мере из 256 разрядов (например, 256 разрядов, 512 разрядов, 1024 разрядов и так далее), по причине чего вышеупомянутые возможные недостатки имеют тенденцию становиться даже еще более значительными.

Во избежание затруднения понимания описания, на чертеже показан и описан относительно простой процессор (100). В других вариантах воплощения изобретения, процессор, если требуется, может включать в себя другие хорошо известные компоненты, находящиеся в процессорах. Примеры таких компонентов включают в себя: звено предсказания ветвей, звено выборки команд, буферы быстрого преобразования адресов команд и данных, буферы предварительной выборки, очереди микрокоманд, задатчики последовательностей микрокоманд, звено переименования регистров, звено планирования команд, звено изъятия, другие компоненты, входящие в состав процессоров, и разнообразные их сочетания, но не ограничены этими компонентами. Имеются без преувеличения многочисленные различные сочетания и конфигурации компонентов в процессорах, и варианты воплощения изобретения не ограничены никаким конкретным сочетанием или конфигурацией. Варианты воплощения изобретения могут быть включены в состав процессоров, иметь множественные ядра, логические процессоры или, механизмы исполнения, по меньшей мере один из которых включает в себя или использует раскрываемый здесь вариант воплощения изобретения.

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа (214), выполняемого внутри или посредством процессора. В некоторых вариантах воплощения изобретения, операции и/или способ, показанные на Фиг. 2, могут быть выполнены посредством или внутри процессора, показанного на Фиг. 1. Подробности и дополнительные признаки, описанные выше для процессора, показанного на Фиг. 1, также, если требуется, применяются к операциям и/или способу, показанным на Фиг. 2, которые могут быть выполнены посредством и/или внутри такого рода процессора. В качестве альтернативы, операции и/или способ, показанные на Фиг. 2, могут быть выполнены посредством и/или внутри схожего или другого процессора. Помимо этого, процессор, показанный на Фиг. 1, может выполнять операции и/или способы, одинаковые с теми, что показаны на Фиг. 2, сходные с ними или отличные от них.

Способ включает в себя, на этапе 216, осуществление доступа к набору регистров по некоторому первому методу. В некоторых вариантах воплощения изобретения, в первом методе этот набор регистров может представлять некоторое множество N-разрядных регистров. Доступ может осуществляться для того, чтобы извлечь из каждого регистра из этого множества N-разрядных регистров соответствующие N-разрядные упакованные данные (или сохранить в каждом регистре из этого множества N-разрядных регистров соответствующие N-разрядные упакованные данные).

Способ включает в себя, на этапе 218, осуществление доступа к этому набору регистров по некоторому второму, другому, методу. В некоторых вариантах воплощения изобретения, во втором методе этот набор регистров может представлять единый регистр, состоящий по меньшей мере из 2N разрядов. Доступ может осуществляться для того, чтобы извлечь из этого единого регистра соответствующие упакованные данные, состоящие по меньшей мере из 2N разрядов, (или сохранить в этом едином регистре соответствующие упакованные данные, состоящие по меньшей мере из 2N разрядов). В некоторых вариантах воплощения изобретения, эти по меньшей мере 2N разрядов могут представлять собой по меньшей мере 256 разрядов.

В других вариантах воплощения изобретения, этот способ может, если требуется, включать в себя осуществление доступа к набору регистров по меньшей мере по третьему другому методу, а в некоторых случаях также и по четвертому другому методу. В некоторых вариантах воплощения изобретения, один из этих методов может обращаться с этими регистрами как с единым регистром, имеющим разрядность, составляющую по меньшей мере 512 разрядов.

Фиг. 3 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении (310), и как к 256-разрядным регистрам для упакованных данных - на втором представлении (312). На первом представлении (310) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к восьми 128-разрядным регистрам для упакованных данных, помеченным как Х0-Х7. На втором представлении (312) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 256-разрядным регистрам, помеченным как Y0-Y3. На втором представлении (312) самые младшие 128 разрядов (то есть разряды 127 : 0) 256-разрядного регистра (Y0) отображаются на 128-разрядный регистр (Х0) или соответствуют ему, тогда как самые старшие 128 разрядов (то есть разряды 127 : 64) 256-разрядного регистра (Y0) отображаются на 128-разрядный регистр (XI) или соответствуют ему. Аналогичным образом, каждый из других 256-разрядных регистров (Y1)-(Y3) включает в себя отличную от других пару 128-разрядных регистров (Х2)-(Х7). Множественные (в этом случае два) малые (в этом случае 128-разрядные) регистры логически объединяются или группируется для того, чтобы сформировать единый большой (в этом случае 256-разрядный) регистр. В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы другие разрядности.

Предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. В проиллюстрированном варианте воплощения, логически объединяются или группируются смежные 128-разрядные регистры (например, Х0 объединяется с X1, Х2 объединяется с Х3 и так далее). В других вариантах воплощения изобретения, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В проиллюстрированном варианте воплощения изобретения, показаны восемь 128-разрядных регистров (Х0-Х7) и четыре 256-разрядных регистра (Y0-Y3), хотя при желании, можно, если требуется, использовать либо меньшее, либо большее количество регистров. В одном приводимом в качестве примера варианте воплощения изобретения, может иметься достаточно регистров для того, чтобы рассматривать по меньшей мере шестнадцать 128-разрядных регистров (или по меньшей мере тридцать два 128-разрядных регистра) на первом представлении (310), и/или достаточно регистров для того, чтобы рассматривать по меньшей мере восемь 256-разрядных регистров (или по меньшей мере шестнадцать 128-разрядных регистров) на втором представлении (312). Помимо этого, в других вариантах воплощения изобретения, могут поддерживаться три или большее количество представлений, на которых набор регистров рассматриваются в качестве 64-разрядных регистров, 512-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 4 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 64-разрядным регистрам для упакованных данных - на первом представлении (410), как к 128-разрядным регистрам для упакованных данных - на втором представлении (412), и как к 256-разрядным регистрам для упакованных данных - на третьем представлении (420). На первом представлении (410) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к шестнадцати 64-разрядным регистрам для упакованных данных, помеченным как W0-W15.

На втором представлении (412) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 128-разрядным регистрам, помеченным как Х0-Х7. На втором представлении (412) самые младшие 64 разряда (то есть разряды 63 : 0) 128-разрядного регистра (Х0) соответствуют 64-разрядному регистру (W0), тогда как самые старшие 64 разряда (то есть разряды 127 : 64) 128-разрядного регистра (Х0) соответствуют 64-разрядному регистру (WI). Помимо этого, на втором представлении (412) самые младшие 64 разряда (то есть разряды 63 : 0) 128-разрядного регистра (X1) соответствуют 64-разрядному регистру (W2), тогда как самые старшие 64 разряда (то есть разряды 127 : 64) 128-разрядного регистра (X1) соответствуют 64-разрядному регистру (W3).

На третьем представлении (420) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем 256-разрядным регистрам, помеченным как Y0-Y3. На третьем представлении (420) самые младшие 64 разряда (то есть разряды 63 : 0) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W0), самые младшие промежуточные 64 разряда (то есть разряды 127 : 64) 256-разрядного регистра (Y0) соответствуют, 64-разрядному регистру (W1), самые старшие промежуточные 64 разряда (то есть разряды 191 : 128) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W2), и самые старшие 64 разряда (то есть разряды 255 : 192) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W3). Если взглянуть на это по-другому, то на третьем представлении (420) самые младшие 128 разрядов (то есть разряды 127 : 0) 256-разрядного регистра (Y0) соответствуют 128-разрядному регистру (Х0), а самые старшие 128 разрядов (то есть разряды 255 : 128) 256-разрядного регистра (Y0) соответствуют 128-разрядному регистру (Х0).

В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы и другие разрядности. Как и ранее, предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. Например, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В качестве другого примера, могут быть использованы другие количества регистров. Помимо этого в других вариантах воплощения изобретения, могут поддерживаться другие представления, на которых набор регистров рассматриваются в качестве 512-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 5 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении (510), как к 256-разрядным регистрам для упакованных данных - на втором представлении (512), и как к 512-разрядным регистрам для упакованных данных - на третьем представлении (522). На первом представлении (510) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к восьми 128-разрядным регистрам для упакованных данных, помеченным как Х0-Х7. На втором представлении (512) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 256-разрядным регистрам, помеченным как Y0-Y3. Эта конфигурация может быть сходной с подходом, показанным и описанным для Фиг. 3.

На третьем представлении (522) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к двум 512-разрядным регистрам, помеченным как Z0-Z1. На третьем представлении (522) самые младшие 128 разрядов (то есть разряды 127 : 0) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х0), самые младшие промежуточные 128 разрядов (то есть разряды 255 : 128) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (X1), самые старшие промежуточные 128 разрядов (то есть разряды 383 : 256) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х2), и самые старшие 128 разрядов (то есть разряды 511 : 384) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х3). Если взглянуть на это по-другому, то на третьем представлении (522) самые младшие 256 разрядов (то есть разряды 255 : 0) 512-разрядного регистра (Z0) соответствуют 256-разрядному регистру (Y0), а самые старшие 256 разрядов (то есть разряды 511 : 256) 512-разрядного регистра (Z0) соответствуют 256-разрядному регистру (Y1). Аналогичным образом, каждый из других регистров имеет аналогичное соответствие, как это показано метками разрядов.

В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы, другие разрядности. Как и ранее, предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. Например, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В качестве другого примера, могут быть использованы другие количества регистров. Помимо этого в других вариантах воплощения изобретения, могут поддерживаться другие представления, на которых набор регистров рассматриваются в качестве 64-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 6 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 255-разрядным регистрам для упакованных данных - на первом представлении (610), и как к 512-разрядным регистрам для упакованных данных - на втором представлении (612). На первом представлении (610) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к четырем 255-разрядным регистрам для упакованных данных, помеченным как Y0-Y3. На втором представлении (612) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к двум (то есть имеющимся в два раза меньшем количестве) 512-разрядным регистрам, помеченным как Z0-Z3. На втором представлении (612) самые младшие 255 разрядов (то есть разряды 255 : 0) 512-разрядного регистра (Z0) соответствуют 255-разрядному регистру (Y0), а самые старшие 255 разрядов (то есть разряды 511 : 256) 512-разрядного регистра (Z0) соответствуют 256-разрядному регистру (Y1). Аналогичным образом, каждый из других регистров имеет аналогичное соответствие, как это показано метками разрядов.

В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры, 128-разрядные регистры или 256-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы другие разрядности. Как и ранее, предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. Например, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В качестве другого примера, могут быть использованы другие количества регистров. Помимо этого в других вариантах воплощения изобретения, могут поддерживаться другие представления, на которых набор регистров рассматриваются в качестве 64-разрядных регистров, 128-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 7А-С представляют собой блок-схемы вариантов воплощения подходящих форматов команды для использования различных представлений набора регистров. Фиг. 7А представляет собой блок-схему первого варианта воплощения подходящего формата (730А) команды. В этом варианте воплощения изобретения, формат команды имеет код операции или opcode (732А), который способен функционировать таким образом, чтобы указывать то, как следует рассматривать набор регистров или осуществлять к нему доступ при обработке этой команды. Традиционно, код операции может представлять множество разрядов или одно или более полей, которые способны функционировать таким образом, чтобы идентифицировать команду и/или операцию, подлежащую выполнению. В некоторых вариантах воплощения изобретения, код операции может также явным образом специфицировать или неявно указывать то, каким образом следует рассматривать набор регистров или осуществлять к нему доступ при обработке этой команды. Например, некоторые коды операции и/или операции могут неявным образом использовать набор регистров некоторым заданным способом. Например, код операции для операции умножения упакованных данных, выполняемой на 128-разрядных исходных регистрах может неявным образом указывать на то, что для того, чтобы сохранять полные произведения, которые имеют размер, в два раза превышающий размер исходных элементов данных, адресат должен рассматриваться как 256-разрядный регистр.

Формат команды также включает в себя любое из разнообразных традиционных полей (734А) в зависимости от конкретного типа команды. Примеры таких традиционных полей включают в себя: одно или более полей для того, чтобы специфицировать один или более исходных операндов, и/или одно или более полей для того, чтобы специфицировать один или более операндов - адресатов, но не ограничиваются ими. Эти операнды могут представлять регистры, как здесь описано, ячейки памяти или другие места хранения данных. Исходные операнды и/или операнды - адресаты могут также быть указаны командой неявным образом, вместо того, чтобы быть специфицированными явным образом. Помимо этого, регистр или другое место хранения данных для исходного операнда могут быть повторно использованы для операнда - адресата. Другие примеры традиционных полей включают в себя: один или более непосредственных операндов, поле для указания маски операции над упакованными данными (например, маски, используемой для предикации), поле для управления предикацией или маскированием, поле для управления пересылкой, поле для управления округлением значений с плавающей запятой и другие традиционные поля, известные в данной области техники, но не ограничиваются ими.

Фиг. 7В представляет собой блок-схему второго варианта воплощения подходящего формата (730В) команды. В этом варианте воплощения изобретения, формат команды имеет код операции или opcode (732В). В некоторых вариантах воплощения изобретения, формат команды также имеет заранее выделенное поле (738) для того, чтобы указывать то, как следует рассматривать набор регистров или осуществлять доступ к нему при обработке этой команды. В этом варианте воплощения изобретения, поле (738) может быть отдельным от или отличным от кода операции. В некоторых вариантах воплощения изобретения, это поле может включать в себя единственный разряд для выбора между любым из двух различных представлений набора регистров. В качестве альтернативы, это поле может иметь два или больше разрядов для выбора между более чем двумя различными представлениями регистров. Разрешение указывать в команде представление (например, либо посредством кода операции, либо посредством отдельного выделенного поля) может позволить указать в команде представление и может помочь избежать необходимости выполнять смену режима. В качестве альтернативы, программное обеспечение (например, операционная система, гипервизор и так далее) может изменять режим работы для логического процессора для того, чтобы указывать представление. Формат команды также включает в себя любое из разнообразных традиционных полей (734В) в зависимости от конкретного типа команды. Ранее описанные традиционные поля являются подходящими.

Фиг. 7С представляет собой блок-схему третьего варианта воплощения подходящего формата (730С) команды. Как показано на фигуре, в некоторых вариантах воплощения изобретения, формат команды может иметь код (732С) операции, который способен функционировать таким образом, чтобы указывать то, как следует рассматривать набор регистров или осуществлять к нему доступ при обработке этой команды. В качестве альтернативы, формат команды может иметь выделенное поле, аналогичное полю во втором формате команды, показанном на Фиг. 7В. Формат команды также включает в себя одно или более полей для указания того, какие регистры из набора подлежат объединению для создания относительно больших регистров. В различных вариантах воплощения изобретения это может быть сделано разнообразными методами. В одном варианте воплощения изобретения, могут быть введены поля для того, чтобы явным образом специфицировать два 128-разрядных регистра или четыре 64-разрядных регистра, подлежащих объединению для создания единого 256-разрядного регистра. В других вариантах воплощения изобретения, могут быть использованы одно или более полей для того, чтобы делать выбор между различными предварительно заданными методами объединения регистров. Например, один метод состоял бы в том, чтобы использовать смежные регистры, другой метод состоял бы в том, чтобы использовать каждый второй регистр, и еще один метод состоял бы в том, чтобы использовать последовательные регистры в различных блоках регистров. Формат команды также включает в себя любое из разнообразных традиционных полей (734С) в зависимости от конкретного типа команды. Ранее описанные традиционные поля являются подходящими.

Это только несколько примеров подходящих форматов команды. Следует понимать, что в любой из этих форматов команды, если требуется, быть добавлены дополнительные поля. Помимо этого, как было упомянуто, содержание может быть указано неявным образом вместо того, чтобы быть специфицированным явным образом. Хотя вышеприведенное обсуждение относится к полям, следует понимать, что нет необходимости, чтобы поля включали в себя последовательности разрядов, но, вместо этого, могут, если требуется, быть сформированы из несмежных разрядов. Поля, если требуется, могут также перекрываться. В дополнение к этому, проиллюстрированный порядок/расположение полей является только иллюстративным, и в других вариантах воплощения изобретения эти поля могут быть перемещены или переустроены.

Фиг. 7D представляет собой блок-схему, иллюстрирующую примеры подходящих форматов упакованных данных. На этих иллюстрациях, числа поверх прямоугольников представляют позиции разрядов. 128-разрядный формат (842) с упакованными словами имеет разрядность в 128 разрядов и включает в себя восемь элементов данных, являющихся словами с разрядностью в 16-разрядов, помеченных на иллюстрации в направлении от позиции самого младшего к позиции самого старшего разряда как: WORD0 - WORD7. 128-разрядный формат (844) с упакованными двойными словами имеет 128 разрядов и включает в себя четыре элемента данных, являющихся 32-разрядными двойными словами, помеченных в направлении от позиции самого младшего к позиции самого старшего разряда как: DWORD0 - DWORD3. 128-разрядный формат (846) с упакованными учетверенными словами имеет 128 разрядов и включает в себя два элемента данных, являющихся 64-разрядными учетверенными словами, помеченных в направлении от позиции самого младшего к позиции самого старшего разряда как: QWORD0 - QWORD1.

256-разрядный формат (848) с упакованными словами имеет разрядность в 128 разрядов и включает в себя шестнадцать элементов данных, являющихся словами с разрядностью в 16-разрядов, помеченных на иллюстрации в направлении от позиции самого младшего к позиции самого старшего разряда как: WORD0 - WORD15. 256-разрядный формат (850) с упакованными двойными словами имеет 256 разрядов и включает в себя восемь элементов данных, являющихся 32-разрядными двойными словами, помеченных в направлении от позиции самого младшего к позиции самого старшего разряда как: DWORD0 - DWORD7. 128-разрядный формат (852) с упакованными учетверенными словами имеет 256 разрядов и включает в себя четыре элемента данных, являющихся 64-разрядными учетверенными словами, помеченных в направлении от позиции самого младшего к позиции самого старшего разряда как: QWORD0 - QWORD3.

Также подходящими являются и другие форматы упакованных данных. Например, другие подходящие 128-разрядные и 256-разрядные форматы упакованных данных включают в себя форматы с упакованными 8-разрядными байтами, форматы с упакованными 32-разрядными данными с обычной точностью с плавающей запятой и форматы с упакованными 64-разрядными данными с двойной точностью с плавающей запятой. Форматы с упакованными байтами могут иметь в два раза больше элементов данных, чем формат с упакованными словами, и каждый элемент данных может иметь половинную разрядность. Форматы обычной и двойной точности с плавающей запятой могут, соответственно, казаться похожими на проиллюстрированные форматы с двойными словами и учетверенными словами, хотя значение/интерпретация разрядов в пределах элементов данных могут быть другими. Помимо этого, подходящими также являются более высокие или более низкие разрядности упакованных данных, такие как, например, 64-разрядные упакованные данные, 512-разрядные упакованные данные, 1024-разрядные упакованные данные и так далее. Подходящим является любое из числа: байта, слова, двойного слова, учетверенного слова или других форматов. Обычно, количество элементов упакованных данных равно размеру в битах упакованных данных, разделенных на размер в битах элементов упакованных данных.

Не являющиеся обязательными подробности в отношении представлений или атрибутов регистров, описанные для любой из Фиг. 3-6, могут, если требуется, применяться к процессору, показанному на Фиг. 1, и/или способу, показанному на Фиг. 2. Не являющиеся обязательными подробности в отношении форматов команды, показанных на Фиг. 7А-D, могут, если требуется, применяться к процессору, показанному на Фиг. 1, и/или способу, показанному на Фиг. 2. Помимо этого, компоненты, признаки и подробности, описанные здесь для любого аппарата, могут также, если требуется, использоваться в любом из описанных здесь способов, которые в вариантах воплощения изобретения могут быть выполнены посредством такого аппарата и/или с таким аппаратом.

Приводимые в качестве примера архитектуры ядра, процессоры и архитектуры компьютера

Ядра процессора могут быть реализованы различным образом, для различных целей и в различных процессорах. Например, варианты реализации таких ядер могут включать в себя: 1) универсальное ядро без переупорядочения последовательности команд, предназначенное для универсальных вычислений; 2) высокопроизводительное универсальное ядро с переупорядочением последовательности команд, предназначенное для универсальных вычислений; 3) специализированное ядро, предназначенное, главным образом, для вычислений (обрабатываемых объемов) графических и/или научных данных. Варианты реализации различных процессоров могут включать в себя: 1) центральный процессор, включающий в себя одно или более универсальных ядер без переупорядочения последовательности команд, которые (ядра) предназначены для универсальных вычислений, и/или одно или более универсальных ядер с переупорядочением последовательности команд, которые (ядра) предназначены для универсальных вычислений; и 2) сопроцессор, включающий в себя одно или более специализированных ядер, предназначенных, главным образом, для (обрабатываемых объемов) графических и/или научных данных. Такие различные процессоры приводят к различным архитектурам вычислительных систем, которые могут включать в себя: 1) сопроцессор на отдельной, от центрального процессора, микросхеме; 2) сопроцессор на отдельном кристалле в том же самом корпусе, что и центральный процессор; 3) сопроцессор на том же самом кристалле, что и центральный процессор (в этом случае, такого рода сопроцессор иногда именуется как специализированная логика, такая как интегрированная логика для (обрабатываемых объемов) графических и/или научных данных, или как специализированные ядра); и 4) внутрикристальную систему, которая может включать в себя на одном и том же кристалле описанный центральный процессор (иногда именуемый как прикладное ядро (прикладные ядра) или прикладной процессор (прикладные процессоры)), вышеописанный сопроцессор и дополнительные функциональные элементы. Далее описываются приводимые в качестве примера архитектуры ядра, за которыми следуют описания приводимых в качестве примера архитектур процессоров и компьютера.

Приводимые в качестве примера архитектуры ядра

Блок-схема ядра без переупорядочения последовательности команд и с переупорядочением последовательности команд

Фиг. 8А представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера конвейер без переупорядочения последовательности команд, так и приводимый в качестве примера конвейер с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, соответствующие вариантам воплощения изобретения. Фиг. 8В представляет собой блок-схему, на которой проиллюстрировано как приводимый в качестве примера вариант воплощения ядра, имеющего архитектуру без переупорядочения последовательности команд, так и приводимое в качестве примера ядро, имеющее архитектуру с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, подлежащие включению в состав процессора, соответствующего вариантам воплощения изобретения. Прямоугольники, вычерченные на Фиг. 8А-В сплошной линией, иллюстрируют конвейер без переупорядочения последовательности команд и ядро без переупорядочения последовательности команд, в то время как необязательное добавление прямоугольников, вычерченных пунктирной линией, иллюстрирует конвейер и ядро с переименованием регистров, переупорядочением последовательности выдачи/исполнения команд. Учитывая, что аспект без переупорядочения последовательности команд представляет собой подмножество аспекта с переупорядочением последовательности команд, опишем аспект с переупорядочением последовательности команд.

На Фиг. 8А процессорный конвейер (800) включает в себя: стадию (802) выборки, стадию (804) декодирования длины, стадию (806) декодирования, стадию (808) распределения, стадию (810) переименования, стадию (812) планирования (также известного как диспетчеризация или выдача), стадию (814) считывания из регистра/считывания из памяти, стадию (816) исполнения, стадию (818) записи в обратном направлении/записи в память, стадию (822) обработки исключительных ситуаций и стадию (1024) фиксации.

На Фиг. 8В показано ядро (890) процессора, включающее в себя звено (830) передней части, сопряженное со звеном (850) исполняющей машины, и оба этих звена сопряжены с запоминающим звеном (870). Ядро (890) может представлять собой ядро для вычисления с сокращенным набором команд (RISC - ядро), ядро для вычисления со сложным набором команд (CISC - ядро), ядро с командными словами сверхбольшой длины (VLIW - ядро) или гибридный или альтернативный тип ядра. В качестве еще одного другого необязательного варианта, ядро (890) может представлять собой специализированное ядро, такое как, например, сетевое ядро или ядро для связи, машину сжатия данных, сопроцессорное ядро, ядро универсального вычислительного звена обработки графических данных (GPGPU - ядро), графическое ядро или тому подобное.

Звено (830) передней части включает в себя звено (832) предсказания ветвей, сопряженное со звеном (834) кэша команд, которое сопряжено с буфером (836) быстрого преобразования адреса (TLB - буфером) команд, которое сопряжено со звеном (838) выборки команд, которое сопряжено с декодирующим звеном (840). Декодирующее звено (840) (или декодер) может декодировать команды и генерировать, в качестве своих выходных данных, одну или более микроопераций, точек входа в микрокод, микрокоманд, других команд или другие управляющие сигналы, которые декодируются из первоначальных команд, или которые иным образом отражают эти команды или выведены из них. Декодирующее звено (840) может быть реализовано с использованием всевозможных различных механизмов. Примеры подходящих механизмов включают в себя: таблицы поиска, варианты реализации посредством аппаратных средств, программируемые логические матрицы (PLA - матрицы), постоянные запоминающие устройства (ПЗУ - устройства) для микрокода и так далее, но не ограничены ими. В одном варианте воплощения изобретения, ядро (890) включает в себя постоянное запоминающее устройство для микрокода или другой носитель информации, который хранит микрокод для некоторых макрокоманд (например, в декодирующем звене (840) или, в ином случае, в пределах звена (830) передней части). Декодирующее звено (840) сопряжено с переименовывающим/распределяющим звеном (852) в звене (850) исполняющей машины.

Звено (850) исполняющей машины включает в себя переименовывающее/распределяющее звено (852), сопряженное со звеном (854) изъятия и набором из одного или более звена (звеньев) (856) планировщика. Звено (звенья) (856) планировщика представляет (представляют) любое количество различных планировщиков, включающих в себя станции резерваций, центральное окно команды и так далее. Звено (звенья) (856) планировщика сопряжено (сопряжены) со звеном (звеньями) (858) физического регистрового файла (физических регистровых файлов). Каждое из звеньев (858) физического регистрового файла (физических регистровых файлов) представляет один или более физических регистровых файлов, различные из которых хранят один или более различных типов данных, таких как скалярные целочисленные данные, скалярные данные с плавающей запятой, упакованные целочисленные данные, упакованные данные с плавающей запятой, векторные целочисленные данные, векторные данные с плавающей запятой, данные о состоянии (например, указатель команды, который представляет собой адрес следующей команды, подлежащей исполнению) и так далее. В одном варианте воплощения изобретения, звено (858) физического регистрового файла (физических регистровых файлов) содержит звено векторных регистров, звено регистров маски записи и звено скалярных регистров. Эти звенья регистров могут обеспечивать архитектурные векторные регистры, векторные регистры маски и регистры общего назначения. Звено (звенья) (858) физического регистрового файла (физических регистровых файлов) перекрывается (перекрываются) звеном (854) изъятия, что иллюстрирует разнообразные методы, посредством которых может быть осуществлено переименование регистров и исполнение с переупорядочением последовательности команд (например, посредством использования переупорядочивающего буфера (переупорядочивающих буферов) и регистрового файла (регистровых файлов) изъятия; посредством использования будущего файла (будущих файлов), буфера (буферов) предыстории и регистрового файла (регистровых файлов) изъятия; посредством использования карт регистров и пула регистров; и так далее). Звено (854) изъятия и звено (звенья) (858) физического регистрового файла (физических регистровых файлов) сопряжены с исполняющим кластером (исполняющими кластерами) (860). Исполняющий кластер (исполняющие кластеры) (860) включает (включают) в себя набор из одного или боле исполняющих звеньев (862) и набор из одного или более звеньев (864) доступа к памяти. Исполняющие звенья (862) могут выполнять разнообразные операции (например, сдвиги, сложение, вычитание, умножение) и над разнообразными типами данных (например, скалярными данными с плавающей запятой, упакованными целочисленными данными, упакованными данными с плавающей запятой, векторными целочисленными данными, векторными данными с плавающей запятой). Притом что некоторые варианты воплощения изобретения могут включать в себя некоторое количестве исполняющих звеньев, выделенных для конкретных функций или наборов функций, другие варианты воплощения изобретения могут включать в себя только одно исполняющее звено или множественные исполняющие звенья, все из которых выполняют все функции. Звено (звенья) (856) планировщика, звено (звенья) (858) физического регистрового файла (физических регистровых файлов) и исполняющий кластер (исполняющие кластеры) (860) показаны как, возможно, имеющиеся во множественном числе, потому что в некоторых вариантах воплощения изобретения создаются раздельные конвейеры для некоторых типов данных/операций (например, конвейер для скалярных целочисленных данных, конвейер для скалярных данных с плавающей запятой/упакованных целочисленных данных/упакованных данных с плавающей запятой/векторных целочисленных данных/векторных данных с плавающей запятой и/или конвейер доступа к памяти, каждые из которых (конвейеров) имеют свои собственные звено планировщика, звено физического регистрового файла (физических регистровых файлов) и/или исполняющий кластер, - а в случае отдельного конвейера доступа к памяти, реализованы некоторые варианты воплощения изобретения, в которых звено (звенья) (864) доступа к памяти имеется (имеются) только у исполняющего кластера этого конвейера. Следует также понимать, что там, где используются раздельные конвейеры, один или больше из этих конвейеров может представлять собой конвейер с переупорядочиванием последовательности выдачи/исполнения команд, а остальные без упорядочения этой последовательности.

Набор звеньев (864) доступа к памяти сопряжен с запоминающим звеном (870), которое включает в себя звено (872) TLB (буфера быстрого преобразования адреса) для данных, сопряженное со звеном (874) кэша данных, сопряженным со звеном (876) кэша уровня 2 (L2). В одном приводимом в качестве примера варианте воплощения изобретения, звенья (864) доступа к памяти могут включать в себя звено загрузки, звено сохранения адреса и звено сохранения данных, каждое из которых сопряжено со звеном (872) TLB для данных, находящимся в запоминающем звене (870). Кроме того, со звеном (876) кэша уровня 2 (L2), находящимся в запоминающем звене (870), сопряжено звено (834) кэша команд. Звено (876) кэша уровня 2 сопряжено с одним или более другими уровнями кэша и, в конечном счете, с основной памятью.

В порядке примера отметим, что эта приводимая в качестве примера архитектура ядра с переименованием регистров, с переупорядочиванием последовательности выдачи/исполнения команд может реализовывать конвейер (800) следующим образом: 1) звено (838) выборки команд выполняет стадии (802 и 804) выборки и декодирования длины; 2) декодирующее звено (840) выполняет стадию (806) декодирования; 3) переименовывающее/распределяющее звено (852) выполняет стадию (808) распределения и стадию (810) переименования; 4) звено (звенья) (856) планировщика выполняет (выполняют) стадию (812) планирования; 5) звено (звенья) (858) физического регистрового файла (физических регистровых файлов) и запоминающее звено (1070) выполняют стадию (814) считывания из регистра/считывания из памяти; исполняющий кластер (860) выполняет стадию (816) исполнения; 6) запоминающее звено (870) и звено (звенья) (858) физического регистрового файла (физических регистровых файлов) выполняют стадию (818) записи в обратном направлении/записи в память; 7) в стадию (822) обработки исключительных ситуаций могут быть вовлечены разнообразные звенья; и 8) звено (854) изъятия и звено (звенья) (858) физического регистрового файла (физических регистровых файлов) выполняют стадию (824) фиксации.

Ядро (890) может поддерживать один или более наборов команд (например, набор команд х86 (с некоторыми расширениями, которые были добавлены в более новых версиях)); набор (MIPS) команд от MIPS Technologies, Саннивейл, штат Калифорния, США; набор (ARM) команд (с необязательными дополнительными расширениями, такими как NEON) от ARM Holdings, Саннивейл, штат Калифорния, США, включающие в себя команду (команды), описанную (описанные) здесь. В одном варианте воплощения изобретения, ядро (890) включает в себя логику для поддержки расширения набора команд для упакованных данных (например, расширения AVX1, AVX2), таким образом, делая возможными операции, используемые многими мультимедийными приложениями, выполняемыми с использованием упакованных данных.

Следует понимать, что ядро может поддерживать многопоточную обработку (исполнение двух или больше параллельных наборов операций или потоков обработки), и может делать это разнообразными методами, включающими в себя многопоточную обработку с квантованием времени, одновременную многопоточную обработку (при которой одно физическое ядро предоставляет логическое ядро для каждого из потоков обработки, одновременная многопоточная обработка которых осуществляется этим физическим ядром) или сочетание этих методов (например, выборка и декодирование с квантованием времени, а после этого одновременная многопоточная обработка, так, как это делается в технологии Intel® Hyperthreading technology (Технологии гиперпоточной обработки Intel®).

Следует понимать, что, хотя переименование регистров описано в контексте исполнения с переупорядочиванием последовательности команд, переименование регистров может быть использовано в архитектуре без переупорядочивания последовательности команд. Хотя проиллюстрированный вариант воплощения процессора также включает в себя раздельные звенья (834/874) кэша команд и данных и совместно используемое звено (876) кэша уровня 2, альтернативные варианты воплощения изобретения могут иметь единый внутренний кэш, как для команд, так и для данных, такой как, например, внутренний кэш уровня 1 (L1) или множественные уровни внутреннего кэша. В некоторых вариантах воплощения изобретения, система может включать в себя сочетание внутреннего кэша и внешнего кэша, который является внешним по отношению к ядру и/или процессору. В качестве альтернативы, весь кэш может быть внешним по отношению к ядру и/или процессору.

Конкретная приводимая в качестве примера архитектура ядра без переупорядочения последовательности команд

На Фиг. 9А-В проиллюстрирована блок-схема более конкретной приводимой в качестве примера архитектуры ядра без переупорядочения последовательности команд, каковое ядро было бы одним из нескольких логических блоков (включающих в себя другие ядра того же самого типа и/или других типов) в микросхеме. Логические блоки поддерживают связь через широкополосную сеть межсоединений (например, кольцевую сеть) с некоторой неизменяемой функциональной логикой, интерфейсами ввода-вывода для памяти и другой необходимой логикой ввода-вывода, в зависимости от варианта применения.

Фиг. 9А представляет собой блок-схему одиночного ядра процессора наряду с его соединением с расположенной на кристалле сетью (902) межсоединений и с его локальным подмножеством (904) кэша уровня 2 (L2), соответствующими вариантам воплощения изобретения. В одном варианте воплощения изобретения, декодер (900) команд поддерживает набор команд (х86) с расширением набора команд для обработки упакованных данных. Кэш (906) уровня 1 делает возможным имеющие малое время ожидания доступы к кэш - памяти в скалярные и векторные звенья. Хотя в одном варианте воплощения изобретения (для того, чтобы упростить конструкцию), скалярное звено (908) и векторное звено (910) используют раздельные наборы регистров (соответственно, скалярные регистры (912) и векторные регистры 914), и данные, передаваемые между ними, записываются в память и затем считываются в них в обратном направлении из кэша (906) уровня 1 (LI), в альтернативных вариантах воплощения изобретения может использоваться другой подход (например, использование единого набора регистров или введение тракта связи, который позволяет передавать данные между этими двумя регистровыми файлами, не записывая их и не считывая их в обратном направлении).

Локальное подмножество (904) кэша уровня 2 представляет собой часть глобального кэша уровня 2, который разделен на отдельные локальные подмножества, по одному на ядро процессора. Каждое ядро процессора имеет тракт прямого доступа к своему собственному локальному подмножеству (904) кэша уровня 2. Данные, считываемые ядром процессора, сохраняются в его локальном подмножестве (904) кэша уровня 2, и доступ к ним может быть осуществлен быстро, параллельно с другими ядрами процессора, осуществляющими доступ к своим собственным локальным подмножествам кэша уровня 2. Данные, записанные ядром процессора, сохраняются в его собственном локальном подмножестве (904) кэша уровня 2 и, в случае необходимости, сбрасываются из других подмножеств. Кольцевая сеть обеспечивает когерентность для совместно используемых данных. Кольцевая сеть является двунаправленной для того, чтобы позволять агентам, таким как ядра процессора, кэши уровня 2 и другие логические блоки, поддерживать связь друг с другом в пределах микросхемы. Каждый кольцевой тракт передачи данных имеет разрядность, составляющую 1012 разрядов, приходящихся на одно направление.

Фиг. 9В представляет собой расширенное представление части ядра процессора, показанного на Фиг. 9А, соответствующего вариантам воплощения изобретения. Фиг. 9В включает в себя кэш (906А) уровня 1 для данных, являющийся частью кэша (904) уровня 1, так же как и больше подробностей, относящихся к векторному звену (910) и векторным регистрам (914). В частности, векторное звено (910) представляет собой 16-разрядное устройство обработки векторных данных (VPU - устройство) (смотри 16-разрядное арифметико-логическое устройство (928)), которое исполняет одну или больше команд целочисленных вычислений, вычислений с обычной точностью с плавающей запятой и вычислений с двойной точностью с плавающей запятой. Устройство обработки векторных данных поддерживает настройку по адресам входов регистра посредством звена (920) настройки по адресам, числовое преобразование посредством звеньев (922А-В) числового преобразования и копирование посредством звена (924) копирования на входе памяти. Регистры (926) маски записи позволяют осуществлять предикацию записей результирующего вектора.

Процессор с интегрированным контроллером памяти и графическими средствами

Фиг. 10 представляет собой блок-схему процессора (1000), который может иметь более чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированные графические средства в соответствии с вариантами воплощения изобретения. Прямоугольники, очерченные на Фиг. 10 сплошной линией, иллюстрируют процессор (1000) с единственным ядром (1002А), системного агента (1010), набор из одного или более звеньев (1016) шинного контроллера, в то время как необязательное добавление прямоугольников, очерченных пунктирной линией, иллюстрирует альтернативный процессор (1000) с множественными ядрами (1002А-N), набор из одного или более звена (звеньев) (1014) интегрированного контроллера памяти в звене (1010) системного агента и специализированную логику (1008).

Таким образом, различные варианты реализации процессора (1000) могут включать в себя: 1) центральный процессор со специализированной логикой (1008), представляющей собой интегрированную логику для (обрабатываемых объемов) графических и/или научных данных (которая может включать в себя одно или более ядер), и ядра (1002А-N), представляющие собой одно или более универсальных ядер (например, универсальных ядер без переупорядочения последовательности команд, универсальных ядер с переупорядочением последовательности команд, сочетание этих двух типов ядер); 2) сопроцессор с ядрами (1002А-N), представляющими собой большое количество специализированных ядер, предназначенных, главным образом, для (обрабатываемых объемов) графических и/или научных данных; и 3) сопроцессор с ядрами (1002А-N), представляющими собой большое количество универсальных ядер без переупорядочения последовательности команд. Таким образом, процессор (1000) может представлять собой универсальный процессор, сопроцессор или специализированный процессор, такой как, например, сетевой процессор или процессор передачи данных, машина сжатия данных, графический процессор, GPGPU (универсальное устройство обработки графических данных), высокопроизводительный сопроцессор со многими интегрированными ядрами (MIC - сопроцессор) (включающий в себя 30 или больше ядер), встроенный процессор или тому подобное. Процессор может быть реализован на одной или более микросхемах. Процессор (1000) может являться частью одной или более подложек и/или может быть реализован на одной или более подложках с использованием любого из ряда технологических процессов, таких как, например, BiCMOS (биполярная комплементарная структура "металл - оксид - полупроводник"), CMOS (комплементарная структура "металл - оксид - полупроводник") или NMOS (n - канальная структура "металл - оксид - полупроводник").

Иерархия памяти включает в себя один или более уровней кэша в пределах ядер, набор из одного или более совместно используемых звеньев (1006) кэша и внешнюю память (не показанную на чертеже), сопряженную с набором звеньев (1014) интегрированного контроллера памяти. Набор совместно используемых звеньев (1006) кэша может включать в себя один или более кэшей среднего уровня, таких как уровня 2 (L2), уровня 3 (L3), уровня 4 (L4) или других уровней кэша, кэш последнего уровень (LLC - кэш) и/или их сочетания. Хотя в одном варианте воплощения изобретения межсоединение между интегрированной логикой (1008) графики, набором совместно используемых звеньев (1006) кэша и звеном (1010) системного агента/звеном (звеньями) (1014) интегрированного контроллера памяти осуществляет основанное на кольце звено (1012) межсоединения, в альтернативных вариантах воплощения изобретения может использоваться любое количество хорошо известных технологий для межсоединения таких звеньев. В одном варианте воплощения изобретения, поддерживается когерентность между одним или более звеньями (1006) кэша и ядрами (1002-N).

В некоторых вариантах воплощения изобретения, одно или более ядер (1002А-N) способны к многопоточной обработке данных. Системный агент (1010) включает в себя те компоненты, которые координируют и управляют ядрами (1002А-N). Звено (1010) системного агента может включать в себя, например, звено управления электропитанием (PCU - звено) и звено отображения. Звено управления электропитанием может представлять собой или включать в себя логику и компоненты, необходимые для регулирования состояние электропитания ядер (1002А-N) и интегрированной логики (1008) графики. Звено отображения предназначено для приведения в действие одного или более подсоединенных внешним образом устройств отображения.

Ядра (1002А-N) могут быть однородными или неоднородными в том, что касается набора команд архитектуры, то есть два или более из ядер (1002А-N) могут быть способны исполнять один и тот же набор команд, в то время как другие могут быть способны исполнять только некоторое подмножество этого набора команд или другой набор команд.

Приводимая в качестве примера архитектура вычислительной системы

Фиг. 11-14 представляют собой блок-схемы приводимых в качестве примера архитектур вычислительных систем. Также подходящими являются и другие конструкции и конфигурации систем, известные в данных областях техники для переносных компьютеров, настольных компьютеров, карманных персональных компьютеров, персональных цифровых секретарей, инженерных рабочих станций, серверов, сетевых устройств, сетевых концентраторов, коммутаторов, встроенных процессоров, процессоров цифровой обработки сигналов (DSP - процессоров), графических устройств, игровых видеоустройств, телевизионных абонентских приставок, микроконтроллеров, сотовых телефонов, портативных универсальных проигрывателей, ручных устройств и разнообразных других электронных устройств. В общем, обычно подходящим является огромное разнообразие систем или электронных устройств, в состав которых может быть введен процессор и/или другая исполняющая логики, которые раскрываются в данном описании.

Обратимся теперь к Фиг. 11, на которой показана блок-схема системы (1100) в соответствии с одним вариантом воплощения настоящего изобретения. Система (1100) может включать в себя один или более процессоров (1110), (1115), которые сопряжены с концентратором - контроллером (1120). В одном варианте воплощения изобретения концентратор - контроллер (1120) включает в себя концентратор - контроллер (GMCH - концентратор) (1190) памяти графических данных и концентратор ввода-вывода (IOH - концентратор) (1150) (которые могут находиться на раздельных микросхемах); концентратор - контроллер (1190) памяти графических данных включает в себя контроллер памяти и графический контроллер, с которыми сопряжены память (1140) и сопроцессор (1145); концентратор (1150) ввода-вывода сопрягает с концентратором - контроллером (1190) памяти графических данных устройства (1160) ввода-вывода (I/O - устройства). В качестве альтернативы, один или оба контроллера из числа: контроллера памяти и графического контроллера, интегрированы в пределах процессора (как здесь описано), память (1140) и сопроцессор (1145) сопряжены непосредственно с процессором (1110), и концентратором - контроллером (1120) в единой микросхеме с концентратором (1150) ввода-вывода.

Необязательная природа дополнительных процессоров (1115) обозначена на Фиг. 11 пунктирными линиями. Каждый процессор (1110), (1115) может включать в себя одно или больше описанных здесь обрабатывающих ядер, и может представлять собой некоторую версию процессора (1000).

Память (1140) может представлять собой, например, динамическое оперативное запоминающее устройство (DRAM), память с изменением фазы (РСМ - память) или сочетание этих двух типов памяти. По меньшей мере для одного варианта воплощения изобретения, концентратор - контроллер (1120) поддерживает связь с процессором (процессорами) (1110), (1115) через многоотводную шину, такую как управляющая шина (FSB - шина), двухточечный интерфейс, такой как межсоединение QuickPath (QPI - межсоединение) или аналогичное соединение (1195).

В одном варианте воплощения изобретения, сопроцессор (1145) представляет собой специализированный процессор, такой как, например, высокопроизводительный MIC-процессор (процессор со многими интегрированными ядрами), сетевой процессор или процессор передачи данных, машина сжатия данных, графический процессор, GPGPU (универсальное устройство обработки графических данных), встроенный процессор или тому подобное. В одном варианте воплощения изобретения, концентратор - контроллер (1120) может включать в себя интегрированный графический акселератор.

Может иметь место многообразие различий между физическими ресурсами (1110), (1115) в том, что касается спектра показателей их качества, включающих в себя архитектурные, микроархитектурные, тепловые характеристики, характеристики энергопотребления и тому подобное.

В одном варианте воплощения изобретения, процессор (1110) выполняет команды, которые управляют операциями по обработке данных, относящимися к общему типу. В пределах команд могут быть встроены команды для сопроцессора. Процессор (1110) распознает эти команды для сопроцессора как относящиеся к типу, который подлежит выполнению приданным сопроцессором (1145). Соответственно, процессор (1110) выдает эти команды для сопроцессора (или управляющие сигналы, представляющие команды для сопроцессора) по шине сопроцессора или другому межсоединению в сопроцессор (1145). Сопроцессор(ы) (1145) принимает (принимают) и исполняет (исполняют) принятые команды для сопроцессора.

Обратимся теперь к Фиг. 12, на которой показана блок-схема первой более конкретной системы (1200), приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения. Как показано на Фиг. 12, многопроцессорная система (1200) представляет собой систему с двухточечными межсоединениями, и включает в себя первый процессор (1270) и второй процессор (1280), сопряженные через двухточечное межсоединение (1250). Каждый из процессоров: (1270) и (1280) может представлять собой некоторую версию процессора (1000). В одном варианте воплощения изобретения, процессоры (1270) и (1280) представляют собой, соответственно, процессоры (1110) и (1115), в то время как сопроцессор (1238) представляет собой сопроцессор (1145). В другом варианте воплощения изобретения, процессоры (1270) и (1280) представляют собой, соответственно, процессор (1110), сопроцессор (1145).

Процессоры (1270) и (1280) показаны включающими в себя, соответственно, звенья (1272) и (1282) интегрированных контроллеров памяти (IMC - контроллеров). Процессор (1270) также включает в себя, как часть своих звеньев - шинных контроллеров, двухточечные (Р-Р) интерфейсы (1276) и (1278); аналогичным образом, второй процессор (1280) включает в себя (двухточечные) интерфейсы (1286) и (1288). Процессоры (1270), (1280) могут осуществлять обмен информацией через двухточечный (Р-Р) интерфейс (1250) с использованием схем (1278), (1288) (двухточечного) интерфейса. Как показано на Фиг. 12, интегрированные контроллеры (1272) и (1282) памяти (IMC - контроллеры) сопрягают процессоры с соответствующими запоминающими устройствами, а именно, с памятью (1232) и памятью (1234), которые могут являться частями основной памяти, локально закрепленными за соответствующими процессорами.