Область техники, к которой относится изобретение

Изобретение относится к области логики обработки данных, к микропроцессорам и связанной с ними структурой набора команд, которые при их исполнении посредством процессора или другой логики обработки данных выполняют логические, математические или другие функциональные операции. В частности, изобретение относится к командам и логике для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Уровень техники

Хеш-функции могут использоваться для многих целей: например, для индексации данных в хеш-таблицах, для создания идентифицирующих характеристик, для балансировочного распределения нагрузки, для поиска данных в базах данных, для обнаружения дублированных данных или для однозначной идентификации файлов, и в качестве контрольных сумм для обнаружения случайного нарушения целостности данных. Например, в приложении к балансировочному распределению нагрузки, в хеш-алгоритме может использоваться в качестве основы для выбора сервера IP-адрес (адрес по межсетевому протоколу) клиента, или MAC-адрес (адрес по Протоколу управления доступом к передающей среде) клиента, или значение HTTP-заголовка (заголовка по Протоколу передачи гипертекста) и так далее. В таких приложениях один и тот же клиент может обслуживаться одним и тем же сервером, даже тогда, когда список располагаемых серверов изменен в течение сеанса связи с клиентом. Такого рода свойство может также сделать этот алгоритм полезным для приложений, которые требуют хранения информации о состоянии стороны сервера, таких как "cookies" (небольшой фрагмент данных о предыстории обращений данного пользователя к данному веб-серверу, автоматически создаваемый сервером на машине пользователя).

Термин "согласующееся хеширование" относится к способу распределения запросов между изменяющейся совокупностью Web-серверов. Каждое гнездо представлено узлом в распределенной системе. Добавление (подсоединения) и удаление (отключения/отказы) узлов требует переключения элементов, при котором количество гнезд/узлов изменяется. Хеш-функция может не сохранять структуру. В идеальном варианте для каждых входных данных вероятность получения любых из возможных выходных данных должна быть равной. Любые неравномерности в частотном распределении входных данных трансформируются в равномерное распределение выходных данных.

Однако могут иметь место проблемы как вследствие случайностей, так и по умыслу. В случае случайности пользователи могут состоять из различных групп, которым доступ к ресурсам требуется в различной степени. Если эти группы ненадлежащим образом сбалансированы, то пользователям, которых хеш-функция направляет на некоторый ресурс, доступ к ресурсам может требоваться в большей степени, чем другим пользователям. Этот некоторый ресурс в таком случае подвергается более высокой нагрузке, чем другие ресурсы, что приводит к смещению баланса нагрузки между ресурсами.

В случае умысла могут иметь место так называемые "хеш-атаки", которые предназначены для того, чтобы вызвать смещение баланса нагрузки между ресурсами. Хеш-атаки обычно делаются возможными действиями атакующих лиц, имеющих достаточное знание о системе, и/или атакующих лиц, использующих информацию, которая выводится из системы, содержащей ресурсы. Атакующие лица в таком случае заботятся о том, чтобы каждый запрос на ресурсы при прохождении хеш-функции направлялся на один и тот же ресурс. Этот ресурс в таком случае подвергается необычно высокой нагрузке и в таком случае функционирует более или менее неэффективно, что может в результате привести к так называемому "отказу в обслуживании", при котором ресурс не принимает более никаких пользователей. Этот отказ в обслуживании может оказывать воздействие на эффективность обслуживания всей системы.

Криптографическая хеш-функция представляет собой хеш-функцию, то есть алгоритм, который берет произвольный блок данных и возвращает битовую строку постоянного размера, (криптографическое) хеш-значение, таким образом, что (случайное или намеренное) изменение данных будет (с очень высокой вероятностью) изменять хеш-значение. Кодируемые данные часто называются "сообщением", а хеш-значение иногда называется профиль сообщения или "профиль".

Криптографические хеш-функции имеют много вариантов применения по защите информации, особенно в цифровых подписях, кодах аутентификации сообщений (MAC-кодах) и других формах аутентификации. Они могут также использоваться в качестве обыкновенных хеш-функций для индексации данных в хеш-таблицах, для для создания идентифицирующих характеристик, для обнаружения дублированных данных или для однозначной идентификации файлов, и в качестве контрольных сумм для обнаружения случайного нарушения целостности данных. В контекстах защиты информации криптографические хеш-значения иногда называются (цифровыми) "отпечатками пальцев", контрольными суммами или просто хеш-значениями, даже при том, что все эти термины представляют функции с довольно различными свойствами и целями.

Одна из наиболее известных криптографических хеш-функций представляет собой алгоритм MD5 (Алгоритм 5 "Сообщение - профиль"), разработанный Рональдом Райвестом (Ronald Rivest). Другие распространенные алгоритмы представляют собой SHA 1 (Алгоритм 1 защищенного хеширования), так же, как и его варианты SHA 2 и SHA 3, опубликованные Национальным институтом стандартов и технологии (институтом NIST (США)) в качестве Федерального стандарта США по обработке информации (FIPS-стандарта).

Если криптографическая хеш-функция основана на некоторой математической функции, то она все-таки может стать восприимчивой к атакам, имеющим целью отказ в обслуживании, в том, что при некоторых обстоятельствах она может стать подверженной одному закону из числа так называемых: "закона Ципфа (Zipfs)", "степенного закона" или "распределение Парето", при которых некоторый конкретный ресурс подвергается необычно высокой нагрузке. Это свойство или аналогичные свойства могут злонамеренно использоваться для того, чтобы вызвать смещение баланса нагрузки между ресурсами, приводящее к отказу в обслуживании.

Два важных компромисса в хеш-функциях для одного класса хеширования для выполнения поиска представляют собой: (1) сложность против скорости вычисления - слишком простая, и хеш-функция легко взламывается, слишком сложная, и хеш-функция слишком долго вычисляется; и (2) распределение профиля и лавинообразные свойства - изменение единственного бита во входных данных должно вызывать изменение n битов в выводимом значении хеш-профиля, самым сильным является случай, при котором n составляет приблизительно половину размера выводимого значения хеш-профиля.

Некоторыми предложены процессоры (например, в патенте США, имеющем номер 8255703) или сопроцессоры (например, в патенте США, имеющем номер 7240203), способные исполнять весь алгоритм защищенного хеширования. Один недостаток такого подхода заключается в том, что он не вписывается с легкостью в стандартный конвейер исполнения в современном микропроцессоре, если не уделить специальное внимание таким вопросам, как специальная обработка прерываний или одновременное суперскалярное исполнение других команд. Другое несоответствие со стандартными конвейерами исполнения заключается в задержке, требующейся для исполнения всего алгоритма защищенного хеширования.

Современные процессоры часто включают в себя команды для обеспечения операций, которые являются интенсивными в вычислительном отношении, но предлагают высокий уровень параллелизма данных, что может использоваться при эффективной реализации с использованием разнообразных устройств хранения данных, таких как, например, векторные регистры в технологии (SIMD) с одним потоком команд и многими потоками данных. Центральный процессор (CPU) может в таком случае предоставлять параллельные аппаратные средства для поддержки обработки векторов. Вектор представляет собой структуру данных, которая содержит некоторое количество последовательных элементов данных. Векторный регистр размера М может содержать N векторных элементов размера О, где N=М/О. Например, векторный регистр размером в 64 байта может быть разделен на: (а) 64 векторных элемента, при этом каждый элемент содержит порцию данных, которая занимает 1 байт; (b) 32 векторных элемента, содержащих порции данных, которые занимают 2 байта (или одно "слово") каждый; (с) 16 векторных элементов, содержащих порции данных, которые занимают 4 байта (или одно "двойное слово") каждый; или (d) 8 векторных элементов, содержащих порции данных, которые занимают 8 байтов (или одно "учетверенное слово") каждый. Природа параллелизма в векторных регистрах SIMD могла бы хорошо подходить для обработки алгоритмов защищенного хеширования.

До настоящего времени потенциальные решения для таких сложностей, несоответствий, проблем, ограничивающих производительность, и других критических вопросов не были надлежащим образом исследованы.

Краткое описание чертежей

Изобретение проиллюстрировано в порядке примера, а не ограничения, чертежами.

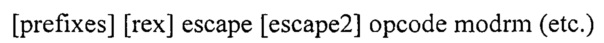

Фиг. 1A представляет собой структурную схему одного варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Фиг. 1B представляет собой структурную схему другого варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Фиг. 1C представляет собой структурную схему другого варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

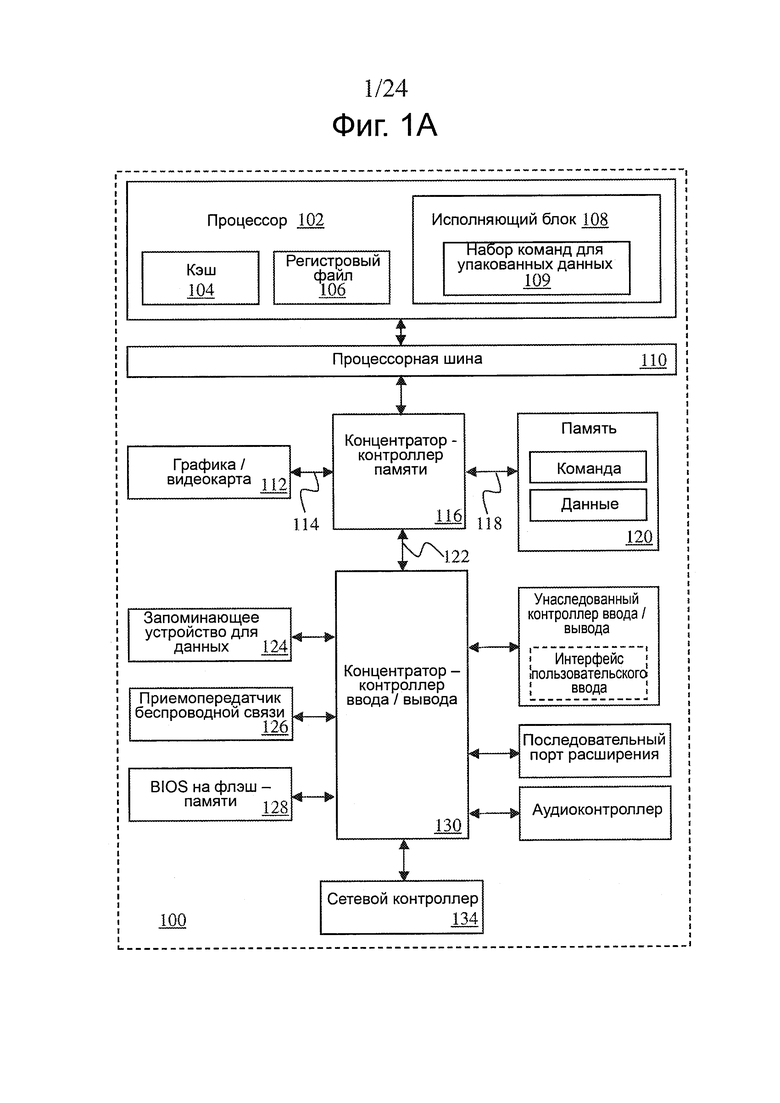

Фиг. 2 представляет собой структурную схему одного варианта воплощения процессора, который исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 3A проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

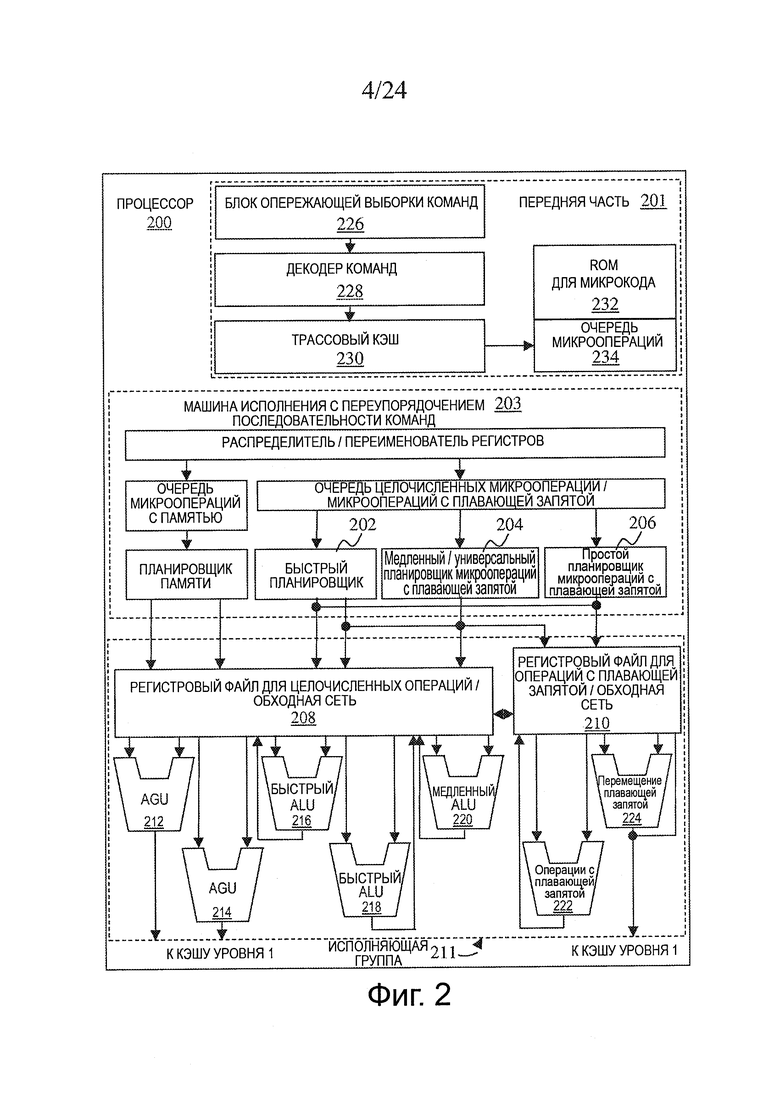

На Фиг. 3B проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

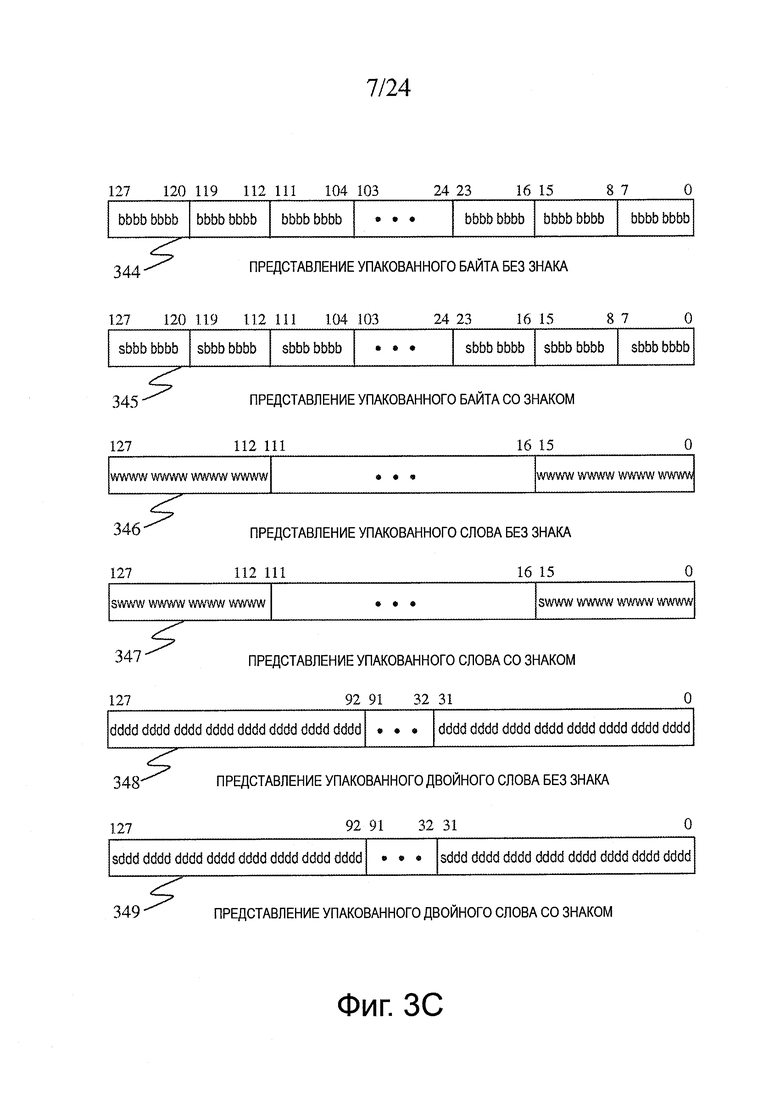

На Фиг. 3C проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

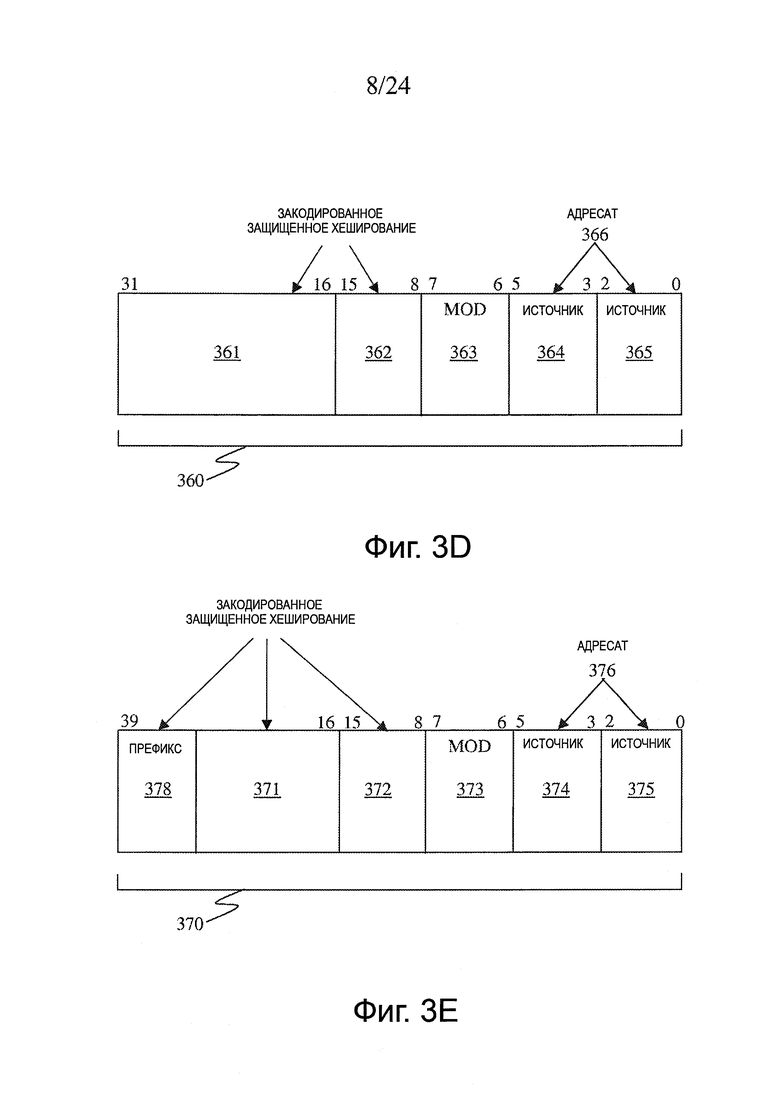

На Фиг. 3D проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее одному варианту воплощения изобретения.

На Фиг. 3E проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

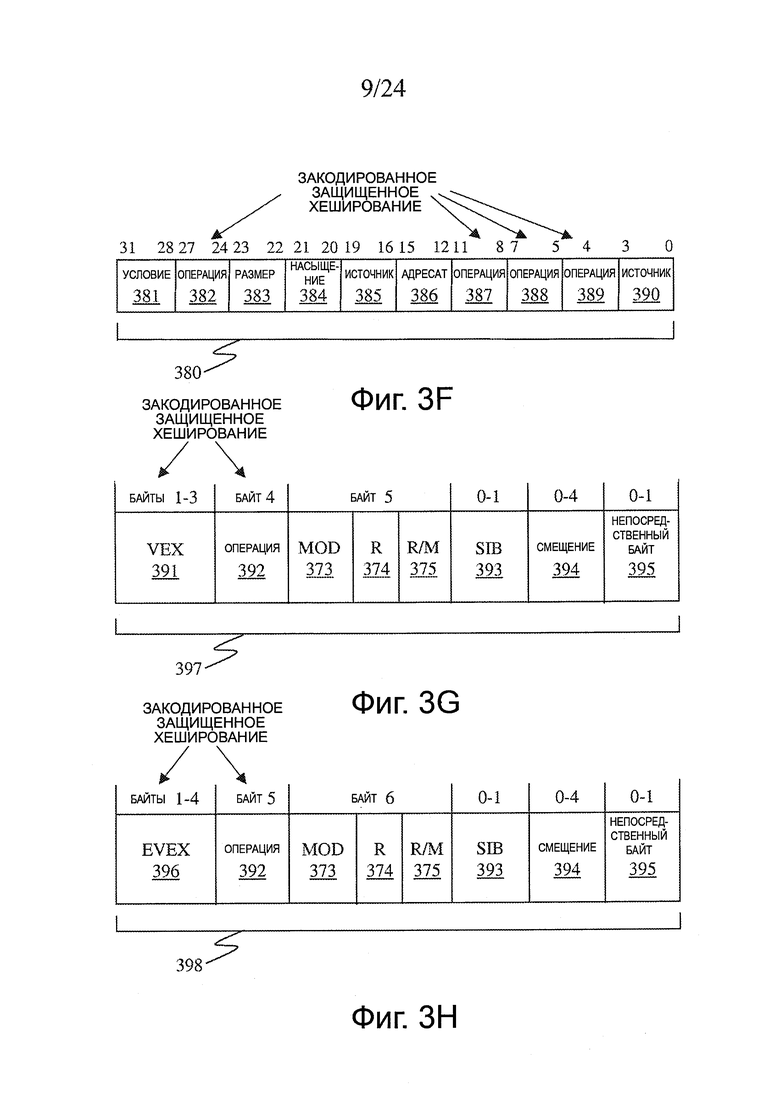

На Фиг. 3F проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 3G проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 3H проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

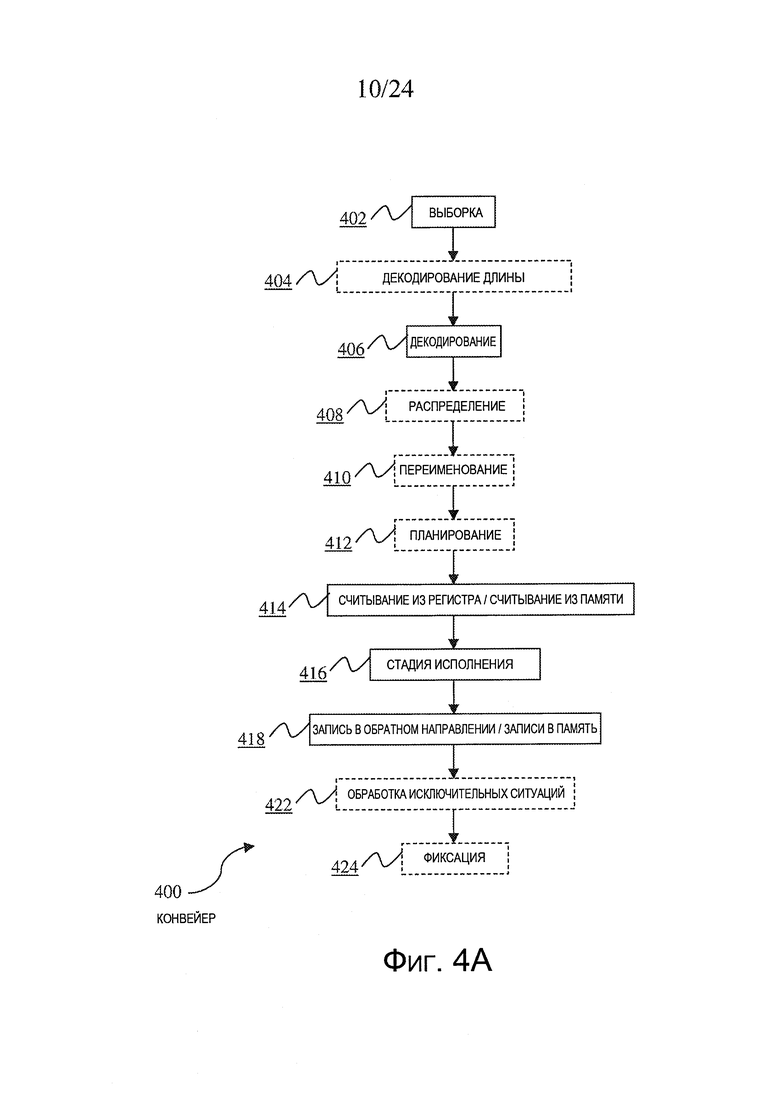

На Фиг. 4A проиллюстрированы элементы одного варианта воплощения микроархитектуры процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

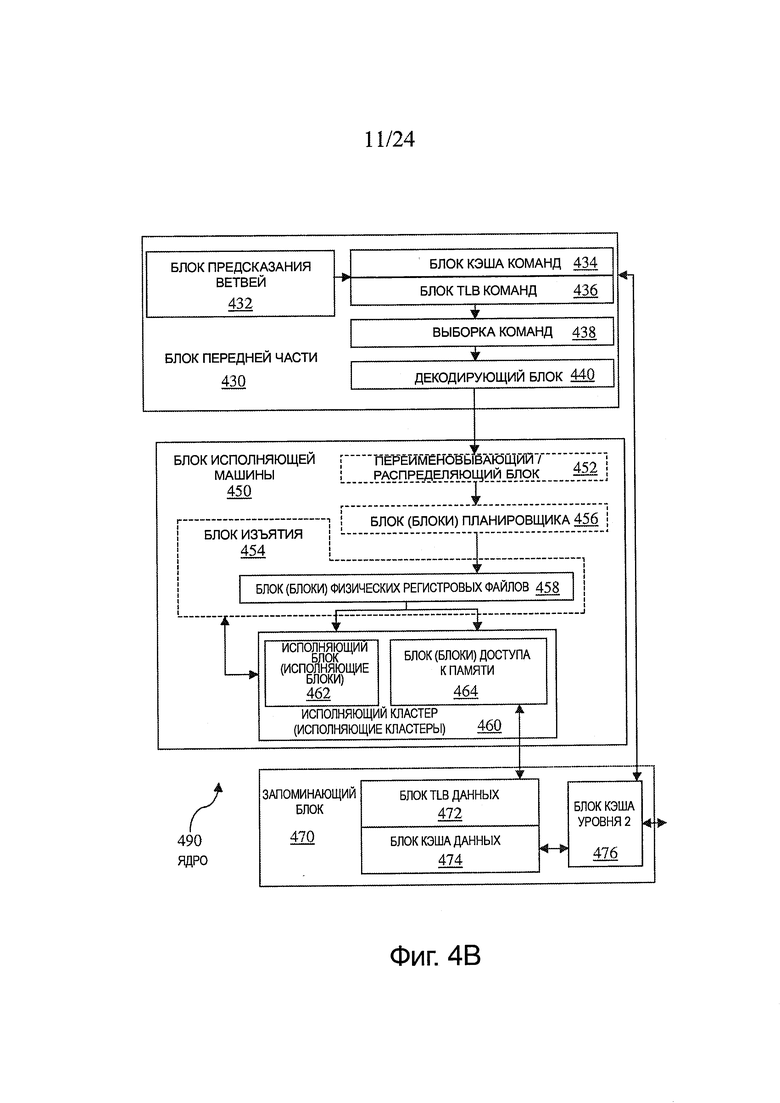

На Фиг. 4B проиллюстрированы элементы другого варианта воплощения микроархитектуры процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

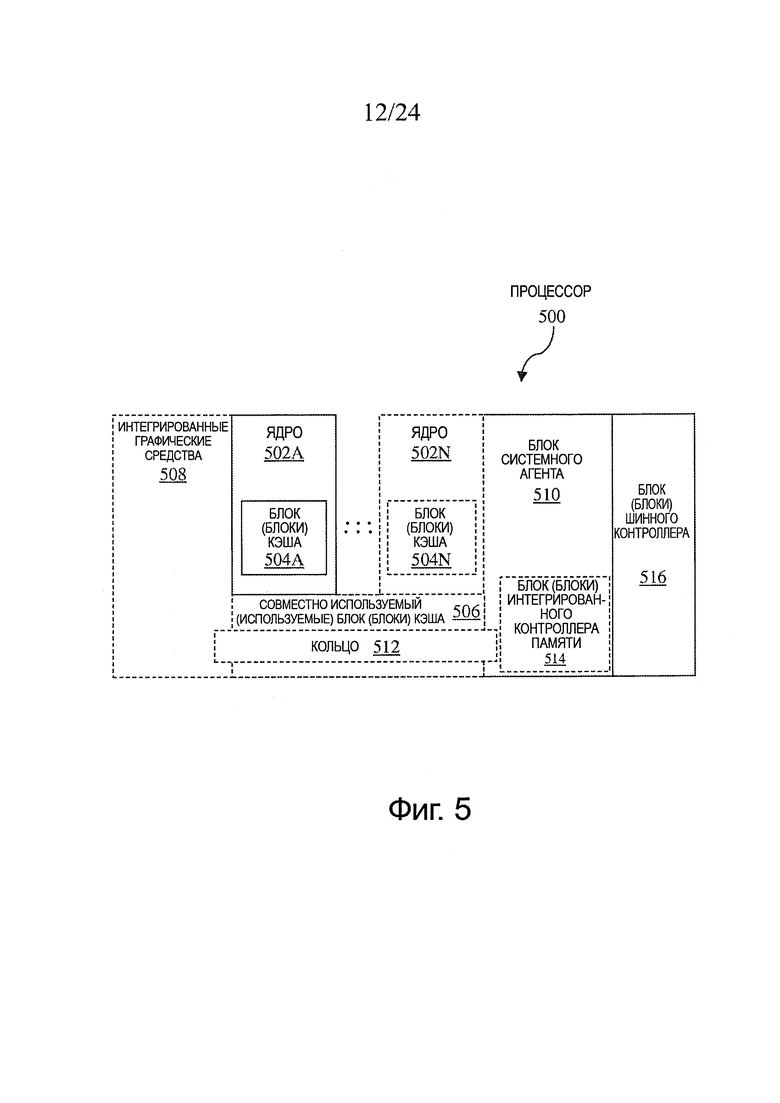

Фиг. 5 представляет собой структурную схему одного варианта воплощения процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

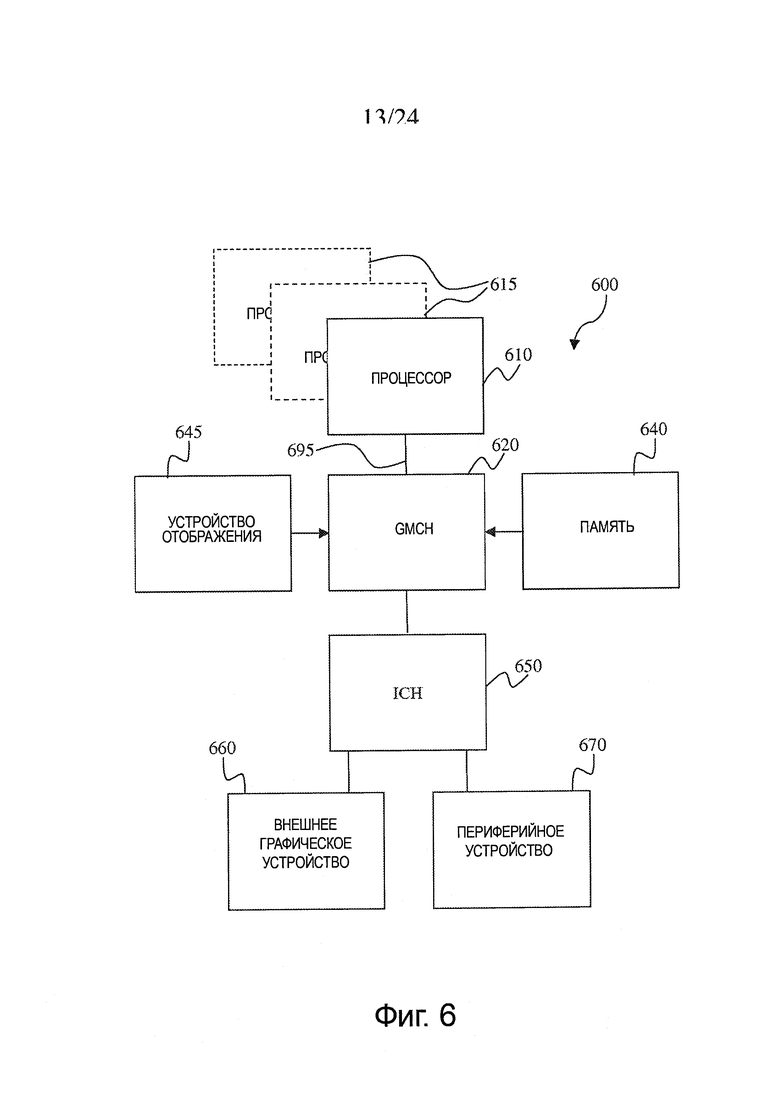

Фиг. 6 представляет собой структурную схему одного варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

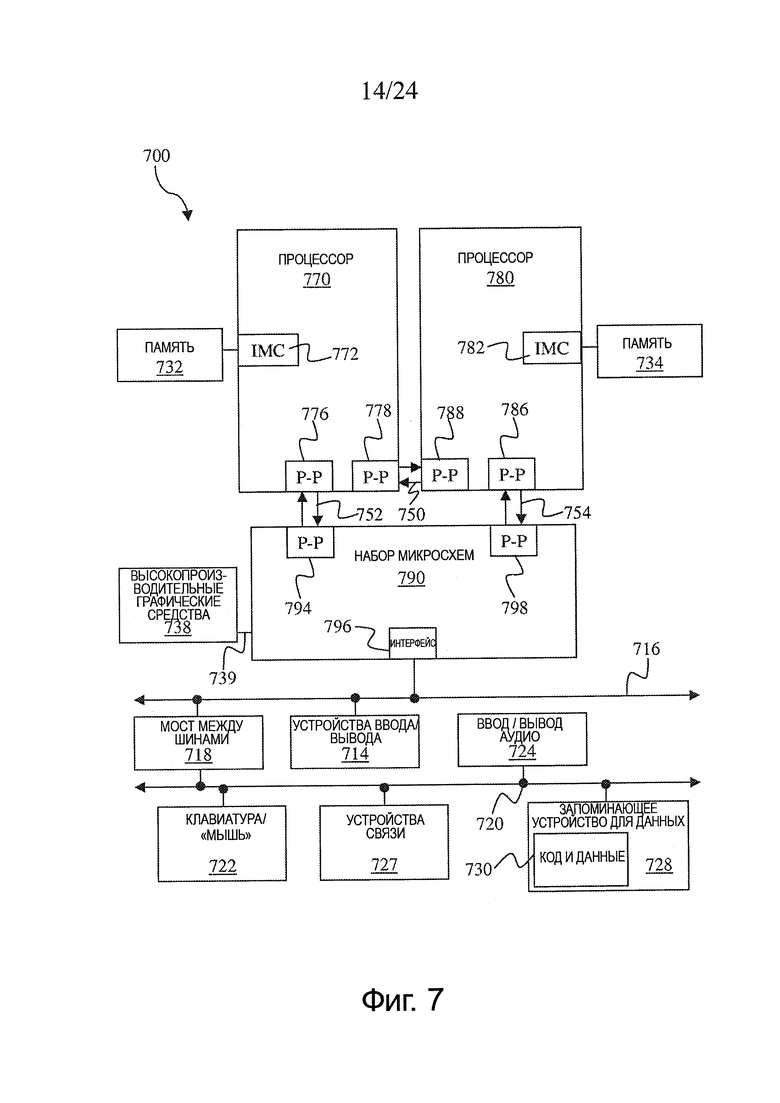

Фиг. 7 представляет собой структурную схему другого варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

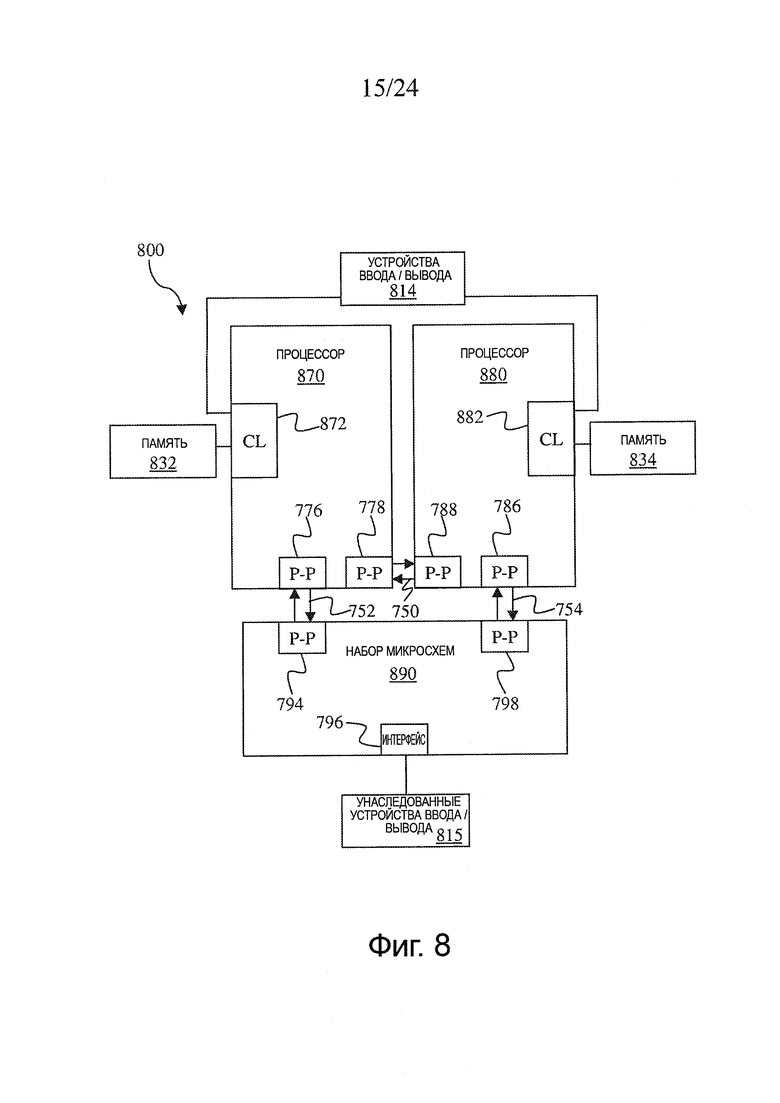

Фиг. 8 представляет собой структурную схему другого варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 9 представляет собой структурную схему одного варианта воплощения внутрикристальной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

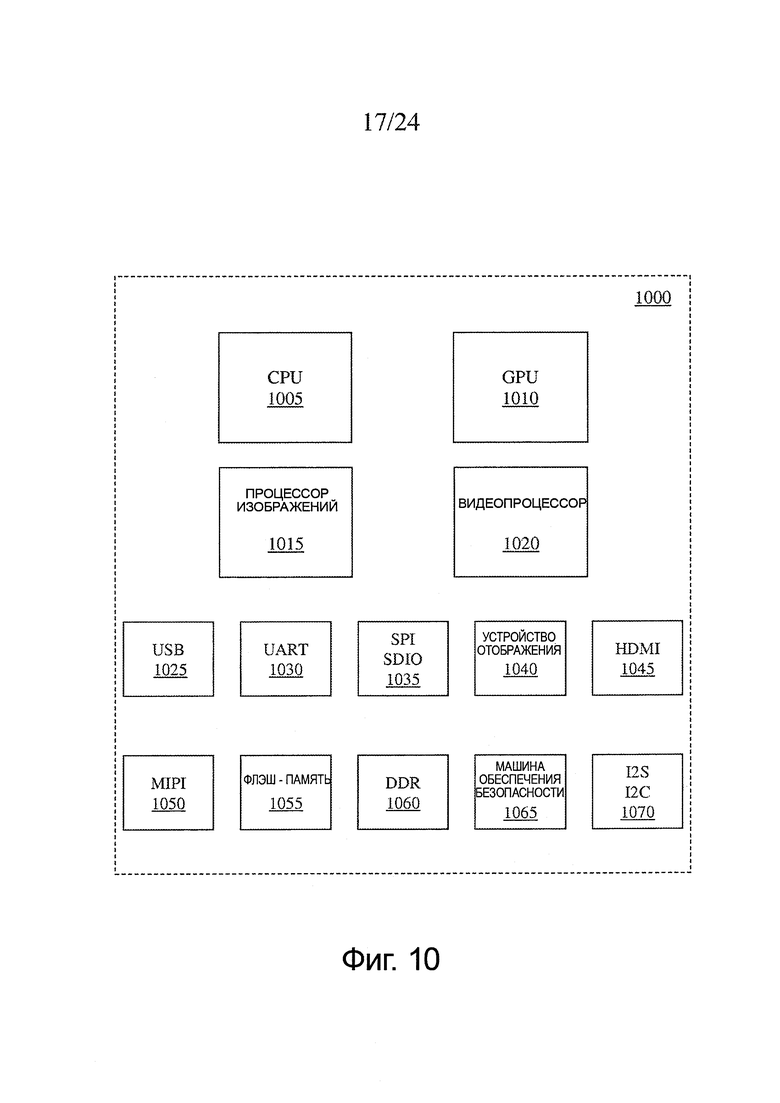

Фиг. 10 представляет собой структурную схему некоторого варианта воплощения процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

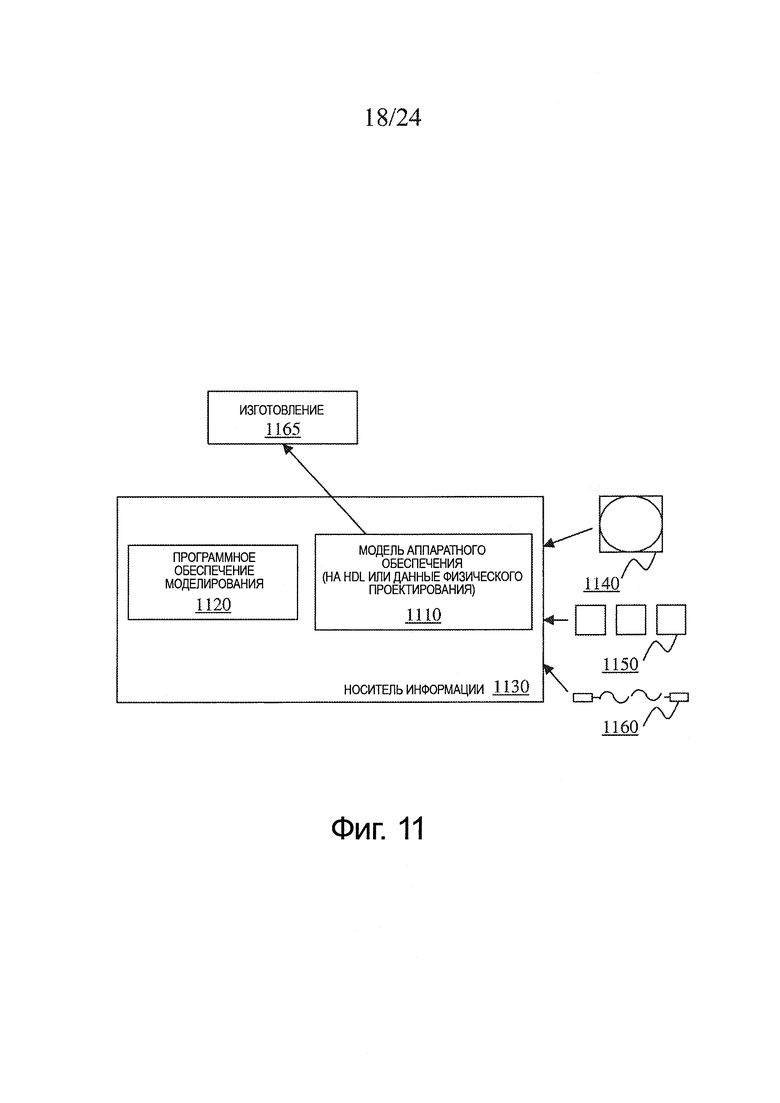

На Фиг. 11 проиллюстрирована структурная схема одного варианта воплощения системы разработки IP-ядра, которая обеспечивает функциональные возможности "среза" циклов защищенного хеширования в технологии SIMD (с одним потоком команд и многими потоками данных.

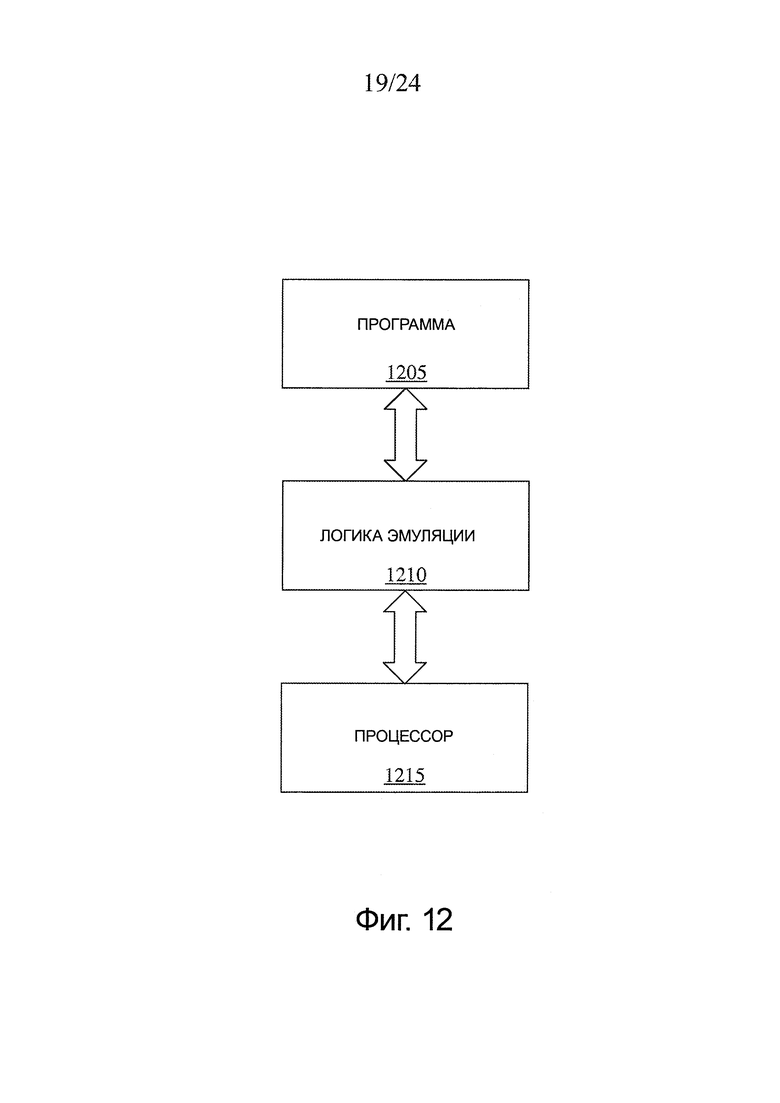

На Фиг. 12 проиллюстрирован один вариант воплощения системы эмуляции архитектуры, которая обеспечивает функциональные возможности "среза" циклов защищенного хеширования в технологии SIMD.

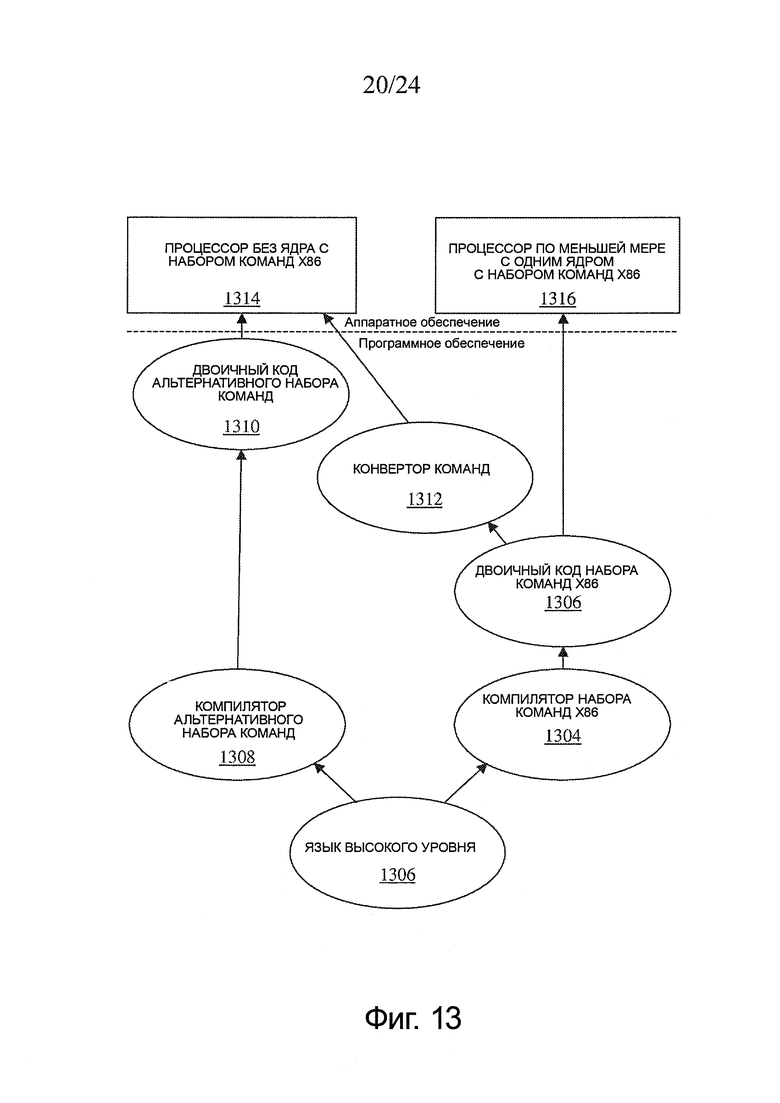

На Фиг. 13 проиллюстрирован один вариант воплощения системы для преобразования команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

На Фиг. 14 проиллюстрирована схема для одного варианта воплощения аппарата для исполнения команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 15 проиллюстрирована схема для альтернативного варианта воплощения аппарата для исполнения команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

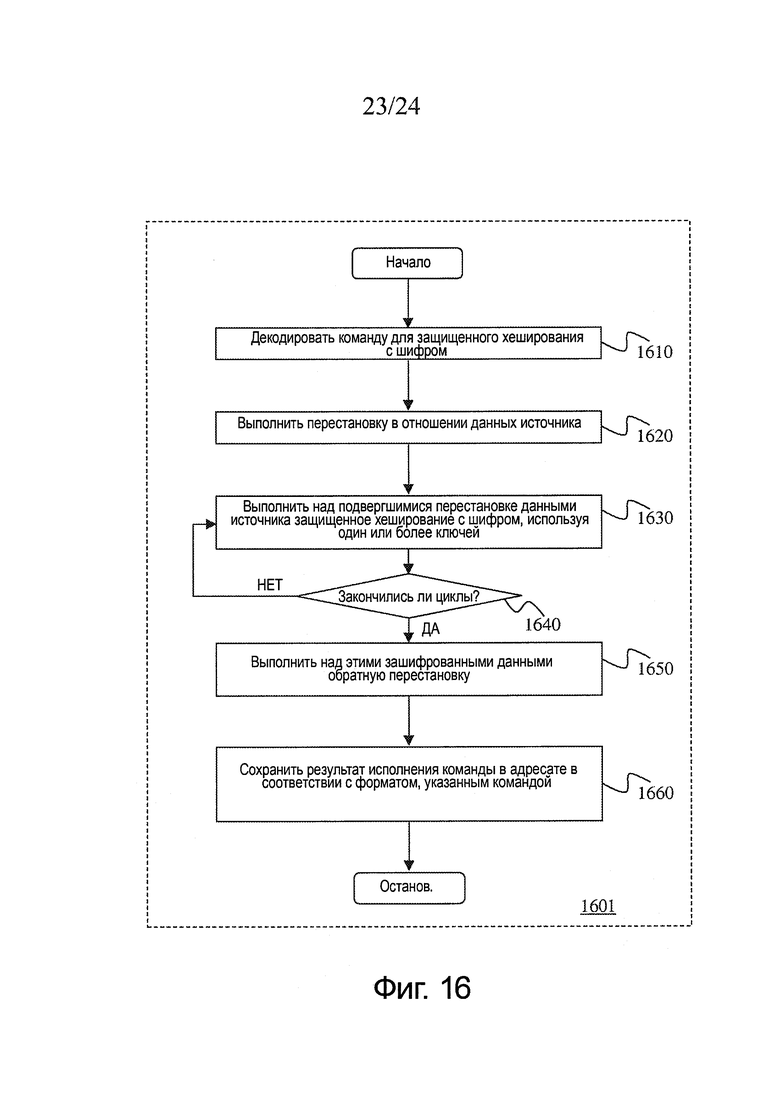

На Фиг. 16 проиллюстрирована блок-схема алгоритма для некоторого варианта воплощения процесса для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 17 проиллюстрирована блок-схема алгоритма для другого варианта воплощения процесса для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Детализированное описание

В нижеследующем описании раскрываются команды и логика обработки данных, обеспечивающие функциональные возможности цикла алгоритма защищенного хеширования с шифром. Некоторые варианты воплощения изобретения включают в себя процессор, содержащий: декодирующую стадию для декодирования команды для алгоритма защищенного хеширования с шифром, первую команду, указывающую данные источников, и один или более операндов-ключей. Исполняющие блоки процессора реагируют на декодированную команду, выполняя над данными источников одну или более циклических итераций алгоритма защищенного хеширования с шифром, используя эти один или более операндов-ключей, и сохраняют результат исполнения команды в регистре-адресате. В одном варианте воплощения команды указывают итерацию цикла алгоритма защищенного хеширования с шифром, использующую шифровальный алгоритм Файстела (Feistel), такой как DES (Стандарт шифрования данных) или TDES (Тройной DES). В альтернативных вариантах воплощения изобретения могут использоваться другие шифровальные алгоритмы, например, такие как Blowfish, SAFER (Защищенная и быстрая процедура шифрования) K - 64, CAST5 (разработанный Карлайлом Эдэмсом (Carlisle Adams) and и Стаффордом Тавэйрсом (Stafford Tavares)), FEAL (Алгоритм быстрого шифрования данных) и так далее. В одном варианте воплощения изобретения результат исполнения команды может быть использован при генерировании назначения ресурса из запроса для запросов на балансировку нагрузки по набору ресурсов обработки данных. В некоторых вариантах воплощения изобретения может указываться (например, в непосредственном операнде) диапазон номеров цикла для выполнения алгоритма защищенного хеширования с шифром. Например, в одном варианте воплощения шестнадцатеричный диапазон 0×0F в непосредственном байтовом операнде может указывать на то, что команда должна выполнить все шестнадцать (16) итераций алгоритма хеширования с шифром, тогда как шестнадцатеричный диапазон 0×FF в непосредственном байтовом операнде может указывать на то, что команда должна выполнить только одну итерацию цикла шестнадцать (16), или шестнадцатеричный диапазон 0×F8 в непосредственном байтовом операнде может указывать на то, что команда должна выполнить итерации: с цикла шестнадцать (16) по цикл девять (9), в режиме дешифрования алгоритма хеширования с шифром. Следует понимать, что одно неожиданное преимущество от использования шифра в качестве алгоритма хеширования, в противоположность однонаправленным алгоритмам хеширования, заключается в том, что он является обратимым, что может помочь с конструированием ключей для балансировки нагрузки, которые обеспечивают требуемые характеристики (например, стойкое и/или согласующееся хеширование), позволяя при этом введение новых ключей для воспрепятствования атаке (например, такой как атака с целью отказа в обслуживании). Другое неожиданное преимущество от выполнения в качестве алгоритма хеширования только указанного количества итераций шифра заключается в том, что для каждого цикла или диапазона циклических итераций могут быть использованы различные наборы ключей, что обеспечивает результаты шифрования, которые невозможны при использовании стандартной схемы с подключом.

Следует понимать, что команды для использования алгоритма защищенного хеширования с шифром, как в описанных здесь вариантах воплощения изобретения, могут быть использованы для обеспечения функциональных возможностей защищенного хеширования в приложениях, таких как приложения для обеспечения балансировочного распределения нагрузки и/или защиту от атак, имеющих целью отказ в обслуживании, и так далее, не требуя при этом чрезмерной сложности вычислений или неприемлемых времен задержки, но тем не менее предусматривая хорошо выбранные настройки для воспрепятствования атакам и вдобавок к этому не уменьшая требуемое качество обслуживания в этом процессе.

В нижеследующем описании для обеспечения более полного понимания вариантов воплощения изобретения приводятся многочисленные конкретные подробности, такие как логика обработки данных, типы процессоров, микроархитектурные условия, события, механизмы разблокирования и тому подобное. Специалисту в данной области техники следует, однако, понимать, что изобретение может быть осуществлено на практике и без таких конкретных подробностей. В дополнение к этому некоторые хорошо известные структуры, схемы и тому подобное не показаны подробно для того, чтобы избежать излишнего затруднения понимания вариантов воплощения изобретения.

Хотя нижеследующие варианты воплощения изобретения описаны в отношении процессора, другие варианты воплощения изобретения применимы к другим типам интегральных схем и логических устройств. Технологии и концепции, аналогичные вариантам воплощения изобретения, могут быть применены к другим типам схем или полупроводниковых устройств, которые могут выиграть от более высокой пропускной способности и повышенной производительности конвейера. Концепции вариантов воплощения изобретения применимы к любому процессору или машине, которая выполняет манипулирование данными. Однако изобретение не ограничено процессорами или машинами, которые выполняют операции над 512-разрядными, 256-разрядными, 128-разрядными, 64-разрядными, 32-разрядными или 16-разрядными данными и могут быть применены к любому процессору и машине, в которой выполняется манипуляция или управление данными. В дополнение к этому в нижеследующем описании приводятся примеры и на прилагаемых чертежах показаны разнообразные примеры для целей иллюстрации. Однако эти примеры не должны толковаться в ограничивающем смысле, поскольку они предназначены просто для того, чтобы дать примеры вариантов воплощения изобретения, а не дать исчерпывающий перечень всех возможных реализаций вариантов воплощения изобретения.

Хотя нижеприведенные примеры описывают обработку и распределение команд в контексте исполняющих блоков и логических схем, другие варианты воплощения изобретения могут быть реализованы посредством данных и/или команд, хранящихся на машиночитаемом, материальном носителе информации, которые при их выполнении машиной заставляют машину выполнять функции, согласующиеся с, по меньшей мере, одним вариантом воплощения изобретения. В одном варианте воплощения изобретения функции, связанные с вариантами воплощения изобретения, воплощены в исполняемых машиной командах. Эти команды могут быть использованы для того, чтобы заставлять универсальный или специализированный процессор, который запрограммирован посредством этих команд, выполнять этапы изобретения. Варианты воплощения изобретения могут быть предоставлены в виде компьютерного программного продукта или программного обеспечения, которое может включать в себя машиночитаемый или читаемый компьютером носитель информации, хранящий на себе команды, которые могут быть использованы для программирования компьютера (или других электронных устройств) на выполнение одной или более операций, соответствующих вариантам воплощения изобретения. В качестве альтернативы этапы вариантов воплощения изобретения могли бы быть выполнены специальными компонентами аппаратного обеспечения, которые содержат неперепрограммируемую логику для выполнения этапов, или любым сочетанием программируемых компьютерных компонентов и неперепрограммируемых компонентов аппаратного обеспечения.

Команды, используемые для программирования логики на выполнение вариантов воплощения изобретения, могут храниться в памяти в системе, такой как DRAM (динамичное оперативное запоминающее устройство), кэш, флэш-память или другое запоминающее устройство. Кроме того, эти команды могут быть распространены по сети или посредством других читаемых компьютером носителей информации. Таким образом, машиночитаемый носитель информации может включать в себя любой механизм для хранения или передачи информации в форме, читаемой машиной (например, компьютером), но не ограничен: гибкими магнитными дисками, оптическими дисками, компакт-диском, постоянным запоминающим устройством (CD-ROM (постоянными запоминающими устройствами на компакт-дисках)), и магнитооптическими дисками, постоянным запоминающим устройством (ROM-устройствами), оперативным запоминающим устройством (RAM), стираемым программируемым постоянным запоминающим устройством (EPROM), электрически стираемым программируемым постоянным запоминающим устройством (EEPROM), магнитными или оптическими картами, флэш-памятью или материальным, машиночитаемым запоминающим устройством, используемым при передаче информации по сети "Интернет" через электрические, оптические, акустические или другие формы распространяемых сигналов (например, несущие, инфракрасные сигналы, цифровые сигналы и так далее). Соответственно читаемый компьютером носитель информации включает в себя любой тип материального машиночитаемого носителя информации, подходящего для хранения или передачи электронных команд или информации в форме, читаемой машиной (например, компьютером).

Конструкция может проходить через различные стадии: от создания до моделирования и до изготовления. Данные, представляющие конструкцию, могут представлять конструкцию множеством способов. Сначала, что является полезным при моделировании, аппаратные средства могут быть представлены с использованием языка описания аппаратных средств или другого языка функционального описания. В дополнение к этому на некоторых стадиях процесса проектирования может быть выполнена модель уровня схем с логикой и/или элементами транзисторной логики. Кроме того, большинство конструкций на некоторой стадии достигают уровня данных, представляющих физическое размещение различных устройств в модели аппаратных средств. В случае, при котором используются традиционные технологии производства полупроводников, данные, представляющие модель аппаратных средств, могут представлять собой данные, указывающие на присутствие или отсутствие различных признаков на различных маскирующих слоях для фотошаблонов, используемых для производства интегральной схемы. В любом представлении конструкции данные могут храниться на любой форме машиночитаемого носителя информации. Память или магнитное или оптическое запоминающее устройство, такое как диск, могут являться этим машиночитаемым носителем информации, предназначенным для хранения информации, переданной посредством оптической или электрической волны, модулированной или иным образом сгенерированной для передачи такой информации. Когда осуществляется передача электрической несущей, указывающей или переносящей код или конструкцию, то в той мере, в какой выполняется копирование, буферизация или ретрансляция электрического сигнала, создается новая копия. Таким образом, поставщик услуг связи или поставщик сетевых услуг могут сохранить на материальном, машиночитаемом носителе информации, по меньшей мере, временно, некоторую вещь, такую как информация, закодированная в несущей, воплощающую технологии вариантов воплощения изобретения.

В современных процессорах множество различных исполняющих блоков используется таким образом, чтобы обрабатывать и исполнять разнообразие кода и команд. Не все команды созданы равными, поскольку некоторые завершаются более быстро, в то время как другие могут до своего завершения занять некоторое количество периодов тактовых импульсов. Чем выше пропускная способность для команд, тем лучше общая производительность процессора. Таким образом, было бы выгодно, чтобы как можно больше команд исполнялось настолько быстро, насколько это возможно. Однако существуют некоторые команды, которые имеют более высокую сложность и требуют большего в том, что касается времени исполнения и ресурсов процессора. Например, существуют команды на вычисления с плавающей запятой, операции загрузки/сохранения в памяти, перемещения данных и так далее.

По мере того, как все больше компьютерных систем используется в Интернет-приложениях, текстовых и мультимедийных приложениях, со временем вводилась дополнительная поддержка процессора. В одном варианте воплощения изобретения набор команд может быть связан с одной или более архитектурами компьютера, включающими в себя типы данных, команды, архитектуру регистров, способы адресации, архитектуру памяти, обработку прерываний и особых ситуаций и внешний ввод данных и вывод данных (I/O).

В одном варианте воплощения изобретения архитектура набора команд (ISA-архитектура) может быть реализована посредством одной или более микроархитектур, которые включают в себя логику и схемы процессора, используемые для реализации одного или более набора команд. Соответственно процессоры с различной микроархитектурой могут совместно использовать, по меньшей мере, часть общего набора команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core™ и процессоры от компании Advanced Micro Devices, Inc., Саннивейл, штат Калифорния, США, реализуют почти идентичные версии набора команд x86 (с некоторыми расширениями, которые были добавлены с более новыми версиями), но имеют различающиеся внутренние конструкции. Аналогичным образом, процессоры, сконструированные другими компаниями-разработчиками процессоров, такими как ARM Holdings, Ltd., MIPS, или их лицензиатами или последователями могут совместно использовать, по меньшей мере, часть общего набора команд, но могут включать в себя различающиеся конструкции процессора. Например, одна и та же архитектура регистров ISA-архитектуры может быть реализована различными способами в различных микроархитектурах с использованием новых или хорошо известных технологий, включая в себя выделенные физические регистры, один или более динамически распределяемых физических регистров, использующих механизм переименования регистров (например, с использованием таблицы альтернативных имен регистров (RAT-таблицы), переупорядочивающего буфера (ROB-буфера) и регистрового файла изъятия. В одном варианте воплощения изобретения регистры могут включать в себя один или более регистров, архитектур регистров, регистровых файлов или других наборов регистров, которые могут быть или могут не быть адресуемыми для разработчика программного обеспечения.

В одном варианте воплощения изобретения команда может включать в себя один или более форматов команды. В одном варианте воплощения изобретения формат команды может указывать различные поля (количество разрядов, место расположения разрядов, и так далее) для определения, среди прочего, операции, подлежащей выполнению, и операнда (операндов), над котором (которыми) должна быть выполнена эта операция. Некоторые форматы команд могут быть дополнительно подразделены по шаблонам команд (или подформатам). Например, шаблоны команд некоторого данного формата команды могут быть определены как имеющие различные подмножества полей формата команды и/или определены как имеющие некоторое данное поле, интерпретируемое различным образом. В одном варианте воплощения изобретения команда выражается с использованием формата команды (и, если это определено, в некотором заданном одном из шаблонов команды этого формата команды) и определяет или указывает операцию и операнды, которыми будет оперировать эта операция.

Научные, финансовые, универсальные автовекторизируемые приложения, RMS-приложения (приложения с распознаванием, разработкой и синтезом) и визуальные и мультимедийные приложения (например, двумерная/трехмерная графика, обработка изображений, сжатие видеоданных/восстановление сжатых видеоданных, алгоритмы распознавания речи и манипуляции аудиоданными) могут требовать, чтобы одна и та же операция выполнялась над большим количеством порций данных. В одном варианте реализации изобретения аббревиатура SIMD (с одним потоком команд и многими потоками данных) относится к типу команды, которая заставляет процессор выполнять операцию над множественными элементами данных. Технология SIMD может быть использована в процессорах, которые могут логически разделять разряды в регистре на некоторое количество элементов данных фиксированного размера или переменного размера, каждый из которых представляет отдельное значение. Например, в одном варианте воплощения изобретения разряды в 64-разрядном регистре могут быть организованы как операнд-источник, содержащий четыре отдельных 16-разрядных элемента данных, каждый из которых представляет отдельное 16-разрядное значение. Этот тип данных может именоваться как 'упакованный' тип данных или 'векторный' тип данных, и операнды этого типа данных именуются как операнды упакованных данных или векторные операнды. В одном варианте воплощения изобретения порция упакованных данных или вектор может представлять собой последовательность элементов упакованных данных, хранящихся в одном регистре, и операнд упакованных данных или векторный операнд может представлять собой операнд-источник или операнд-адресат в SIMD-команде (или 'команде с упакованными данными' или 'векторной команде'). В одном варианте воплощения изобретения SIMD-команда определяет отдельную векторную операцию, которая должна быть выполнена над двумя векторными операндами-источниками для того, чтобы сгенерировать векторный операнд-адресат (также именуемый как результирующий векторный операнд), имеющий тот же самый или другой размер, с тем же самым или другим количеством элементов данных и в том же самом или другом порядке следования элементов данных.

Технология SIMD, такая как та, что используется процессорами Intel® Core™, имеющими набор команд, включающий в себя команды х86, MMX™ (Мультимедийного расширения), расширения SIMD для потоковой обработки (SSE - расширений), SSE 2, SSE 3, SSE 4.1 и SSE 4.2, процессорами ARM, такими как семейство процессоров ARM Cortex®, имеющих набор команд, включающий в себя векторные команды с плавающей запятой (VFP - команды) и/или команды технологии NEON, и процессорами MIPS, такими как семейство процессоров Loongson, разработанных Институтом вычислительной техники (ICT) Китайской Академии Наук, сделала возможным значительное повышение производительности приложения (Core™ и ММХ™ представляют собой зарегистрированные товарные знаки или товарные знаки корпорации Intel Corporation, Санта-Клара, штат Калифорния, США).

В одном варианте воплощения изобретения термины "регистры/данные адресата и источника" представляют собой общие термины, представляющие источник и адресат соответствующих данных или операции. В некоторых вариантах воплощения изобретения они могут быть реализованы посредством регистров, памяти или других запоминающих областей, имеющих другие названия или функции, чем те, которые изображены. Например, в одном варианте реализации изобретения "DEST1" может представлять собой регистр временного запоминания или другую запоминающую область, тогда как "SRC1" и "SRC2" могут представлять собой первый и второй запоминающие регистры-источники или другую область памяти и так далее. В других вариантах воплощения изобретения две или более области из числа запоминающих областей SRC и DEST могут соответствовать различным элементам хранения данных в пределах одной и той же запоминающей области (например, SIMD - регистра). В одном варианте воплощения изобретения один из регистров-источников может также действовать в качестве регистра-адресата, например, при записи результата операции, выполненной над первыми и вторыми данными источников, в обратном направлении, в один из двух регистров - источников, служащий в качестве регистра-адресата.

Фиг. 1A представляет собой структурную схему приводимой в качестве примера вычислительной системы, сформированной с процессором, который включает в себя исполняющие блоки для исполнения команды в соответствии с одним вариантом воплощения изобретения. Система (100) включает в себя компонент, такой как процессор (102), для использования исполняющих блоков, включающих в себя логику для выполнения алгоритмов для обработки данных, в соответствии с изобретением, такой как в описанном здесь варианте воплощения изобретения. Система (100) является представителем систем обработки данных, основанных на микропроцессорах Pentium® III, Pentium® 4, Xeon™, Itanium®, XScale® и/или StrongARM™, поставляемых корпорацией Intel Corporation, Санта Клара, штат Калифорния, США, хотя могут также использоваться и другие системы (включающие в себя персональные компьютеры, имеющие другие микропроцессоры, инженерные рабочие станции, телевизионные абонентские приставки и тому подобное). В одном варианте воплощения изобретения приводимая в качестве примера система (100) может исполнять версию операционной системы WINDOWS®, поставляемой корпорацией Microsoft Corporation, г. Редмонд, Вашингтон, США, хотя могут также использоваться и другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические пользовательские интерфейсы. Таким образом, варианты воплощения изобретения не ограничены никаким конкретным сочетанием схем аппаратного обеспечения и программного обеспечения.

Варианты воплощения изобретения не ограничены компьютерными системами. Альтернативные варианты воплощения изобретения могут быть использованы в других устройствах, таких как карманные устройства, и встроенных вариантах применения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства связи по Интернет-протоколу, цифровые фотокамеры, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Встроенные варианты применения могут включать в себя микроконтроллер, процессор цифровой обработки сигналов (DSP-процессор), внутрикристальную систему, сетевые компьютеры (NetPC (сетевые персональные компьютеры)), телевизионные абонентские приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая может выполнять одну или более команд в соответствии с, по меньшей мере, одним вариантом воплощения изобретения.

Фиг. 1A представляет собой структурную схему компьютерной системы (100), сформированной с процессором (102), который включает в себя одно или более исполняющих блоков (108) для того, чтобы выполнять алгоритм для выполнения, по меньшей мере, одной команды в соответствии с одним вариантом воплощения изобретения. Один вариант воплощения изобретения может быть описан в контексте однопроцессорного настольного компьютера или системы сервера, но альтернативные варианты воплощения изобретения могут быть включены в состав многопроцессорной системы. Система (100) представляет собой пример архитектуры системы 'концентратор'. Компьютерная система (100) включает в себя процессор (102) для обработки сигналов данных. Процессор (102) может представлять собой микропроцессор компьютера со сложным набором команд (CISC - микропроцессор), микропроцессор для вычисления с сокращенным набором команд (RISC - микропроцессор), микропроцессор с командными словами сверхбольшой длины (VLIW - микропроцессор), процессор, реализующий комбинацию наборов команд или любое другое процессорное устройство, такое как, например, процессор цифровой обработки сигналов. Процессор (102) сопряжен с процессорной шиной (110), которая может передавать сигналы данных между процессором (102) и другими компонентами в системе (100). Элементы системы (100) выполняют свои традиционные функции, которые хорошо известны специалистам, знакомым с этой областью техники.

В одном варианте воплощения изобретения процессор (102) включает в себя внутреннюю кэш-память (104) уровня 1 (L1). В зависимости от архитектуры процессор (102) может иметь единственный внутренний кэш или множественные уровни внутреннего кэша. В качестве альтернативы в другом варианте воплощения изобретения кэш-память может находиться вне процессора (102). Другие варианты воплощения изобретения могут также включать в себя сочетание как внутренних, так и внешних кэшей в зависимости от конкретного варианта осуществления изобретения и потребностей. Регистровый файл (106) может сохранять различные типы данных в различных регистрах, включающих в себя целочисленные регистры, регистры с плавающей запятой, регистры состояния и регистр указателя команды.

В процессоре (102) также находится исполняющий блок (108), включающий в себя логику для выполнения целочисленных операций и операций с плавающей запятой. Процессор (102) также включает в себя постоянное запоминающее устройство для микрокода (ucode), которое хранит микрокод для некоторых макрокоманд. Для одного варианта воплощения изобретения исполняющий блок (108) включает в себя логику для обработки набора команд (109) для упакованных данных. Благодаря включению набора команд (109) для упакованных данных в набор команд универсального процессора (102), наряду со связанными с ним схемами для исполнения этих команд, операции, используемые многими мультимедийными приложениями, могут быть в универсальном процессоре (102) выполнены с использованием упакованных данных. Таким образом, многие мультимедийные приложения могут быть ускорены и исполнены более эффективно с использованием для выполнения операций над упакованными данными полной ширины процессорной шины данных. Это может устранить необходимость передавать более мелкие порции данных по процессорной шине данных для выполнения одной или более операций по одному элементу данных единовременно.

Альтернативные варианты воплощения исполняющего блока (108) могут также использоваться в микроконтроллерах, встроенных процессорах, графических устройствах, процессорах цифровой обработки сигналов и других типах логических схем. Система (100) включает в себя память (120). Память (120) может представлять собой динамическое оперативное запоминающее устройство (DRAM - устройство), статическое оперативное запоминающее устройство (SRAM - устройство), устройство с флэш-памятью или другое запоминающее устройство. Память (120) может хранить команды и/или данные, представленные сигналами данных, которые могут быть исполнены процессором (102).

С процессорной шиной (110) и памятью (120) сопряжена логическая интегральная схема (116) системы. Логическая интегральная схема (116) системы в проиллюстрированном варианте воплощения изобретения представляет собой концентратор-контроллер памяти (МСН). Процессор (102) может поддерживать связь с концентратором-контроллером (116) памяти через процессорную шину (110). Концентратор-контроллер (116) памяти обеспечивает тракт (118) связи с памятью, имеющий высокую пропускную способность, к памяти (120) для хранения команд и данных и для хранения графических команд, данных и текстур. Концентратор-контроллер (116) памяти должен направлять сигналы данных между процессором (102), памятью (120) и другими компонентами в системе (100) и служить мостом для сигналов данных между процессорной шиной (110), памятью (120) и входом/выходом (122) системы. В некоторых вариантах воплощения изобретения логическая интегральная схема (116) системы может предусматривать графический порт для сопряжения с графическим контроллером (112). Концентратор-контроллер (116) памяти сопряжен с памятью (120) посредством интерфейса (118) памяти. Графическая карта (112) сопрягается с концентратором-контроллером (116) памяти посредством межсоединения (114) Ускоренного графического порта (AGP - порта).

Для сопряжения концентратора-контроллера (116) памяти с концентратором-контроллером (130) ввода/вывода (ICH) система (100) использует специализированную интерфейсную шину (122) концентратора. Концентратор-контроллер (130) ввода/вывода обеспечивает прямые соединения с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Эта локальная шина ввода/вывода представляет собой высокоскоростную шину ввода/вывода, предназначенную для соединения периферийного оборудования с памятью (120), набором микросхем и процессором (102). Некоторые примеры представляют собой аудиоконтроллер, программно-аппаратный концентратор (128) (BIOS (базовая система ввода-вывода) флэш-памяти), приемопередатчик (126) беспроводной связи, запоминающее устройство (124) для данных, унаследованный контроллер ввода/вывода, содержащий интерфейсы пользовательского ввода и клавиатуры, последовательный порт расширения, такой как Универсальная последовательная шина (USB), и сетевой контроллер (134). Запоминающее устройство (124) для данных может содержать накопитель на жестких магнитных дисках, накопитель на гибких магнитных дисках, устройство CD-ROM (постоянное запоминающее устройство на компакт-диске), устройство с флэш-памятью или другое запоминающее устройство большой емкости.

Для другого варианта воплощения системы команда в соответствии с одним вариантом воплощения изобретения может быть использована с внутрикристальной системой. Один вариант воплощения внутрикристальной системы содержит процессор и память. Память для одной такой системы представляет собой флэш-память. Флэш-память может быть расположена в том же самом кристалле, что и процессор и другие компоненты системы. В дополнение к этому во внутрикристальной системе также могут быть расположены другие логические блоки, такие как контроллер памяти или графический контроллер.

На Фиг. 1B проиллюстрирована система (140) обработки данных, которая реализует принципы одного варианта воплощения изобретения. Специалист в данной области техники легко поймет, что описанные здесь варианты воплощения изобретения могут быть использованы с альтернативными системами обработки данных, что не выходит за рамки объема вариантов воплощения изобретения.

Вычислительная система (140) содержит ядро (159) обработки данных, способное выполнять, по меньшей мере, одну команду в соответствии с одним вариантом воплощения изобретения. Для одного варианта воплощения изобретения, ядро (159) обработки данных представляет блок обработки данных любого типа архитектуры, включая тип архитектуры: CISC (архитектура компьютера со сложным набором команд), RISC (архитектура компьютера с сокращенным набором команд) или VLIW (архитектура с командными словами сверхбольшой длины, но не ограничиваясь ими. Ядро (159) обработки данных может также подходить для изготовления в одном или более технологических процессах и, будучи представленным на машиночитаемых носителях информации достаточно подробно, может подходить для облегчения упомянутого изготовления.

Ядро (159) обработки данных содержит исполняющий блок (142), набор регистрового файла (регистровых файлов) (145) и декодер (144). Ядро (159) обработки данных также включает в себя дополнительные электрические схемы (не показанные на чертеже), которые не являются необходимыми для понимания вариантов воплощения изобретения. Исполняющий блок (142) используется для исполнения команды, принятой ядром (159) обработки данных. В дополнение к выполнению обычных процессорных команд исполняющий блок (142) может выполнять команды в наборе команд (143) для упакованных данных для выполнения операций над форматами упакованных данных. Набор команд (143) для упакованных данных включает в себя команды для выполнения вариантов воплощения изобретения и другие команды для упакованных данных. Исполняющий блок (142) посредством внутренней шины сопряжен с регистровым файлом (145). Регистровый файл (145) представляет запоминающую область на ядре (159) обработки данных, предназначенную для хранения информации, включающей в себя данные. Как было упомянуто выше, следует понимать, что запоминающая область, используемая для хранения упакованных данных, не является критически необходимой. Исполняющий блок (142) сопряжен к декодером (144). Декодер (144) используется для декодирования команд, принимаемых ядром (159) обработки данных, в управляющие сигналы и/или точки входа микрокода. В ответ на эти управляющие сигналы и/или точки входа микрокода, исполняющий блок (142) выполняет соответствующие операции. В одном варианте воплощения изобретения декодер используется для того, чтобы интерпретировать код операции команды, который укажет то, какую операцию следует выполнять над соответствующими данными, указанными внутри команды.

Ядро (159) обработки данных сопряжено с шиной (141) для поддержания связи с разнообразными другими устройствами системы, которые могут включать в себя, например, блок (146) управления синхронным динамическим оперативным запоминающим устройством (SDRAM - устройством), блок (147) управления статическим оперативным запоминающим устройством (SRAM - устройством), интерфейс (148) пакетной флэш-памяти, блок (149) управления картой Международной ассоциации производителей карт памяти для персональных компьютеров (PCMCIA)/компактной флэш-памяти, блок (150) управления жидкокристаллическим дисплеем (LCD - дисплеем), контроллер (151) прямого доступа к памяти (DMA - доступа) и интерфейс (152) альтернативного устройства управления шиной, но не ограничиваются ими. В одном варианте воплощения изобретения система (140) обработки данных может также содержать мост (154) ввода/вывода для поддержания связи с разнообразными устройствами ввода-вывода через шину (153) ввода/вывода. Такие устройства ввода/вывода могут включать в себя, например, универсальный асинхронный приемопередатчик (UART) (155), универсальную последовательную шину (USB) (156), универсальный асинхронный приемопередатчик (UART) (157) беспроводной связи Bluetooth и интерфейс (158) расширения для ввода/вывода, но не ограничиваются ими.

Один вариант воплощения системы (140) обработки данных предусматривает мобильную, сетевую и/или беспроводную связь, и ядро (159) обработки данных способно выполнять SIMD - операции (операции с одним потоком команд и многими потоками данных), включающие в себя операцию сравнения текстовых строк. Ядро (159) обработки данных может быть запрограммировано на разнообразные алгоритмы обработки аудиоинформации, видеоинформации, алгоритмы формирования изображения и алгоритмы связи, включающие в себя дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование Фурье (FFT - преобразование), дискретное косинусное преобразование (DCT - преобразование), и соответствующие им обратные преобразования; технологии сжатия данных/восстановления сжатых данных, такие как преобразование цветового пространства, оценка движения при кодировании видеоданных или компенсация движения при декодировании видеоданных; и функции модуляции/демодуляции (MODEM), такие как импульсно - кодовая модуляция (РСМ).

На Фиг. 1C проиллюстрированы другие альтернативные варианты воплощения системы обработки данных, способной к исполнению команд для обеспечения функциональных возможностей цикла защищенного хеширования с шифром. В соответствии с одним альтернативным вариантом воплощения изобретения система (160) обработки данных может включать в себя основной процессор (166), SIMD - сопроцессор (сопроцессор с одним потоком команд и многими потоками данных) (161), кэш-память (167) и систему (168) ввода/вывода. Система (168) ввода/вывода может, если требуется, быть сопряжена с интерфейсом (169) беспроводной связи. SIMD - сопроцессор (161) способен к выполнению операций, включая в себя команды в соответствии с одним вариантом воплощения изобретения. Ядро (170) обработки данных может подходить для изготовления в одном или более технологических процессах и, будучи представленным на машиночитаемых носителях информации достаточно подробно, может подходить для облегчения изготовления всей или части системы (160) обработки данных, включающей в себя ядро (170) обработки данных.

Для одного варианта воплощения изобретения, SIMD - сопроцессор (161) содержит исполняющий блок (162) и набор регистрового файла (регистровых файлов) (164). Один вариант воплощения основного процессора (166) содержит декодер (165) для распознавания команд набора (163) команд, включающего в себя команды в соответствии с одним вариантом воплощения изобретения, для исполнения исполняющим блоком (162). Для альтернативных вариантов воплощения изобретения SIMD - сопроцессор (161) также содержит, по меньшей мере, часть декодера (165 В) для того, чтобы декодировать команды набора (163) команд. Ядро (170) обработки данных также включает в себя дополнительные схемы (не показанные на чертеже), которые не являются необходимыми для понимания вариантов воплощения изобретения.

При работе основной процессор (166) исполняет поток команд обработки данных, управляющих операциями обработки данных общего типа, включающих в себя взаимодействия с кэш-памятью (167) и системой (168) ввода/вывода. В поток команд обработки данных встроены команды для SIMD - сопроцессора. Декодер (165) из основного процессора (166) распознает эти команды для SIMD - сопроцессора как относящиеся к типу, который должен исполняться приданным SIMD - сопроцессором (161). Соответственно основной процессор (166) выдает эти команды для SIMD - сопроцессора (или управляющие сигналы, представляющие команды для SIMD - сопроцессора) в шину (171) сопроцессора, из которой они принимаются каким-либо приданным SIMD - сопроцессором. В этом случае SIMD - сопроцессор (161) примет и исполнит любые принятые команды для SIMD - сопроцессора, предназначенные для него.

Для обработки посредством команд для SIMD - сопроцессора данные могут приниматься через интерфейс (169) беспроводной связи. В качестве одного примера речевая связь может приниматься в форме цифрового сигнала, который можно обрабатывать посредством команд для SIMD - сопроцессора таким образом, чтобы восстанавливать отсчеты цифровой аудиоинформации, представляющие речевую связь. В качестве другого примера сжатые аудиоинформация и/или видеоинформация могут быть приняты в форме цифрового потока битов, который можно обрабатывать посредством команд SIMD - сопроцессора таким образом, чтобы восстанавливать отсчеты цифровой аудиоинформации и/или кадры движущегося видеоизображения. Для одного варианта воплощения ядра (170) обработки данных основной процессор (166) и SIMD - сопроцессор (161) интегрированы в единое ядро (170) обработки данных, содержащее исполняющий блок (162), набор регистрового файла (регистровых файлов) (164) и декодер (165) для распознавания команд набора (163) команд, включающего в себя команды в соответствии с одним вариантом воплощения изобретения.

Фиг. 2 представляет собой структурную схему микроархитектуры для процессора (200), который включает в себя логические схемы для выполнения команд в соответствии с одним вариантом воплощения изобретения. В некоторых вариантах воплощения изобретения команда в соответствии с одним вариантом своего воплощения может быть реализована таким образом, чтобы оперировать над элементами данных, имеющими размеры: байта, слова, двойного слова, учетверенного слова и так далее, так же как типы данных, такие как целое число одинарной и двойной точности и типы данных с плавающей запятой. В одном варианте реализации изобретения передняя часть (201) без переупорядочения последовательности команд представляет собой часть процессора (200), которая осуществляет выборку команд, подлежащих исполнению, и подготавливает их для использования позже в процессорном конвейере. Передняя часть (201) может включать в себя несколько блоков. В одном варианте воплощения изобретения блок (226) опережающей выборки команд осуществляет выборку команд из памяти и подает их в декодер (228) команд, который, в свою очередь, декодирует или интерпретирует их. Например, в одном варианте воплощения изобретения декодер декодирует принятую команду на одну или более операций, именуемых как "микрокоманды" или "микрооперации" (также именуемых как "micro op" или "uop"), которые могут исполняться машиной. В других вариантах реализации изобретения декодер осуществляет синтаксический анализ команды, преобразуя ее в код операции и соответствующие поля данных и управления, которые используются микроархитектурой для выполнения операций в соответствии с одним вариантом воплощения изобретения. В одном варианте воплощения изобретения трассовый кэш (230) берет декодированные микрооперации и собирает их в упорядоченные последовательности программы или трассы в очереди (234) микроопераций на исполнение. Когда трассовый кэш (230) сталкивается со сложной командой, постоянное запоминающее устройство (232) для микрокода обеспечивает микрооперации, необходимые для выполнения операции.

Некоторые команды преобразуются в единственную микрооперацию, тогда как другим для выполнения полной операции требуются нескольких микроопераций. В одном варианте воплощения изобретения, если для выполнения команды необходимо больше чем четыре микрооперации, то декодер (228) для выполнения команды осуществляет доступ к постоянному запоминающему устройству (232) для микрокода. Для одного варианта воплощения изобретения команда может быть декодирована на небольшое количество микроопераций для обработки в декодере (228) команды. В другом варианте реализации изобретения, если для выполнения команды требуется ряд микроопераций, то команда может быть сохранена в постоянном запоминающем устройстве (232) для микрокода. Трассовый кэш (1330) обращается к программируемой логической матрице (PLA - матрице) точки входа для того, чтобы определить правильный указатель микрокоманды для того, чтобы считывать из постоянного запоминающего устройства (232) для микрокода последовательности микрокода для выполнения одной или более команд в соответствии с одним вариантом воплощения изобретения. После того, как постоянное запоминающее устройство (232) для микрокода заканчивает задание последовательности микроопераций для команды, передняя часть (201) этой машины возобновляет осуществление выборки микроопераций из трассового кэша (230).

Машина (203) исполнения с переупорядочением последовательности команд представляет собой то место, где команды подготавливаются к исполнению. Логика исполнения с переупорядочением последовательности команд имеет некоторое количество буферов для сглаживания и переупорядочения последовательности потока команд для оптимизации рабочих характеристик, когда команды движутся по конвейеру и планируются к исполнению. Логика распределителя распределяет буферные запоминающие устройства и ресурсы машины, в которых каждая микрооперация нуждается для своего исполнения. Логика переименования регистров переименовывает логические регистры в записи в регистровом файле. Распределитель также распределяет запись для каждой микрооперации в одной из двух очередей микроопераций: одной - для операций с памятью, и одной - для операций не с памятью, перед планировщиками команд: планировщиком памяти, быстрым планировщиком (202), медленным/универсальным планировщиком (204) микроопераций с плавающей запятой и простым планировщиком (206) микроопераций с плавающей запятой. Планировщики (202), (204), (206) микроопераций определяют то, когда микрооперация готова к исполнению, основываясь на готовности их зависимых источников входных регистровых операндов и доступности исполняющих ресурсов, в которых эти микрооперации нуждаются для выполнения своей работы. Быстрый планировщик (202) по одному варианту воплощения изобретения может осуществлять планирование каждую половину периода основных тактовых импульсов, тогда как другие планировщики могут осуществлять планирование только один раз за период тактовых импульсов основного процессора. Планировщики осуществляют арбитраж для портов отправки для планирования микроопераций к исполнению.

Регистровые файлы (208), (210) находятся между планировщиками (202), (204), (206) и исполняющими блоками (212), (214), (216), (218), (220), (222), (224) в исполняющей группе (211). Существует отдельный регистровый файл (208), (210) для соответственно целочисленных операций и операций с плавающей запятой. Каждый регистровый файл (208), (210) по одному варианту воплощения изобретения также включает в себя обходную сеть, которая может пропускать или направлять только что завершенные результаты, которые еще не были записаны в регистровый файл, к новым зависимым микрооперациям. Регистровый файл (208) для целочисленных операций и регистровый файл (210) для операций с плавающей запятой также способны осуществлять обмен данным друг с другом. Для одного варианта воплощения изобретения регистровый файл (208) для целочисленных операций разделен на два отдельных регистровых файла: один регистровый файл для 32 младших разрядов данных и второй регистровый файл для 32 старших разрядов данных. Регистровый файл (210) для операций с плавающей запятой, соответствующий одному варианту воплощения изобретения, имеет записи шириной в 128 разрядов, потому что команды с плавающей запятой обычно имеют операнды шириной от 64 до 128 разрядов.

Исполняющая группа (211) содержит исполняющие блоки (212), (214), (216), (218), (220), (222), (224), в которых фактически исполняются команды. Эта секция включает в себя регистровые файлы (208), (210), которые сохраняют значения целочисленных операндов данных и значения операндов данных с плавающей запятой, которые микрокомандам необходимо исполнить. Процессор (200) по одному варианту воплощения изобретения состоит из множества исполняющих блоков: блока (212) формирования адресов (AGU - блока), блока (214) формирования адресов, быстрого арифметико-логического блока (ALU) (216), быстрого арифметико-логическое блока (218), медленного арифметико-логического блока (220), арифметико-логического блока (222) для операций с плавающей запятой, блока (224) перемещения плавающей запятой. Для одного варианта воплощения изобретения блоки (222), (224) исполнения операций с плавающей запятой исполняют операции с плавающей запятой, операции ММХ (Мультимедийного расширения), SIMD (с Одним потоком команд и многими потоками данных) и SSE (Расширения SIMD для потоковой обработки) или другие операции. Арифметико-логический блок (222) для операций с плавающей запятой, соответствующий одному варианту воплощения изобретения, включает в себя делительный блок для операций с плавающей запятой, имеющий размер: 64 разряда на 64 разряда, для исполнения микроопераций деления, извлечения квадратного корня и нахождения остатка. Для вариантов воплощения изобретения команды, включающие в себя значение с плавающей запятой, могут обрабатываться посредством аппаратных средств вычислений с плавающей запятой. В одном варианте воплощения изобретения операции арифметико-логического блока направляются быстродействующим арифметико-логическим исполняющим блокам (216), (218). Быстрые арифметико-логические блоки (216), (218) по одному варианту воплощения изобретения могут исполнять быстрые операции с эффективным временем задержки, составляющим половину периода тактовых импульсов. Для одного варианта воплощения изобретения наиболее сложные целочисленные операции направляются медленному арифметико-логическому блоку (220), поскольку медленный арифметико-логический блок (220) включает в себя аппаратные средства исполнения целочисленных вычислений, предназначенные для типа операций с длительным временем задержки, такие как умножитель, сдвигатели, логика признаков и обработка ветвления. Блоками (212), (214) формирования адресов исполняются операции загрузки/сохранения в памяти. Для одного варианта воплощения изобретения арифметико-логические блоки (216), (218), (220) для целочисленных операций описаны в контексте выполнения целочисленных операций над 64-разрядными операндами данных. В альтернативных вариантах воплощения изобретения арифметико-логические блоки (216), (218), (220) могут быть реализованы таким образом, чтобы поддерживать разнообразные количества разрядов данных, включающие в себя 16, 32, 128, 256 и так далее. Аналогичным образом блоки (222), (224) для операций с плавающей запятой могут быть реализованы таким образом, чтобы поддерживать некоторый диапазон операндов, имеющих разрядность различной ширины. Для одного варианта воплощения изобретения блоки (222), (224) для операций с плавающей запятой могут, в сочетании с мультимедийными командами и SIMD - командами, оперировать с операндами упакованных данных, имеющими ширину в 128 разрядов.

В одном варианте воплощения изобретения планировщики (202), (204), (206) микроопераций отправляют зависимые операции прежде, чем закончится исполнение загрузки операции-предка. Поскольку теоретически микрооперации планируются и исполняются в процессоре (200), то процессор (200) также включает в себя логику для обработки неудачных обращений к памяти. Если происходит неудача при загрузке данных в кэше данных, то могут иметь место зависимые операции, находящиеся на конвейере, которые оставили планировщика с временно неправильными данными. Механизм повторной обработки отслеживает и повторно исполняет команды, которые используют неправильные данные. Повторно обрабатываться должны только зависимые операции, а независимым операциям позволено завершиться. Планировщики и механизм повторной обработки, соответствующие одному варианту воплощения процессора, также спроектированы таким образом, чтобы улавливать команды, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Термин "регистры" может относиться к внутриплатным ячейкам памяти процессора, которые используются как часть команд для того, чтобы идентифицировать операнды. Другими словами, регистры могут быть такими, которые используются извне процессора (с перспективы программиста). Однако термин "регистры" по варианту воплощения изобретения не должен быть ограничен в своем значении некоторым конкретным типом электрических схем. Скорее, "регистр" по варианту воплощения изобретения способен хранить и предоставлять данные и выполнять описанные здесь функции. Описанные здесь регистры могут быть реализованы посредством электрических схем внутри процессора, использующих любое количество различных технологий, таких как выделенные физические регистры, динамически распределяемые физические регистры с использованием переименования регистров, сочетание выделенных и динамически распределяемых физических регистров и так далее. В одном варианте воплощения изобретения регистры для целочисленных данных хранят в себе тридцатидвухразрядные целочисленные данные. Регистровый файл по одному варианту воплощения изобретения также содержит восемь мультимедийных SIMD - регистров для упакованных данных. Для приводимого ниже обсуждения, "регистры" понимаются как представляющие собой регистры данных, спроектированные таким образом, чтобы хранить упакованные данные, такие как регистры ММХ™ (Мультимедийного расширения), имеющие ширину в 64 разряда (также в некоторых экземплярах именуемые как регистры 'mm' (мультимедийные)), в микропроцессорах, наделенных возможностями технологии ММХ™ от корпорации Intel Corporation, Санта - Клара, штат Калифорния, США. Эти ММХ - регистры, имеющиеся как в целочисленной форме, так и в форме с плавающей запятой, могут работать с элементами упакованных данных, которые сопровождают команды технологий SIMD и SSE (Расширения SIMD для потоковой передачи данных). Аналогичным образом, для хранения таких операндов упакованных данных могут также использоваться ХММ - регистры с шириной в 128 разрядов, относящиеся к технологии SSE 2, SSE 3, SSE 4 или выше (обычно именуемым как "SSEx"). В одном варианте воплощения изобретения при хранении упакованных данных и целочисленных данных регистрам не нужно проводить различие между этими двумя типами данных. В одном варианте воплощения изобретения целочисленные данные и данные с плавающая запятой либо содержатся в одном и том же регистровом файле или в различных регистровых файлах. Кроме того, в одном варианте воплощения изобретения данные с плавающей запятой и целочисленные данные могут храниться в различных регистрах или в одних и тех же регистрах.

В примерах, показанных на нижеследующих чертежах, описывается некоторое количество операндов данных. На Фиг. 3A проиллюстрированы различные представления типов упакованных данных в мультимедийных регистрах в соответствии с одним вариантом воплощения изобретения. На Фиг. 3A проиллюстрированы типы данных для упакованного байта (310), упакованного слова (320) и упакованного двойного слова (dword) (330) для операндов с шириной в 128 разрядов. Формат (310) упакованного байта из этого примера имеет длину в 128 разрядов и содержит шестнадцать упакованных байтовых элементов данных. Байт определен здесь как 8 разрядов данных. Информация для каждого байтового элемента данных хранится в разрядах: с разряда 7 по разряд 0 - для байта 0; с разряда 15 по разряд 8 - для байта 1; с разряда 23 по разряд 16 - для байта 2; и, наконец, с разряда 120 по разряд 127 - для байта 15. Таким образом, в регистре используются все имеющиеся разряды. Эта организация хранения информации повышает эффективность хранения в процессоре. Также, при осуществлении доступа к шестнадцати элементам данных одна операция может теперь выполняться над шестнадцатью элементами данных параллельно.

Обычно элемент данных представляет собой индивидуальный фрагмент данных, который хранится в одном регистре или ячейке памяти вместе с другими элементами данных той же самой длины. В последовательностях упакованных данных, относящихся к технологии SSEx, количество элементов данных, хранящихся в ХММ – регистре, составляет 128 разрядов, разделенных по длине на разряды индивидуального элемента данных. Аналогичным образом в последовательностях упакованных данных, относящихся к технологии ММХ (Мультимедийного расширения) и SSE (Расширения SIMD для потоковой обработки, количество элементов данных, хранящихся в ММХ - регистре, составляет 64 разряда, разделенные по длине на разряды индивидуального элемента данных. Хотя типы данных, проиллюстрированные на Фиг. 3A, имеют длину в 128 разрядов, варианты воплощения изобретения могут также оперировать операндами, имеющими ширину в 64 разряда, ширину в 256 разрядов, ширину в 512 разрядов или имеющими другие размеры. Формат (320) упакованного слова из этого примера имеет длину в 128 разрядов и содержит восемь упакованных элементов данных - слов. Каждое упакованное слово содержит шестнадцать разрядов информации. Формат (330) упакованных двойных слов, показанный на Фиг. 3A, имеет длину в 128 разрядов и содержит четыре упакованных элемента данных - двойных слова. Каждый упакованный элемент данных - двойное слово содержит тридцать два разряда информации. Упакованное учетверенное слово имеет длину в 128 разрядов и содержит два упакованных элемента данных - учетверенных слова.

На Фиг. 3B проиллюстрированы альтернативные форматы хранения данных в регистре. Каждые упакованные данные могут включать в себя больше чем один независимый элемент данных. Проиллюстрировано три формата упакованных данных: упакованные половинные данные (341), упакованные одинарные данные (342) и упакованные двойные данные (343). Один вариант воплощения упакованных половинных данных (341), упакованных одинарных данных (342) и упакованных двойных данных (343) содержит элементы данных с фиксированной запятой. Для альтернативного варианта воплощения изобретения один или более форматов из числа: упакованных половинных данных (341), упакованных одинарных данных (342) и упакованных двойных данных (343), могут содержать элементы данных с плавающей запятой. Один альтернативный вариант воплощения упакованных половинных данных (341) имеет длину в сто двадцать восемь разрядов и содержит восемь 16-разрядных элементов данных. Один вариант воплощения упакованных одинарных данных (342) имеет длину сто двадцать восемь разрядов и содержит четыре 32-разрядных элемента данных. Один вариант воплощения упакованных двойных данных (343) имеет длину в сто двадцать восемь разрядов и содержит два 64-разрядных элемента данных. Следует понимать, что такие форматы упакованных данных могут быть далее расширены на другие разрядности регистра, например на 96 разрядов, 160 разрядов, 192 разряда, 224 разряда, 256 разрядов, 512 разрядов или больше.

На Фиг. 3C проиллюстрированы разнообразные представления типов упакованных данных со знаком и без знака в мультимедийных регистрах в соответствии с одним вариантом воплощения изобретения. Представление упакованного байта (344) без знака иллюстрирует хранение упакованного байта без знака в SIMD - регистре. Информация для каждого байтового элемента данных хранится в разрядах: с разряда семь по разряд ноль - для байта ноль; с разряда пятнадцать по разряд восемь - для байта один; с разряда двадцать три по разряд шестнадцать - для байта два, и так далее; и, наконец, с разряда сто двадцать по разряд сто двадцать семь - для байта пятнадцать. Таким образом, в регистре используются все имеющиеся разряды. Эта организация хранения информации может повысить эффективность хранения в процессоре. Также, при осуществлении доступа к шестнадцати элементам данных одна операция может теперь выполняться над шестнадцатью элементами данных параллельно. Представление (345) упакованного байта со знаком иллюстрирует хранение упакованного байта со знаком. Отметим, что восьмой разряд каждого байтового элемента данных представляет собой указатель знака. Представление (346) упакованного слова без знака иллюстрирует то, как слова: со слова семь по слово ноль, хранятся в SIMD - регистре. Представление (347) упакованного слова со знаком аналогично внутрирегистровому представлению (346) упакованного слова без знака. Отметим, что шестнадцатый разряд каждого элемента данных - слова представляет собой указатель знака. Представление (348) упакованного двойного слова без знака показывает то, как хранятся элементы данных - двойные слова. Представление (349) упакованного двойного слова со знаком аналогично внутрирегистровому представлению (348) упакованного двойного слова без знака. Отметим, что необходимый знаковый разряд представляет собой тридцать второй разряд каждого элемента данных - двойного слова.

Фиг. 3D представляет собой изображение одного варианта воплощения формата (360) кодирования операции (кода операции), который имеет тридцать два разряда и режимы адресации операнда, хранимого в регистре/памяти, соответствующие типу формата кода операции, описанному в "Intel® 64 and IA-32 Intel Architecture Software Developer's Manual Combined Volumes 2A and 2B: Instruction Set Reference A - Z" ("Объединенные тома 2A и 2B Руководства разработчику программного обеспечения для архитектуры Intel® 64 и Intel IA - 32: Справочник по набору команд: с А по Z"), который доступен у корпорации Intel Corporation, Санта-Клара, штат Калифорния, США, во всемирной сети (www) по адресу: intel.com/products/proccssor/manuals/. В одном варианте воплощения изобретения команда может быть закодирована посредством одного или больше полей (361) и (362). Может быть идентифицировано до двух мест расположения операндов, приходящихся на одну команду, включая сюда до двух идентификаторов (364) и (365) операндов-источников. Для одного варианта воплощения изобретения идентификатор (366) операнда-адресата является тем же самым, что и идентификатор (364) операнда-источника, тогда как в других вариантах воплощения изобретения они различаются. Для альтернативного варианта воплощения изобретения идентификатор (366) операнда-адресата является тем же самым, что и идентификатор (365) операнда-источника, тогда как в других вариантах воплощения изобретения они различаются. В одном варианте воплощения изобретения, результаты исполнения команды записываются на место одного из операндов-источников, идентифицированных идентификаторами (364) и (365) операндов-источников, тогда как в других вариантах воплощения изобретения идентификатор (364) соответствует элементу регистра-источника, а идентификатор (365) соответствует элементу регистра-адресата. Для одного варианта воплощения изобретения идентификаторы (364) и (365) операндов могут быть использованы для идентификации 32-разрядных или 64-разрядных операнда-источника и операнда-адресата.

Фиг. 3E представляет собой изображение другого альтернативного формата (370) кодирования операции (кода операции), который имеет сорок или больше разрядов. Формат (370) кода операции соответствует формату (360) кода операции и содержит необязательный префиксный байт (378). Команда в соответствии с одним вариантом воплощения изобретения может быть закодирована посредством одного или более полей (378), (371) и (372). Посредством двух идентификаторов (374) и (375) операндов-источников и посредством префиксного байта может быть идентифицировано до двух мест расположения операндов, приходящихся на одну команду. Для одного варианта воплощения изобретения префиксный байт (378) может использоваться для идентификации 32-разрядных или 64-разрядных операндов источника и адресата. Для одного варианта воплощения изобретения идентификатор (376) операнда-адресата является тем же самым, что и идентификатор (374) операнда источника, тогда как в других вариантах воплощения изобретения они различаются. Для альтернативного варианта воплощения изобретения идентификатор (376) операнда-адресата является тем же самым, что и идентификатор (375) операнда-источника, тогда как в других вариантах воплощения изобретения они различаются. В одном варианте воплощения изобретения команда оперирует одним или более операндами из числа операндов, идентифицированных идентификаторами (374) и (375) операндов, и результаты исполнения команды записываются на место одного или более операндов, идентифицированных идентификаторами (374) и (375) операндов, тогда как в других вариантах воплощения изобретения операнды, идентифицированные идентификаторами (374) и (375) записываются в другой элемент данных в другом регистре. Форматы (360) и (370) кода операции позволяют адресацию: из регистра в регистр; из памяти в регистр; в регистр посредством памяти; в регистр посредством регистра, в регистр посредством непосредственного операнда, из регистра в память, указываемую частично посредством полей (363) и (373) MOD и необязательными байтами базы - индекса - шкалы и смещения.

Обратимся далее к Фиг. 3F, в некоторых альтернативных вариантах воплощения изобретения, 64-разрядные (или 128-разрядные или 256-разрядные или 512-разрядный или имеющие более высокую разрядность) арифметические операции с одним потоком команд и многими потоками данных (SIMD) могут быть выполнены посредством команды обработки данных сопроцессором (CDP - обработки) команда. Формат (380) кодирования операции (кода операции) изображает одну такую команду CDP - обработки, имеющую поля (382) и (389) кода операции CDP - обработки. Тип команды CDP - обработки для альтернативных вариантов воплощения изобретения операции могут быть закодированы посредством одного или более полей: 383, 384, 387 и 388. Может быть идентифицировано до трех мест расположения операндов, приходящихся на одну команду, включая сюда до двух идентификаторов (385) и (390) операндов-источников и один идентификатор (386) операнда-адресата. Один вариант воплощения сопроцессора может оперировать 8-, 16-, 32- и 64-разрядными значениями. Для одного варианта воплощения изобретения, команда выполняется над целочисленными элементами данных. В некоторых вариантах воплощения изобретения команда может исполняться в зависимости от условия, используя поле (381) условия. Для некоторых вариантов воплощения изобретения размеры данных источника могут быть закодированы посредством поля (383). В некоторых вариантах воплощения изобретения в отношении SIMD - полей может выполняться обнаружение нуля (Z), отрицательной величины (N), переноса (С) и переполнения (V). Для некоторых команд тип насыщения может быть закодирован посредством поля (384).

Обратимся далее к Фиг. 3G, которая представляет собой изображение другого альтернативного формата (397) кодирования операции (кода операции) для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующих другому варианту воплощения изобретения, корреспондирующего типу формата кода операции описанному в "Intel® Advanced Vector Extensions Programming Reference" ("Справочник по программированию усовершенствованных векторных расширений для Intel®"), который доступен у корпорации Intel Corp., Санта-Клара, штат Калифорния, США, во всемирной сети (www) по адресу: intel.com/products/processor/manuals/.

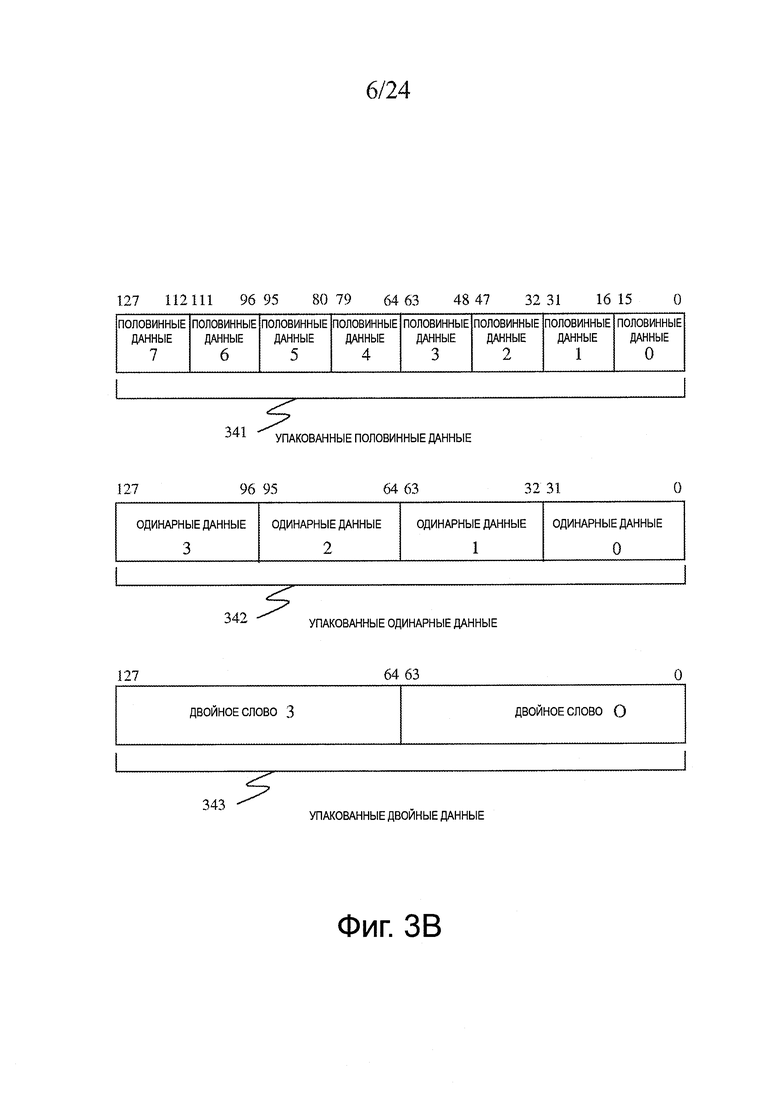

Первоначальный набор команд х86 предусматривал 1-байтовый код операции, при этом различные форматы адресного слога и непосредственного операнда, содержатся в дополнительных байтах, присутствие которых известно из первого байта с "кодом операции". В дополнение к этому имелись некоторые байтовые значения, которые были зарезервированы в качестве модификаторов кода операции (называемые префиксами, поскольку они должны были размещаться перед командой). Когда первоначальная палитра, состоящая из 256 байтов кода операции (включающая в себя эти специальные префиксные значения) была исчерпана, один байт был назначен в качестве перехода к новому набору, состоящему из 256 кодов операции. Поскольку были добавлены векторные команды (например, SIMD), то возникла потребность в большем количестве кодов операции, и "двухбайтовая" карта кода операции также была недостаточна, даже при ее расширении с помощью префиксов. С этой целью в дополнительные карты были добавлены новые команды, которые используют 2 байта плюс необязательный префикс в качестве идентификатора.

В дополнение к этому для того, чтобы содействовать дополнительным регистрам в 64-разрядном режиме, может быть использован дополнительный префикс (называемый "REX") между префиксами и кодом операции (и любыми байтами перехода, необходимыми для определения кода операции). В одном варианте воплощения изобретения REX может иметь 4 разряда "полезных данных" для того, чтобы указывать использование дополнительных регистров в 64-разрядном режиме. В других вариантах воплощения изобретения это он может иметь меньше или больше чем 4 разряда. Общий формат, по меньшей мере, одного набора команд (который, в общем, корреспондирует формату (360) и/или формату (370)) проиллюстрирован в общем виде следующим выражением: