УРОВЕНЬ ТЕХНИКИ

[0001] Память является важным элементом для запоминания информации в системе. Память может быть обеспечена посредством создания и поддержания некоторого количества разных состояний, таких как «0» и «1». Стираемое программируемое постоянное запоминающее устройство (erasable programmable read only memory - EPROM) является одним из типов энергонезависимой памяти, содержащим массив отдельно программируемых транзисторов с плавающим затвором, которые запоминают единицы памяти (например, биты), кодированные посредством удельной электропроводности запоминающих транзисторов.

[0002] Интегрированные печатающие головки (integrated print head - IPH) могут включать в себя память. IPH-память может быть использована для запоминания информации, такой как идентификатор пера, уникальный идентификатор, аналоговый серийный номер (ASN), информации о безопасности и другой информации для улучшения характеристик IPH.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

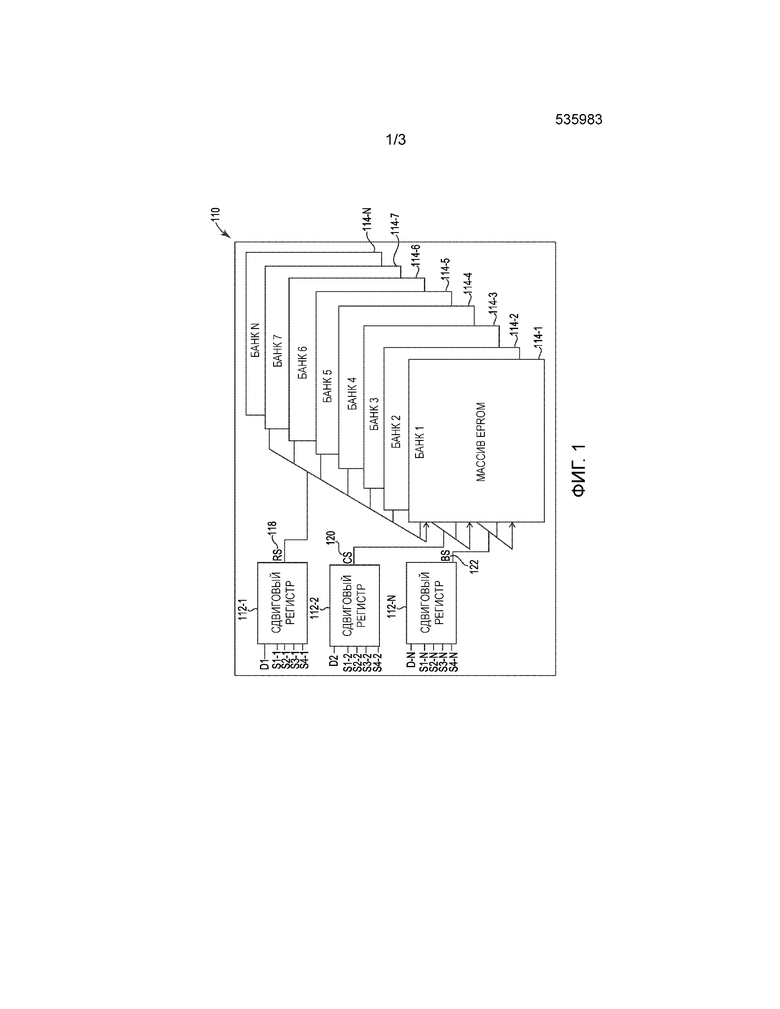

[0003] Фиг. 1 является схемой примера запоминающего устройства печатающей головки, согласно данному раскрытию.

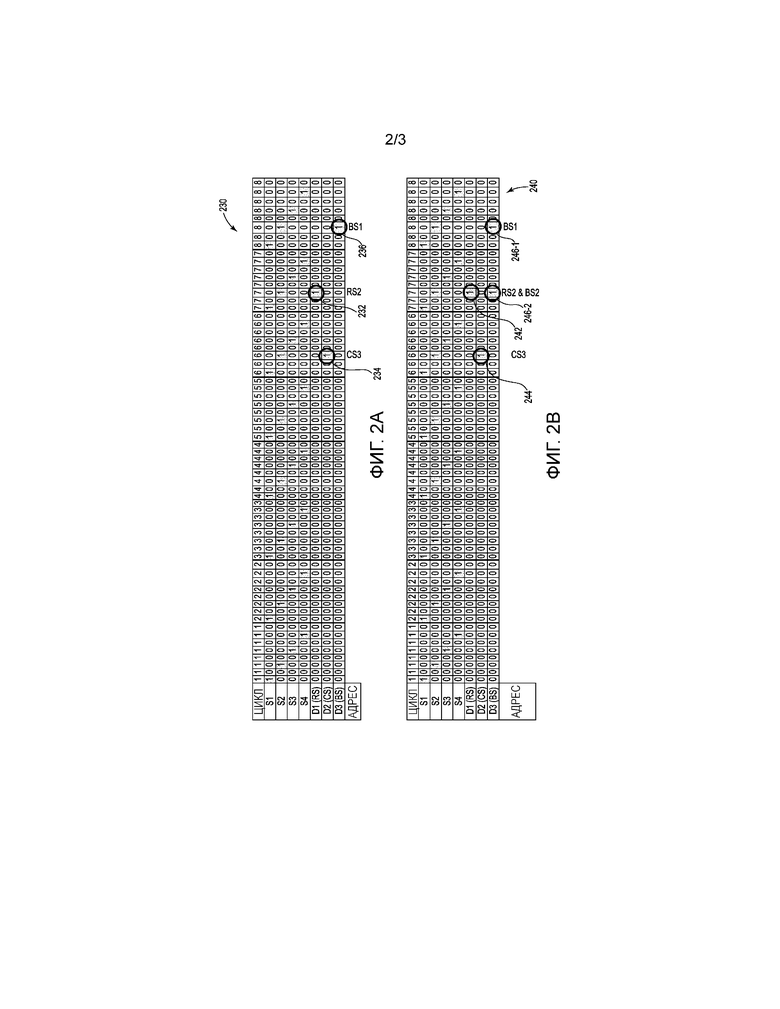

[0004] Фиг. 2А является таблицей, иллюстрирующей пример схемы трехмерной адресации для EPROM, согласно данному раскрытию.

[0005] Фиг. 2В является таблицей, иллюстрирующей пример схемы трехмерной параллельной адресации для EPROM, согласно данному раскрытию.

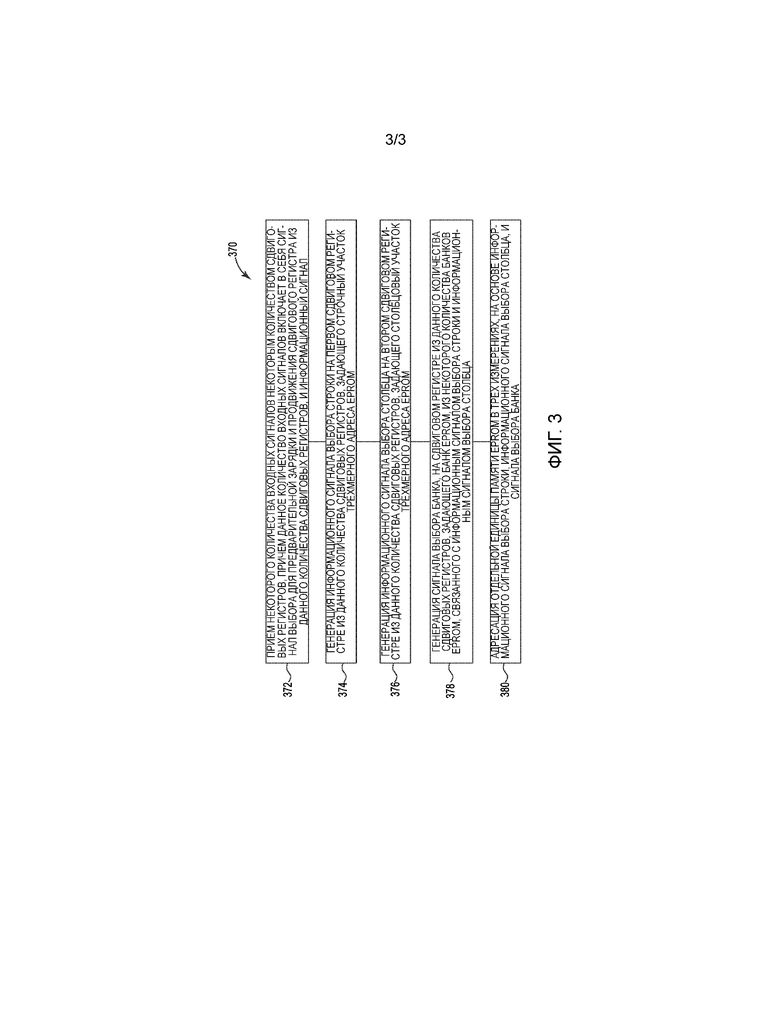

[0006] Фиг. 3 является блок-схемой последовательности операций примера способа для трехмерной адресации единицы памяти EPROM интегрированной печатающей головки.

ПОДРОБНОЕ ОПИСАНИЕ

[0007] Интегрированные печатающие головки (IPH) могут использовать множество разных технологий памяти. Например, IPH могут использовать технологию памяти с металлическими плавкими перемычками для запоминания информации. Однако стираемое программируемое постоянное запоминающее устройство (EPROM) обеспечивает преимущества по сравнению с технологией с металлическими плавкими перемычками, состоящие в том, что для транзистора селектора EPROM могут быть выполнены требования по относительно меньшим размерам, нет необходимости в потенциально повреждающем механическом усилии при программировании EPROM, и невозможно идентифицировать статус состояния при визуальном обследовании EPROM.

[0008] Способность IPH-платформы к реализации функций может быть ограничена величиной ее памяти (например, количеством адресуемых единиц памяти, которые хранятся в памяти). А именно, чем больше информации может быть запомнено на IPH, тем больше будет характеристик, которые могут быть реализованы на IPH. Количество адресуемых единиц памяти (например, битов) для IPH может быть ограничено многими факторами.

[0009] Общепринятую IPH EPROM адресацию выполняют с использованием прямой адресации. Прямая адресация использует независимый информационный сигнал для каждого банка EPROM. В результате, прямая адресация нуждается в одном регистре (например, сдвиговом регистре) на банк EPROM, для адресации единиц памяти EPROM соответствующего банка EPROM.

[0010] Величина полезной площади кремния (Si), доступная для данного регистра и соответствующего EPROM, может быть ограничена многими факторами. Например, ограничения размера, налагаемые размером IPH и/или функцией, могут служить для ограничения доступной полезной площади Si. Кроме того, ограничения стоимости, связанные с изготовлением данной IPH, могут ограничивать величину полезной площади Si, доступной для ее регистра и соответствующего банка EPROM. Ограничения полезной площади Si IPH преобразуются в ограничения регистра IPH и банка EPROM, которые, соответственно, преобразуются в ограничения адресуемых единиц памяти.

[0011] Примеры данного раскрытия сущности изобретения включают в себя запоминающее устройство печатающей головки, использующее схему трехмерной адресации для EPROM, вместе с системой, и способ для трехмерной адресации для единицы памяти EPROM. Запоминающее устройство печатающей головки, системы и способы могут использовать некоторое количество сдвиговых регистров, каждый из которых соединен с некоторым количеством банков EPROM, для генерации трехмерного адреса EPROM. Трехмерный адрес EPROM может включать в себя информационный сигнал выбора строки, информационный сигнал выбора столбца и информационный сигнал выбора банка. Информационный сигнал выбора строки может задавать строчный участок отдельного адреса единицы памяти EPROM, информационный сигнал выбора столбца может задавать столбцовый участок отдельного адреса EPROM, и сигнал выбора банка может задавать банк EPROM из некоторого количества банков EPROM, связанный с отдельным адресом единицы памяти EPROM, заданным первым и вторым сдвиговыми регистрами. В результате, примеры данного раскрытия сущности изобретения, использующие трехмерный адрес EPROM, в отличие от общепринятых способов, могут адресовать единицы памяти EPROM в большем количестве банков EPROM, при использовании меньшей полезной площади Si (например, меньшего количества сдвиговых регистров, поскольку каждый банк EPROM не требует соответствующего сдвигового регистра для его адресации).

[0012] Фиг. 1 показывает пример запоминающего устройства 110 печатающей головки, согласно данному раскрытию. Запоминающее устройство 110 печатающей головки может быть интегрировано в любую конструкцию IPH. Например, запоминающее устройство 110 печатающей головки может быть частью струйной IPH, имеющей печатающую головку, интегрированную в чернильный картридж. IPH, связанная с запоминающим устройством 110 печатающей головки, может включать в себя, например, корпус, чернильную камеру, некоторое количество входных и выходных каналов, связанных по текучей среде с чернильной камерой, некоторое количество запускающих резисторов, различные электрические контакты и контроллер. Контроллер может включать в себя запоминающее устройство 110 печатающей головки.

[0013] Запоминающее устройство 110 печатающей головки может включать в себя некоторое количество сдвиговых регистров 112-1, …, 112-N. Хотя на фиг. 1 показаны три сдвиговых регистра 112-1, …, 112-N, данное изобретение этим не ограничено. Например, количество сдвиговых регистров 112-1, …, 112-N может быть любым количеством сдвиговых регистров в пределах ограничений доступной полезной площади Si.

[0014] В некоторых примерах, каждый из данного количества сдвиговых регистров 112-1, …, 112-N может включать в себя каскад триггерных схем с двумя стабильными состояниями, совместно использующих общий тактовый генератор. Каждая триггерная схема может быть соединена с информационным входом следующего триггера в каскаде, что обеспечивает в результате схему, которая сдвигает запомненный битовый массив, посредством сдвига в данных, принимаемых на ее входе, и сдвига на дополнительный регистр последнего бита в этом массиве при каждой передаче тактового входного сигнала. Каждая триггерная схема сдвигового регистра может быть названа ступенью. Данное количество сдвиговых регистров 112-1, …, 112-N может включать в себя любое количество ступеней. Например, сдвиговые регистры могут включать в себя восемь ступеней, как показано на фиг. 1.

[0015] Сдвиговые регистры 112-1, …, 112-N могут быть любым типом сдвигового регистра. Например, каждый из данного количества сдвиговых регистров 112-1, …, 112-N может быть сдвиговым регистром с последовательным входом и параллельным выходом.

[0016] Сдвиговые регистры 112-1, …, 112-N могут принять некоторое количество входных сигналов (например, сигналов S1-1, …, S4-N выбора, информационных сигналов D1, …, D-N, и т.д.) через любое количество входных линий. Сигналы S1-1, …, S4-N выбора могут быть использованы для предварительной зарядки и продвижения сдвигового регистра 112-1, …, 112-N, принимающего сигналы S1-1, …, S4-N выбора. Например, сдвиговый регистр 112-1 может быть продвинут посредством многократной посылки импульсов сигналов S1-1, …, S4-1 выбора, причем каждый цикл из четырех сигналов S1-1, …, S4-1 выбора обеспечивает продвижение сдвигового регистра 112-1 на одну ступень. Сигналы S1-1, …, S4-N выбора могут быть независимыми сигналами или общим сигналом. Например, сигналы S1-1, …, S4-N выбора могут быть общим сигналом вместо отдельных сигналов. То же самое относится к сигналам S2-1, S2-2, S2-N выбора, сигналам S3-1, S2-2, S3-N выбора и сигналам S4-1, S4-2, S4-N выбора.

[0017] Информационные сигналы D1, …, D-N могут служить в качестве инициирующих сигналов и могут передавать адрес строки и столбца единицы памяти EPROM. Данные, введенные посредством сигналов D1, …, D-N, могут быть произвольно назначены для любых сдвиговых регистров 112-1, …, 112-N таким образом, чтобы конкретный сдвиговый регистр 112-1, …, 112-N не был ограничен приемом конкретного типа входных данных.

[0018] Каждый из некоторого количества сдвиговых регистров 112-1, …, 112-N может быть соединен с некоторым количеством банков 114-1, …, 114-N памяти. Возможно любое количество банков 114-1, …, 114-N памяти. Однако количество банков 114-1, …, 114-N памяти запоминающего устройства 110 печатающей головки может быть ограничено количеством сдвиговых регистров 112-1, …, 112-N и количеством ступеней и циклов каждого из сдвиговых регистров 112-1, …, 112-N, поскольку адресация некоторого количества банков 114-1, …, 114-N памяти включает в себя наличие достаточного количества сдвиговых регистров/ ступеней сдвиговых регистров/ циклов сдвиговых регистров для различения единиц памяти данного количества банков 114-1, …, 114-N памяти.

[0019] Каждый банк 114-1, …, 114-N памяти может быть массивом адресуемых единиц памяти EPROM (например, битов, и т.д.). Банк 114-1, …, 114-N памяти может быть массивом EPROM любого размера с любым количеством отдельных адресов единиц памяти EPROM. Например, банк 114-1, …, 114-N памяти логически может быть массивом EPROM из восьми строк и восьми столбцов, образующим шестьдесят четыре отдельные адресуемые единицы памяти EPROM. Логическая структура и количество адресуемых битов могут быть ограничены количеством ступеней и циклов каждого из сдвиговых регистров 112-1, …, 112-N, поскольку адресация некоторого количества отдельных адресуемых единиц памяти EPROM включает в себя наличие достаточного количества ступеней сдвиговых регистров/ циклов сдвиговых регистров для их различения.

[0020] Каждый сдвиговый регистр 112-1, …, 112-N может генерировать некоторое количество выходных сигналов (например, сигнал 118 выбора строки (RS), сигнал 120 выбора столбца (CS), сигнал 122 выбора банка (BS)). Хотя фиг. 1 показывает, что сигналы RS 118, CS 120 и BS 122 генерируются из отдельных сдвиговых регистров 112-1, …, 112-N, данное раскрытие сущности изобретения этим не ограничено. Более одного сигнала может быть сгенерировано из отдельного сдвигового регистра из данного количества сдвиговых регистров 112-1, …, 112-N. Например, если бы каждый из банков 114-1, …, 114-N памяти включал в себя массив EPROM, логически содержащий восемь строк и восемь столбцов, образующих шестьдесят четыре отдельные адресуемые единицы памяти EPROM, и каждый сдвиговый регистр 112-1, …, 112-N был 16-ступенчатым сдвиговым регистром 112-1, …, 112-N, то тогда конкретный сдвиговый регистр (например, сдвиговый регистр 12-1) мог бы сгенерировать как сигнал RS 118, так и сигнал CS 120, достаточные для адресации строки и столбца адресуемой единицы памяти EPROM любых массивов, при образовании пары с сигналом BS 122. Соотношение между количеством ступеней сдвигового регистра 112-1, …, 112-N и количеством отдельно адресуемых единиц памяти EPROM может определить, сколько сигналов может сгенерировать конкретный сдвиговый регистр (например, сдвиговый регистр 112-1). Если конкретный сдвиговый регистр (например, сдвиговый регистр 112-1) включает в себя достаточно ступеней для адресации как столбцового, так и строчного участка адреса единицы памяти EPROM из любых массивов EPROM из данного количества банков 114-1, …, 114-N памяти, при образовании пары с сигналом BS 122, то тогда этот конкретный сдвиговый регистр (например, сдвиговый регистр 112-1) может сгенерировать как сигнал RS 118, так и сигнал CS 120.

[0021] Информационный сигнал D1 может быть использован для генерации RS-сигнала 118. RS-сигнал 118 может идентифицировать логический строчный участок адреса отдельно адресуемой единицы памяти EPROM в пределах любого из массивов EPROM банков 114-1, …, 114-N памяти. RS-сигнал 118 может быть сгенерирован посредством подачи информационного сигнала D1 во время конкретного цикла конкретного сигнала S1-1, …, S4-N выбора.

[0022] Информационный сигнал D2 может быть использован для генерации CS-сигнала 120. CS-сигнал 120 может идентифицировать логический столбцовый участок адреса отдельно адресуемой единицы памяти EPROM в пределах любого из массивов EPROM банков 114-1, …, 114-N памяти. CS-сигнал 120 может быть сгенерирован посредством подачи информационного сигнала D2 во время конкретного цикла конкретного сигнала S1-1, …, S4-N выбора в конкретном сдвиговом регистре 112-2.

[0023] Информационный сигнал D-N может быть использован для генерации BS-сигнала 122. BS-сигнал 122 может идентифицировать конкретный банк памяти из данного количества банков 114-1, …, 114-N памяти, в пределах которого логически или физически находится отдельно адресуемая единица памяти EPROM. Когда BS-сигнал 122 образует пару с RS-сигналом 118 и CS-сигналом 120, задается трехмерный адрес единицы памяти EPROM. А именно, RS-сигнал 118 и CS-сигнал 120 представляют двумерный адрес EPROM, задающий логическую строку (например, RS-сигнал 118) и логический столбец (например, CS 120), которые применимы при адресации единицы памяти EPROM в любом из банков 114-1, …, 114-N памяти. BS-сигнал 122 вводит третье измерение адреса EPROM, который задает, какому банку 114-1, …, 114-N памяти адресованы RS-сигнал 118 и CS-сигнал 120. В ряде вариантов осуществления, BS-сигнал 122 может задавать единственный банк памяти из некоторого количества банков 114-1, …, 114-N памяти.

[0024] Альтернативно, BS-сигнал 122 может задавать более одного банка из данного количества банков 114-1, …, 114-N памяти, что обеспечивает возможность параллельной трехмерной адресации EPROM. Например, D-N может быть подан во время многочисленных циклов сигнала S1-1, …, S4-N выбора, для параллельной адресации заданных строки и столбца более одного банка из данного количества банков 114-1, …, 114-N памяти.

[0025] RS-сигнал 118, CS-сигнал 120 и BS-сигнал 122 может быть введен посредством соответствующего транзистора. Например, RS-сигнал 118 может быть введен посредством RS-транзистора, CS-сигнал 120 может быть введен посредством CS-транзистора, и BS-сигнал 122 может быть введен посредством BS-транзистора. RS, CS, и BS транзисторы могут быть NMOS-транзисторами. RS, CS, и BS транзисторы могут быть выполнены любым способом, который обеспечивает возможность генерации трехмерного адреса EPROM. Например, BS-транзистор может быть соединен с CS-транзистором и RS-транзистором каскадным/последовательным способом. В другом примере, BS-транзистор может быть соединен с затвором CS-транзистора и RS-транзистора. В еще одном примере, BS-транзистор может быть соединен с CS-транзистором и RS-транзистором через дополнительный декодер.

[0026] Иллюстративное запоминающее устройство 110 печатающей головки (фиг. 1) демонстрирует схему трехмерной адресации памяти, которая обеспечивает меньшее количество сдвиговых регистров 112-1, …, 112-N с меньшим количеством циклов адресации, для адресации гораздо большего количества адресуемых единиц памяти EPROM, чем в общепринятых способах. Например, при использовании общепринятого способа прямой адресации с четырьмя 16-ступенчатыми сдвиговыми регистрами, только четыре соответствующих банка памяти из массивов памяти из 8*8 единиц памяти EPROM могут быть адресованы. А именно, общепринятый способ прямой адресации нуждается в четырех 16-ступенчатых сдвиговых регистрах для адресации 256 единиц памяти. При сопоставлении с общепринятым способом, некоторые примеры данного раскрытия сущности изобретения могут обеспечить генерацию 8-ступенчатыми сдвиговыми регистрами 112-1, …, 112-N трехмерных адресов единиц памяти EPROM для восьми банков 114-1, …, 114-N памяти из массивов памяти EPROM из 8*8 единиц памяти. А именно, примеры данного раскрытия сущности изобретения обеспечивают возможность адресации тремя 8-ступенчатыми сдвиговыми регистрами 112-1, …, 112-N 512 единиц памяти. Данное раскрытие сущности изобретения может обеспечить меньшее количество сдвиговых регистров и/или меньшие сдвиговые регистры. В вышеупомянутом примере имеется три сдвиговых регистра вместо четырех, и эти три сдвиговых регистра являются 8-ступенчатыми, а не 16-ступенчатыми, что обеспечивает экономию пространства как в отношении количества, так и размера сдвиговых регистров.

[0027] Фиг. 2А и фиг 2В являются схемами примеров схемы трехмерной адресации для EPROM. Фиг. 2А показывает таблицу 230, демонстрирующую пример схемы трехмерной адресации для EPROM данного раскрытия сущности изобретения. Таблица 230 состоит из некоторого количества строк и столбцов, соответствующих сигналам и тактированию их подачи, соответственно. В таблице 230 подача сигнала показана появлением «1» вместо «0» в матрице таблицы 230.

[0028] Строки S1, S2, S3 и S4 таблицы 230 представляют сигналы S1, S2, S3 и S4 выбора, которые могут быть поданы на каждый сдвиговый регистр для предварительной зарядки и продвижения каждого сдвигового регистра. В таблице 230 сигналы S1, S2, S3 и S4 выбора необязательно являются сигналами выбора одного сдвигового регистра. А именно, сигналы S1, S2, S3 и S4 выбора могут обозначать любые сигналы выбора, подаваемые на любой из сдвиговых регистров, которые принимают информационные сигналы. Для дополнительного разъяснения, со ссылкой опять на фиг. 1, S1 таблицы 230 может представлять сигналы S1-1, S1-2, S1-3 и/или S1-N выбора. Дополнительно, S2, S3 и S4 таблицы 230 могут представлять S2-1, S2-2, S2-3 и/или S2-N; S3-1, S3-2, S3-3, и/или S3-N; и S4-1, S4-2, S4-3 и/или S4-N, соответственно. Таким образом, таблица 230 может иллюстрировать похожие сигналы S1, S2, S3 и S4 выбора, подаваемые для предварительной зарядки и продвижения некоторого количества отдельных сдвиговых регистров.

[0029] Каждый столбец таблицы 230 представляет цикл сдвигового регистра (например, цикл 1, цикл 2, цикл 3, цикл 4, цикл 5, цикл 6, цикл 7, цикл 8), причем цикл 1 является первым циклом для сдвига на нижний регистр. Поскольку цикл может соответствовать подаче сигналов S1-S4 выбора, каждый цикл таблицы 230 соответствует четырем подачам сигналов S1, S2, S3 и S4 выбора. Таким образом, каждый цикл соответствует восьми похожим образом пронумерованным столбцам цикла, на протяжении которых подаются сигналы выбора строк S1, S2, S3 и S4.

[0030] Таблица 230 дополнительно показывает информационные сигналы строк D1 (RS), D2 (CS) и D3 (BS). Информационный сигнал строки D1 (RS) может соответствовать информационному сигналу D1, задающему строку трехмерного адреса для EPROM, информационный сигнал строки D2 (CS) может соответствовать информационному сигналу D2, задающему столбец трехмерного адреса для EPROM, и информационный сигнал строки D3 (BS) может соответствовать информационному сигналу D3, соответствующему банку трехмерного адреса для EPROM. Как описано выше, информационный сигнал D1, информационный сигнал D2, и информационный сигнал D3, показанные в строках D1 (RS), D2 (CS) и D3 (BS), могут быть информационными сигналами, подаваемыми в отдельных сдвиговых регистрах.

[0031] Таким образом, таблица 230 показывает тактирование подачи вышеупомянутых сигналов для определения трехмерного адреса для EPROM (например, RS2, CS3, BS1 в качестве выходных сигналов в адресной строке таблицы 230). Например, таблица 230 показывает, что информационный сигнал D1 может быть подан во время седьмого цикла сигнала выбора, соответствующего S2 8-ступенчатого сдвигового регистра. При подаче в этот момент, D1 генерирует сигнал 232 выбора строки (RS), означающий выбор строки 2 (RS2). В таблице 230 дополнительно показано, что информационный сигнал D2 может быть подан во время шестого цикла сигнала S2 выбора сдвигового регистра, для генерации сигнала 234 выбора столбца (CS), означающего выбор столбца 3 (CS3). Таблица 230 также показывает, что информационный сигнал D3 может быть подан во время восьмого цикла сигнала S2 выбора сдвигового регистра, для генерации сигнала 236 выбора банка (BS), означающего выбор банка 1 (BS1). При объединении, сигналы RS, CS и BS задают трехмерный адрес для единицы памяти EPROM. В примере фиг. 2А, трехмерным адресом являются RS2, CS3, BS1, адресующие единицу памяти второй строки, третьего столбца первого банка памяти EPROM.

[0032] Фиг. 2В показывает таблицу 240, демонстрирующую пример схемы трехмерной параллельной адресации для EPROM данного раскрытия сущности изобретения. Таблица 240 состоит из некоторого количества строк и столбцов, соответствующих сигналам и тактированиям их подачи, соответственно. Как и в случае таблицы 230, подача сигнала показана появлением «1» вместо «0» в матрице таблицы 240. Строки и столбцы таблицы 240 демонстрируют те же основные принципы таблицы 230, за исключением принципов, реализованных в схеме параллельной адресации. Схема параллельной адресации таблицы 240 может быть обеспечена посредством дополнительной подачи информационного сигнала D3. При подаче информационного сигнала D3 в дополнительное время, RS-сигнал 242 и CS-сигнал 244 могут быть поданы параллельно на два банка EPROM, заданные двумя BS-сигналами 246-1 и 246-2.

[0033] Например, таблица 240 показывает тактирование подачи вышеупомянутых сигналов для определения параллельных трехмерных адресов для EPROM (например, RS2, CS3, BS1 и RS2, CS3, BS2 в качестве выходных данных в адресной строке таблицы 240). Например, таблица 240 показывает, что информационный сигнал D1 может быть подан во время седьмого цикла сигнала выбора, соответствующего S2 8-ступенчатого сдвигового регистра. При подаче в этот момент, D1 генерирует сигнал 242 выбора строки (RS), означающий выбор строки 2 (RS2). В таблице 240 дополнительно показано, что информационный сигнал D2 может быть подан во время шестого цикла сигнала S2 выбора сдвигового регистра, для генерации сигнала 244 выбора столбца (CS), означающего выбор столбца 3 (CS3). Таблица 240 также показывает, что информационный сигнал D3 может быть обеспечен как во время седьмого цикла, так и во время восьмого цикла сигнала S2 выбора сдвигового регистра 240, для генерации двух BS сигналов 246-1 и 246-2, означающих выбор банка 1 (BS1) и выбор банка 2 (BS2), соответственно. При объединении, сигналы RS, CS и BS задают параллельные трехмерные адреса единиц памяти для EPROM. В примере фиг. 2В, трехмерными адресами являются RS2, CS3, BS1 и RS2, CS3, BS2. RS2, CS3, BS1 адресует единицу памяти второй строки, третьего столбца первого банка памяти EPROM. RS2, CS3, BS2 адресует единицу памяти второй строки, третьего столбца второго банка памяти EPROM. Схема трехмерной параллельной адресации для EPROM, показанная в таблице 240, является схемой межбанкового параллельного считывания. А именно, схема трехмерной параллельной адресации для EPROM, показанная в таблице 240, одновременно адресует строку и столбец среди отдельных банков памяти EPROM. Другой альтернативой (не показана) является схема внутрибанковой параллельной адресации. В схеме внутрибанковой параллельной адресации, сигнал D1 и/или D2 может быть подан много раз для генерации множества сигналов RS и/или CS. Таким образом, схема внутрибанковой параллельной адресации может одновременно адресовать многочисленные строки и/или столбцы одного и того же банка памяти EPROM.

[0034] Примеры данного раскрытия сущности изобретения могут включать в себя системы для трехмерной адресации для EPROM на печатающем устройстве. Такая система может включать в себя некоторое количество банков EPROM. Банки EPROM могут быть расположены на печатающем устройстве. Например, они могут быть расположены на интегрированной печатающей головке. Каждый из этих банков EPROM может быть массивом памяти EPROM. Массив памяти EPROM может быть массивом единиц памяти EPROM, организованных в строки и столбцы.

[0035] Система может включать в себя некоторое количество сдвиговых регистров. Эти сдвиговые регистры могут быть сдвиговыми регистрами с последовательным входом и параллельным выходом. А именно, строка данных может быть последовательно введена в сдвиговый регистр и может быть выведена в параллельном формате к многочисленным выходам. Например, последовательно введенные данные, принятые через единственный физический вход (например, провод), могут быть выведены через многочисленные физические выходы (например, провода), для одновременной адресации многочисленных банков EPROM, с которыми сдвиговые регистры соединены.

[0036] Каждый из сдвиговых регистров системы может быть синхронизирован с соответствующими им сигналами выбора. А именно, сигналы выбора, которые вводятся в сдвиговый регистр для предварительной зарядки сдвигового регистра и продвижения сдвигового регистра, могут содержать тактовый импульс, определяющий, когда происходит каждый сдвиг сдвигового регистра. Например, могут существовать четыре повторяющихся сигнала выбора (например, S1, S2, S3 и S4), служащие в качестве тактовых импульсов. Набор из четырех сигналов выбора может быть одним тактовым циклом для сдвигового регистра. В примерах данного раскрытия сущности изобретения, сдвиговый регистр может использовать тактовые циклы при сдвиге данных для генерации сигналов RS, CS и BS. Количество тактовых циклов, связанных с сдвиговым регистром, может определять количество банков памяти EPROM и количество единиц памяти EPROM каждого банка EPROM. Например, количество банков памяти EPROM может быть равным количеству тактовых циклов, связанных со сдвиговым регистром, генерирующим BS-сигнал, поскольку каждый тактовый цикл может соответствовать одному банку из данного количества банков EPROM. Дополнительно, количество строк и количество столбцов единиц памяти EPROM в каждом массиве памяти EPROM может быть равным количеству тактовых циклов, связанных со сдвиговым регистром, задающим CS-сигнал и/или RS-сигнал, поскольку каждый тактовый цикл может соответствовать одному из обозначений строки и/или столбца массива памяти EPROM.

[0038] Система может включать в себя информационный сигнал выбора строки, для задания строчного участка трехмерного адреса для EPROM. Например, информационный сигнал выбора строки может включать в себя указание на строку единицы памяти EPROM в пределах массива памяти EPROM, адресуемую посредством трехмерного адреса для EPROM. Информационный сигнал выбора строки может соответствовать первому сдвиговому регистру из данного количества сдвиговых регистров. Например, сигнал выбора строки может быть введен в первый сдвиговый регистр в виде информационного сигнала и может задавать строчный участок трехмерного адреса для EPROM на основе того, когда этот информационный сигнал подан относительно некоторого количества сигналов выбора.

[0039] Система может также включать в себя информационный сигнал выбора столбца, для задания столбцового участка трехмерного адреса для EPROM. Например, информационный сигнал выбора столбца может включать в себя указание на столбец единицы памяти EPROM в пределах массива памяти EPROM, адресуемой посредством трехмерного адреса для EPROM. Информационный сигнал выбора столбца может соответствовать второму сдвиговому регистру из данного количества сдвиговых регистров. Например, сигнал выбора столбца может быть введен во второй сдвиговый регистр в виде информационного сигнала и может задавать столбцовый участок трехмерного адреса для EPROM на основе того, когда информационный сигнал подан относительно некоторого количества сигналов выбора.

[0040] Информационный сигнал выбора банка, задающий EPROM-банковый участок трехмерного адреса для EPROM, может быть включен в систему. Например, информационный сигнал выбора банка может включать в себя указание на банк EPROM из данного количества банков EPROM, которому адресованы столбец сигнала выбора столбца и строка сигнала выбора строки. Информационный сигнал выбора банка может соответствовать третьему сдвиговому регистру из данного количества сдвиговых регистров. Например, сигнал выбора банка может быть введен в третий сдвиговый регистр в виде информационного сигнала и может задавать строчный участок трехмерного адреса для EPROM на основе того, когда этот информационный сигнал подан относительно некоторого количества сигналов выбора.

[0041] Фиг. 3 показывает блок-схему последовательности операций примера способа 370 для трехмерной адресации единицы памяти EPROM интегрированной печатающей головки. На этапе 372, способ 370 может включать в себя прием некоторого количества входных сигналов некоторым количеством сдвиговых регистров, причем данное количество входных сигналов включает в себя сигнал выбора для предварительной зарядки и продвижения сдвигового регистра из данного количества сдвиговых регистров, и информационный сигнал. Каждый из сдвиговых регистров может быть соединен с каждым банком EPROM из некоторого количества банков EPROM. Например, каждый сдвиговый регистр может осуществлять обмен данными с каждым банком EPROM из данного количества банков EPROM таким образом, чтобы он мог передавать и/или принимать данные от каждого из банков памяти EPROM.

[0042] На этапе 374, способ 370 может включать в себя генерацию информационного сигнала выбора строки на первом сдвиговом регистре из данного количества сдвиговых регистров, задающего строчный участок трехмерного адреса EPROM.

[0043] На этапе 376, способ 370 может включать в себя генерацию информационного сигнала выбора столбца на втором сдвиговом регистре из данного количества сдвиговых регистров, задающего столбцовый участок трехмерного адреса EPROM.

[0044] На этапе 378, способ 370 может включать в себя генерацию сигнала выбора банка, на сдвиговом регистре из данного количества сдвиговых регистров, задающего банк EPROM, из некоторого количества банков EPROM, связанного с информационным сигналом выбора строки и информационным сигналом выбора столбца.

[0045] На этапе 380, способ 370 может включать в себя адресацию отдельной единицы памяти EPROM в трех измерениях, на основе информационного сигнала выбора строки, информационного сигнала выбора столбца и сигнала выбора банка. Трехмерный адрес единицы памяти EPROM может быть сгенерирован в пределах восьми циклов данного количества сдвиговых регистров. Например, данное количество сдвиговых регистров может сгенерировать сигнал выбора строки, сигнал выбора столбца и сигнал выбора банка, в пределах восьми циклов сдвигового регистра, принимающего информационный сигнал.

[0046] В подробном описании данного раскрытия сущности изобретения сделана ссылка на сопутствующие чертежи, которые образуют его часть и в которых показаны, в качестве иллюстрации, как могут быть осуществлены на практике примеры данного раскрытия. Эти примеры описаны достаточно подробно для обеспечения того, чтобы специалисты в данной области техники могли осуществить на практике примеры данного раскрытия, и следует понимать, что могут быть использованы другие примеры, и могут быть выполнены процессные, электрические и/или конструктивные изменения, не выходя за рамки объема данного раскрытия.

[0047] Дополнительно, пропорции и относительный масштаб элементов, обеспеченных на чертежах, предназначены для иллюстрации примеров данного раскрытия сущности изобретения и не должны иметь ограничивающего смысла. При использовании здесь, обозначения «N», конкретно, в отношении ссылочных позиций в чертежах, указывают на то, что некоторое количество конкретных признаков, обозначенных таким образом, может быть включено в некоторое количество примеров данного раскрытия сущности изобретения. При использовании здесь, «один» или «некоторое количество» иногда могут относиться к одному или нескольким таким элементам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ организации поиска документов в прикладных базах неструктурированных данных и аппаратная версия двойной памяти для его осуществления | 2022 |

|

RU2792584C1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| ВХОДНЫЕ УПРАВЛЯЮЩИЕ СИГНАЛЫ, ПРОХОДЯЩИЕ ПО СИГНАЛЬНЫМ ПУТЯМ | 2016 |

|

RU2710691C1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| ДОСТУП К БЛОКАМ ПАМЯТИ В БАНКЕ ПАМЯТИ | 2017 |

|

RU2748727C2 |

| ВЫСОКОПАРАЛЛЕЛЬНЫЙ СПЕЦПРОЦЕССОР ДЛЯ РЕШЕНИЯ ЗАДАЧ О ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 1993 |

|

RU2074415C1 |

| ПАНЕЛЬ ЖИДКОКРИСТАЛЛИЧЕСКОГО ДИСПЛЕЯ (ПЖКД) И СПОСОБ ЕЕ УПРАВЛЕНИЯ | 1993 |

|

RU2122242C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

Изобретение относится к средствам памяти, интегрированным в печатные головки. Технический результат заключается в расширении арсенала средств того же назначения. Трехмерная адресация для стираемого программируемого постоянного запоминающего устройства (erasable programmable read only memory - EPROM) может включать в себя некоторое количество банков EPROM, некоторое количество сдвиговых регистров, информационный сигнал выбора строки, информационный сигнал выбора столбца и информационный сигнал выбора банка. 3 н. и 12 з.п. ф-лы, 4 ил.

1. Запоминающее устройство печатающей головки, содержащее

некоторое количество банков стираемого программируемого постоянного запоминающего устройства (erasable programmable read only memory - EPROM), причем каждый из них содержит массив памяти EPROM на интегрированной печатающей головке; и

некоторое количество сдвиговых регистров, причем каждый из них соединен с данным количеством банков EPROM, для генерации трехмерного адреса EPROM, содержащего:

информационный сигнал выбора строки, задающий строчный участок трехмерного адреса EPROM,

информационный сигнал выбора столбца, задающий столбцовый участок трехмерного адреса EPROM, и

информационный сигнал выбора банка, задающий банк EPROM из данного количества банков EPROM, связанный с информационным сигналом выбора строки и информационным сигналом выбора столбца.

2. Устройство по п. 1, в котором информационный сигнал выбора банка задает более одного банка из данного количества банков EPROM, связанного с данными выбора строки и данными выбора столбца, для генерации параллельного трехмерного адреса EPROM.

3. Устройство по п. 1, в котором информационный сигнал выбора строки сгенерирован первым сдвиговым регистром из данного количества сдвиговых регистров, информационный сигнал выбора столбца сгенерирован первым сдвиговым регистром из некоторого количества сдвиговых регистров, и информационный сигнал выбора банка сгенерирован вторым сдвиговым регистром из данного количества сдвиговых регистров.

4. Устройство по п. 1, в котором информационный сигнал выбора строки сгенерирован первым сдвиговым регистром из данного количества сдвиговых регистров, информационный сигнал выбора столбца сгенерирован вторым сдвиговым регистром из некоторого количества сдвиговых регистров, и информационный сигнал выбора банка сгенерирован третьим сдвиговым регистром из данного количества сдвиговых регистров.

5. Устройство по п. 4, в котором каждый из данного количества сдвиговых регистров принимает некоторое количество входных сигналов, включающих в себя соответствующий информационный сигнал и некоторое количество соответствующих сигналов выбора.

6. Устройство по п. 5, в котором соответствующий информационный сигнал инициирует соответствующий сдвиговый регистр и задает строчный участок и столбцовый участок трехмерного адреса EPROM.

7. Устройство по п. 5, в котором соответствующие сигналы выбора предварительно заряжают и продвигают соответствующий сдвиговый регистр.

8. Устройство по п. 7, в котором соответствующий сдвиговый регистр продвигается на одну ступень после циклического прохождения четырех соответствующих сигналов выбора.

9. Система для трехмерной адресации единицы памяти стираемого программируемого постоянного запоминающего устройства (EPROM) интегрированной печатающей головки, содержащая:

некоторое количество банков стираемого программируемого постоянного запоминающего устройства (EPROM), причем каждый из них содержит массив памяти EPROM на печатающем устройстве;

некоторое количество сдвиговых регистров, имеющих последовательный вход данных и некоторое количество параллельных выходов, причем каждый из данного количества сдвиговых регистров соединен с данным количеством банков EPROM;

информационный сигнал выбора строки, соответствующий первому сдвиговому регистру из данного количества сдвиговых регистров, для задания строчного участка трехмерного адреса EPROM;

информационный сигнал выбора столбца, соответствующий второму сдвиговому регистру из данного количества сдвиговых регистров, для задания столбцового участка трехмерного адреса EPROM; и

информационный сигнал выбора банка, соответствующий третьему сдвиговому регистру из данного количества сдвиговых регистров, для задания банка EPROM, из данного количества банков EPROM, как участка трехмерного адреса EPROM.

10. Система по п. 9, в которой каждый сдвиговый регистр из данного количества сдвиговых регистров синхронизирован с соответствующим набором из четырех повторяющихся сигналов выбора, которые совокупно представляют тактовый цикл из некоторого количества тактовых циклов, связанных с соответствующим сдвиговым регистром.

11. Система по п. 10, в которой количество банков стираемого программируемого постоянного запоминающего устройства (EPROM) определено количеством тактовых циклов, связанных с соответствующим сдвиговым регистром.

12. Система по п. 10, в которой количество строк и количество столбцов единиц памяти массива EPROM каждого банка из данного количества банков EPROM определено количеством тактовых циклов, связанных с соответствующим сдвиговым регистром.

13. Способ для трехмерной адресации единицы памяти стираемого программируемого постоянного запоминающего устройства (EPROM) интегрированной печатающей головки, содержащий этапы, на которых:

принимают некоторое количество входных сигналов на некотором количестве сдвиговых регистров, причем данное количество входных сигналов включает в себя сигнал выбора для предварительной зарядки и продвижения сдвигового регистра из данного количества сдвиговых регистров и информационный сигнал;

генерируют информационный сигнал выбора строки на первом сдвиговом регистре из данного количества сдвиговых регистров, задающий строчный участок трехмерного адреса EPROM;

генерируют информационный сигнал выбора столбца на втором сдвиговом регистре из данного количества сдвиговых регистров, задающий столбцовый участок трехмерного адреса EPROM;

генерируют сигнал выбора банка на сдвиговом регистре из данного количества сдвиговых регистров, задающий банк EPROM, из некоторого количества банков EPROM, связанного с информационным сигналом выбора строки и информационным сигналом выбора столбца; и

адресуют отдельную единицу памяти EPROM в трех измерениях, на основе информационного сигнала выбора строки, информационного сигнала выбора столбца и сигнала выбора банка.

14. Способ по п. 13, в котором каждый сдвиговый регистр из данного количества сдвиговых регистров соединен с каждым банком EPROM из данного количества банков EPROM.

15. Способ по п. 14, причем этот способ включает в себя генерацию одного трехмерного адреса EPROM с использованием восьми циклов для данного количества сдвиговых регистров.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| СИСТЕМА ПЕЧАТИ, КОНТРОЛЛЕР ПЕЧАТИ, ПЕЧАТАЮЩЕЕ УСТРОЙСТВО, СПОСОБ УПРАВЛЕНИЯ ОПЕРАЦИЕЙ ПЕЧАТИ, СПОСОБ ПЕЧАТИ, ЧЕРНИЛЬНЫЙ КАРТРИДЖ, ИСТОЧНИК ЧЕРНИЛ И НОСИТЕЛЬ ЗАПИСИ | 2000 |

|

RU2258010C2 |

| СТРУЙНАЯ ПЕЧАТАЮЩАЯ ГОЛОВКА И СПОСОБ ЕЕ ЭКСПЛУАТАЦИИ | 2001 |

|

RU2285617C2 |

| US 5029020 A, 02.07.1991. | |||

Авторы

Даты

2018-01-10—Публикация

2014-01-31—Подача