Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения в целом касаются области памяти. Конкретные варианты осуществления изобретения включают в себя способы обновления перекрестной памяти.

Уровень техники

Описание уровня техники предназначено в целом для показа общего контекста изобретения. Работа авторов настоящего изобретения в рамках описания в этом разделе, а также аспекты описания, которые иначе могли бы рассматриваться как уровень техники во время регистрации изобретения, ни прямо ни косвенно нельзя рассматривать как уровень техники для настоящего изобретения. Если не сказано обратное, описанные в этом разделе подходы не являются уровнем техники для формулы настоящего изобретения и их наличие в этом разделе не предполагает, что они рассматриваются как уровень техники.

Перекрестная энергонезависимая память, в том числе память (РСМ) на фазовых переходах, может состоять из дву- или трехмерной решетки ячеек памяти. Системы, использующие РСМ, могут строить адрес памяти как объединение нескольких ячеек памяти из одного или более массивов памяти. Состояние ячейки памяти может быть представлено порогом напряжения, который можно обозначить как VT. В некоторых РСМ значение напряжения каждой ячейки может быть установлено равным одному из двух порогов напряжения, которые могут представлять соответственно логические «0» или «1». Значение напряжения ячейки памяти может быть задано при операции записи и считано при операции чтения. В некоторых случаях физические механизмы, стоящие за операциями чтения и записи для заданной ячейки памяти или для заданного адреса памяти, могут приводить к потере или повреждению данных, хранящихся в упомянутых одной или более ячейках, или по упомянутым одному или более адресам памяти.

Краткое описание чертежей

Варианты осуществления изобретения будут лучше ясны из последующего подробного описания изобретения, приведенного со ссылками на приложенные чертежи. Для облегчения этого описания одинаковыми ссылочными позициями обозначены аналогичные структурные элементы. Варианты осуществления изобретения являются только примерами и не ограничены фигурами с приложенных чертежей.

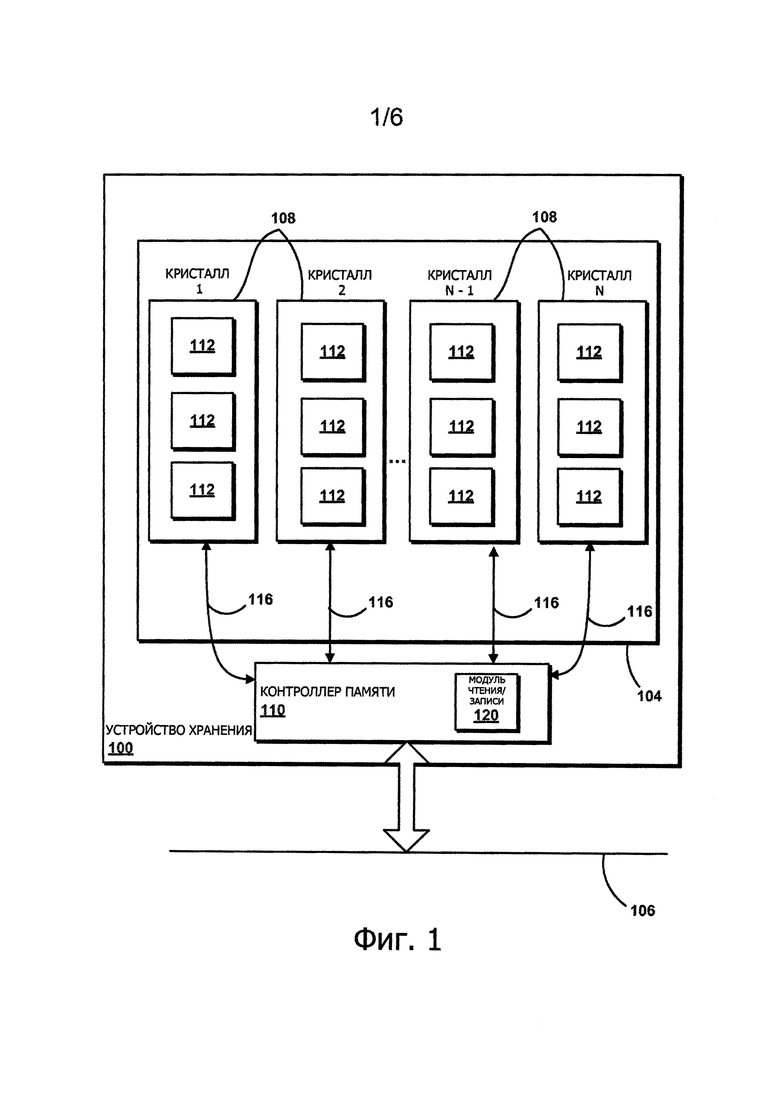

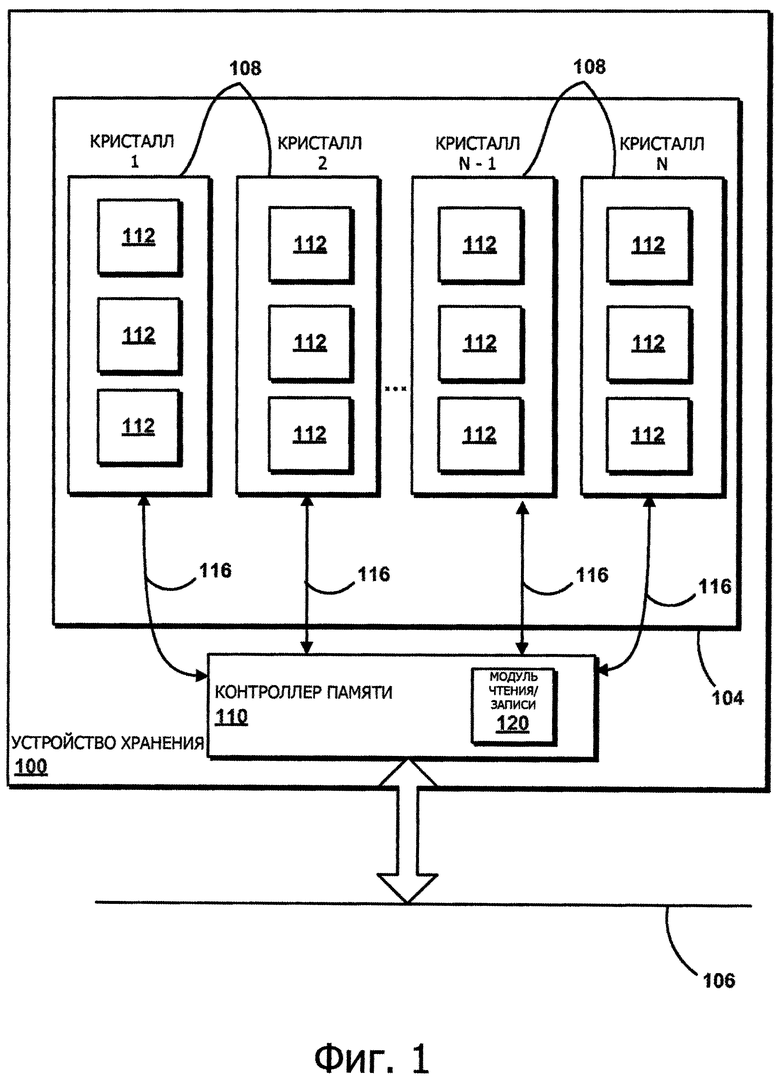

Фиг. 1 - вид, показывающий пример устройства хранения, в котором реализованы принципы настоящего изобретения в соответствии с различными вариантами осуществления изобретения;

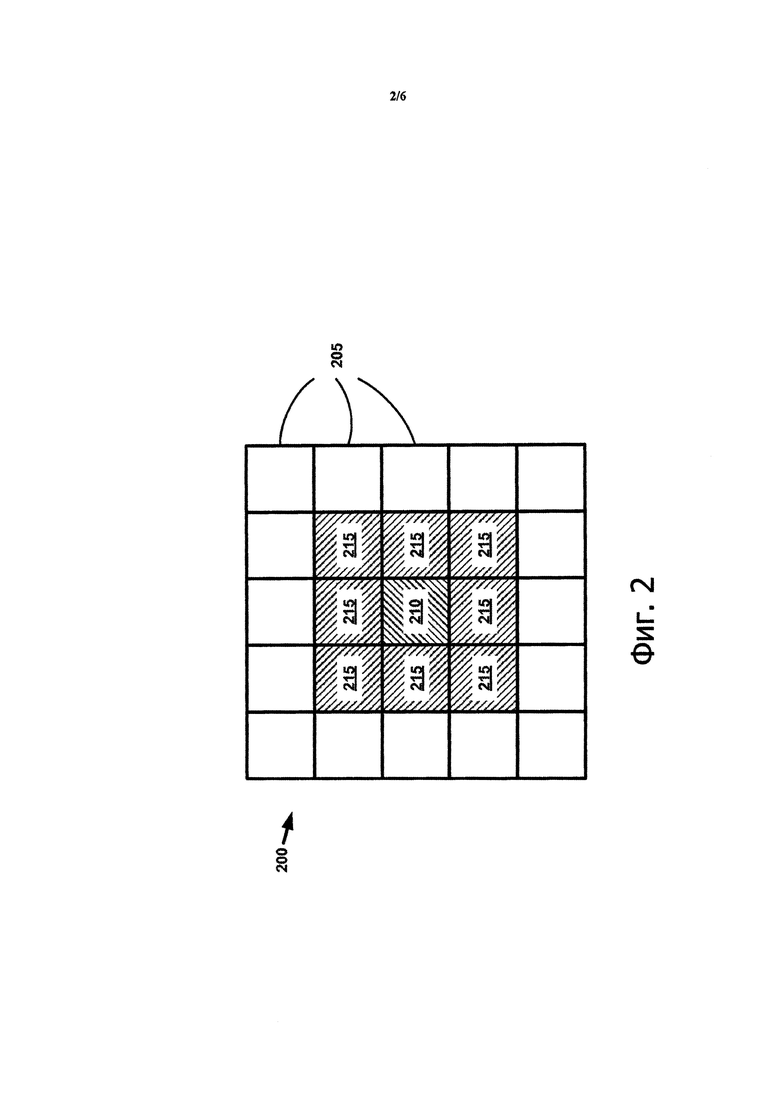

фиг. 2 - вид, показывающий пример ячеек памяти в соответствии с различными вариантами осуществления изобретения;

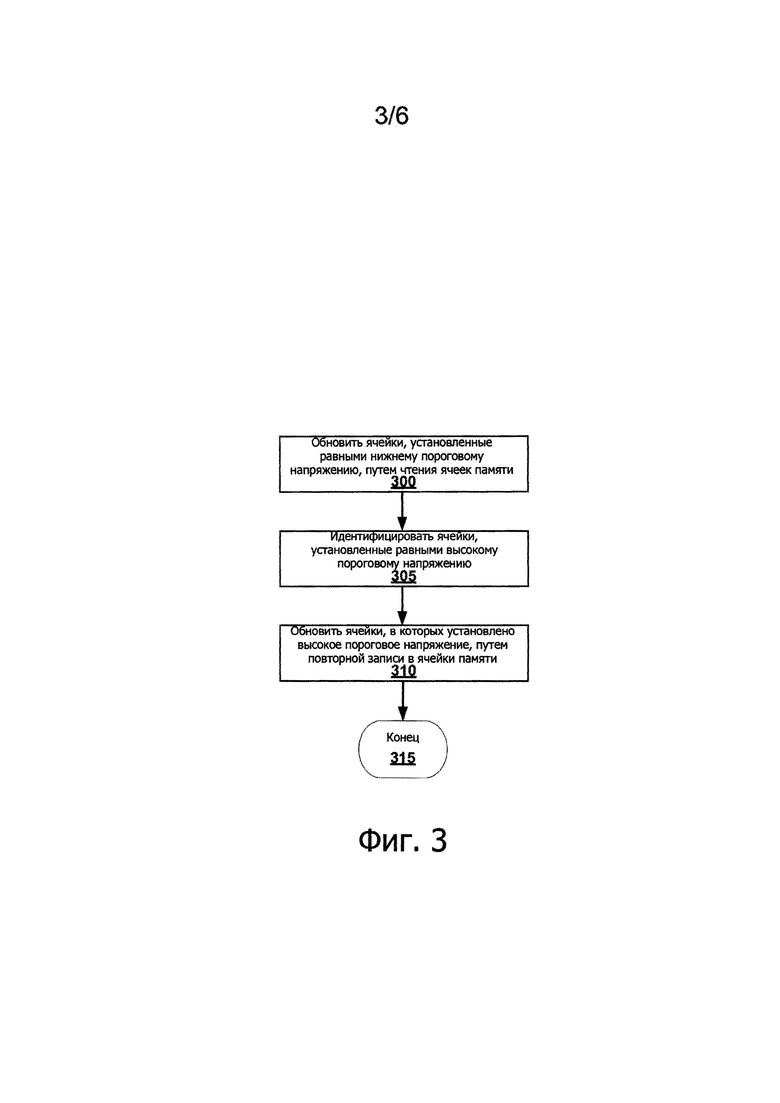

фиг. 3 - вид, показывающий пример процесса обновления ячеек памяти в соответствии с различными вариантами осуществления изобретения;

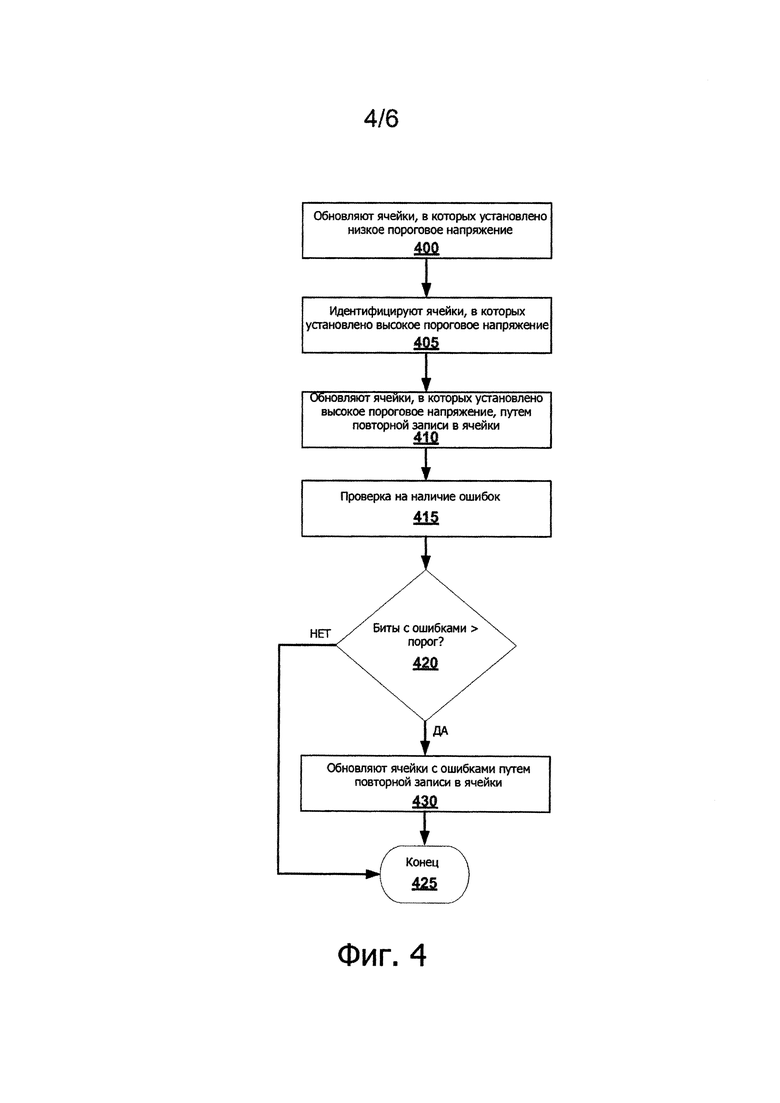

фиг. 4 - вид, показывающий альтернативный процесс обновления ячеек памяти в соответствии с различными вариантами осуществления изобретения;

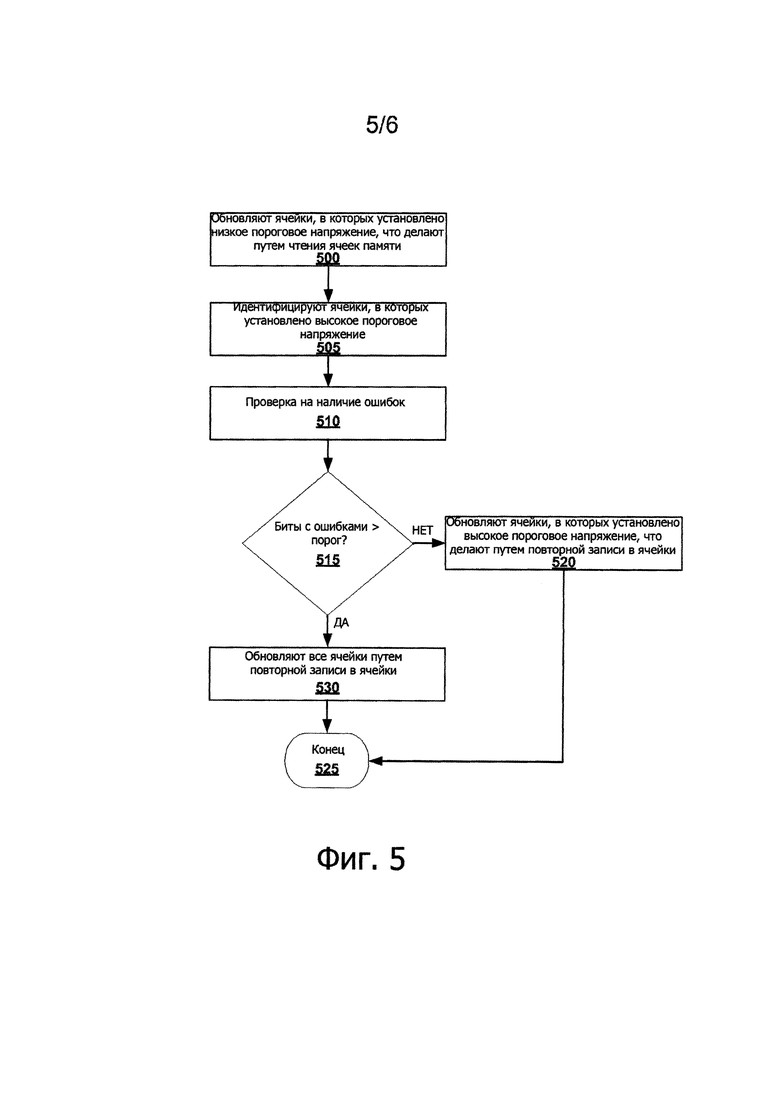

фиг. 5 - вид, показывающий альтернативный процесс обновления ячеек памяти в соответствии с различными вариантами осуществления изобретения;

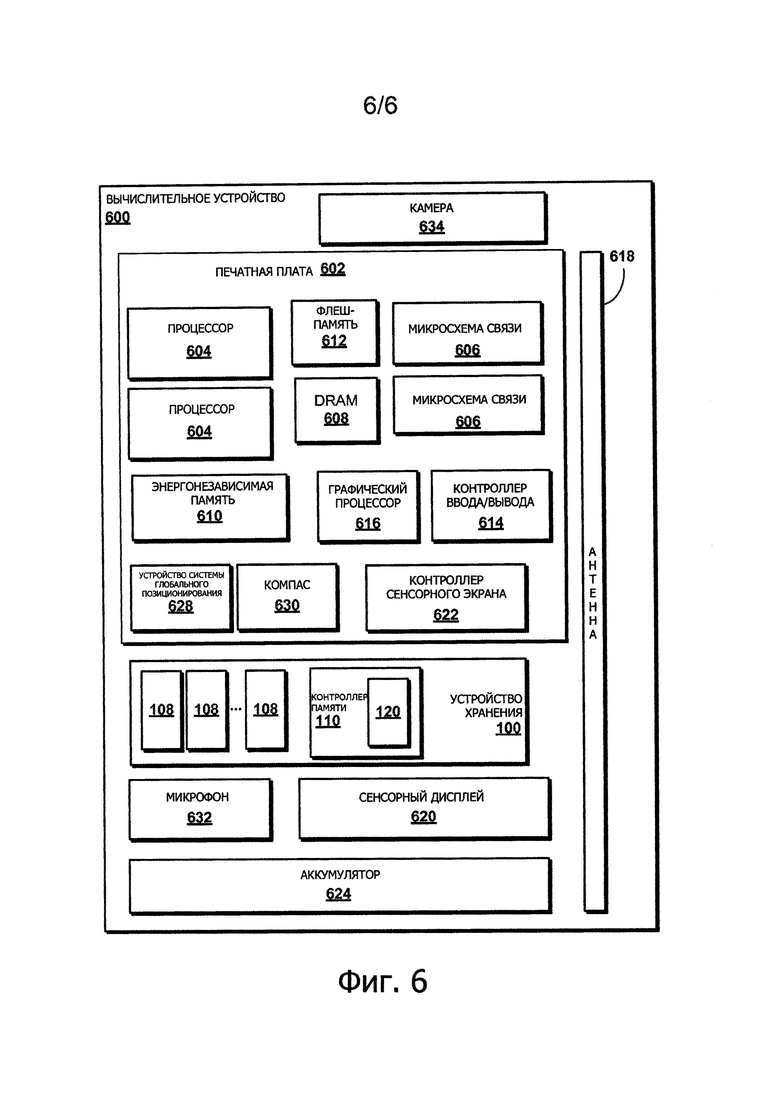

фиг. 6 - вид, показывающий пример системы, выполненной для осуществления описанных здесь способов, в соответствии с различными вариантами осуществления изобретения.

Подробное описание изобретения

В последующем подробном описании содержатся ссылки на приложенные чертежи, которые образуют часть описания, при этом одинаковыми ссылочными позициями обозначены аналогичные элементы, и на которых для примера показаны варианты осуществления изобретения, которые могут быть реализованы. Ясно, что могут быть реализованы другие варианты осуществления изобретения и могут быть выполнены структурные или логические изменения, не выходящие за пределы объема настоящего изобретения. Следовательно, приведенное ниже подробное описание не рассматривается в ограничительном смысле и объем вариантов осуществления изобретения определен приложенной формулой изобретения и ее эквивалентами.

Здесь будут рассмотрены устройства, способы и носители информации, связанные с обновлением ячеек памяти. В вариантах осуществления изобретения перекрестная энергонезависимая память, например РСМ, может содержать несколько ячеек памяти, обладающих соответствующими значениями напряжения, которые могут быть установлены равными первому пороговому напряжению или второму пороговому напряжению. Тем не менее со временем значения напряжения одной или более ячеек памяти, которые установлены равным первому или второму пороговому напряжению, могут начать изменяться. Контроллер памяти может быть выполнен для осуществления операции чтения ячеек памяти. Операция чтения может повторно устанавливать значения напряжения ячеек памяти, которые были установлены равными первому пороговому напряжению. То есть благодаря операции чтения значения напряжения ячеек памяти могут возвращаться к первому пороговому напряжению. Также операция чтения может позволить контроллеру памяти определить ячейки памяти, значения напряжения в которых были установлены равными второму пороговому напряжению. Далее контроллер памяти может быть выполнен для осуществления операции записи с целью повторного установления значений напряжения ячеек памяти, равными второму пороговому напряжению.

Различные операции могут быть описаны как несколько последовательных дискретных действий или операций, чтобы наиболее просто понять объект патентования. Тем не менее порядок описания не нужно понимать так, что указанные операции необходимо выполнять в определенном порядке. В частности, эти операции можно не выполнять в порядке появления. Описанные операции могут быть выполнены в порядке, отличном от приведенного в описанном варианте осуществления изобретения. Могут быть осуществлены различные дополнительные операции и/или описанные операции могут быть опущены в дополнительных вариантах осуществления изобретения.

Для целей настоящего изобретения под фразами «А и/или В» и «А или В» понимаем (А), (В) или (А и В). Для целей настоящего изобретения фраза «А, В и/или С» означает (А), (В), (С), (А и В), (А и С), (В и С) или (А, В и С).

В описании могут быть использованы фразы «в варианте осуществления изобретения» или «в вариантах осуществления изобретения», которые могут ссылаться на один или более одинаковых или разных вариантов осуществления изобретения. Более того, при использовании относительно вариантов осуществления изобретения термины «содержит», «включает в себя», «имеет» и подобные являются синонимами.

В настоящем документе термин «модуль» может относиться, или быть частью, или содержать следующее: специализированную интегральную схему (ASIC), электронную схему, процессор (используемый совместно, выделенный или группу) и/или память (используемую совместно, выделенную или группу), в которых выполняют одно или более программно или аппаратно реализованных программ, объединенную логическую схему и/или другие подходящие компоненты, которые обеспечивают описываемую функциональность. В настоящем документе «реализуемым компьютером способом» могут называть любой способ, выполняемый одним или более процессорами, вычислительной системой, содержащей один или более процессоров, мобильным устройством, таким как смартфон (который может содержать один или более процессоров), планшетом, ноутбуком, телевизионной приставкой, игровой консолью и так далее.

Как показано на фиг. 1, в различных вариантах осуществления изобретения устройство 100 хранения может содержать перекрестную энергонезависимую память 104, такую как РСМ. Информация может быть записана в перекрестную энергонезависимую память 104 и/или считана из перекрестной энергонезависимой памяти 104 с помощью контроллера ПО памяти. Контроллер ПО памяти может быть соединен с перекрестной энергонезависимой памятью 104 с помощью одной или более линий 116 связи, например с помощью шины памяти. Операции чтения или записи могут быть осуществлены соответственно логической схемой чтения или логической схемой записи, которые могут быть отделены одна от другой или объединены, например, в модуле 120 чтения/записи. Для целей этого описания ниже будет рассмотрен модуль 120 чтения/записи и может быть предположено, что он содержит как логическую схему чтения, так и логическую схему записи. Тем не менее в других вариантах осуществления изобретения модуль чтения может содержать логическую схему чтения и осуществлять описанные ниже операции чтения, а модуль записи может содержать логическую схему записи и осуществлять описанные ниже операции записи, и модуль чтения, и модуль записи могут быть отделены друг от друга.

Как показано, модуль 120 чтения/записи может быть элементом контроллера ПО памяти, а в некоторых вариантах осуществления изобретения модуль 120 чтения/записи (или отдельный модуль чтения и/или модуль записи) может быть отделен от контроллера 110 памяти, но может быть соединен с контроллером 110 памяти. В некоторых вариантах осуществления изобретения (не показаны) модуль 120 чтения/записи может быть элементом перекрестной энергонезависимой памяти 104 или может быть другим образом соединен с перекрестной энергонезависимой памятью 104. В некоторых вариантах осуществления изобретения (не показаны) модуль 120 чтения/записи может быть распределен между контроллером 110 памяти и перекрестной энергонезависимой памятью 104. В некоторых вариантах осуществления изобретения модуль 120 чтения/записи может быть реализован в виде аппаратного обеспечения, аппаратнореализованного программного обеспечения, программного обеспечения или любого объединения перечисленного. В вариантах осуществления изобретения модуль 120 чтения/записи может быть выполнен для осуществления операции чтения с целью чтения значений напряжения одной или более ячеек 112 перекрестной энергонезависимой памяти 104, что будет описано ниже. Кроме того, модуль 120 чтения/записи может быть выполнен для осуществления операции записи с целью установки или повторной установки значений напряжения одной или более ячеек 112 перекрестной энергонезависимой памяти 104, что будет дополнительно описано ниже. В вариантах осуществления изобретения значение напряжения ячейки 112 перекрестной энергонезависимой памяти 104 можно рассматривать как значение напряжения, измеренное в ячейке 112 памяти при операции чтения, осуществляемой модулем 120 чтения/записи, что будет дополнительно описано ниже.

В некоторых вариантах осуществления изобретения контроллер 110 памяти и/или устройство 100 хранения могут быть соединены с другими компонентами вычислительной системы с помощью одной или более внешних линий 106 связи, таких как шина (PCI) соединения периферийных компонентов или шина PCI Express. Хотя это не показано на чертежах, различные другие компоненты могут быть соединены с устройством 100 хранения с помощью одной или более линий 106 связи, в том числе, помимо прочего, один или более центральных процессоров (CPU), энергозависимая память (например, DRAM), одно или более устройств ввода/вывода (I/O), альтернативные процессоры (например, графические процессоры) и так далее. В различных вариантах осуществления изобретения устройство 100 хранения может быть твердотельным накопителем (SSD) или гибридным накопителем (HHD) на жестких дисках.

Во многих случаях, в том числе в примере с фиг. 1, перекрестная энергонезависимая память 104 может содержать несколько кристаллов 108. Например, на фиг. 1 перекрестная энергонезависимая память 104 содержит N кристаллов 108. N может быть любым положительным целым числом. В других вариантах осуществления изобретения перекрестная энергонезависимая память 104 может содержать только один кристалл 108. Как показано на фиг. 1, каждый кристалл 108 может содержать одну или более ячеек 112 памяти. Ясно, что, хотя в каждом кристалле 108 показаны три ячейки 112 памяти, каждый кристалл может содержать больше или меньше ячеек 112 памяти. Кроме того, каждый кристалл 108 не обязательно содержит такое же количество ячеек 112 памяти, как и другой кристалл 108. Наконец, данные могут быть организованы с разной группировкой, как описано в настоящем документе, например, ячейки 112 памяти могут быть организованы в блоки или страницы памяти.

Как описано выше, перекрестная энергонезависимая память, такая как перекрестная энергонезависимая память 104, или каждый кристалл перекрестной энергонезависимой памяти, такой как кристалл 108 перекрестной энергонезависимой памяти 104, может содержать несколько ячеек памяти, организованных в дву- или трехмерную решетку. На фиг. 2 показана решетка 200 ячеек 205 перекрестной энергонезависимой памяти, такой как перекрестная энергонезависимая память 104. Более конкретно, решетка 200 может быть решеткой ячеек 205 памяти на кристалле, таком как кристалл 108 перекрестной энергонезависимой памяти 104. Хотя решетка 200 здесь показана как двумерная решетка, в вариантах осуществления изобретения решетка 200 может быть трехмерной решеткой. В одной или более ячейках 205 памяти может быть установлено первое пороговое напряжение или второе пороговое напряжение, которые могут соответственно указывать на некоторое логическое значение, такое как «0» или «1». Следовательно, в вариантах осуществления изобретения каждую ячейку 205 памяти можно рассматривать как содержащую бит информации.

Более конкретно, перекрестная энергонезависимая память, такая как перекрестная энергонезависимая память 104, которая может быть РСМ, может быть выполнена из халькогенидного стекла. Например, перекрестная энергонезависимая память может содержать такой материал, как Ge2Sb2Te5, называемый GST, или InSbTe, называемый IST. В перекрестной энергонезависимой памяти могут быть использованы другие материалы, тем не менее для простоты объяснения ниже, в качестве примера, будет рассмотрено только халькогенидное стекло. Более конкретно, каждая ячейка памяти, такая как ячейки 205 памяти, может быть отдельным дискретным элементом из халькогенидного стекла. Если халькогенидное стекло ячейки 205 памяти быстро нагреть и затем быстро охладить, то халькогенидное стекло может перейти в физическое состояние, известное как «аморфное» состояние. В отличие от этого, если халькогенидное стекло ячейки 205 памяти держать при определенной температуре заданное количество времени, то халькогенидное стекло может кристаллизоваться и перейти в физическое состояние, известное как «кристаллическое» состояние. В вариантах осуществления изобретения процесс нагревания может направлять или осуществлять устройство записи, такое как модуль 120 чтения/записи, и этот процесс может быть осуществлен с помощью пропускания тока через заданную ячейку 205 памяти в течение заданного количества времени. Естественное электрическое сопротивление халькогенидного стекла может порождать теплоту в ячейке 205 памяти и в результате произойдет описанное фазовое изменение ячейки 205 памяти.

В вариантах осуществления изобретения ячейка 205 памяти в аморфном состоянии может обладать другим электрическим сопротивлением по сравнению с ячейкой 205 памяти в кристаллическом состоянии. Например, ячейка 205 памяти в аморфном состоянии может обладать сравнительно малым электрическим сопротивлением и существовать в состоянии «установить». В отличие от этого, ячейка 205 памяти в кристаллическом состоянии может обладать сравнительно большим электрическим сопротивлением и существовать в состоянии «повторно установить». В вариантах осуществления изобретения состояние «установить» и состояние «повторно установить» могут соответственно отвечать логическому «0» и логической «1», и наоборот. Для простоты описания, ниже термины «низкое» состояние и «высокое» состояние будут использоваться соответственно для описания состояния «установить» и состояния «повторно установить» ячейки 205 памяти.

Для чтения логического значения ячейки 205 памяти небольшой ток может быть пропущен через ячейку 205 памяти и может быть измерено значение напряжения на ячейке 205 памяти. Так как напряжение равно произведению силы тока на сопротивление и ячейка 205 памяти в «низком» состоянии может обладать сопротивлением, отличным от ячейки 205 памяти в «высоком» состоянии, то измеренное значение напряжения ячейки 205 памяти может быть различным в зависимости от того, в каком состоянии находится ячейка 205 памяти. Например, на «низкое» состояние ячейки 205 памяти может указывать измерение сравнительно малого значения напряжения на ячейке 205 памяти, а на «высокое» состояние ячейки 205 памяти может указывать измерение сравнительно большого значения напряжения на ячейке 205 памяти.

Так как конкретное состояние халькогенидного стекла может приводить к конкретному сопротивлению, что может привести к измерению конкретного значения напряжения, то может быть целесообразно установить физическое состояние каждой ячейки 205 памяти так, чтобы ячейка 205 памяти порождала измерение конкретного значения напряжения во время операции чтения, известного как порог VТ, напряжение для «низкого» или «высокого» состояний. В вариантах осуществления изобретения, и как будет дополнительно описано ниже, операция чтения может быть процессом сравнения измеренного значения напряжения для ячейки памяти с эталонным значением напряжения, что делают с целью определить, находится ли ячейка памяти в «низком» или «высоком» состоянии. В отличие от этого, операция по изменению физических свойств ячейки 205 памяти, чтобы ячейка 205 порождала измерение заданного значения напряжения во время операции чтения, может быть известна как операция записи. Более конкретно, в модуле 120 чтения/записи могут осуществлять операцию записи с целью такого изменения физических свойств халькогенидного стекла одной или более ячеек 205 памяти, что каждая ячейка 205 памяти, установленная в «низкое» состояние, будет обладать одинаковым электрическим сопротивлением, и, следовательно, в модуле 120 чтения/записи может считываться такое же сравнительно низкое значение напряжения для всех ячеек 205 памяти, находящихся в «низком» состоянии. Аналогично, в модуле 120 чтения/записи могут осуществлять операцию записи с целью такого изменения физических свойств халькогенидного стекла одной или более ячеек 205 памяти, что каждая ячейка 205 памяти, установленная в «высокое» состояние, будет обладать одинаковым электрическим сопротивлением, и, следовательно, в модуле 120 чтения/записи может считываться такое же сравнительно большое значение напряжения для всех ячеек 205 памяти, находящихся в «высоком» состоянии.

В вариантах осуществления изобретения целевая ячейка 210 памяти может быть окружена несколькими соседними ячейками 215 памяти. Когда в устройстве записи, таком как модуль 120 чтения/записи контроллера 110 памяти, записывают значение в целевую ячейку 210 памяти, то это может оказывать влияние на значения напряжений в соседних ячейках 215 памяти. Этот эффект может быть назван «помехами для памяти». Как отмечено выше, запись значения в целевую ячейку 210 памяти может включать в себя нагревание и/или охлаждение целевой ячейки 210 памяти. Кроме того, чтение значения из целевой ячейки 210 памяти может включать в себя прохождение известного тока по целевой ячейке 210 памяти и измерение напряжения на целевой ячейке 210 памяти. В каждом из этих процессов целевая ячейка 210 памяти может вырабатывать теплоту в одной или более соседних ячейках 215 памяти. Помимо этого или в качестве альтернативы, теплота может вырабатываться в целевой ячейке 210 памяти. Эта выработанная теплота может приводить к изменению состояния одной или более целевых ячеек 210 памяти, соседних ячеек 215 памяти или некоторых других ячеек 205 памяти в решетке 200 ячеек 205 памяти. Помехи для памяти могут быть вызваны дополнительными или альтернативными механизмами, такими как механический отказ в ячейке 205 памяти, или некоторыми другими причинами.

Когда состояние заданной ячейки 205 памяти, такой как целевая ячейка 210 памяти, соседняя ячейка 215 памяти или некоторая другая ячейка 205 памяти, изменяется, то может измениться измеренное значение напряжения этой ячейки памяти. Более конкретно, значение напряжения ячейки 205 памяти, которое установлено равным «низкому» пороговому напряжению, может немного возрасти. Например, если «низкое» пороговое напряжение заданной перекрестной энергонезависимой памяти 104 равно 1,0 В, то для ячейки памяти, которую нужно установить в «низкое» состояние, могут изначально установить с помощью модуля 120 чтения/записи и операции записи значение напряжения, равное 1,0 В при операции чтения. Тем не менее из-за помех для памяти значение напряжения этой ячейки 205 памяти может возрасти со временем. В качестве альтернативы, если «высокое» пороговое напряжение заданной перекрестной энергонезависимой памяти 104 равно 2,0 В, то для ячейки памяти, которую нужно установить в «высокое» состояние, могут изначально установить с помощью модуля 120 чтения/записи и операции записи значение напряжения, равное 2,0 В при операции чтения. Тем не менее ячейки 205 памяти, которые установлены в «высокое» состояние, могут измениться как в сторону увеличения, так и в сторону уменьшения. То есть со временем в ячейке 205 памяти, которая установлена в «высокое» состояние, значение напряжения может стать больше или меньше 2,0 В.

Это изменение может привести к ошибкам данных, так как в модуле 120 чтения/записи, осуществляющем операцию чтения заданной ячейки 025 памяти, могут предположить, что ячейка 205 памяти находится в «высоком» состоянии, когда она находится в «низком» состоянии и наоборот. Следовательно, из-за этих ошибок может быть целесообразно периодически обновлять одну или более ячеек 205 перекрестной энергонезависимой памяти 104. То есть в некоторых случаях может быть целесообразно, чтобы модуль 120 чтения/записи обновлял значение напряжения каждой ячейки 205 памяти путем осуществления операции записи с целью установки в каждой ячейке 205 памяти нужного порогового напряжения. Другими словами, для ячеек 205 памяти, которые должны быть в «высоком» состоянии, в модуле 120 чтения/записи могут так изменить физическое состояние ячеек памяти, чтобы измеренное значение напряжения этих ячеек 205 памяти во время операции чтения было равно «высокому» порогу напряжения. В отличие от этого, для ячеек 205 памяти, которые должны быть в «низком» состоянии, в модуле 120 чтения/записи могут так изменить физическое состояние ячеек памяти, чтобы измеренное значение напряжения этих ячеек 205 памяти во время операции чтения было равно «низкому» порогу напряжения. Тем не менее во многих случаях полное обновление всех ячеек в заданной перекрестной энергонезависимой памяти, такой как перекрестная энергонезависимая память 104, может быть нецелесообразно, так как операция полного обновления может приводить к появлению периода ожидания системы и/или дополнительному потреблению системой электроэнергии.

На фиг. 3 показан пример альтернативного процесса осуществления обновления нескольких ячеек памяти, например ячеек 205 перекрестной энергонезависимой памяти, такой как перекрестная энергонезависимая память 104. В начале, в модуле чтения/записи, таком как модуль 120 чтения/записи, в 300 могут осуществить операцию чтения с целью чтения значения напряжения каждой ячейки памяти в заданной перекрестной энергонезависимой памяти. Так как операция чтения подразумевает измерение значения напряжения на каждой ячейке памяти при прохождении известного тока по ячейке, сама операция чтения может привести к изменению состояния ячейки памяти.

Более конкретно, операция чтения может включать в себя осуществляемое в модуле чтения/записи сравнение измеренного напряжения на ячейке перекрестной энергонезависимой памяти с эталонным напряжением. Эталонное напряжение может быть, например, напряжением, которое больше «низкого» порога напряжения, но меньше «высокого» порога напряжения. В качестве примера, если «низкий» порог напряжения равен 1,0 В, а «высокий» порог напряжения равно 2,0 В, то эталонное напряжение может быть равно 1,5 В. Тем не менее в других вариантах осуществления изобретения одно или более из следующих величин могут иметь другие значения: «низкий» порог напряжения, «высокий» порог напряжения и/или эталонное напряжение. В некоторых вариантах осуществления изобретения операция чтения может приводить к обновлению значения напряжения одной или более ячеек памяти, которые находятся в «низком» состоянии, так что значение напряжения на одной или более ячейках памяти, находящихся в «низком» состоянии, равно «низкому» порогу напряжения.

Далее, в модуле чтения/записи могут идентифицировать, по меньшей мере, частично на основе операции чтения, осуществленной в 300, ячейки перекрестной энергонезависимой памяти, которые находятся в «высоком» состоянии. Более конкретно, в модуле 120 чтения/записи и/или контроллере памяти, таком как контроллер 110 памяти, могут идентифицировать ячейки перекрестной энергонезависимой памяти, значение напряжения на которых больше эталонного напряжения, как описано выше.

Наконец, в 310 в модуле чтения/записи могут обновить значения напряжения для ячеек перекрестной энергонезависимой памяти, которые установлены равными «высокому» порогу напряжения. То есть в модуле чтения/записи могут осуществить операцию записи в одну или более ячеек памяти, что так изменит физическое состояние одной или более ячеек памяти, что значение напряжения на одной или более ячейках памяти повторно установится равным «высокому» порогу напряжения.

Далее процесс обновления одной или более ячеек памяти может закончиться в 315.

В некоторых вариантах осуществления изобретения перекрестная энергонезависимая память, такая как перекрестная энергонезависимая память 104, может содержать одну или более ячеек памяти, которые порождают ошибки в ходе операции чтения ячейки перекрестной энергонезависимой памяти. На фиг. 4 показан альтернативный процесс, направленный на потенциальное уменьшение количества ошибок, которые могут возникнуть при операции чтения одной или более ячеек перекрестной энергонезависимой памяти.

В начале, в модуле чтения/записи, таком как модуль 120 чтения/записи, в 400 могут считать значение напряжения каждой ячейки памяти в заданной перекрестной энергонезависимой памяти. Как описано выше для элемента 300 с фиг. 3, сама операция чтения может привести к изменению физического состояния ячейки памяти и, следовательно, ее значения напряжения. Кроме того, одна или более ячеек перекрестной энергонезависимой памяти может быть идентифицирована как находящаяся в «высоком» состоянии в 405 с помощью модуля 120 чтения/записи в ходе операции чтения, как описано выше при рассмотрении элемента 305 с фиг. 3. Наконец, в модуле чтения/записи могут обновить значения напряжения одной или более ячеек, которые установлены в «высокое» состояние в 410, что делают путем осуществления операции записи в одну или более ячеек памяти, которая повторно устанавливает значения напряжения одной или более ячеек памяти равными «высокому» порогу, как описано выше при рассмотрении элемента 310 с фиг. 3.

Далее в контроллере памяти, например, контроллере 110 памяти или модуле 120 чтения/записи контроллера памяти, в элементе 415 могут осуществить проверку на наличие ошибок в данных, сохраненных в перекрестной энергонезависимой памяти. В некоторых вариантах осуществления изобретения проверка на наличие ошибок может включать в себя проверку с помощью исправляющего ошибки кода (ЕСС) некоторых или всех данных, сохраненных в перекрестной энергонезависимой памяти, хотя в других вариантах осуществления изобретения (не показаны) может быть осуществлена проверка на наличие ошибок другого типа. Более конкретно, если осуществляют проверку с помощью ЕСС, в контроллере памяти могут одно или более логических значений из ячеек перекрестной энергонезависимой памяти или одно или более кодовых слов на основе логических значений из ячеек перекрестной энергонезависимой памяти сравнивать с одним или более известными значениями или кодовыми словами. В некоторых вариантах осуществления изобретения кодовые слова на основе логических значений из ячеек памяти и/или известные кодовые слова могут храниться в перекрестной энергонезависимой памяти, а в других вариантах осуществления изобретения и кодовые слова и/или известные кодовые слова могут храниться в другой памяти вычислительной системы, например, в постоянном запоминающем устройстве (ROM), оперативном запоминающем устройстве (RAM) или некоторой другой памяти вычислительной системы. На основе сравнения контроллер памяти может быть настроен для идентификации одной или более ячеек перекрестной энергонезависимой памяти, которые порождают ошибку в ходе операции чтения ячейки памяти. Ошибка может представлять собой сигнал, что ячейка памяти находится в «высоком» состоянии, когда ячейка памяти находится в «низком» состоянии, и наоборот. В качестве альтернативы ошибка может заключаться в том, что состояние ячейки памяти не может быть определено.

Далее в 420 в контроллере памяти могут сравнить общее количество ячеек памяти, которые порождают ошибку, с порогом ошибок. В некоторых случаях порог ошибок может быть равным 10%, а в других вариантах осуществления изобретения порог ошибок может быть некоторым другим числом. То есть, если 10% ячеек памяти порождают ошибки в ходе операции чтения, то в контроллере памяти могут определить, что количество ячеек памяти, которые порождают ошибки, превосходит порог. Если общее количество ячеек памяти, которые порождают ошибки, не превышает порог, то процесс может закончиться в 425.

Тем не менее, если общее количество ячеек памяти, которые порождают ошибки, превышает порог, то в контроллере памяти могут обновить одну или более ячеек памяти, которые порождают ошибки, что делают в 430 путем осуществления операции записи для этих ячеек. Более конкретно, для ячеек памяти, которые идентифицировали как находящиеся в «низком» состоянии, в модуле чтения/записи контроллера памяти могут осуществить операцию записи с целью повторной установки значения напряжения ячеек памяти равным низкому порогу напряжения. Аналогично, для ячеек памяти, которые идентифицировали как находящиеся в «высоком» состоянии, в модуле чтения/записи контроллера памяти могут осуществить операцию записи с целью повторной установки значения напряжения памяти равным высокому порогу напряжения. В некоторых вариантах осуществления изобретения эти операции записи могут быть обращены, например, если ячейки, которые должны быть в «низком» состоянии, читают как находящиеся в «высоком» состоянии или наоборот, то в модуле чтения/записи могут осуществить операцию записи в ячейки, идентифицированные как находящиеся в «низком» состоянии с целью установки значений напряжения этих ячеек равным высокому порогу напряжения или, наоборот, для ячеек, которые идентифицированы как находящиеся в «высоком» состоянии. В некоторых вариантах осуществления изобретения значение напряжения для операции записи может быть выбрано на основе, по меньшей мере, частично проверки на наличие ошибок, осуществленной в 420, и операция записи, осуществляемая в 430, может быть основана на записи значения напряжения в ячейку памяти, что приведет к отсутствию ошибки при проверке на наличие ошибок в ходе операции чтения. Например, ячейки памяти, которые порождают ошибки, могут быть идентифицированы в 405, и значение напряжения этих ячеек памяти может быть «заменено на противоположное» во время операции обновления в 430, так что ячейки памяти, которые порождают ошибки в ходе операции чтения, так как их считывают как находящиеся в «низком» состоянии, могут быть обновлены до «высокого» состояния или наоборот.

На фиг. 5 показан альтернативный процесс, направленный на уменьшение количества ошибок, которые возникают при операции чтения одной или более ячеек памяти, например перекрестной энергонезависимой памяти. В начале, в 500 в модуле чтения/записи, таком как модуль 120 чтения/записи, могут сначала считать значение напряжения каждой ячейки в заданной памяти, например перекрестной энергонезависимой памяти из примера. Как описано выше для элемента 300 с фиг. 3 и элемента 400 с фиг. 4, сама операция чтения может привести к изменению состояния ячейки памяти. Кроме того, одна или более ячеек перекрестной энергонезависимой памяти из примера могут быть идентифицированы как находящиеся в «высоком» состоянии в 505 с помощью модуля чтения/записи в ходе операции чтения, как описано выше при рассмотрении элемента 305 с фиг. 3 и элемента 405 с фиг. 4.

Далее в 510 в контроллере памяти, например контроллере 110 памяти или модуле 120 чтения/записи контроллера памяти, могут осуществить проверку на наличие ошибок в данных, сохраненных в перекрестной энергонезависимой памяти, что может быть аналогично проверке на наличие ошибок, описанной выше при рассмотрении 415. В некоторых вариантах осуществления изобретения проверка на наличие ошибок может являться проверкой с помощью ЕСС некоторых или всех данных, сохраненных в перекрестной энергонезависимой памяти. В других вариантах осуществления изобретения (не показаны) может быть осуществлена проверка на наличие ошибок другого типа. На основе сравнения контроллер памяти может быть реализован для идентификации одной или более ячеек перекрестной энергонезависимой памяти, которые порождают ошибку в ходе операции чтения ячейки памяти. В 515 в контроллере памяти могут сравнить общее количество ячеек памяти, которые порождают ошибку, с порогом ошибок, что может быть аналогично сравнению, описанному при рассмотрении 420. В некоторых случаях порог ошибок может быть равным 10%, а в других вариантах осуществления изобретения порог ошибок может быть некоторым другим числом.

Если общее количество ячеек памяти, которые порождают ошибки, не превышает порог, то в контроллере памяти могут перейти к обновлению ячеек памяти, которые идентифицированы в 505 и которые установлены как имеющие «высокий» порог напряжения, что делают в 520 путем осуществления повторной записи значений напряжения для этих ячеек. Процесс обновления и повторной записи может быть аналогичен, например, процессу обновления и повторной записи, который описан в 410. Далее процесс может закончиться в 525.

Тем не менее, если общее количество ячеек памяти, которые порождают ошибки, превышает порог, то в контроллере памяти в 530 могут обновить и осуществить повторную запись во все ячейки памяти в перекрестной энергонезависимой памяти из примера. То есть для каждой ячейки памяти в перекрестной энергонезависимой памяти из примера, которая идентифицирована как находящаяся в «низком» состоянии, в модуле чтения/записи контроллера памяти могут осуществить операцию записи с целью повторной установки значения напряжения ячейки памяти равным низкому порогу напряжения. Аналогично, для каждой ячейки памяти в перекрестной энергонезависимой памяти из примера, которая идентифицирована как находящаяся в «высоком» состоянии, в модуле чтения/записи контроллера памяти могут осуществить операцию записи с целью установки значения напряжения ячеек памяти равным высокому порогу напряжения. В некоторых вариантах осуществления изобретения эти операции записи могут быть обращены, например, если ячейки, которые должны быть в «низком» состоянии, считывают как находящиеся в «высоком» состоянии или наоборот. Далее в модуле чтения/записи могут осуществить операцию записи в ячейки, идентифицированные как находящиеся в «низком» состоянии, с целью повторной установки значений напряжения этих ячеек равными высокому порогу напряжения, или, наоборот, для ячеек, которые идентифицированы как находящиеся в «высоком» состоянии. В некоторых вариантах осуществления изобретения значение напряжения для операции записи может быть выбрано на основе, по меньшей мере, частично проверки на наличие ошибок, осуществленной в 510, и операция записи, осуществляемая в 530, может быть основана на записи значения напряжения в ячейку памяти, что приведет к отсутствию ошибки при проверке на наличие ошибок в ходе операции чтения значения напряжения ячейки. Далее процесс может закончиться в 525. Хотя приведенные выше процессы описаны для всей перекрестной энергонезависимой памяти из примера, процесс, описанный при рассмотрении фиг. 3, 4 и 5, может быть использован только для конкретного кристалла, страницы в кристалле, блоков ячеек памяти или некоторого другого подмножества ячеек памяти.

В вариантах осуществления изобретения, процессы, описанные выше и касающиеся, например, фиг. 3, 4 и 5, могут обеспечивать значительные преимущества для контроллера памяти, такого как контроллер 110 памяти. Более конкретно, чистое время ожидания процесса обновления, показанного на фиг. 4, может иметь порядок примерно 200 наносекунд, а потребленная энергия может иметь порядок примерно 80 пикоДжоулей на ячейку памяти. Это время ожидания и потребление энергии может составлять примерно треть от времени ожидания и потребляемой энергии для существующих процессов. Процесс, показанный на фиг. 5, может обладать аналогичным временем ожидания и/или экономией энергии.

На фиг. 6 показан пример вычислительного устройства 600, в котором в соответствии с различными вариантами осуществления изобретения могут быть реализованы системы, такие как описанная выше перекрестная энергонезависимая память 104, контроллер 110 памяти и/или модуль 120 чтения/записи. Вычислительное устройство 600 может содержать некоторое количество компонентов, один или более процессоров 604, перекрестную энергонезависимую память 104 в форме одного или более кристаллов 108, контроллер 110 памяти, модуль 120 чтения/записи и, по меньшей мере, одну интегральную микросхему 606 связи.

В различных вариантах осуществления изобретения каждый из одного или более процессоров 604 может содержать одно или более ядер процессора. В различных вариантах осуществления изобретения, по меньшей мере, одна интегральная микросхема 606 связи может быть физически и электрически соединена с одним или более процессорами 604. В других вариантах осуществления изобретения интегральная микросхема 606 связи может быть частью одного или более процессоров 604. В различных вариантах осуществления изобретения вычислительное устройство 600 может содержать печатную плату 602 (РСВ) Для этих вариантов осуществления изобретения на этой плате могут быть размещены один или более процессоров 604 и интегральная микросхема 606 связи. В альтернативных вариантах осуществления изобретения различные компоненты могут быть соединены без использования РСВ 602.

В зависимости от приложений вычислительное устройство 600 может содержать другие компоненты, которые могут быть физически и электрически соединены с РСВ 602, а могут не быть физически и электрически соединены с РСВ 602. Этими другими компонентами являются, помимо прочего, энергозависимая память (например, динамическая RAM (DRAM) 608), энергонезависимая память, такая как ROM 610, контроллер 614 ввода/вывода, цифровой сигнальный процессор (не показан), криптографический процессор (не показан), графический процессор 616, одна или более антенн 618, дисплей (не показан), сенсорный дисплей 620, контроллер 622 сенсорного экрана, аккумулятор 624, аудиокодек (не показан), видеокодек (не показан), устройство 628 системы глобального позиционирования (GPS), компас 630, устройство измерения ускорения (не показано), гироскоп (не показан), микрофон 632, камера 634 и запоминающее устройство большой емкости (такое как накопитель на жестких дисках, твердотельный накопитель, компакт-диск (CD), универсальный цифровой диск (DVD)) (не показано) и так далее. В разных вариантах осуществления изобретения процессор 604 может быть объединен на том же кристалле с другими компонентами с целью формирования Системы на кристалле (SoC). В вариантах осуществления изобретения DRAM 608 и/или ROM 610 могут являться или могут содержать перекрестную энергонезависимую память, такую как перекрестная энергонезависимая память 104, которая может быть соответственно соединена с контроллером памяти, таким как контроллер 110 памяти.

В различных вариантах осуществления изобретения вместо перекрестной энергонезависимой памяти 104 или в дополнение к ней вычислительное устройство 600 может содержать постоянную или энергонезависимую память, например флеш-память. В некоторых вариантах осуществления изобретения один или более процессоров 604 и/или флеш-память 612 могут содержать соответствующее аппаратно реализованное программное обеспечение (не показано), в котором хранятся программные команды, выполненные так, чтобы вычислительное устройство 600 в ответ на выполнение программных команд одним или более процессорами 604 осуществляло все или выбранные аспекты блоков, описанных выше при рассмотрении фиг. 3, 4 или 5. В различных вариантах осуществления изобретения эти аспекты дополнительно или в качестве альтернативы могут быть реализованы с использованием аппаратного обеспечения, отличного от одного или более процессоров 604 или флеш-памяти 612.

Интегральная микросхема 606 связи может обеспечить проводную и/или беспроводную связь с целью передачи данных в вычислительное устройство 600 и от него. Термин «беспроводной» и его производные могут быть использованы для описания схем, устройств, систем, способов, технологий, каналов связи и так далее, с помощью которых могут передавать данные с использованием модулированного электромагнитного излучения по нетвердой среде. Этот термин не подразумевает то, что соответствующие устройства не содержат никаких проводов, хотя в некоторых вариантах осуществления изобретения эти устройства могут не содержать проводов. Интегральная микросхема 606 связи может реализовывать любое количество беспроводных стандартов или протоколов, в том числе, помимо прочего, ШЕЕ 802,20, общий сервис (GPRS) пакетной радиопередачи, стандарт эволюционировавшей оптимизированной передачи данных (Ev-DO), развитый высокоскоростной пакетный доступ (HSPA+), развитый высокоскоростной пакетный доступ по нисходящему каналу (HSDPA+), развитый высокоскоростной пакетный доступ по восходящему каналу (HSUPA+), глобальная система мобильной связи (GSM), технология EDGE (Enhanced Data rates for GSM Evolution), множественный доступ с кодовым разделением (CDMA), множественный доступ с временным разделением (TDMA), Технология улучшенной цифровой беспроводной связи (DECT), Bluetooth, их производные, а также любой другой беспроводной протокол, который обозначен как 3G, 4G, 5G и далее. Вычислительное устройство 600 может содержать несколько интегральных микросхем 606 связи. Например, первая интегральная микросхема 606 связи может быть выделена для беспроводной связи на более короткие расстояния, такой как Wi-Fi и Bluetooth, и вторая интегральная микросхема 606 связи может быть выделена для беспроводной связи на более длинные расстояния, такой как GPS, EDGE, GPRS, CDMA, WiMAX, LTE, Ev-DO, и других.

В различных реализациях вычислительное устройство 600 может быть лэптопом, нетбуком, ноутбуком, ультрабуком, смартфоном, планшетом, персональным цифровым помощником (PDA), ультрамобильным ПК, сотовым телефоном, настольным компьютером, сервером, принтером, сканером, телевизионной приставкой, блоком управления развлечениями (например, игровой консолью), цифровой камерой, переносным музыкальным плеером или цифровым видео проигрывателем. В других вариантах осуществления изобретения вычислительное устройство 600 может быть любым другим электронным устройством, в котором обрабатывают данные.

В вариантах осуществления изобретения первый пример настоящего изобретения может включать в себя контроллер памяти для обновления значения напряжения ячейки памяти, контроллер памяти содержит: логическую схему чтения, выполненную для чтения значения напряжения ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, при этом во множестве ячеек памяти значения напряжения соответственно установлены равными первому пороговому напряжению или второму пороговому напряжению; и логическую схему записи, соединенную с логической схемой чтения и выполненную для обновления значения напряжения первой одной или более ячеек из множества ячеек памяти, которое установлено равным второму пороговому напряжению, без изменения значения напряжения второй одной или более ячеек из множества ячеек памяти, которое установлено равным первому пороговому напряжению.

Пример 2 может содержать контроллер памяти из примера 1, при этом второе пороговое напряжение больше первого порогового напряжения.

Пример 3 может содержать контроллер памяти из примера 1, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

Пример 4 может содержать контроллер памяти из любого примера 1-3, при этом логическая схема записи выполнена для осуществления операции записи с целью повторной установки значения напряжения каждой ячейки памяти из первой одной или более ячеек из множества ячеек памяти равным второму пороговому напряжению для обновления значения напряжения первой одной или более ячеек из множества ячеек памяти.

Пример 5 может содержать контроллер памяти из любого примера 1-3, при этом логическая схема чтения выполнена для обновления значения напряжения второй одной или более ячеек из множества ячеек памяти, что делают путем сравнения значения напряжения каждой ячейки памяти во второй одной или более ячейках из множества ячеек памяти с эталонным напряжением.

Пример 6 может содержать контроллер памяти из примера 5, при этом эталонное напряжение больше значения первого порогового напряжения и меньше значения второго порогового напряжения.

Пример 7 может содержать контроллер памяти из любого примера 1-3, дополнительно содержащий логическую схему исправления ошибок, соединенную с логической схемой чтения и логической схемой записи, логическая схема исправления ошибок выполнена для следующего: идентифицировать третью одну или более ячеек памяти из множества ячеек памяти, которые порождают ошибку при чтении значения напряжения третьей одной или более ячеек памяти с помощью логической схемы чтения; и определять, превышает ли порог ошибок количество третьих одной или более ячеек памяти из множества ячеек памяти.

Пример 8 может содержать контроллер памяти из примера 7, при этом логическая схема записи дополнительно выполнена для следующего: осуществляют операцию записи, в ответ на определение с помощью логической схемы исправления ошибок, что количество третьих одной или более ячеек памяти из множества ячеек памяти превышает порог ошибок, повторно устанавливают соответствующие значения напряжения каждой ячейки памяти в третьих одной или более ячейках памяти равными первому пороговому напряжению, если значение напряжения ячейки памяти установлено равным первому пороговому напряжению; и осуществляют операцию записи в ответ на определение с помощью логической схемы исправления ошибок, с целью повторной установки соответствующих значений напряжения каждой ячейки памяти в третьих одной или более ячейках памяти равными второму пороговому напряжению, если значение напряжения ячейки памяти установлено равным второму пороговому напряжению.

Пример 9 может содержать способ обновления значения напряжение ячейки памяти, включающий в себя следующее: обновляют, с помощью контроллера памяти, первое значение напряжения первой ячейки памяти в перекрестной энергонезависимой памяти, соответственно содержащей множество ячеек памяти, обладающих значением напряжения установленным равным первому пороговому напряжению или второму пороговому напряжению, первое значение напряжение первой ячейки устанавливают равным первому пороговому напряжению и при этом обновление включает в себя сравнение первого значения напряжение первой ячейки памяти с эталонным напряжением; определяют, с помощью контроллера памяти и после обновления, одну или более ячеек памяти во множестве ячеек памяти, которые порождают ошибку при чтении соответствующих значений напряжения одной или более ячеек памяти; сравнивают, с помощью контроллера памяти, некоторое количество из одной или более ячеек памяти со значением порога ошибок; и обновляют, с помощью контроллера памяти, если количество из одной или более ячеек памяти меньше значения порога ошибок, второе значение напряжения второй ячейки памяти в перекрестной энергонезависимой памяти, что делают путем повторной записи второго порогового напряжение во вторую ячейку памяти без изменения первого значения напряжения первой ячейки памяти.

Пример 10 может содержать способ из примера 9, дополнительно включающий в себя следующее: обновляют, с помощью контроллера памяти, если количество из одной или более ячеек памяти больше значения порога ошибок, первое значение напряжения первой ячейки памяти, что делают путем повторной записи первого порогового напряжения в первую ячейку памяти.

Пример 11 может содержать способ из примеров 9 или 10, при этом первое пороговое напряжение меньше второго порогового напряжения.

Пример 12 может содержать способ из примеров 9 или 10, при этом эталонное напряжение больше значения первого порогового напряжения.

Пример 13 может содержать способ из примеров 9 или 10, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

Пример 14 может содержать один или более считываемых компьютером носителей, содержащих команды по обновлению значения напряжения ячейки памяти, эти команды таковы, что выполнение команд с помощью вычислительного устройства приводит к тому, что с помощью контроллера памяти вычислительного устройства: обновляют первое значение напряжения первой ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, до первого порогового напряжения или второго порогового напряжения, при этом обновление включает в себя сравнение первого значения напряжения первой ячейки памяти с эталонным напряжением; и обновляют второе значение напряжения второй ячейки памяти в перекрестной энергонезависимой памяти, что делают путем повторной записи второго порогового напряжения во вторую ячейку памяти.

Пример 15 может содержать один или более считываемых компьютером носителей из примера 14, при этом команды дополнительно выполнены так, чтобы в результате их работы с помощью контроллера памяти: определяют, после обновления первого значения напряжения и обновления второго значения напряжения, одну или более ячеек памяти во множестве ячеек памяти, которые порождают ошибку при чтении соответствующего значения напряжения упомянутых одной или более ячеек памяти; сравнивают, с помощью контроллера памяти, количество этих одной или более ячеек памяти со значением порога ошибок; и обновляют, с помощью контроллера памяти, если количество этих одной или более ячеек памяти больше значения порога ошибок, соответствующее значение напряжения этих одной или более ячеек памяти.

Пример 16 может содержать один или более считываемых компьютером носителей из примера 15, при этом обновление соответствующего значения напряжения этих одной или более ячеек памяти включает в себя следующее: повторно записывают первое пороговое напряжение в первое подмножество ячеек памяти в этих одной или более ячейках памяти, в которых установлено первое пороговое напряжение; и повторно записывают второе пороговое напряжение во второе подмножество ячеек памяти в этих одной или более ячейках памяти, в которых установлено второе пороговое напряжение.

Пример 17 может содержать один или более считываемых компьютером носителей из любого примера 14-16, при этом значение первого порогового напряжения меньше значения второго порогового напряжения.

Пример 18 может содержать один или более считываемых компьютером носителей из любого примера 14-16, при этом эталонное напряжение больше значения первого порогового напряжения.

Пример 19 может содержать один или более считываемых компьютером носителей из любого примера 14-16, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

Пример 20 может содержать устройство, выполненное для обновления значения напряжения ячейки памяти, это устройство содержит: средство для обновления первого значения напряжения первой ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, соответственно обладающих значением напряжения, установленным равным первому пороговому напряжению или второму пороговому напряжению, и при этом средство обновления содержит средство для сравнения первого значения напряжение первой ячейки памяти с эталонным напряжением; средство для определения, после обновления с помощью средства для обновления, одной или более ячеек памяти во множестве ячеек памяти, которые порождают ошибку при чтении соответствующих значений напряжения одной или более ячеек памяти; средство для сравнения количества из одной или более ячеек памяти со значением порога ошибок; и средство для обновления, если количество из одной или более ячеек памяти меньше значения порога ошибок, второго значения напряжения второй ячейки памяти в перекрестной энергонезависимой памяти, что делают путем повторной записи второго порогового напряжение во вторую ячейку памяти без изменения первого значения напряжения первой ячейки памяти.

Пример 21 может содержать устройство из примера 20, дополнительно содержащее следующее: средство для обновления, если количество из одной или более ячеек памяти больше значения порога ошибок, первого значения напряжения первой ячейки памяти, что делают путем повторной записи первого порогового напряжения в первую ячейку памяти.

Пример 22 может содержать устройство из примеров 20 или 21, при этом первое пороговое напряжение меньше второго порогового напряжения.

Пример 23 может содержать устройство из примеров 20 или 21, при этом эталонное напряжение больше значения первого порогового напряжения.

Пример 24 может содержать устройство из примеров 20 или 21, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

Хотя здесь описаны и проиллюстрированы некоторые варианты осуществления изобретения, этот документ предназначен для охвата любой адаптации или изменения рассмотренных вариантов осуществления изобретения. Следовательно, очевидно, что описанные здесь варианты осуществления изобретения ограничены только формулой изобретения.

Когда в описании говорится об «одном» или «первом» элементе или его эквиваленте, такое описание содержит одни или более таких элементов, при этом не требуется, но и не исключается наличие двух или более таких элементов. Более того, порядковые указатели (например, первый, второй или третий) для идентифицированных элементов используют для различения этих элементов, а не указания требуемого или ограниченного количества этих элементов, и такие указатели не подразумевают конкретное положение или порядок таких элементов, если не оговорено обратное.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И ВЕДУЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2348992C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| СПОСОБ УПРАВЛЕНИЯ ТЕХНИЧЕСКИМ РЕСУРСОМ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2012 |

|

RU2600525C2 |

| КОНТРОЛЬНЫЕ ТОЧКИ ДЛЯ ФАЙЛОВОЙ СИСТЕМЫ | 2011 |

|

RU2554847C2 |

| СПОСОБЫ СОХРАНЕНИЯ ДАННЫХ В ЭНЕРГОНЕЗАВИСИМЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВАХ | 2003 |

|

RU2278426C2 |

| Декодер контроллера твердотельного накопителя информации | 2021 |

|

RU2769562C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ПАМЯТЬ С РАЗДЕЛЕНИЕМ РАЗРЯДНЫХ ШИН ЗАПИСИ И ЧТЕНИЯ | 2011 |

|

RU2533308C2 |

| УСТРОЙСТВО, СИСТЕМА И СПОСОБ УЛУЧШЕНИЯ КОРРЕКЦИИ ЗАДАВАЕМЫМ АППАРАТУРОЙ АЛГОРИТМОМ | 2014 |

|

RU2580404C2 |

| КОРРЕКТНОСТЬ БЕЗ ЗАВИСИМОСТИ ОТ УПОРЯДОЧЕННОСТИ | 2010 |

|

RU2560786C2 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ | 2014 |

|

RU2643499C2 |

Группа изобретений относится к запоминающим устройствам и может быть использована для обновления ячеек памяти. Техническим результатом является повышение надежности перекрестной энергонезависимой памяти. Контроллер памяти для обновления значения напряжения ячейки памяти содержит логическую схему чтения, выполненную для чтения значения напряжения ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, при этом во множестве ячеек памяти значения напряжения соответственно установлены равными первому пороговому напряжению или второму пороговому напряжению; и логическую схему записи, соединенную с логической схемой чтения и выполненную для обновления значения напряжения первой одной или более ячеек из множества ячеек памяти, которое установлено равным второму пороговому напряжению, без изменения значения напряжения второй одной или более ячеек из множества ячеек памяти, которое установлено равным первому пороговому напряжению. 3 н. и 14 з.п. ф-лы, 6 ил.

1. Контроллер памяти для обновления значения напряжения ячейки памяти, этот контроллер памяти содержит:

логическую схему чтения, выполненную для чтения значения напряжения ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, при этом во множестве ячеек памяти значения напряжения соответственно установлены равными первому пороговому напряжению или второму пороговому напряжению; и логическую схему записи, соединенную с логической схемой чтения и выполненную для обновления значения напряжения первой одной или более ячеек из множества ячеек памяти, которое установлено равным второму пороговому напряжению, без изменения значения напряжения второй одной или более ячеек из множества ячеек памяти, которое установлено равным первому пороговому напряжению, при этом

логическая схема записи дополнительно выполнена для следующего: осуществляют операцию записи, в ответ на определение с помощью логической схемы исправления ошибок, что количество третьих одной или более ячеек памяти из множества ячеек памяти превышает порог ошибок, повторно устанавливают соответствующие значения напряжения каждой ячейки памяти в третьих одной или более ячейках памяти равными первому пороговому напряжению, если значение напряжения ячейки памяти установлено равным первому пороговому напряжению; и

осуществляют операцию записи в ответ на определение с помощью логической схемы исправления ошибок, с целью повторной установки соответствующих значений напряжения каждой ячейки памяти в третьих одной или более ячейках памяти равными второму пороговому напряжению, если значение напряжения ячейки памяти установлено равным второму пороговому напряжению.

2. Контроллер памяти по п. 1, при этом второе пороговое напряжение больше первого порогового напряжения.

3. Контроллер памяти по п. 1, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

4. Контроллер памяти по п. 1, при этом логическая схема записи выполнена для осуществления операции записи с целью повторной установки значения напряжения каждой ячейки памяти из первой одной или более ячеек из множества ячеек памяти равным второму пороговому напряжению для обновления значения напряжения первой одной или более ячеек из множества ячеек памяти.

5. Контроллер памяти по п. 1, при этом логическая схема чтения выполнена для обновления значения напряжения второй одной или более ячеек из множества ячеек памяти, что делают путем сравнения значения напряжения каждой ячейки памяти во второй одной или более ячейках из множества ячеек памяти с эталонным напряжением.

6. Контроллер памяти по п. 5, при этом эталонное напряжение больше значения первого порогового напряжения и меньше значения второго порогового напряжения.

7. Контроллер памяти по п. 1, дополнительно содержащий логическую схему исправления ошибок, соединенную с логической схемой чтения и логической схемой записи, логическая схема исправления ошибок выполнена для следующего: идентифицируют третью одну или более ячеек памяти из множества ячеек памяти, которые порождают ошибку при чтении значения напряжения третьей одной или более ячеек памяти с помощью логической схемы чтения; и

определяют, превышает ли порог ошибок количество третьих одной или более ячеек памяти из множества ячеек памяти.

8. Способ обновления значения напряжения ячейки памяти, включающий в себя следующее:

обновляют, с помощью контроллера памяти, первое значение напряжения первой ячейки памяти в перекрестной энергонезависимой памяти, соответственно содержащей множество ячеек памяти, обладающих значением напряжения, установленным равным первому пороговому напряжению или второму пороговому напряжению, первое значение напряжение первой ячейки устанавливают равным первому пороговому напряжению и при этом обновление включает в себя сравнение первого значения напряжение первой ячейки памяти с эталонным напряжением; определяют, с помощью контроллера памяти и после обновления, одну или более ячеек памяти во множестве ячеек памяти, которые порождают ошибку при чтении соответствующих значений напряжения одной или более ячеек памяти;

сравнивают, с помощью контроллера памяти, некоторое количество из одной или более ячеек памяти со значением порога ошибок; и

обновляют, с помощью контроллера памяти, если количество из одной или более ячеек памяти меньше значения порога ошибок, второе значение напряжения второй ячейки памяти в перекрестной энергонезависимой памяти, что делают путем повторной записи второго порогового напряжение во вторую ячейку памяти без изменения первого значения напряжения первой ячейки памяти.

9. Способ по п. 8, дополнительно включающий в себя следующее:

обновляют, с помощью контроллера памяти, если количество из одной или более ячеек памяти больше значения порога ошибок, первое значение напряжения первой ячейки памяти, что делают путем повторной записи первого порогового напряжения в первую ячейку памяти.

10. Способ по п. 8, в котором первое пороговое напряжение меньше второго порогового напряжения.

11. Способ по п. 8, в котором эталонное напряжение больше значения первого порогового напряжения.

12. Способ по п. 8, в котором перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

13. Один или более считываемых компьютером носителей, содержащих команды по обновлению значения напряжения ячейки памяти, эти команды таковы, что выполнение команд с помощью вычислительного устройства приводит к тому, что с помощью контроллера памяти вычислительного устройства:

обновляют первое значение напряжения первой ячейки памяти в перекрестной энергонезависимой памяти, содержащей множество ячеек памяти, до первого порогового напряжения или второго порогового напряжения, при этом обновление включает в себя сравнение первого значения напряжения первой ячейки памяти с эталонным напряжением;

обновляют второе значение напряжения второй ячейки памяти в перекрестной энергонезависимой памяти, что делают путем повторной записи второго порогового напряжения во вторую ячейку памяти;

обновляют, если определенное количество ошибок одной или более ячеек памяти превышает значение порога ошибок, соответствующее значению напряжения одной или более ячеек памяти, при этом обновление соответствующего значения напряжения одной или более ячеек памяти включает в себя следующее:

повторно записывают первое пороговое напряжение в первое подмножество ячеек памяти в этих одной или более ячейках памяти, в которых установлено первое пороговое напряжение; и

повторно записывают второе пороговое напряжение во второе подмножество ячеек памяти в этих одной или более ячейках памяти, в которых установлено второе пороговое напряжение.

14. Один или более считываемых компьютером носителей по п. 13, при этом команды дополнительно выполнены так, чтобы в результате их работы с помощью контроллера памяти:

определяют, после обновления первого значения напряжения и обновления второго значения напряжения, одну или более ячеек памяти во множестве ячеек памяти, которые порождают ошибку при чтении соответствующего значения напряжения упомянутых одной или более ячеек памяти; сравнивают, с помощью контроллера памяти, количество этих одной или более ячеек памяти со значением порога ошибок; и

обновляют, с помощью контроллера памяти, если количество этих одной или более ячеек памяти больше значения порога ошибок, соответствующее значение напряжения этих одной или более ячеек памяти.

15. Один или более считываемых компьютером носителей по п. 13, при этом значение первого порогового напряжения меньше значения второго порогового напряжения.

16. Один или более считываемых компьютером носителей по п. 13, при этом эталонное напряжение больше значения первого порогового напряжения.

17. Один или более считываемых компьютером носителей по п. 13, при этом перекрестная энергонезависимая память является памятью (РСМ) на фазовых переходах.

| EP 1927990 A2, 04.06.2008 | |||

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| УНИВЕРСАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ С СИСТЕМАМИ, ИСПОЛЬЗУЮЩИМИ ЭТОТ ЭЛЕМЕНТ, СПОСОБ И УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ, ЗАПИСИ И ПРОГРАММИРОВАНИЯ УНИВЕРСАЛЬНОГО ЭЛЕМЕНТА ПАМЯТИ | 2000 |

|

RU2216054C2 |

Авторы

Даты

2018-02-07—Публикация

2014-08-26—Подача