ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

[0001] По данной заявке испрашивается приоритет в соответствии с Предварительной Патентной Заявкой США № 61/359155, озаглавленной “Non-Volatile Memory with Split Write and Read Bitlines” (Энергонезависимая память с разделением разрядных шин записи и чтения), поданной 28 Июня 2010 г.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Настоящее раскрытие в целом относится к энергонезависимой памяти (NVM). Более конкретно, настоящее изобретение относится к повышению производительности одноразрядных ячеек энергонезависимой памяти посредством разделения разрядных шин.

УРОВЕНЬ ТЕХНИКИ

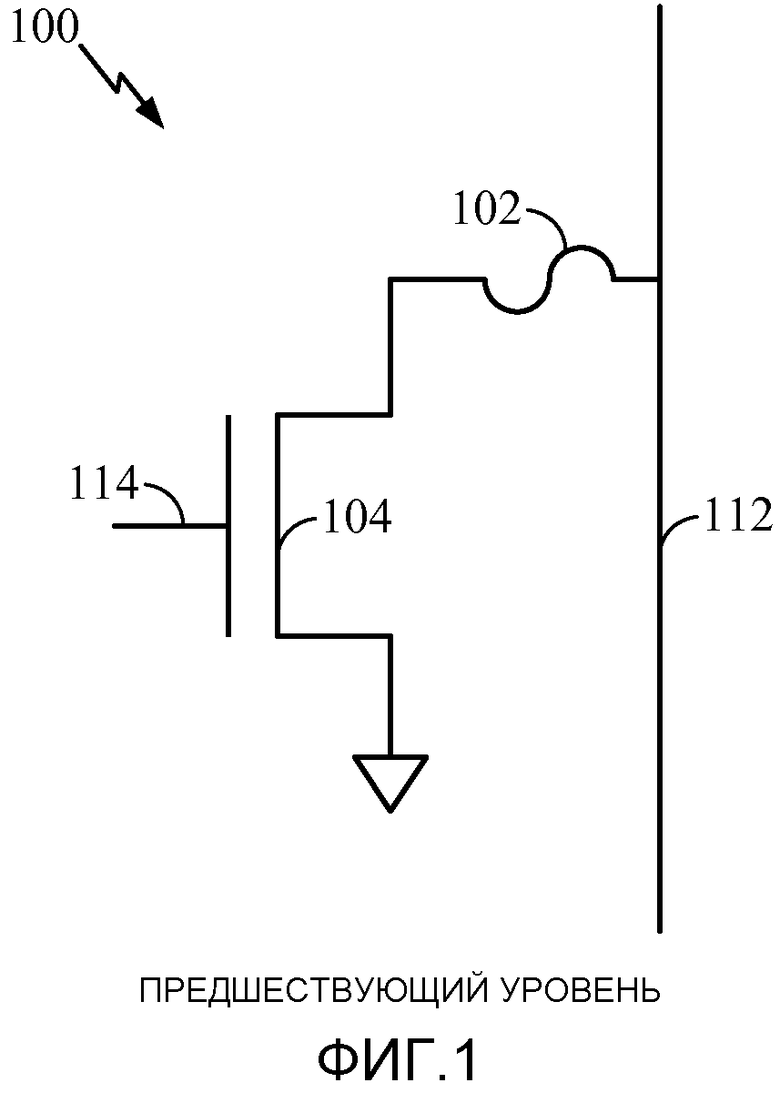

[0003] Одноразрядные ячейки энергонезависимой памяти (NVM), такие как одноразрядные ячейки с электронной перемычкой (eFUSE), имеют единственную разрядную шину для операций чтения и записи в одноразрядную ячейку и единственный транзистор доступа для операций чтения и записи. Однако операции чтения и записи имеют разные рабочие характеристики, что приводит в результате к конфликтам при проектировании одноразрядной ячейки NVM. Традиционно используемая одноразрядная ячейка NVM будет описана со ссылкой на ФИГ. 1 ниже.

[0004] ФИГ. 1 представляет собой принципиальную схему, иллюстрирующую одноразрядную ячейку общепринятой энергонезависимой памяти. Одноразрядная ячейка 100 NVM включает в себя плавкую перемычку 102 и транзистор 104 доступа. Плавкая перемычка 102 соединена с разрядной шиной 112 и транзистором 104 доступа. Затвор транзистора 104 доступа соединен с числовой шиной 114.

[0005] Операции записи в одноразрядных ячейках NVM включают в себя большие токи, которыми наилучшим образом оперируют посредством разрядных шин с низким сопротивлением. Дополнительно, транзистор доступа для операции записи занимает большую площадь кристалла, чтобы оперировать большими токами. Большие разрядные шины с низким сопротивлением имеют большую емкость. Например, некоторые традиционные разрядные шины имеют емкости, равные нескольким пикофарадам.

[0006] Операции чтения в одноразрядных ячейках NVM включают в себя малые токи считывания, которыми наилучшим образом оперируют посредством разрядных шин с низкой емкостью. Таким образом, возникает конфликт при проектировании, когда проектируют одноразрядную ячейку NVM для операций чтения и записи. Высокая емкость разрядных шин для операций записи приводит в результате к низким скоростям чтения и высоким средним и импульсным токам чтения. В результате одноразрядной ячейки NVM, совместно использующей единственную разрядную шину для операций чтения и записи, одноразрядную ячейку NVM невозможно сконструировать для операции как с высоким, так и низким напряжением. Дополнительно, действующие множественные напряжения (напряжение записи и напряжение чтения) на единственной разрядной шине одноразрядной ячейки NVM увеличивают сложность периферийной схемы, соединенной с одноразрядной ячейкой NVM.

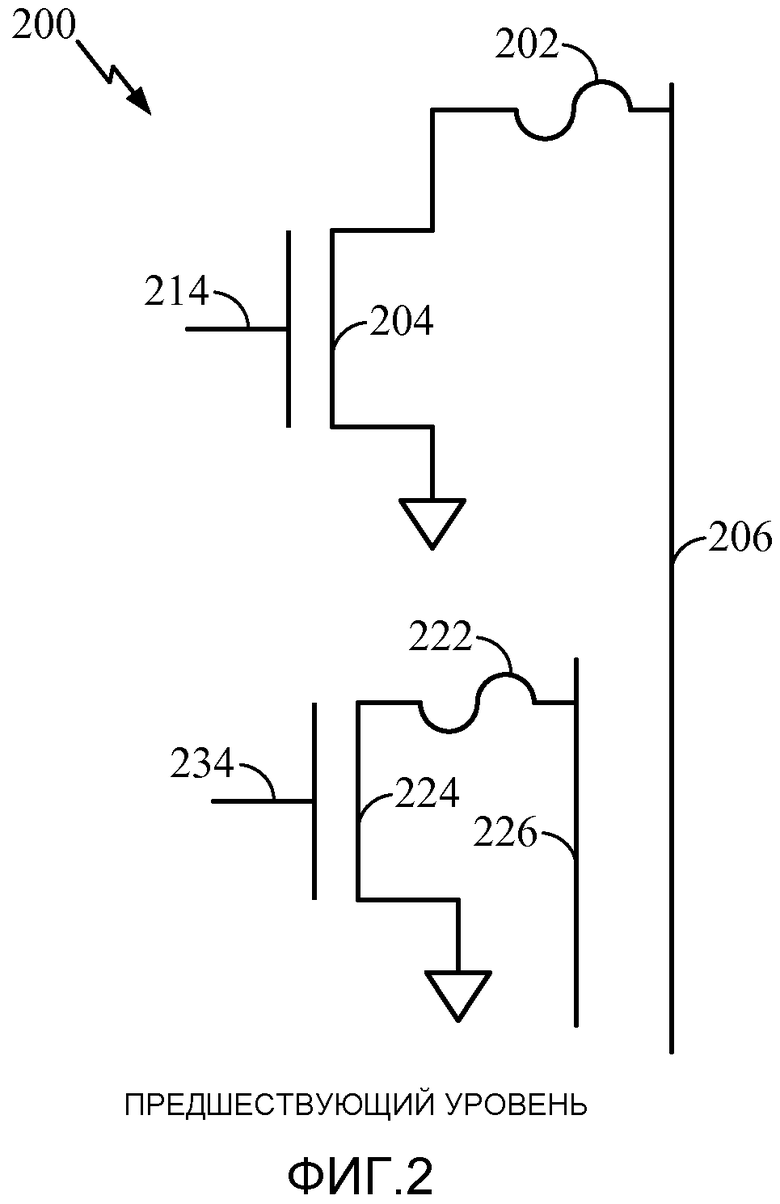

[0007] Альтернативные конструкции для одноразрядных ячеек NVM включают в себя дифференциальную компоновку. ФИГ. 2 представляет собой принципиальную схему, иллюстрирующую общепринятую одноразрядную ячейку энергонезависимой памяти с дифференциальным считыванием. Одноразрядная ячейка 200 NVM включает в себя плавкую перемычку 202, соединенную с нечетной разрядной шиной 206, и плавкую перемычку 222, соединенную с четной разрядной шиной 226. Транзистор 204 доступа соединен с плавкой перемычкой 202 и управляется нечетной числовой шиной 214. Транзистор 224 доступа соединен с плавкой перемычкой 222 и управляется четной числовой шиной 234. Несмотря на то что дифференциальная конструкция может увеличить эффективность чтения, добавление второй разрядной шины увеличивает сопротивление разрядных шин, поскольку слои проводящей шины (например, металлические слои), имеющиеся на кристалле, совместно используются нечетной разрядной шиной 206 и четной разрядной шиной 226. Когда меньшее число слоев проводящей шины предназначено для разрядной шины, сопротивление разрядной шины возрастает.

[0008] Таким образом, существует потребность в более надежной и более производительной одноразрядной ячейке энергонезависимой памяти.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0009] В соответствии с одним вариантом осуществления, одноразрядная ячейка энергонезависимой памяти (NVM) включает в себя первый элемент NVM для одноразовой записи, соединенный с разрядной шиной записи. Одноразрядная ячейка также включает в себя первый транзистор доступа для записи, соединяющий первый элемент NVM для одноразовой записи с заземлением. Затвор первого транзистора доступа для записи соединен с числовой шиной записи. Одноразрядная ячейка также включает в себя первый транзистор доступа для чтения, соединяющий первый элемент NVM для одноразовой записи с разрядной шиной чтения. Затвор первого транзистора доступа для чтения соединен с числовой шиной чтения.

[0010] В соответствии с еще одним вариантом осуществления, способ чтения с элемента энергонезависимой памяти (NVM) для одноразовой записи включает в себя смещение разрядной шины записи, соединенной с элементом NVM для одноразовой записи, до нуля. Способ также включает в себя подачу высокого сигнала на числовую шину чтения для включения транзистора доступа для чтения, соединяющего элемент NVM для одноразовой записи с разрядной шиной чтения. Способ дополнительно включает в себя считывание тока через элемент NVM для одноразовой записи, чтобы определить состояние элемента NVM для одноразовой записи.

[0011] В соответствии с дополнительным вариантом осуществления, способ записи на элемент энергонезависимой памяти (NVM) для одноразовой записи включает подачу напряжения записи на разрядную шину записи, соединенную с элементом NVM для одноразовой записи. Способ также включает подачу высокого сигнала на числовую шину записи для включения транзистора доступа для записи, вызывая прохождение тока через элемент NVM для одноразовой записи.

[0012] В соответствии с еще одним другим вариантом осуществления, устройство включает в себя элемент энергонезависимой памяти (NVM) для одноразовой записи. Устройство также включает в себя средство для записи на элемент NVM для одноразовой записи, соединенное с элементом NVM для одноразовой записи. Устройство дополнительно включает в себя транзистор записи, соединяющий элемент NVM для одноразовой записи с заземлением. Затвор транзистора записи соединен с числовой шиной записи. Устройство также включает в себя средство для чтения с элемента NVM для одноразовой записи. Устройство дополнительно включает транзистор чтения, соединяющий элемент NVM для одноразовой записи со средством для чтения. Затвор транзистора чтения соединен с числовой шиной чтения.

[0013] Данное обозначает, достаточно широко, признаки и технические преимущества настоящего раскрытия для того, чтобы подробное описание, которое следует, могло быть лучше понято. Дополнительные признаки и преимущества раскрытия будут описаны ниже. Специалисты в данной области техники должны оценить, что данное раскрытие может с легкостью использоваться в качестве основы для модификации или конструирования других структур для осуществления таких же целей настоящего раскрытия. Специалисты в данной области техники также должны осознать, что такие эквивалентные конструкции не выходят за пределы идей раскрытия, как изложено в прилагаемой формуле изобретения. Новые признаки, которые, как полагают, являются отличительными для раскрытия, как в отношении организации и способа операции, вместе с дополнительными целями и преимуществами, будут более понятными из следующего описания, при рассмотрении в связи с сопроводительными чертежами. Должно быть очевидным, однако, что каждая из фигур предоставлена только с целью иллюстрации и описания и не предназначена для определения пределов настоящего раскрытия.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0014] Для более полного понимания настоящего раскрытия, здесь приводится ссылка на следующее описание, взятое в сочетании с сопроводительными чертежами.

[0015] ФИГ. 1 представляет собой принципиальную схему, иллюстрирующую традиционную одноразрядную ячейку энергонезависимой памяти.

[0016] ФИГ. 2 представляет собой принципиальную схему, иллюстрирующую традиционную одноразрядную ячейку энергонезависимой памяти с дифференциальным считыванием.

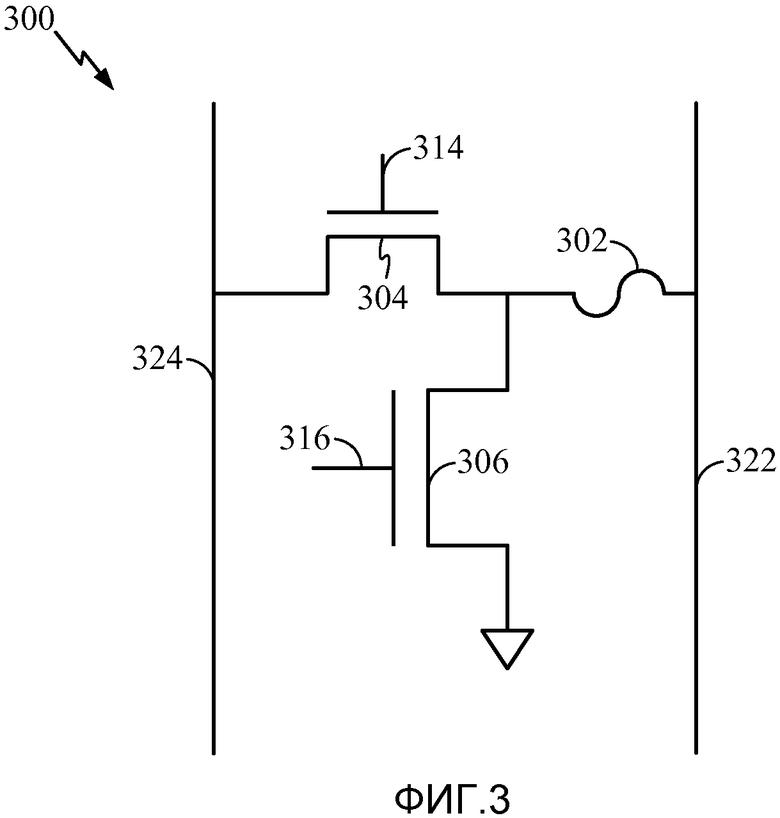

[0017] ФИГ. 3 представляет собой принципиальную схему, иллюстрирующую примерную одноразрядную ячейку энергонезависимой памяти в соответствии с одним вариантом осуществления.

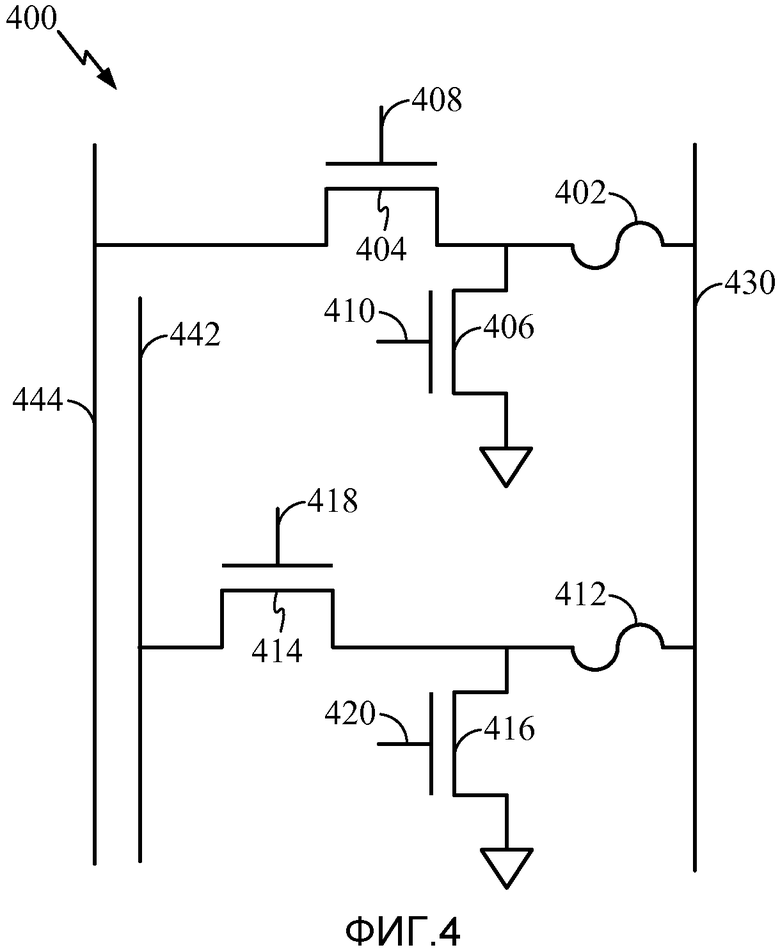

[0018] ФИГ. 4 представляет собой принципиальную схему, иллюстрирующую примерную одноразрядную ячейку энергонезависимой памяти с дифференциальным считыванием в соответствии с одним вариантом осуществления.

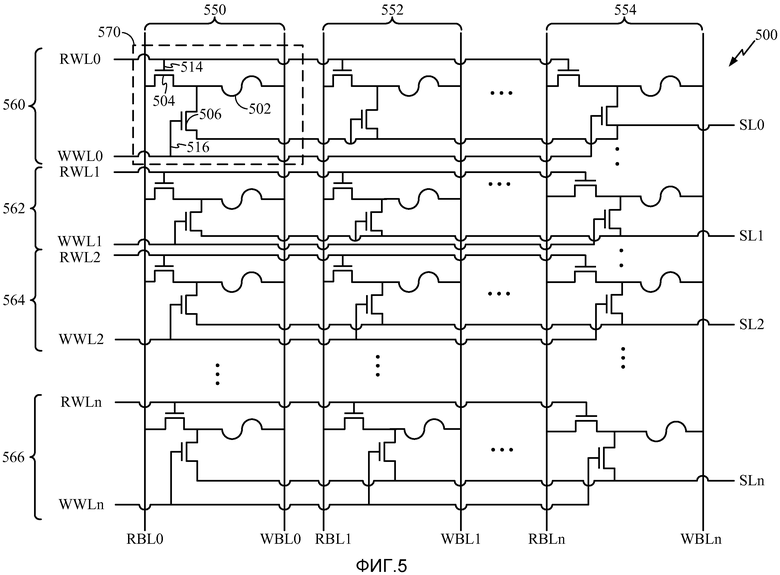

[0019] ФИГ. 5 представляет собой принципиальную схему, иллюстрирующую примерную матрицу одноразрядных ячеек энергонезависимой памяти в соответствии с одним вариантом осуществления.

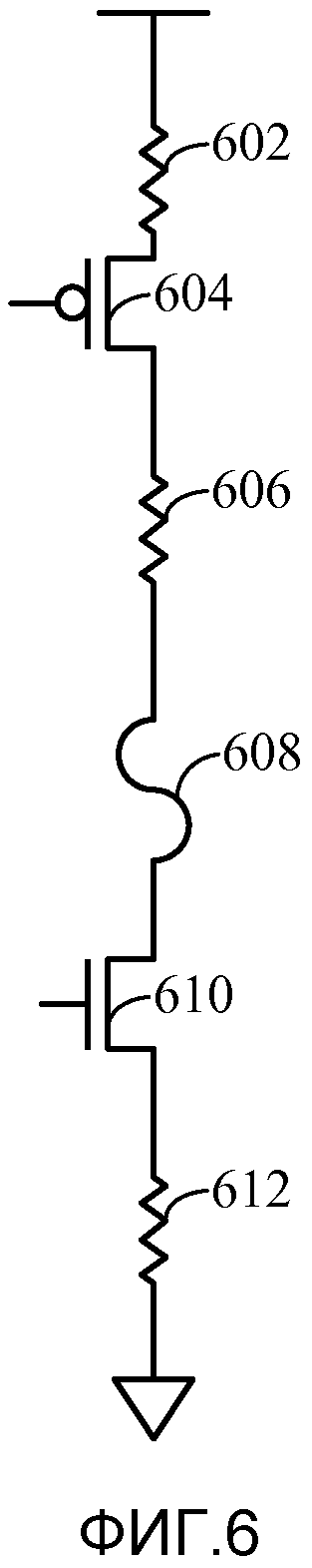

[0020] ФИГ. 6 представляет собой принципиальную схему, иллюстрирующую схему, эквивалентную примерной одноразрядной ячейке энергонезависимой памяти в соответствии с одним вариантом осуществления.

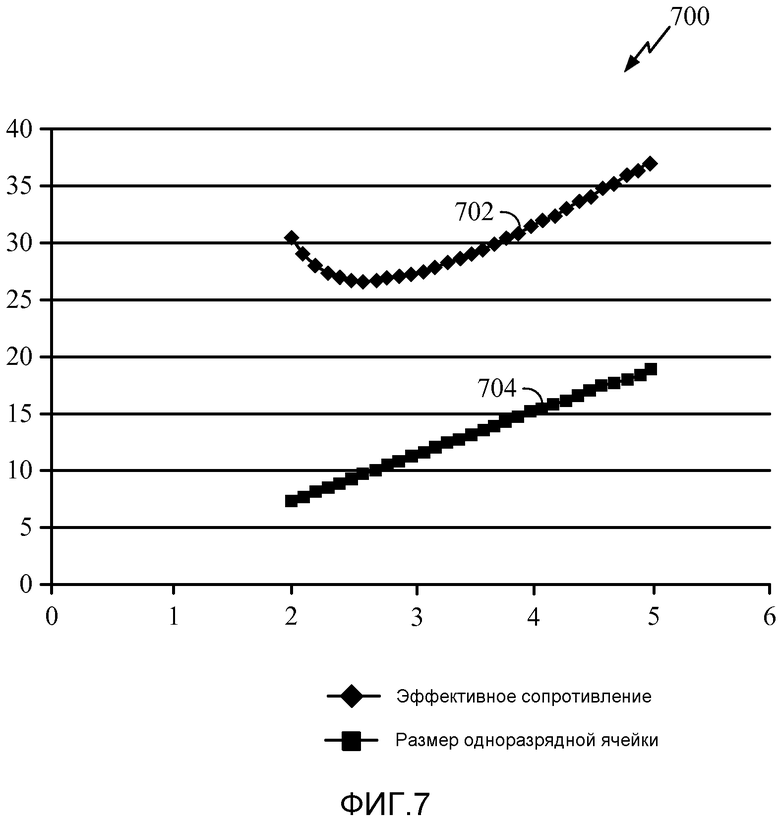

[0021] ФИГ. 7 представляет собой график, иллюстрирующий сопротивление одноразрядной ячейки как функцию высоты одноразрядной ячейки в соответствии с одним вариантом осуществления.

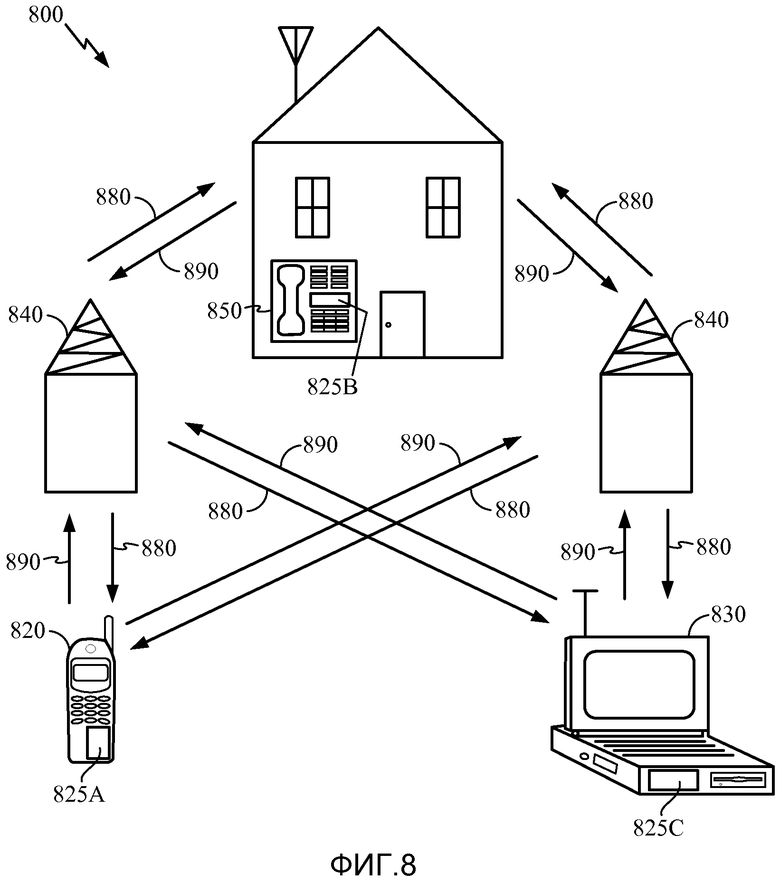

[0022] ФИГ. 8 представляет собой блок-схему, показывающую примерную систему беспроводной связи, в которой вариант осуществления раскрытия может быть предпочтительно использован.

[0023] ФИГ. 9 представляет собой блок-схему, иллюстрирующую конструкцию рабочей станции, применяемую для схемы, разводки, и логического проектирования полупроводникового компонента в соответствии с одним вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

[0024] Одноразрядные ячейки энергонезависимой памяти (NVM) с раздельными физическими разрядными шинами для операций чтения и записи предлагают улучшенные рабочие характеристики чтения и записи по сравнению с одноразрядными ячейками NVM с единственной разрядной шиной. Каждая из разрядных шин в одноразрядной ячейке NVM сконструирована для операций чтения или записи. Таким образом, предоставлена разрядная шина с низкой емкостью в процессе операций чтения, и предоставлено низкое сопротивление в процессе операций записи.

[0025] ФИГ. 3 представляет собой принципиальную схему, иллюстрирующую примерную одноразрядную ячейку энергонезависимой памяти в соответствии с одним вариантом осуществления. Одноразрядная ячейка 300 NVM включает в себя элемент 302 памяти, соединенный с разрядной шиной 322 записи. Элемент 302 памяти может представлять собой, например, плавкую перемычку, антиперемычку, электронную перемычку (eFUSE) или магнитный туннельный переход (MTJ). В соответствии с одним вариантом осуществления, элемент 302 памяти представляет собой устройство для одноразовой записи, которое записывает, по большей мере, однократно на одноразрядную ячейку. Транзистор 306 доступа для записи соединен с элементом 302 памяти и заземлением. Затвор транзистора 306 доступа для записи соединен с числовой шиной 316 записи. Транзистор 304 доступа для чтения соединен с элементом 302 памяти и с разрядной шиной 324 чтения. Затвор транзистора 304 доступа для чтения соединен с числовой шиной 314 чтения.

[0026] В соответствии с одним вариантом осуществления, разрядная шина 324 чтения представляет собой разрядную шину с низкой емкостью, сконструированную для высокоэффективных операций чтения. В соответствии с одним вариантом осуществления, разрядная шина 322 записи представляет собой разрядную шину с низким сопротивлением, сконструированную для операций записи с высоким током. Сопротивление разрядной шины 322 записи может быть снижено посредством добавления металлических слоев к разрядной шине 322 записи.

[0027] Операция записи может осуществляться на элемент 302 памяти посредством изоляции разрядной шины 324 чтения и установления низкого сигнала на числовой шине 314 чтения. Напряжение записи подается на разрядную шину 322 записи, и высокий сигнал подается на числовую шину 316 записи. В соответствии с одним вариантом осуществления, напряжение при записи составляет 1,8 В, и высокий сигнал составляет 1,0 В. Транзистор 306 доступа для записи включается, чтобы обеспечить прохождение тока через элемент 302 памяти от разрядной шины 322 записи к заземлению, соединенному с транзистором 306 доступа для записи. В соответствии с одним вариантом осуществления, элемент 302 памяти представляет собой плавкую перемычку, и ток через элемент 302 памяти разрывает плавкую перемычку, приводя к обрыву в цепи на элементе 302 памяти во время операций чтения.

[0028] Операция чтения может осуществляться на элементе 302 памяти посредством установления низкого сигнала на числовой шине 316 записи. Разрядная шина 322 записи смещается до нуля посредством устройства управления столбцом (не показано), и высокий сигнал подается к числовой шине 314 чтения. В соответствии с одним вариантом осуществления, высокий сигнал составляет 1,0 В. Транзистор 304 доступа для чтения включается для проведения тока через элемент 302 памяти от разрядной шины 322 записи к разрядной шине 324 чтения. Величина тока через элемент 302 памяти может быть измерена, чтобы определить состояние элемента 302 памяти. Например, если элемент 302 памяти представляет собой плавкую перемычку и ток не проходит через элемент 302 памяти, то элемент памяти может представлять собой "0". Альтернативно, если элемент 302 памяти представляет собой плавкую перемычку и ток проходит через элемент 302 памяти, то элемент памяти может представлять собой "1". В соответствии с одним вариантом осуществления, ток через элемент 302 памяти считывают посредством подачи напряжения на разрядную шину 324 чтения. Если напряжение разрядной шины 324 чтения значительно возрастает, то элемент 302 памяти представляет собой обрыв в цепи. Если напряжение разрядной шины 324 чтения существенно не возрастает, то элемент 302 памяти представляет собой цепь короткого замыкания.

[0029] Примерная конструкция одноразрядной ячейки NVM ФИГ. 3 улучшает эффективность чтения посредством размещения низкоемкостной разрядной шины 324 чтения в одноразрядной ячейке 300 NVM. Дополнительная разрядная шина 324 чтения и транзистор 304 доступа для чтения занимают дополнительную площадь кристалла, однако, площадь кристалла, занимаемая транзистором 304 доступа для чтения, существенно меньше, чем площадь кристалла, занимаемая транзистором 306 доступа для записи. Таким образом, общая площадь кристалла, занимаемая примерной конструкцией одноразрядной ячейки 300 NVM ФИГ. 3, существенно не увеличивается.

[0030] В соответствии с еще одним вариантом осуществления, разрядную шину чтения добавляют к конструкции дифференциальной одноразрядной ячейки NVM. ФИГ. 4 представляет собой принципиальную схему, иллюстрирующую примерную одноразрядную ячейку энергонезависимой памяти с дифференциальным считыванием в соответствии с одним вариантом осуществления. Дифференциальная одноразрядная ячейка 400 NVM включает в себя разрядную шину 430 записи. Разрядная шина 430 записи соединена с и совместно используется элементами 402, 412 памяти. Элемент 402 памяти соединен с транзистором 404 доступа для чтения и транзистором 406 доступа для записи. Транзистор 406 доступа для записи соединяет элемент 402 памяти с заземлением и управляется четной числовой шиной 410 записи. Транзистор 404 доступа для чтения соединяет элемент 402 памяти с четной разрядной шиной 444 чтения и управляется четной числовой шиной 408 чтения.

[0031] Элемент 412 памяти соединен с транзистором 416 доступа для записи и транзистором 414 доступа для чтения. Транзистор 416 доступа для записи соединяет элемент 412 памяти с заземлением и управляется нечетной числовой шиной 420 записи. Транзистор 414 доступа для чтения соединяет элемент 412 памяти с нечетной разрядной шиной 442 чтения и управляется нечетной числовой шиной 418 чтения.

[0032] Во время операции чтения в дифференциальной одноразрядной ячейке NVM, считанный ток через элемент 412 памяти можно сравнить со считанным током через элемент 402 памяти. Например, операционный усилитель (не показан) может сравнивать напряжение, присутствующее на четной разрядной шине 444 чтения и нечетной разрядной шине 442 чтения.

[0033] Дифференциальная одноразрядная ячейка 400 NVM включает в себя единственную разрядную шину 430 записи, которая имеет низкое сопротивление. Сопротивление единственной разрядной шины 430 записи минимизируется или уменьшается посредством понижающих ресурсов (например, металлических линий), совместно используемых между разрядной шиной 430 записи и другими разрядными шинами записи (не показано). Разрядные шины 442, 444 чтения сконструированы так, чтобы иметь низкую емкость для улучшения операций чтения без оказания воздействия на способность одноразрядной ячейки 400 NVM обрабатывать операции записи с высоким током.

[0034] ФИГ. 5 представляет собой принципиальную схему, иллюстрирующую примерную матрицу одноразрядных ячеек энергонезависимой памяти в соответствии с одним вариантом осуществления. Матрица 500 включает ряд одноразрядных ячеек 570. Каждая из одноразрядных ячеек, такая как одноразрядная ячейка 570, включает в себя элемент 502 памяти, соединенный с транзистором 504 доступа для чтения и транзистором 506 доступа для записи. Элемент 502 памяти одноразрядной ячейки 570 соединен с разрядной шиной записи, WBL0. Затвор 516 транзистора 506 доступа для записи соединен с числовой шиной записи, WWLO, и затвор 514 транзистора 504 доступа для чтения соединен с числовой шиной чтения, RWLO. Транзистор 504 доступа для чтения соединяет элемент 502 памяти с разрядной шиной чтения, RBL0. Транзистор 506 доступа для записи соединяет элемент 502 памяти с истоковой шиной, SL0, которая может быть, например, соединена с заземлением.

[0035] Одноразрядная ячейка 570 повторяется вдоль столбцов 550, 552, 554, соответствующих разрядным шинам RBL0 и WBL0, RBL1 и WBL1, и RBLn и WBLn. Несмотря на то что только три столбца показаны в матрице 500, могут присутствовать дополнительные столбцы. Одноразрядная ячейка 570 также повторяется вдоль рядов 560, 562, 564, 566, соответствующих числовым шинам RWLO и WWLO, RWLl и WWLl, RWL2 и WWL2, и RWLn и WWLn. Несмотря на то что только четыре ряда показаны в матрице 500, могут присутствовать дополнительные ряды.

[0036] Одноразрядные ячейки энергонезависимой памяти (NVM) с раздельными путями записи и чтения обеспечивают лучшую эффективность операции чтения, снижают энергопотребление операции чтения и делают более быстрой скорость операции чтения. Дополнительное отделение пути операции чтения с низким напряжением от пути операции записи с высоким напряжением существенно снижает сложность периферийной схемы, приводя в результате к уменьшению площади кристалла, занимаемой периферийной схемой.

[0037] Эффективность работы одноразрядных ячеек NVM может быть дополнительно улучшена посредством минимизации или снижения сопротивления посредством выбора неквадратной геометрии одноразрядной ячейки. ФИГ. 6 представляет собой принципиальную схему, иллюстрирующую схему, эквивалентную примерной одноразрядной ячейке NVM, в соответствии с одним вариантом осуществления. Сопротивление 602 представляет паразитное сопротивление на уровне кристалла, сопротивление 606 представляет сопротивление разрядной шины и сопротивление 612 представляет паразитное сопротивление истока. Транзистор 604 представляет транзистор выбора столбцов и транзистор 610 представляет программный транзистор. Элемент 608 памяти подсоединен между сопротивлением 606 разрядной шины и программным транзистором 610.

[0038] При выборе геометрии одноразрядной ячейки имеет место компромисс между высотой одноразрядной ячейки и шириной одноразрядной ячейки. Более высокая одноразрядная ячейка приводит к более низкому сопротивлению 610 программного транзистора, но более высокому сопротивлению 606 разрядной шины. Более короткая одноразрядная ячейка приводит к более высокому сопротивлению 610 программного транзистора, но более низкому сопротивлению 606 разрядной шины. Для данной ширины одноразрядной ячейки, эффективное сопротивление сопротивления 606 разрядной шины и сопротивление 610 программного транзистора задается выражением

Reff=n*Rm*y+Rds/(f*y),

где n равно числу рядов на разрядную шину, Rm является сопротивлением разрядной шины на единицу высоты, y является высотой одноразрядной ячейки, Rds является линейным сопротивлением программного транзистора и f число ветвей топологии внутри топологии одноразрядной ячейки.

[0039] ФИГ. 7 представляет собой график, иллюстрирующий сопротивление одноразрядной ячейки как функцию высоты одноразрядной ячейки в соответствии с одним вариантом осуществления. График 700 иллюстрирует на линии 702 эффективное сопротивление как функцию высоты одноразрядной ячейки. График 700 также иллюстрирует на линии 704 размер одноразрядной ячейки как функцию высоты одноразрядной ячейки. График 700 демонстрирует, что минимальное сопротивление не всегда достигается при минимальной высоте ячейки.

[0040] ФИГ. 8 представляет собой блок-схему, показывающую примерную систему беспроводной связи 800, в которой может быть предпочтительно использован вариант осуществления раскрытия. В целях иллюстрации, ФИГ. 8 показывает три удаленных блока 820, 830 и 850 и две базовые станции 840. Следует понимать, что системы беспроводной связи могут иметь намного больше удаленных блоков и базовых станций. Удаленные блоки 820, 830 и 850 включают интегральные схемы (ИС) 825A, 825C и 825B, которые включают в себя раскрытую энергонезависимую память. Следует понимать, что любое устройство, содержащее ИС, может также включать в себя одноразрядную ячейку энергонезависимой памяти, раскрытую здесь, включая базовые станции, коммутаторы и сетевое оборудование. ФИГ. 8 показывает сигналы прямой связи 880 от базовой станции 840 к удаленным блокам 820, 830 и 850 и сигналы обратной связи 890 от удаленных блоков 820, 830 и 850 к базовым станциям 840.

[0041] На ФИГ. 8, удаленный блок 820 показан в виде мобильного телефона, удаленный блок 830 показан в виде переносного компьютера, и удаленный блок 850 показан в виде удаленного блока с фиксированным положением в системе беспроводного абонентского доступа. Например, удаленные блоки могут представлять собой мобильные телефоны, портативные блоки систем персональной связи (PCS), портативные блоки данных, такие как карманные компьютеры, устройства с поддержкой GPS, навигационные устройства, телевизионные абонентские приставки, музыкальные проигрыватели, видеопроигрыватели, развлекательные блоки, блоки данных с фиксированным положением, такие как оборудование для снятия показаний измерительных приборов или любое другое устройство, которое сохраняет или воспроизводит данные или инструкции компьютера или любую их комбинацию. Несмотря на то что ФИГ. 8 иллюстрирует удаленные блоки в соответствии с идеями раскрытия, раскрытие не ограничено этими примерными иллюстрированными блоками. Варианты осуществления раскрытия могут подходящим образом использоваться в любом устройстве, которое включает в себя запоминающее устройство.

[0042] ФИГ. 9 представляет собой блок-схему, иллюстрирующую автоматизированное рабочее место проектировщика, используемое для создания схемы, топологии и логического проектирования полупроводникового компонента, такого как одноразрядная ячейка энергонезависимой памяти, как раскрыто выше. Автоматизированное рабочее место 900 проектировщика включает в себя жесткий диск 901, содержащий программное обеспечение операционной системы, файлы поддержки и программное обеспечение, такое как Cadence или OrCAD. Автоматизированное рабочее место 900 проектировщика также включает дисплей для облегчения проектирования схемы 910 или полупроводникового компонента 912, такого как энергонезависимая память. Носитель 904 данных предоставлен для материального сохранения проекта схемы 910 или полупроводникового компонента 912. Проект схемы 910 или полупроводникового компонента 912 могут сохраняться на носителе 904 данных в формате файла, таком как GDSII или GERBER. Носитель 904 данных может представлять собой CD-ROM, DVD, жесткий диск, флэш-память, или другое соответствующее устройство. Кроме того, автоматизированное рабочее место 900 проектировщика включает в себя приводное устройство 903 для приема ввода от или записи вывода на носитель 904 данных.

[0043] Данные, записанные на носителе 904 данных, могут задавать конфигурации логической схемы, данные рисунка масок для фотолитографии или данные рисунка масок для инструментов последовательной записи, таких как электронно-лучевая литография. Данные могут дополнительно включать в себя данные верификации проекта на логическом уровне, такие как временные диаграммы или сетевые схемы, ассоциированные с логическим моделированием. Предоставление данных на носителе 904 данных облегчает проектирование схемы 910 или полупроводникового компонента 912 посредством уменьшения числа процессов для проектирования полупроводниковых пластин.

[0044] Для программно-аппаратного и/или программного осуществления методологии могут быть реализованы с помощью модулей (например, методик, функций и т.д.), которые выполняют функции, описанные здесь. Любой машиночитаемый носитель, материально выполняющий инструкции, может применяться при осуществлении методологий, описанных здесь. Например, программные коды могут храниться в памяти и выполняться процессорным блоком. Память может осуществляться внутри процессорного блока или быть внешней по отношению к процессорному блоку. Как используется здесь, термин "память" относится к любому типу долговременной, кратковременной или другой памяти и не должен ограничиваться каким-либо конкретным типом памяти или рядом памяти, или типом носителя, на котором память хранится.

[0045] Если осуществление проводится в виде программно-аппаратного и/или программного обеспечения, функции могут сохраняться в виде одной или более инструкций или кода на машиночитаемом носителе. Примеры включают машиночитаемые носители, кодируемые с помощью структуры данных и машиночитаемые носители, кодируемые с помощью компьютерной программы. Машиночитаемые носители включают в себя физические запоминающие носители компьютера. Носитель данных может представлять собой любой доступный носитель, который может быть введен в компьютер. Посредством примера, а не ограничения, такие машиночитаемые носители могут включать RAM, ROM, EEPROM, CD-ROM или другой накопитель на оптических дисках, накопитель на магнитных дисках или другие устройства для магнитного запоминания или любой другой носитель, который может применяться для хранения желательного программного кода в виде инструкций или структур данных и который может быть введен в компьютер; диск (disk) и диск (disc), как используют здесь, включает в себя компактный диск (CD), лазерный диск, оптический диск, цифровой универсальный диск (DVD), флоппи-диск и диск блю-рэй, где диски (disks) обычно воспроизводят данные магнитно, в то время как диски (discs) воспроизводят данные оптически с помощью лазеров. Комбинации приведенного выше также должны быть включены в объем машиночитаемых носителей.

[0046] В дополнение к памяти на машиночитаемом носителе, инструкции и/или данные могут быть предоставлены в виде сигналов в средах передачи данных, включенных в аппаратуру связи. Например, аппаратура связи может включать в себя приемопередатчик, имеющий сигнал, указывающий на инструкции и данные. Инструкции и данные конфигурируют, чтобы заставить один или более процессоров выполнять функции, обозначенные в формуле изобретения.

[0047] Несмотря на то что были представлены конкретные схемы, специалисты в данной области техники смогут понять, что не все из раскрытых схем требуются для практической реализации раскрытия. Кроме того, некоторые хорошо известные схемы не были описаны, чтобы уделить основное внимание раскрытию. Аналогично, несмотря на то что описание относится к логическому "0" и логической "1" в некоторых местах, специалист в данной области оценит, что логические значения могут быть изменены, причем оставшаяся часть схемы регулируется соответственно, без оказания воздействия на действие настоящего изобретения.

[0048] Несмотря на то что раскрытие и его преимущества были описаны подробно, следует понимать, что разнообразные изменения, замены и модификации могут быть проделаны здесь без отступления от способа раскрытия, как определено прилагаемой формулой изобретения. Например, относительные термины, такие как "выше" и "ниже" применяют по отношению к подложке или электронному устройству. Конечно, если подложку или электронное устройство переворачивают, выше становится ниже, и наоборот. Дополнительно, при боковой ориентации, выше и ниже могут относиться к сторонам подложки или электронного устройства. Кроме того, объем притязаний настоящей заявки не предназначен для ограничений конкретными вариантами осуществления процесса, машины, изготовления, композиции вещества, средств, способов и стадий, описанных в описании. Так как рядовой специалист в области техники сможет легко оценить, исходя из раскрытия, процессы, машины, изготовление, композиции вещества, средства, способы или стадии, существующие в настоящее время или предстоящие для разработки позднее, которые реализуют, по существу, ту же функцию или достигают, по существу, такого же результата, соответствующие варианты осуществления, описанные здесь, могут использоваться в соответствии с настоящим раскрытием. Соответственно, подразумевают, что прилагаемая формула изобретения включает в свой объем притязаний такие процессы, машины, изготовление, композиции вещества, средства, способы или стадии.

Изобретение относится к вычислительной технике. Технический результат заключается в повышении производительности одноразрядных ячеек энергонезависимой памяти за счет разделения разрядных шин. Одноразрядная ячейка энергонезависимой памяти (NVM) содержит первый элемент NVM для одноразовой записи, непосредственно соединенный с разрядной шиной записи; первый транзистор доступа для записи, соединяющий первый элемент NVM для одноразовой записи с заземлением, причем затвор первого транзистора доступа для записи соединен с числовой шиной записи; и первый транзистор доступа для чтения, непосредственно соединенный с первым элементом NVM для одноразовой записи и непосредственно соединенный с разрядной шиной чтения, причем затвор первого транзистора доступа для чтения соединен с числовой шиной чтения. 4 н. и 14 з.п. ф-лы, 9 ил.

1. Одноразрядная ячейка энергонезависимой памяти (NVM), содержащая:

первый элемент NVM для одноразовой записи, непосредственно соединенный с разрядной шиной записи;

первый транзистор доступа для записи, соединяющий первый элемент NVM для одноразовой записи с заземлением, причем затвор первого транзистора доступа для записи соединен с числовой шиной записи; и

первый транзистор доступа для чтения, непосредственно соединенный с первым элементом NVM для одноразовой записи и непосредственно соединенный с разрядной шиной чтения, причем затвор первого транзистора доступа для чтения соединен с числовой шиной чтения.

2. Одноразрядная ячейка по п.1, в которой элемент NVM для одноразовой записи представляет собой по меньшей мере одно из плавкой перемычки, антиперемычки и магнитного туннельного перехода (MTJ).

3. Одноразрядная ячейка по п.1, дополнительно содержащая:

второй элемент NVM для одноразовой записи, соединенный с разрядной шиной записи;

второй транзистор доступа для записи, соединяющий второй элемент NVM для одноразовой записи с заземлением, причем затвор второго транзистора доступа для записи соединен с нечетной числовой шиной записи; и

второй транзистор доступа для чтения, соединяющий второй элемент NVM для одноразовой записи с нечетной разрядной шиной чтения, причем затвор второго транзистора доступа для чтения соединен с нечетной числовой шиной чтения,

при этом первый элемент NVM для одноразовой записи соединен с четной разрядной шиной чтения, и затвор первого транзистора доступа для чтения соединен с четной числовой шиной чтения.

4. Одноразрядная ячейка по п.1, в которой разрядная шина чтения является шиной с низкой емкостью, а разрядная шина записи является шиной с низким сопротивлением.

5. Одноразрядная ячейка по п.1, в которой одноразрядная ячейка занимает неквадратную площадь кристалла.

6. Одноразрядная ячейка по п.1, в которой одноразрядная ячейка встроена в матрицу памяти.

7. Одноразрядная ячейка по п.6, в которой матрица памяти встроена в мобильный телефон, телевизионную абонентскую приставку, музыкальный проигрыватель, видеопроигрыватель, развлекательный блок, навигационное устройство, компьютер, портативный блок систем персональной связи (PCS), портативный блок данных и/или блок данных с фиксированным положением.

8. Способ чтения с элемента энергонезависимой памяти (NVM) для одноразовой записи, причем упомянутый способ содержит этапы, на которых:

смещают разрядную шину записи, соединенную с по меньшей мере одним выбранным элементом NVM для одноразовой записи, до нуля;

подают высокий сигнал на числовую шину чтения для включения транзистора доступа для чтения, непосредственно соединенного с выбранным элементом NVM для одноразовой записи и непосредственно соединенного с разрядной шиной чтения;

устанавливают низкий сигнал на числовой шине записи транзистора доступа для записи, соединенного с выбранным элементом NVM для одноразовой записи; и

считывают ток через выбранный элемент NVM для одноразовой записи, чтобы определить состояние элемента NVM для одноразовой записи.

9. Способ по п.8, в котором смещение разрядной шины записи осуществляют посредством устройства управления столбцом.

10. Способ по п.8, дополнительно содержащий этап, на котором сравнивают считанный ток через элемент NVM для одноразовой записи со вторым считанным током через другой элемент NVM для одноразовой записи.

11. Способ по п.8, дополнительно содержащий этап, на котором встраивают элемент NVM для одноразовой записи в мобильный телефон, телевизионную абонентскую приставку, музыкальный проигрыватель, видеопроигрыватель, развлекательный блок, навигационное устройство, компьютер, портативный блок систем персональной связи (PCS), портативный блок данных и/или блок данных с фиксированным положением.

12. Способ записи на элемент энергонезависимой памяти (NVM) для одноразовой записи, причем упомянутый способ содержит этапы, на которых:

изолируют разрядную шину чтения, непосредственно соединенную с транзистором доступа для чтения;

подают низкий сигнал на числовую шину чтения для выключения транзистора доступа для чтения, непосредственно соединенного с по меньшей мере одним выбранным элементом NVM для одноразовой записи;

подают напряжение записи на разрядную шину записи, непосредственно соединенную с по меньшей мере одним выбранным элементом NVM для одноразовой записи; и

подают высокий сигнал на числовую шину записи для включения транзистора доступа записи, непосредственно соединенного с по меньшей мере одним выбранным элементом NVM для одноразовой записи, вызывая прохождение тока через выбранный элемент NVM для одноразовой записи.

13. Способ по п.12, дополнительно содержащий этап, на котором встраивают элемент NVM для одноразовой записи в мобильный телефон, телевизионную абонентскую приставку, музыкальный проигрыватель, видеопроигрыватель, развлекательный блок, навигационное устройство, компьютер, портативный блок систем персональной связи (PCS), портативный блок данных и/или блок данных с фиксированным положением.

14. Одноразрядная ячейка энергонезависимой памяти (NVM), содержащая:

элемент энергонезависимой памяти (NVM) для одноразовой записи;

средство для записи на элемент NVM для одноразовой записи, непосредственно соединенное с элементом NVM для одноразовой записи;

транзистор записи, соединяющий элемент NVM для одноразовой записи с заземлением, причем затвор транзистора записи соединен с числовой шиной записи;

средство для чтения с элемента NVM для одноразовой записи; и транзистор чтения, непосредственно соединенный с элементом NVM для одноразовой записи и непосредственно соединенный со средством для чтения, причем затвор транзистора чтения соединен с числовой шиной чтения.

15. Одноразрядная ячейка по п.14, в которой элемент NVM для одноразовой записи представляет собой по меньшей мере одно из плавкой перемычки, антиперемычки, электронной перемычки (eFUSE) и магнитного туннельного перехода (MTJ).

16. Одноразрядная ячейка по п.14, в которой средство для чтения имеет низкую емкость, а средство для записи имеет низкое сопротивление.

17. Одноразрядная ячейка по п.14, в которой элемент NVM для одноразовой записи встроен в матрицу памяти.

18. Одноразрядная ячейка по п.17, в которой матрица памяти встроена в мобильный телефон, телевизионную абонентскую приставку, музыкальный проигрыватель, видеопроигрыватель, развлекательный блок, навигационное устройство, компьютер, портативный блок систем персональной связи (PCS), портативный блок данных и/или блок данных с фиксированным положением.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 5949712 A1, 07.09.1999 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| УСОВЕРШЕНСТВОВАННОЕ МНОГОРАЗРЯДНОЕ МАГНИТНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ И СПОСОБЫ ЕГО ФУНКЦИОНИРОВАНИЯ И ПРОИЗВОДСТВА | 2005 |

|

RU2310928C2 |

Авторы

Даты

2014-11-20—Публикация

2011-06-28—Подача