Изобретение относится к области управления в реальном масштабе времени сложными объектами и быстротекущими процессами, которые не удается представить математической моделью в виде дифференциальных уравнений. Технический результат - повышение быстродействия управления при снижении аппаратной избыточности, в унификации структуры нечетких регуляторов при изменении количества параметров объекта управления.

Известен четкий логический регулятор для управления технологическими процессами [Патент RU №2445669, МПК G05B 13/02], в котором регулятор включает фаззификатор с семью входами, блок логического вывода с заданными функциями принадлежности четких термов переменных, на вход которого подаются входные и выходные переменные, а также дискретные входные и выходные переменные объекта управления, дефаззификатора, исполнительного устройства, объекта управления и датчика обратной связи. Сравнивающее устройство реализовано в составе условной части продукционных правил блока нечеткого логического вывода. Для повышения точности и быстродействия входные и выходные переменные регулятора представлены совокупностью четких термов, а дополнительное повышение быстродействия регулятора достигнуто автоматическим расположением с помощью ANY-TIME алгоритма в начало системы продукций правил с наибольшей частотой срабатывания. Расширение управляющих функций регулятора достигнуто за счет использования в антецедентах продукционных правил дискретных и выходных переменных объекта управления.

Недостатками данного регулятора являются: последовательный способ обработки продукционных правил снижает быстродействие регулятора, применение прямоугольной формы функции принадлежности снижает точность регулирования в нечеткой области. Известен трехпозиционный регуляторов с адаптивной средней позицией [Патент RU №2220432, МПК G05B 13/02, G05B 11/18], в котором бесконтактность подключения функционального звена перенастройки достигается его подключением на выход трехпозиционного регулятора с фиксированными позициями параллельно с усилительным звеном с коэффициентом усиления К≥2 и последующей подачей суммарного сигнала этих двух параллельных ветвей на звено типа насыщения с единичным коэффициентом усиления и значениями сигналов насыщения, равными значениям крайних позиций исходного трехпозиционного регулятора относительно средней.

Недостатками данного регулятора являются: применение в функциональном звене перенастройки схемы интегрирования, которая снижает скорость регулирования при выбеге регулируемой величины (параметра) в зону (из зоны) нечувствительности, применимость регулятора только с одним параметром объекта управления.

Известен способ формирования нечеткого управляющего воздействия [Патент №2514127, МПК G05B 19/00], согласно которому предложен нечеткий адаптивный позиционный способ автоматического управления объектами с дискретными исполнительными устройствами, реализуемый посредством логического контроллера и заключающийся в формировании параметров управления по нечетким правилам и подаче этих параметров управления на объект, причем формирование параметров управления разделено на два уровня, на первом из которых с помощью нечеткой логики локализуется (выделяется) диапазон регулирования, в котором будет производиться дальнейшая адаптация, причем локализация диапазона регулирования производится путем определения основного (базового) значения параметра управления этого диапазона по формуле  , где Uад1 - адаптируемый параметр управления, Uo и Uk - параметры управления в двух крайних (противоположных) состояниях В объекта,

, где Uад1 - адаптируемый параметр управления, Uo и Uk - параметры управления в двух крайних (противоположных) состояниях В объекта,  нормированный эквивалент состояния объекта (

нормированный эквивалент состояния объекта ( при Bo,

при Bo,  при Bk, где Bo - начальное состояние объекта, Bk - конечное состояние объекта), принимаемого за значение параметра адаптивной средней позиции на данном диапазоне, а на втором уровне значение параметра управления определяется с помощью адаптивного трехпозиционного способа регулирования.

при Bk, где Bo - начальное состояние объекта, Bk - конечное состояние объекта), принимаемого за значение параметра адаптивной средней позиции на данном диапазоне, а на втором уровне значение параметра управления определяется с помощью адаптивного трехпозиционного способа регулирования.

Недостатками данного способа является ограничение характеристики состояния объекта управления одним параметром, последовательная обработка продукционных правил, снижающее быстродействие, и использование только дискретного исполнительного устройства.

Наиболее близкими по технической сущности к изобретению являются способ и устройство построения систем нечеткой логики [Патент №2417442, МПК G06N 7/02], при котором сначала формулируют последовательность правил нечеткой логики, затем каждому из этих правил назначают числовую характеристику - показатель качества управления, причем правила нечеткой логики реализованы на базе обученной нейронной сети, на входы нейронной сети подают информационные сигналы или сигналы от объекта управления, при этом на ее выходе формируется последовательность выходных сигналов или последовательность инструкций и рекомендаций, где обученная нейронная сеть является обученной большой искусственной нейронной сетью, причем каждое из правил нечеткой логики реализуют отдельным фрагментом обученной большой искусственной нейронной сети (доменом), где число доменов соответствует числу правил нечеткой логики и, кроме того, содержит некоторое избыточное число резервных доменов, причем один из доменов выполняет функции арбитра и коммутирует выходы доменов с выходами нейронной сети с учетом показателя качества управления.

Недостатками данного способа и устройства является техническая сложность доменной нейронной сети, которая реализуется с применением компьютерных компонентов. Компьютерные компоненты требуют программной обработки, что также является существенным недостатком устройства, так как значительно снижают быстродействие, достигнутое за счет распараллеливания обработки продукционных правил.

Цель настоящего изобретения:

- повышение быстродействия вычисления значения управляющего сигнала;

- упрощение структуры устройств нечеткого регулирования. Технический результат заявленного способа и устройства для его реализации:

- увеличение быстродействия за счет аппаратное распараллеливание вычисления значения нечеткой функции регулирования;

- унификация блоков обработки нечетких правил регулирования.

Технический результат в патентуемом способе синтеза управляющего сигнала в области нечетких значений функции управления достигается тем, что исходные значения управляющего сигнала  в дискретных точках области изменения параметров U1,U2,U3,…,UN объекта управления заранее известны в результате экспериментальных или теоретических исследований N-мерной функции управления, в процессе управления определяют текущие значения параметров объекта управления Ua1, Ua2, …, UaN, с помощью N фаззификаторов определяют принадлежность параметров объекта управления Ua1, Ua2, … UaN интервалам U1min≤Ua1, <U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления, в интервале [U1min, U1max) вычисляют 2N-1 промежуточных значений управляющего сигнала

в дискретных точках области изменения параметров U1,U2,U3,…,UN объекта управления заранее известны в результате экспериментальных или теоретических исследований N-мерной функции управления, в процессе управления определяют текущие значения параметров объекта управления Ua1, Ua2, …, UaN, с помощью N фаззификаторов определяют принадлежность параметров объекта управления Ua1, Ua2, … UaN интервалам U1min≤Ua1, <U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления, в интервале [U1min, U1max) вычисляют 2N-1 промежуточных значений управляющего сигнала  , причем искомое значение управляющего сигнала

, причем искомое значение управляющего сигнала  находится в такой же пропорции к паре значений управляющего сигнала

находится в такой же пропорции к паре значений управляющего сигнала

и

и  , как и значение Ua1 к значениям U1min и U1max соответственно, где

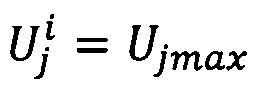

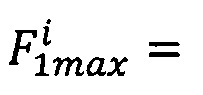

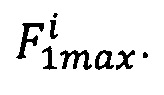

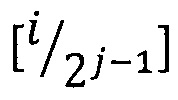

, как и значение Ua1 к значениям U1min и U1max соответственно, где  при четном значении целой части выражения

при четном значении целой части выражения  и

и  при нечетном, j изменяется от 2 до N, в интервале [Ujmin, Ujmax] вычисляют 2N-j промежуточных значений управляющего сигнала

при нечетном, j изменяется от 2 до N, в интервале [Ujmin, Ujmax] вычисляют 2N-j промежуточных значений управляющего сигнала  , причем искомое значение управляющего сигнала

, причем искомое значение управляющего сигнала  находится в такой же пропорции к паре промежуточных значений управляющего сигнала

находится в такой же пропорции к паре промежуточных значений управляющего сигнала  и

и  , как и значение Uaj к значениям Ujmin и Ujmax соответственно, на N-м шаге вычисляют окончательное значение управляющего сигнала Fy, причем искомое значение управляющего сигнала Fy находится в такой же пропорции к парам значений управляющего сигнала

, как и значение Uaj к значениям Ujmin и Ujmax соответственно, на N-м шаге вычисляют окончательное значение управляющего сигнала Fy, причем искомое значение управляющего сигнала Fy находится в такой же пропорции к парам значений управляющего сигнала  и

и  , как и значение UaN к значениям UNmin и UNmax соответственно, управляющий сигнал Fy передают на устройство управления объектом.

, как и значение UaN к значениям UNmin и UNmax соответственно, управляющий сигнал Fy передают на устройство управления объектом.

Технический результатв патентуемом многопараметрическом нечетком процессоре достигается тем, что он содержит N фаззификаторов, блок памяти, N рядов устройств вычисления управляющих сигналов, первый ряд сдержит 2N-1 устройств вычисления управляющих сигналов, j-й ряд 2N-j устройств вычисления управляющих сигналов, первый вход j-го фаззификатора подключен к j-му входу многопараметрического нечеткого регулятора и к третьему входу каждого из устройств вычисления управляющих сигналов j-го ряда, входы со 2 по K+1 j-го фаззификатора подключены соответственно к выходам с (j-1)⋅K+1 по j⋅K блока памяти, второй выход j-го фаззификатора подключен к первому входу каждого устройства вычисления управляющих сигналов j-го ряда и к j-му входу блока памяти, первый выход j-го фаззификатора подключен ко второму входу каждого устройства вычисления управляющих сигналов j-го ряда, выход N×K+1 блока памяти подключен к четвертому входу первого устройства вычисления управляющих сигналов первого ряда, выход N×K+2 блока памяти подключен к пятому входу первого устройства вычисления управляющих сигналов первого ряда, (N×K+2i-1)-й выход блока памяти подключен к четвертому входу i-го устройства вычисления управляющих сигналов первого ряда, (N×K+2i)-й выход блока памяти подключен к пятому входу i-го устройства вычисления управляющих сигналов первого ряда (j изменяется от 1 до N, i изменяется от 1 до 2N-1), выход первого устройства вычисления управляющих сигналов первого ряда подключен к четвертому входу первого устройства вычисления управляющих сигналов второго ряда, выход второго устройства вычисления управляющих сигналов первого ряда подключен к пятому входу первого устройства вычисления управляющих сигналов второго ряда, выход (2i-1)-го устройства вычисления управляющих сигналов j-го ряда подключен к четвертому входу i-го устройства вычисления управляющих сигналов (j+1)-го ряда, выход 2j-го устройства вычисления управляющих сигналов j-го ряда подключен к пятому входу i-го устройства вычисления управляющих сигналов (j+1)-го ряда, выход устройства вычисления управляющих сигналов N-го ряда подключен к выходу многопараметрического нечеткого процессора.

В патентуемом способе значения управляющего сигнала  полученные в результате экспериментальных или теоретических исследований поведения объекта управления в дискретных точках N-мерной области изменения значений множества параметров объекта управления {U1, U2, U3, …,UN}, где ki - номер значения параметра Ui в дискретной модели N-мерной области. С объекта управления поступают мгновенные значения параметров Ua1, Ua2, …, UaN. С помощью фаззификатора определяют интервалы U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN≤UNmax принадлежности значений параметров объекта управления по отношению к соседним дискретным точкам N-мерной области. В интервале [U1min, U1max] с помощью 2N-1 устройств вычисления управляющих сигналов первого ряда вычисляют 2N-1 значений управляющего сигнала по формуле

полученные в результате экспериментальных или теоретических исследований поведения объекта управления в дискретных точках N-мерной области изменения значений множества параметров объекта управления {U1, U2, U3, …,UN}, где ki - номер значения параметра Ui в дискретной модели N-мерной области. С объекта управления поступают мгновенные значения параметров Ua1, Ua2, …, UaN. С помощью фаззификатора определяют интервалы U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN≤UNmax принадлежности значений параметров объекта управления по отношению к соседним дискретным точкам N-мерной области. В интервале [U1min, U1max] с помощью 2N-1 устройств вычисления управляющих сигналов первого ряда вычисляют 2N-1 значений управляющего сигнала по формуле

,

,

где i - номер устройства вычисления управляющих сигналов в первом ряду,

,

,

- крайние значения параметров объекта управления, ограничивающие выбранную подобласть в дискретной модели N-мерной области,

- крайние значения параметров объекта управления, ограничивающие выбранную подобласть в дискретной модели N-мерной области,

,

,

В интервале [Ujmin, Ujmax] с помощью 2N-j устройств вычисления управляющих сигналов j-го ряда вычисляют 2N-j значений управляющего сигнала F по формуле

где i - номер устройства вычисления управляющих сигналов в j-м ряду (j изменяется от 2 до N). С помощью устройства вычисления управляющих сигналов в N-м ряду вычисляют окончательное значение управляющего сигнала Fy, который передают на устройство управления объектом.

Структурная схема многопараметрического процессора (в дальнейшем - процессор), предназначенного для систем регулирования и автоматического управления техническими и технологическими объектами, приведена на фиг.1. Устройство содержит N фаззификаторов 1, N рядов устройств вычисления управляющих сигналов (УВУС) 2, блок памяти 3. В первом ряду размещено 2N-1 УВУС 2, в j-м ряду 2N-j УВУС. Каждый ряд УВУС соединяется с соответствующим ему по номеру фаззификатором.

Рассмотрим работу процессора. Перед началом работы в режиме управления в блоке памяти 3 процессора хранятся значения управляющего сигнала, которые получают и записывают заранее по результатам экспериментальных или теоретических исследований N-мерной функции управления F. Каждая дискретная точка представлена в блоке памяти кортежем  , где F - значение управляющего сигнала, а

, где F - значение управляющего сигнала, а  - значения параметров объекта управления. Кортежи определяют множество правил выбора значения сигнала управления в дискретных точках. Каждый параметр объекта управления Uj может принимать в дискретных точках одно из фиксированных значений

- значения параметров объекта управления. Кортежи определяют множество правил выбора значения сигнала управления в дискретных точках. Каждый параметр объекта управления Uj может принимать в дискретных точках одно из фиксированных значений  где K - количество правил по каждому параметру. Между дискретными точками области управления располагаются области неопределенности, в которых сигнал управления принимает нечеткие значения. Задачей работы процессора является определение значений сигнала управления F в областях неопределенности.

где K - количество правил по каждому параметру. Между дискретными точками области управления располагаются области неопределенности, в которых сигнал управления принимает нечеткие значения. Задачей работы процессора является определение значений сигнала управления F в областях неопределенности.

В режиме управления на входы процессора поступают текущие аналоговые значения параметров объекта управления Ua1, Ua2, …, UaN, которые передаются на первые входы 11 соответствующих номеру параметра фаззификаторы 1. Входы со 12-го по 1K+1 j-го фаззификатора подключены соответственно к выходам с 4(j-1)⋅K+1, …, 4j⋅K блока памяти, из которых поступают аналоговые значения  параметров объекта управления в дискретных точках области изменения j-го параметра объекта управления. С помощью фаззификаторов 1 определяют принадлежность каждого параметра объекта управления Ua1, Ua2, …, UaN интервалам U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления. С выходов 1o1 и 1о2 фаззификаторов выбранные граничные значения подобласти принадлежности текущих параметров объекта управления (U1min, U1max), (U2min, U2max), …, (UNmin, UNmax) подаются на входы 21 и 22 УВУС, расположенных в соответствующих фаззификатору рядах. С выхода 1о2 j-го фаззификатора значения Ujmin подаются на вход 5j блока памяти 3, задавая начальный адрес выбранной подобласти принадлежности текущего значения параметра Uaj объекта управления. Используя начальный адрес U1min, U2min, …, UNmin из выбранной подобласти блок памяти 3 извлекает значения управляющего сигнала

параметров объекта управления в дискретных точках области изменения j-го параметра объекта управления. С помощью фаззификаторов 1 определяют принадлежность каждого параметра объекта управления Ua1, Ua2, …, UaN интервалам U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления. С выходов 1o1 и 1о2 фаззификаторов выбранные граничные значения подобласти принадлежности текущих параметров объекта управления (U1min, U1max), (U2min, U2max), …, (UNmin, UNmax) подаются на входы 21 и 22 УВУС, расположенных в соответствующих фаззификатору рядах. С выхода 1о2 j-го фаззификатора значения Ujmin подаются на вход 5j блока памяти 3, задавая начальный адрес выбранной подобласти принадлежности текущего значения параметра Uaj объекта управления. Используя начальный адрес U1min, U2min, …, UNmin из выбранной подобласти блок памяти 3 извлекает значения управляющего сигнала  всех дискретных точек в углах N-мерного куба выбранной подобласти, ограниченной интервальными значениями параметров объекта управления (U1min, U1max), (U2min, U2max), …, (UNmin, UNmax).

всех дискретных точек в углах N-мерного куба выбранной подобласти, ограниченной интервальными значениями параметров объекта управления (U1min, U1max), (U2min, U2max), …, (UNmin, UNmax).

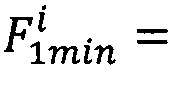

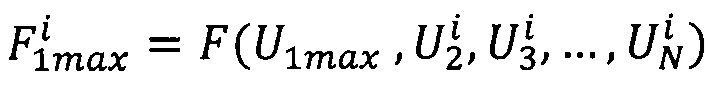

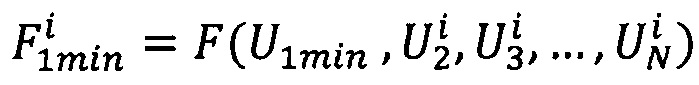

Из блока памяти 3 с выходов 61, …, 6S, где S=2N, на УВУС первого ряда передаются значения управляющих сигналов:  с выхода 62i-1 и

с выхода 62i-1 и

с выхода 62i, где

с выхода 62i, где

,

,

i - номер УВУС в первом ряду, j - номер параметра U (изменяется от 2 до N). На четвертый вход 24 i-го УВУС первого ряда передается сигнал  на пятый вход 25 i-го УВУС первого ряда передается сигнал

на пятый вход 25 i-го УВУС первого ряда передается сигнал  На выходе i-го УВУС в первом ряду будет промежуточное значение управляющего сигнала

На выходе i-го УВУС в первом ряду будет промежуточное значение управляющего сигнала  , которое рассчитывается по формуле (1). При j>1 на четвертый вход 24 i-го УВУС j-го ряда передается сигнал

, которое рассчитывается по формуле (1). При j>1 на четвертый вход 24 i-го УВУС j-го ряда передается сигнал  на пятый вход 25 i-го УВУС j-го ряда передается сигнал

на пятый вход 25 i-го УВУС j-го ряда передается сигнал  На выходе i-го УВУС j-го ряда будет промежуточное значение управляющего сигнала

На выходе i-го УВУС j-го ряда будет промежуточное значение управляющего сигнала  , которое рассчитывается по формуле (2). В N-м ряду на выходе 7 УВУС 2 будет значение управляющего сигнала Fy, которое передается на выход процессора.

, которое рассчитывается по формуле (2). В N-м ряду на выходе 7 УВУС 2 будет значение управляющего сигнала Fy, которое передается на выход процессора.

Фаззификаторы и УВУС реализуются на аналоговых схемах, содержащих компараторы, управляемые ключи, схемы аналоговых вычислений, ситуационные процессоры [Патент №2541850, МПК G06G7/25]. Блок памяти реализуется на цифроаналоговых схемах и микропроцессорах. Ограничения на количество параметров объекта управления определяется только применяемой элементной базой. Предлагаемый способ эффективен при монотонном характере функции управления в промежутках между соседними экспериментальными значениями в N-мерной области ее определения.

Использование данного изобретения позволит снизить время отклика существующих автоматических регуляторов, используемых для управления сложными техническими и технологическими объектами с быстро протекающими процессами, путем параллельной аппаратной обработки правил расчета функции управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИЧЕСКИЙ ФАЗЗИФИКАТОР | 2010 |

|

RU2446431C1 |

| Микрооптоэлектромеханический датчик угловой скорости с кольцевым резонатором | 2019 |

|

RU2702703C1 |

| Способ синхронизации трехфазных инверторов напряжения | 2024 |

|

RU2835153C1 |

| ОПТИЧЕСКИЙ ФАЗЗИФИКАТОР | 2010 |

|

RU2432599C1 |

| ОПТИЧЕСКИЙ ФАЗЗИФИКАТОР | 2009 |

|

RU2416119C2 |

| ОПТИЧЕСКИЙ ФАЗЗИФИКАТОР | 2010 |

|

RU2446434C1 |

| НЕЧЕТКИЙ РЕГУЛЯТОР С ЛИНГВИСТИЧЕСКОЙ ОБРАТНОЙ СВЯЗЬЮ ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2006 |

|

RU2309443C1 |

| Способ хранения и считывания аналоговых значений функций многих переменных | 2017 |

|

RU2656704C1 |

| СПОСОБ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2014 |

|

RU2585965C1 |

| ЧЕТКИЙ ЛОГИЧЕСКИЙ РЕГУЛЯТОР ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2010 |

|

RU2445669C2 |

Изобретение относится к области управления в реальном масштабе времени сложными объектами и быстротекущими процессами с многопараметрической зависимостью функции управления, которые не удается представить математической моделью в виде дифференциальных уравнений. Технический результат - повышение быстродействия управления при снижении аппаратной избыточности. Многопараметрический нечеткий процессор для систем автоматического управления характеризуется тем, что содержит N фаззификаторов, на которые подаются значения N параметров объекта управления, блок памяти, N рядов однотипных устройств вычисления управляющих сигналов, которые выполняют параллельное вычисление значений функции управления. 2 н.п. ф-лы, 1 ил.

1. Способ синтеза управляющего сигнала в области нечетких значений функции управления, в котором исходные значения управляющего сигнала  в дискретных точках области изменения параметров U1, U2, U3, …, UN объекта управления заранее известны в результате экспериментальных или теоретических исследований N-мерной функции управления, в котором в процессе управления определяют текущие значения параметров объекта управления Ua1, Ua2, …, UaN, с помощью N фаззификаторов определяют принадлежность параметров объекта управления Ua1, Ua2, …, UaN интервалам U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления, в интервале [U1min, U1max] вычисляют 2N-1 промежуточных значений управляющего сигнала

в дискретных точках области изменения параметров U1, U2, U3, …, UN объекта управления заранее известны в результате экспериментальных или теоретических исследований N-мерной функции управления, в котором в процессе управления определяют текущие значения параметров объекта управления Ua1, Ua2, …, UaN, с помощью N фаззификаторов определяют принадлежность параметров объекта управления Ua1, Ua2, …, UaN интервалам U1min≤Ua1<U1max, U2min≤Ua2<U2max, …, UNmin≤UaN<UNmax между соседними дискретными точками области изменения параметров объекта управления, в интервале [U1min, U1max] вычисляют 2N-1 промежуточных значений управляющего сигнала  , причем искомое значение управляющего сигнала

, причем искомое значение управляющего сигнала  находится в такой же пропорции к паре значений управляющего сигнала

находится в такой же пропорции к паре значений управляющего сигнала  и

и  , как и значение Ua1 к значениям U1min и U1max соответственно, где

, как и значение Ua1 к значениям U1min и U1max соответственно, где  при четном значении целой части выражения

при четном значении целой части выражения  и

и  при нечетном, j изменяется от 2 до N, в интервале [Ujmin, Ujmax] вычисляют 2N-j промежуточных значений управляющего сигнала

при нечетном, j изменяется от 2 до N, в интервале [Ujmin, Ujmax] вычисляют 2N-j промежуточных значений управляющего сигнала  , причем искомое значение управляющего сигнала

, причем искомое значение управляющего сигнала  находится в такой же пропорции к паре промежуточных значений управляющего сигнала

находится в такой же пропорции к паре промежуточных значений управляющего сигнала  и

и  , как и значение Ua1 к значениям Ujmin и Ujmax соответственно, на N-м шаге вычисляют окончательное значение управляющего сигнала Fу, причем искомое значение управляющего сигнала Fу находится в такой же пропорции к парам значений управляющего сигнала

, как и значение Ua1 к значениям Ujmin и Ujmax соответственно, на N-м шаге вычисляют окончательное значение управляющего сигнала Fу, причем искомое значение управляющего сигнала Fу находится в такой же пропорции к парам значений управляющего сигнала  и

и  , как и значение UaN к значениям UNmin и UNmax соответственно, управляющий сигнал Fу передают на устройство управления объектом.

, как и значение UaN к значениям UNmin и UNmax соответственно, управляющий сигнал Fу передают на устройство управления объектом.

2. Многопараметрический нечеткий процессор, содержащий N фаззификаторов, блок памяти, N рядов устройств вычисления управляющих сигналов, первый ряд содержит 2N-1 устройств вычисления управляющих сигналов, j-й ряд 2N-j устройств вычисления управляющих сигналов, первый вход j-го фаззификатора подключен к j-му входу многопараметрического нечеткого регулятора и к третьему входу каждого из устройств вычисления управляющих сигналов j-го ряда, входы со 2 по K+1 j-го фаззификатора подключены соответственно к выходам с (j-1)⋅K+1 по j⋅K блока памяти, второй выход j-го фаззификатора подключен к первому входу каждого устройства вычисления управляющих сигналов j-го ряда и к j-му входу блока памяти, первый выход j-го фаззификатора подключен ко второму входу каждого устройства вычисления управляющих сигналов j-го ряда, выход N×K+1 блока памяти подключен к четвертому входу первого устройства вычисления управляющих сигналов первого ряда, выход N×K+2 блока памяти подключен к пятому входу первого устройства вычисления управляющих сигналов первого ряда, (N×K+2i-1)-й выход блока памяти подключен к четвертому входу i-го устройства вычисления управляющих сигналов первого ряда, (N×K+2i)-й выход блока памяти подключен к пятому входу i-го устройства вычисления управляющих сигналов первого ряда (j изменяется от 1 до N, i изменяется от 1 до 2N-1), выход первого устройства вычисления управляющих сигналов первого ряда подключен к четвертому входу первого устройства вычисления управляющих сигналов второго ряда, выход второго устройства вычисления управляющих сигналов первого ряда подключен к пятому входу первого устройства вычисления управляющих сигналов второго ряда, выход (2i-1)-го устройства вычисления управляющих сигналов j-го ряда подключен к четвертому входу i-го устройства вычисления управляющих сигналов (j+1)-го ряда, выход 2j-го устройства вычисления управляющих сигналов j-го ряда подключен к пятому входу i-го устройства вычисления управляющих сигналов (j+1)-го ряда, выход устройства вычисления управляющих сигналов N-го ряда подключен к выходу многопараметрического нечеткого процессора.

| СПОСОБ ПОСТРОЕНИЯ СИСТЕМ НЕЧЕТКОЙ ЛОГИКИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2008 |

|

RU2417442C2 |

| МИКРОКОНТРОЛЛЕР С АППАРАТНЫМ НЕЧЕТКИМ ВЫЧИСЛИТЕЛЕМ ПЕРЕМЕННОЙ СТРУКТУРЫ | 2011 |

|

RU2477525C2 |

| ОПТОЭЛЕКТРОННЫЙ ПРОЦЕССОР | 2001 |

|

RU2212046C2 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2018-04-04—Публикация

2017-04-06—Подача