Изобретение относится к области управления с повышенной точностью сложными и быстродействующими технологическими процессами на предприятиях химической, нефтеперерабатывающей и нефтехимической промышленности, которые не удается описать системой линейных дифференциальных уравнений малого порядка, что вынуждает такие процессы представлять в виде вербальных или нелинейных моделей высокого порядка, реализованных на микропроцессорной элементной базе.

К настоящему времени известны многочисленные логические регуляторы в виде нечетких регуляторов для управления сложными технологическими процессами (Гостев В.И. Нечеткие регуляторы в системах автоматического управления. - К.: Радioматор, 2008. - 972 с. (стр.320; 326; 334; 362; 370); Васильев В.И., Ильясов Б.Г. Интеллектуальные системы управления. Теория и практика: учебное пособие. - М.: Радиотехника, 2009. - 392 с. ил. (стр.90). Наиболее типичным представителем упомянутых нечетких регуляторов является контроллер с нечеткой логикой и устройство для управления смешиванием горячей и холодной воды (патент №JР3110442, кл. 7 G05D 23/13, опубл. в 2000 г.), содержащие четкое сравнивающее устройство, блоки дифференцирования и интегрирования, фаззификатор, блок нечеткого логического вывода, дефаззификатор, исполнительный орган, объект управления и датчик обратной связи.

Однако данный нечеткий регулятор обладает большим временем отклика и большой погрешностью регулирования, что в ряде случаев делает невозможным его применение для управления с необходимой точностью быстродействующими технологическими процессами. Увеличение этого времени обусловлено тем, что первый вход автономного четкого сравнивающего устройства соединен с источником задающего сигнала, а второй - с выходом датчика обратной связи, а его выход, на котором формируется сигнал рассогласования (ошибки), соединен с одним из входов фаззификатора, вследствие чего в известных нечетких регуляторах заданное и текущее значения регулируемой величины сравнивается дважды: вначале в автономном четком сравнивающем устройстве, а затем - в условной части продукционных правил блока нечеткого логического вывода. Дополнительным фактором, увеличивающим время отклика известных нечетких регуляторов, является то обстоятельство, что в каждом цикле сканирования безусловно (независимо от текущего значения регулируемой величины) отрабатывается вся система продукционных правил, содержащаяся в блоке логического вывода. К тому же автономное четкое сравнивающее устройство обладает структурной избыточностью, которая, прежде всего, выражается в том, что в существующих нечетких регуляторах автономное четкое сравнивающее устройство предназначено для сравнения непрерывных функций, тогда как алгоритм нечеткого логического вывода оперирует термами лингвистических переменных, то есть не всеми, а только фиксированными значениями интерпретируемых функций.

Наиболее близким к заявленному техническому решению (прототип) является нечеткий регулятор с лингвистической обратной связью для управления технологическими процессами (патент №2309443, кл. G05B 13/02; G05B 11/01, опубл. в 2007 г., бюл. №30), состоящий из сравнивающего устройства, фаззификатора, блока нечеткого логического вывода с непрерывно сканируемой системой продукционных правил и с заданными функциями принадлежности термов лингвистических переменных, дефаззификатора, который по термам - Bmax («Отрицательное максимальное»), -0,5Bm («50% от отрицательного максимального»), B0 («Нулевой»), +0,5Bmax («50% от положительного максимального»), и +Bmax («Положительное максимальное»), лингвистической переменной В («Управляющая величина») вырабатывает текущее четкое значение управляющей величины, исполнительного устройства, объекта управления и датчика обратной связи.

Однако основным фактором снижения времени отклика нечеткого регулятора по патенту №2309443 является создание условий, при которых в системе продукционных правил регулятора в любой момент времени только у одного продукционного правила условная часть (антецедент) равна логической единице и расположением в начало системы продукционных правил правила с наибольшей частотой срабатывания (число случаев равенства логической единице антецедента продукционного правила за определенный интервал времени). Причем частоту срабатывания продукционных правил рекомендуется задавать исходя из опыта разработчика (эксперта) нечеткого регулятора.

Основными недостатками прототипа являются: не всегда в начало системы продукционных правил разработчик (эксперт) нечеткого логического регулятора располагает правило с максимальной частотой срабатывания, из-за чего не удается достичь минимального времени отклика нечеткого регулятора; в антецедентах продукционных правил нельзя использовать дискретные входные и выходные переменные объекта управления, т.к. они являются аргументами двузначной логики, функция принадлежности которых имеет прямоугольную форму (четкий терм), а параметры нечеткого регулятора представляются совокупностью нечетких термов с непрямоугольной формой функции принадлежности, а это ограничивает управляющие свойства нечеткого регулятора; большая погрешность регулирования нечеткого регулятора, вызванная, главным образом, процедурой дефаззификации.

Предлагаемое изобретение решает техническую задачу снижения времени отклика нечеткого регулятора и расширения области его применения за счет преобразования регулируемой величины в переменную, представленную термами «Нижнее допустимое», «Нижнее», «Номинальное», «Верхнее» и «Верхнее допустимое» с прямоугольными функциями принадлежности и сравнения этих термов с текущим значением регулируемой величины в условной части продукционных правил нечеткого регулятора.

Поставленная задача решается тем, что в структуре нечеткого регулятора с лингвистической обратной связью для управления технологическими процессами, состоящей из фаззификатора, блока логического вывода, дефаззификатора, исполнительного органа, объекта управления и датчика обратной связи, выход которого соединен с первым входом фаззификатора, а его входы со второго по шестой соединены с автономными источниками, идентифицирующими верхнее допустимое, верхнее, номинальное, нижнее и нижнее допустимое значения регулируемого параметра, что позволило сигналы задания и обратной связи сравнивать в нечетком формате в виде термов соответствующих лингвистических переменных в системе продукционных правил, в которой в любой момент времени только у одного правила условная часть равна логической единице и в начало системы продукционных правил проектировщик нечеткого логического регулятора исходя из личного опыта (субъективно, а значит не всегда точно) располагает правила с наибольшей частотой срабатывания, согласно изобретению для расширения управляющих свойств логического регулятора дискретные входные (X) и выходные (У) переменные от объекта управления соединены с дополнительными входами блока логического вывода 2, число которых равно общему количеству переменных Х и У, а для снижения времени отклика, уменьшения погрешности регулирования и совместного использования в антецедентах продукционных правил термов дискретных входных и выходных переменных объекта управления с термами регулирующих и регулируемых параметров регулятора с целью расширения его управляющих свойств, регулирующие и регулируемые параметры представлены совокупностью четких термов (их функция принадлежности имеет прямоугольную форму). Причем для автоматического определения частоты срабатывания продукционных правил, а значит и снижения времени отклика регулятора, использован ANY-TIME алгоритм, позволяющий в режиме реального времени систематически повышать точность определения частоты срабатывания каждого продукционного правила и автоматически располагать в начало системы продукционных правил правила с наибольшей частотой срабатывания. Поскольку в таком логическом регуляторе входные и выходные переменные представлены совокупностью четких термов, то в дальнейшем такой регулятор будет называться четким логическим регулятором.

На фиг.1 изображена структурная схема предлагаемого четкого логического регулятора для управления технологическими процессами, в котором входные и выходные переменные представлены совокупностью четких термов, т.е. таких термов, функция принадлежности которых равна единице на заданном отрезке универсальной числовой оси и равна нулю на всех остальных участках этой оси (фиг.2).

Схема четкого логического регулятора на фиг.1 для управления технологическими процессами, в котором входные и выходные переменные представлены совокупностью четких термов, содержит: фаззификатор 1, блок логического вывода 2, дефаззификатор 3, исполнительный орган 4, объект управления 5 и датчик обратной связи 6. Для параметров на фиг.1 введены следующие обозначения: u(t) - текущее значение регулирующего параметра на выходе дефаззификатора 3, z(t) - усиленное текущее значение регулирующего параметра на выходе исполнительного органа 4, p(t) - текущее значение регулируемого параметра, Рд верх - верхнее допустимое значение p(t), Рверх - верхнее значение p(t), Рном - номинальное значение p(t), Рниж - нижнее значение p(t), Рд ниж - нижнее допустимое значение p(t), Т - вектор четких термов регулируемого p(t) и регулирующего z(t) параметров, UT - вектор термов на выходе блока логического вывода 2, X - вектор входных дискретных параметров объекта управления 5, Y - вектор выходных дискретных параметров объекта управления 5.

Выход фаззификатора 1 соединен с входом блока логического вывода 2, выход блока логического вывода 2 соединен с входом дефаззификатора 3, выход дефаззификатора 3 соединен с входом исполнительного органа 4, выход исполнительного органа 4 соединен с входом объекта управления 5, выход объекта управления 5 соединен с входом датчика обратной связи 6, выход исполнительного органа 4 соединен с первым входом фаззификатора 1, выход датчика обратной связи 6 соединен со вторым входом фаззификатора 1, на входы 3÷7 фаззификатора 1 поданы константы Рд верх, Рверх, Pном, Рниж, и Рд ниж соответственно, выходные дискретные параметры Y объекта управления 5 поданы на вторую группу входов блока логического вывода 2, входные дискретные параметры X объекта управления 5 поданы на третью группу входов блока логического вывода 2.

На фиг.2а представлены функции принадлежности четких термов Рд верх, Рверх, Pном, Рниж, и Рд ниж регулируемой переменной p(t), которые равны логической единице на отрезках 0≤p(t)<p1, p1≤p(t)<p2, p2≤p(t)<p3, p3≤p(t)<p4, р4≤p(t)<p5 соответственно универсальной числовой оси р. На фиг.2б изображены функции принадлежности четких термов -Zm, -0,5Zm,>Z0,+0,5Zm,+Zm, управляющей переменной z(t), которые равны логической единице на отрезках z1≤z(t)<z2, z2≤z(t)<z3, z3≤z(t)<z4, z4≤z(t)<z5, z5≤z(t)<z6 соответственно универсальной числовой оси z. Функции принадлежности переменных p(t) и z(t) хранятся в базе данных четкого логического регулятора.

На вход фаззификатора 1 подаются в четком формате следующие величины: текущее значение регулирующей z(t) и регулируемой p(t) величины; верхнее допустимое значение p(t) - Рд верх; верхнее значение p(t) - Рверх; номинальное значение p(t) - Рном; нижнее значение p(t) - Рниж; нижнее допустимое значение p(t) - Рд ниж. В зависимости от текущего значения регулируемой переменной p(t) фаззификатор преобразует это значение в один из четких термов Рд верх, Рверх, Pном, Рниж, Рд ниж переменной p(t).

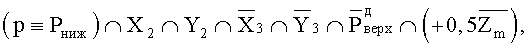

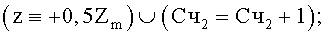

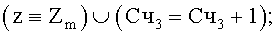

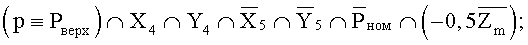

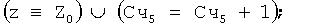

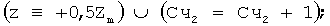

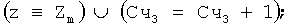

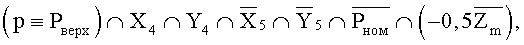

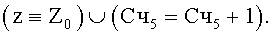

На фиг.3 представлена логическая схема алгоритма блока логического вывода 2 предлагаемого четкого логического регулятора для управления технологическими процессами. Она состоит из следующих операторов 1 - начало и 20 - окончание алгоритма; (2÷6) - операторы условного перехода, проверяющие истинность соответственно следующих условий:

(7÷11) - операторы, присваивающие регулирующей переменной z(t) значения:+Zm, +0,5Zm, -Zm, -0,5Zm, Z0 соответственно; 12÷16 - счетчики, выполняющие операции (Сч1=Сч1+1), (Сч2=Сч2+1), (Сч3=Сч3+1), (Сч4=Сч4+1), (Сч5=Сч5+1) 9 соответственно, т.е. фиксируют количество срабатываний выхода «Да» операторов 2÷6 за интервал времени Тзад, 17 - исполняемый оператор, сигнализирующий о выходе регулируемого параметра за допустимые пределы; 18 - условный оператор, у которого выход «Да» принимает значение логической единицы при выполнении условия Ттек≥Тзад, где Ттек - текущее время работы четкого логического регулятора, а Тзад - априори заданный интервал времени, по истечении которого происходит модификация системы продукционных правил логического регулятора (в начало системы продукционных правил автоматически располагаются правила с наибольшей частотой срабатывания); 19 - оператор, который по информации от счетчиков 12÷16 автоматически устанавливает с периодичностью Тзад в начало системы продукционных правил четкого логического регулятора правила с наибольшей частотой срабатывания.

Выход оператора 1 соединен с входом оператора 2. Выход «Нет» оператора 2 соединен со входом оператора 3, а его выход «Да» - со входом оператора 7. Выход «Нет» оператора 3 соединен со входом оператора 4, а его выход «Да» - со входом оператора 8. Выход «Нет» оператора 4 соединен со входом оператора 5, а его выход «Да» - со входом оператора 9. Выход «Нет» оператора 5 соединен со входом оператора 6, а его выход «Да» - со входом оператора 10. Выход «Нет» оператора 6 соединен со входом оператора 17, а его выход «Да» - со входом оператора 11. Выход оператора 17 соединен со входом оператора 18. Выходы операторов (7÷11) соединены с входами операторов (12÷16) соответственно. Выходы операторов (12÷16) соединены со входом оператора 18. Выход «Да» оператора 18 соединен со входом оператора 19, а его выход «Нет» - со входом оператора 20. Выход оператора 19 соединен со входом оператора 20. Благодаря использованию в условной части продукционных правил регулятора переменных, представляющих собой аргументы двузначной логики, в любой момент времени истинным является условие только в одном из операторов 2÷6 схемы на фиг.3. В этом ее принципиальное отличие от аналогичных схем существующих логических регуляторов.

Система продукционных правил блока логического вывода 2, реализующая логическую схему алгоритма на фиг.3, имеет следующий вид:

1. Если  то

то

2. Если  то

то

3. Если  то

то

4. Если  то

то

5. Если  то

то

Система (1) предлагаемого логического регулятора построена так, что в любой момент времени условная часть истинна только в одном продукционном правиле и ложна во всех остальных правилах этой системы. Это позволяет без утраты адекватности управления в каждом цикле сканирования системы продукционных правил обрабатывать не всю систему (это имеет место в известных нечетких регуляторах), а только ту ее часть, которая в системе (1) расположена выше правила, сработавшего в текущем цикле сканирования.

Кроме того, в антецедентах правил системы (1) используются термы не только входных (четкие термы функции p(t)), но и выходных (четкие термы функции z(t))+Zm, +0,5Zm, -Zm, -0,5Zm, Z0 переменных четкого логического регулятора, а также дискретные входные (X1÷Х2) и выходные (Y1÷Y5) переменные объекта управления в прямой и инверсной формах. Такое стало возможным вследствие того, что регулирующие и регулируемые переменные предлагаемого четкого логического регулятора интерпретированы совокупностью четких термов, которые по своей логической природе, как и дискретные сигналы объекта управления, являются аргументами двузначной логики. Использование в антецедентах продукционных правил упомянутых переменных, характеризующихся богатым спектром целенаправленного воздействия на объект управления, существенно расширяет и усиливает управляющие свойства четкого логического регулятора.

Логический регулятор, в котором входные и выходные переменные представлены совокупностью четких термов, для управления технологическими процессами функционирует следующим образом. На входах 3÷7 фаззификатора 1 устанавливается четкое значение величины сигналов, идентифицирующих следующие фиксированные значения регулируемой величины: Рд верх, Рверх, Pном, Рниж, и Рд ниж. При этом предполагается, что текущее значение регулируемой величины находится в пределах допустимых значений, а счетчики (12÷16) обнулены. Микропроцессор с заданной периодичностью непрерывно сканирует систему правил (1). В зависимости от четкого текущего значения регулируемой величины p(t) фаззификатор преобразует его в один из термов лингвистической переменной Р. Например, если значение p(t) (фиг.2а) находится в диапазоне 0≤p(t)<p1, то его четкое значение преобразуется в терм Рд ниж. Если p1≤p(t)<р2, то p(t) преобразуется в терм Рниж. Аналогично, при условии р2≤p(t)<р3 p(t) преобразуется в терм Pном, при р3≤p(t)<p4 - в терм Рверх, а при р4≤p(t)<р5 - в терм Рд верх. Таким образом, в любой момент времени с выхода фаззификатора на вход блока логического вывода 2 поступает только один терм, причем тот, который идентифицирует четкое текущее значение регулируемой величины p(t) в данном цикле сканирования системы продукционных правил (1). Поскольку в этой системе в любой момент времени условная часть истинна только в одном продукционном правиле и ложна во всех остальных правилах этой системы, то в каждом цикле сканирования системы нечетких правил обрабатывается не вся система (это имеет место в известных нечетких регуляторах), а только та ее часть, которая в системе (1) расположена выше сработавшего в текущем цикле сканирования продукционного правила. Поэтому в каждом цикле сканирования микропроцессор будет отрабатывать не всю схему на фиг.3, а только ту ее часть, которая расположена левее условного оператора, имеющего истинное условие в данный момент времени.

Если в системе (1) сработало первое продукционное правило, то текущее значение регулируемой переменной находится в интервале 0≤p(t)<p1 универсальной оси на фиг.2а. Поэтому управляющему воздействию z(t) в такой ситуации присваивается значение терма +Zm, при котором исполнительный орган 4 воздействует на объект управления таким образом, что происходит интенсивное увеличение значения регулируемой переменной, а в счетчик Cч1 (оператор 12) прибавляется единица. При этом в рассматриваемом цикле сканирования системы (1) микропроцессор отработает только первое правило, а правила 2÷5 пропускаются, после чего приступает к выполнению следующего цикла сканирования. На логической схеме алгоритма (фиг.3) в этой ситуации последовательно отрабатываются блоки 1, 2, 7, 12, 18 и 20.

Если в системе (1) сработало второе продукционное правило, то текущее значение регулируемой переменной на универсальной оси на фиг.2а находится внутри отрезка р1≤p(t)<p2. Поэтому управляющему воздействию z(t) в такой ситуации присваивается значение терма +0,5Zm, при котором исполнительный орган 4 воздействует на объект управления таким образом, что происходит плавное увеличение значения регулируемой величины, а в счетчик Сч2 прибавляется единица. При этом в рассматриваемом цикле сканирования системы (1) микропроцессор отработает первое и второе правила, а правила 3÷5 пропускает, после чего приступает к выполнению следующего цикла сканирования. Причем в первом правиле анализируется только условная часть. На логической схеме алгоритма (фиг.3) в этой ситуации последовательно отрабатываются блоки 1, 2, 3, 8, 13, 18 и 20,

Если в системе (1) сработало третье продукционное правило, то текущее значение регулируемой величины на универсальной оси (фиг.2а) находится внутри отрезка р4≤p(t)<р5. Поэтому управляющему воздействию z(t) в такой ситуации присваивается значение терма -Zm, при котором исполнительный орган 4 воздействует на объект управления 5 таким образом, что происходит интенсивное снижение значения регулируемой величины, а в счетчик Сч3 прибавляется единица. При этом в данном цикле сканирования системы (1) микропроцессор отработает первое, второе и третье, а четвертое и пятое правила пропускает, после чего приступает к выполнению следующего цикла сканирования. Причем в первом и втором правиле анализируется только условная часть. На логической схеме алгоритма (фиг.3) в этой ситуации последовательно отрабатываются блоки 1, 2, 3, 4, 9, 14, 18 и 20.

Если в системе (1) сработало четвертое продукционное правило, то текущее значение регулируемой величины на универсальной оси (фиг.2) находится внутри отрезка р3≤p(t)<p4. Поэтому управляющему воздействию z(t) в такой ситуации присваивается значение терма -0,5Zm, при котором исполнительный орган 4 воздействует на объект управления 5 таким образом, что происходит медленное снижение значения регулируемой величины, а в счетчик Сч4 прибавляется единица. При этом в данном цикле сканирования системы (1) микропроцессор отработает первые четыре правила, а пятое правило пропустит, после чего приступит к выполнению следующего цикла сканирования. Причем в первом, втором и третьем правилах анализируется только условная часть. На логической схеме алгоритма (фиг.3) в этой ситуации последовательно отрабатываются блоки 1, 2, 3, 4, 5, 10, 15, 18 и 20.

Наконец, если в системе правил (1) сработало пятое продукционное правило, то текущее значение регулируемой величины на универсальной числовой оси (фиг.2а) находится внутри отрезка р2≤p(t)<p3. Поэтому управляющему воздействию z(t) в такой ситуации присваивается значение терма Z0, при котором исполнительный орган 4 воздействует на объект управления 5 таким образом, что происходит поддержание значения регулируемой величины на номинальном уровне, а в счетчик Сч5 прибавляется единица. При этом в данном цикле сканирования системы (1) микропроцессор отработает все пять правил, после чего приступает к выполнению следующего цикла сканирования. Причем в первых четырех правилах анализируется только условная часть. На логической схеме алгоритма (фиг.3) в этой ситуации последовательно отрабатываются блоки 1, 2, 3, 4, 5, 6, 11, 16, 18 и 20.

В случае выхода значения регулируемого параметра p(t) за пределы отрезков (0÷p5) универсальной оси на фиг.2а управление с выхода «Нет» блока 6 на фиг.3 передается блоку отработки аварийных ситуаций 17, который выставляет сообщение об аварии, обнуляет значение регулируемого параметра p(t) и блокирует сканирование системы продукционных правил (1).

В блоке логического вывода 2 происходит непрерывное сканирование системы правил (1). Из-за использования в системе (1) четких термов в любой момент времени имеется только одно правило с истинной условной частью. Поэтому система (1) без потери адекватности управления сканируется не полностью, а только до продукционного правила с истинной условной частью, после чего микропроцессор переходит к отработке следующего цикла сканирования. Это приводит к снижению времени отклика предлагаемого нечеткого регулятора. Причем этот эффект проявится в большей степени, если продукционные правила с наибольшей частотой срабатывания поместить в начало системы правил (1).

Для достоверного определения в автоматическом режиме частоты срабатывания продукционных правил в предлагаемом четком логическом регуляторе использован ANY-TIME алгоритм (на фиг.3 он реализован блоками 18 и 19), который в режиме on-line с периодичностью Тзад считывает содержимое счетчиков (12÷16), и в соответствии с этой информацией, т.е. уточненной частотой срабатывания продукционных правил, перерасполагает их с начала системы продукционных правил в порядке убывания их частоты срабатывания.

ANY-TIME алгоритм функционирует следующим образом. В процессе работы логического регулятора, когда Ттек≥Тзад, управление с выхода «Да» блока 18 на фиг.3 передается блоку 19, который считывает информацию со счетчиков (12÷16), т.е. частоту срабатывания продукционных правил и в соответствии с ней продукции в системе продукционных правил располагаются в порядке убывания их частоты срабатывания. В итоге в начале системы продукционных правил четкого логического регулятора с высокой степенью достоверности окажутся правила с наибольшей частотой срабатывания, а это значит, что логический регулятор будет иметь наименьшее время отклика.

Таким образом, в результате непрерывного сканирования системы (1) и вследствие того, что в ней в любой момент времени имеется только одно продукционное правило, условная часть которого истинна, значение регулируемой величины p(t) в предлагаемом логическом регуляторе с высоким быстродействием поддерживается около номинального уровня.

Представление информации в операционной среде логического регулятора с четкими термами совокупностью аргументов двузначной логики позволяет также существенно повысить точность регулирования по сравнению, нечеткими логическими регуляторами. Такой вывод следует из того, что в нечетких регуляторах на вход дефаззификатора поступает терм, функция принадлежности которого представляет собой многоугольник сложной формы. Причем по мере увеличения факторов, влияющих на регулируемую функцию, эта сложность возрастает, а точность дефаззификации снижается.

В предлагаемом логическом регуляторе ограничения на учет числа указанных факторов принципиально не существует, потому что при любой сложности структуры антецедента продукционного правила результатом вывода будет один из четких термов регулирующей функции логического регулятора, который указан в заключительной части (консеквенте) этого продукционного правила. Например, если в системе (1) сработало правило 3 (на фиг.3 блок 4), то регулирующей переменной z(t) присваивается значение терма -Zm. Причем точность логического регулятора здесь полностью определяется шириной терма Zm, которая, в свою очередь, определяется элементной базой, на которой построен четкий логический регулятор.

Результат логического вывода в виде одного из термов регулирующей переменной и u(t) с выхода блока 2 подается на вход дефаззификатора 3, в котором преобразуется в четкий формат и передается на исполнительный орган 4 для усиления и совершения управляющих воздействий на объекте управления 5 с помощью функции z(t) (фиг.2б).

Использование данного изобретения позволит снизить время отклика существующих логических регуляторов, используемых для управления сложными быстродействующими технологическими объектами с быстро протекающими процессами, которые описываются нелинейными интегродифференциальными уравнениями высокого порядка. Такие системы управления находят все большее применение в машиностроении (станкостроение, авиастроение, робототехника, космическая и автомобильная отрасли), пищевой, нефтяной и газовой промышленности в тех случаях, когда объект управления не имеет приемлемой математической модели.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЧЕТКИЙ РЕГУЛЯТОР С ЛИНГВИСТИЧЕСКОЙ ОБРАТНОЙ СВЯЗЬЮ ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2006 |

|

RU2309443C1 |

| АДАПТИВНЫЙ ИНТЕЛЛЕКТУАЛЬНЫЙ ЛОГИЧЕСКИЙ РЕГУЛЯТОР, РАБОТАЮЩИЙ В УСЛОВИЯХ НЕЧЕТКО ЗАДАННОЙ ИНФОРМАЦИИ | 2014 |

|

RU2579987C2 |

| Многопараметрический нечеткий процессор для автоматических регуляторов и способ синтеза управляющего сигнала | 2017 |

|

RU2649791C1 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2010 |

|

RU2445672C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОСТАТОЧНОГО РЕСУРСА ЭЛЕКТРОПРОВОДКИ | 2014 |

|

RU2556299C1 |

| СПОСОБ ОЦЕНКИ ПСИХОФИЗИЧЕСКОГО СОСТОЯНИЯ СПЕЦИАЛИСТА | 2021 |

|

RU2799620C2 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2011 |

|

RU2446436C1 |

| СПОСОБ И УСТРОЙСТВО СТАБИЛИЗАЦИИ ПРОЦЕССА РЕЗАНИЯ НА ТОКАРНОМ ОБОРУДОВАНИИ С ЧПУ | 2010 |

|

RU2465116C2 |

| Способ оценки мышечной усталости на основе контроля паттернов синергии и устройство для его осуществления | 2021 |

|

RU2766764C1 |

| СПОСОБ КОНТРОЛЯ И РЕМОНТА ИЗОЛЯЦИИ ПРОВОДОВ | 2020 |

|

RU2745432C1 |

Изобретение относится к области управления с повышенной точностью сложными и быстродействующими технологическими процессами на предприятиях химической, машиностроительной, нефтеперерабатывающей и нефтехимической промышленности, которые не удается описать системой линейных дифференциальных уравнений малого порядка, что вынуждает такие процессы представлять в виде вербальной модели. Технический результат - повышение быстродействия и точности, а также расширение управляющих функций четких логических регуляторов. Четкий логический регулятор включает фаззификатор с семью входами, блок логического вывода с заданными функциями принадлежности четких термов переменных, на вход которого подаются входные и выходные переменные, а также дискретные входные и выходные переменные объекта управления, дефаззификатора, исполнительного устройства, объекта управления и датчика обратной связи. Сравнивающее устройство реализовано в составе условной части продукционных правил блока нечеткого логического вывода. Для повышения точности и быстродействия входные и выходные переменные регулятора представлены совокупностью четких термов, а дополнительное повышение быстродействия регулятора достигнуто автоматическим расположением с помощью ANY-TIME алгоритма в начало системы продукций правил с наибольшей частотой срабатывания. Расширение управляющих функций регулятора достигнуто за счет использования в антецедентах продукционных правил дискретных входных и выходных переменных объекта управления. Изобретение обеспечивает автоматическое управление быстродействующими технологическими процессами, описанными вербально и требующими качественного регулирования, постоянная времени которых меньше времени отклика известных логических регуляторов. 2 з.п. ф-лы, 3 ил.

1. Четкий логический регулятор для управления технологическими процессами, состоящий из сравнивающего устройства, фаззификатора, блока логического вывода с непрерывно сканируемой системой продукционных правил и с заданными функциями принадлежности термов переменных, дефаззификатора, который по термам -Zm («Отрицательное максимальное»), -0,5Zm («50% от отрицательного максимального»), Z0 («Нулевой»), +0,5Zm («50% от положительного максимального»), и +Zm («Положительное максимальное») вырабатывает текущее четкое значение регулирующей переменной u(t), исполнительного органа, объекта управления и датчика обратной связи, выход которого соединен с одним из входов фаззификатора, остальные входы фаззификатора по отдельности соединены с автономными источниками сигналов, идентифицирующих следующие фиксированные значения регулируемой величины p(t): Рд верх («Верхнее допустимое»), Рверх («Верхнее»), Рном («Номинальное»), Рниж («Нижнее»), Рд ниж («Нижнее допустимое»), а сравнивающее устройство реализовано в составе условной части продукционных правил блока нечеткого логического вывода, причем в системе продукционных правил блока логического вывода в любой момент времени только у одного правила условная часть равна логической единице, и в начало системы продукционных правил при разработке логического регулятора экспертом размещены правила с наибольшей частотой срабатывания, отличающийся тем, что выход исполнительного органа соединен с отдельным входом фаззификатора, а дискретные входные (X) и выходные (Y) переменные объекта управления поданы на отдельные входы блока логического вывода, а в системе продукционных правил блока логического вывода управляющие команды (z≡+Zm), (z≡+0,5Zm), (z≡-Zm), (z≡-0,5Zm), (z≡Z0) расположены соответственно последовательно с операциями со счетчиками (Cч1=Cч1+1)÷(Сч5=Сч5+1), входящими в систему продукционных правил блока логического вывода, и предназначенными для фиксации количества срабатываний соответствующего продукционного правила, причем система продукционных правил блока логического вывода имеет следующий вид:

1) если  то

то

2) если  то

то

3) если  то

то

4) если  то

то

5) если  то

то

2. Устройство по п.1, отличающееся тем, что входные и выходные переменные логического регулятора представлены в виде совокупности четких термов, вследствие чего независимо от сложности антецедента продукционных правил результатом логического вывода является один из четких термов регулируемого параметра регулятора, ширина которого определяет точность четкого логического регулятора, причем пределом уменьшения этой ширины является лишь разрешающая способность элементной базы, на которой реализован логический регулятор.

3. Устройство по п.1, отличающееся тем, что в алгоритм блока логического вывода введены счетчики числа срабатываний продукционных правил за заданный интервал времени Тзад (из расчета один счетчик на одно правило) и два оператора: условного перехода, который определяет начало модификации системы продукционных правил с заданной периодичностью (Тзад) и автоматического перерасположения правил в системе продукционных правил через каждый интервал времени Тзад в порядке убывания их частоты срабатывания по информации, считанной из счетчиков числа срабатываний этих правил за интервал времени Тзад.

| НЕЧЕТКИЙ РЕГУЛЯТОР С ЛИНГВИСТИЧЕСКОЙ ОБРАТНОЙ СВЯЗЬЮ ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2006 |

|

RU2309443C1 |

| СПОСОБ ФОРМИРОВАНИЯ НЕЧЕТКОГО УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ, УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ, СПОСОБ УПРАВЛЕНИЯ И СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1990 |

|

RU2110826C1 |

| JP 4069714 A, 10.05.1992 | |||

| СПОСОБ ЭКСТРЕМАЛЬНОГО РЕГУЛИРОВАНИЯ С ПОДДЕРЖАНИЕМ РАБОЧЕЙ ТОЧКИ ИНЕРЦИОННОГО ОБЪЕКТА НА ЗАДАННОМ РАССТОЯНИИ ОТ ЭКСТРЕМУМА | 2005 |

|

RU2298821C2 |

Авторы

Даты

2012-03-20—Публикация

2010-02-15—Подача