Изобретение относится к области радиотехники и может быть использовано в многоканальных цифровых мониторинговых приемниках, реализованных на программируемой логической интегральной схеме (ПЛИС), в качестве устройства для изменения частоты дискретизации (ресэмплер).

Наиболее близким по внутренней структуре к предлагаемому устройству является устройство для изменения частоты дискретизации (диссертация Абраменко А.Ю. «Устройство формирования узкополосных радиосигналов с использованием алгоритма оптимальной интерполяции», Томск, 2014). В составе устройства присутствуют следующие блоки: блок вычисления коэффициентов полинома с использованием умножителей, линия задержки, блок вычисления интерполирующего полинома, блок формирования временных отсчетов.

Недостатком данного устройства является необходимость использования аппаратных умножителей ПЛИС для реализации блока вычисления коэффициентов полинома. Реализация многоканального цифрового мониторингового приемника (тракт фильтрации, тракт изменения частоты дискретизации, демодулятор, блок определения идентификационных признаков) затрудняется тем, что число аппаратных умножителей ПЛИС ограничено.

Задачей предлагаемого технического решения является обеспечение реализации блока вычисления коэффициентов полинома устройства передискретизации на ПЛИС без использования умножителей для применения в многоканальных цифровых приемниках в задачах радиомониторинга.

Поставленная задача решается тем, что устройство для передискретизации, состоящее из блока вычисления коэффициентов полинома (БВКП), блока формирования временных отсчетов (БФВО), блока вычисления интерполирующего полинома (БВИП), содержит в составе БВКП линию задержки и несколько вычислителей, число которых определяется порядком интерполирующего полинома. Каждый вычислитель содержит сумматоры (вычитатели) и сдвиговые устройства.

Предлагаемое техническое решение поясняется чертежами.

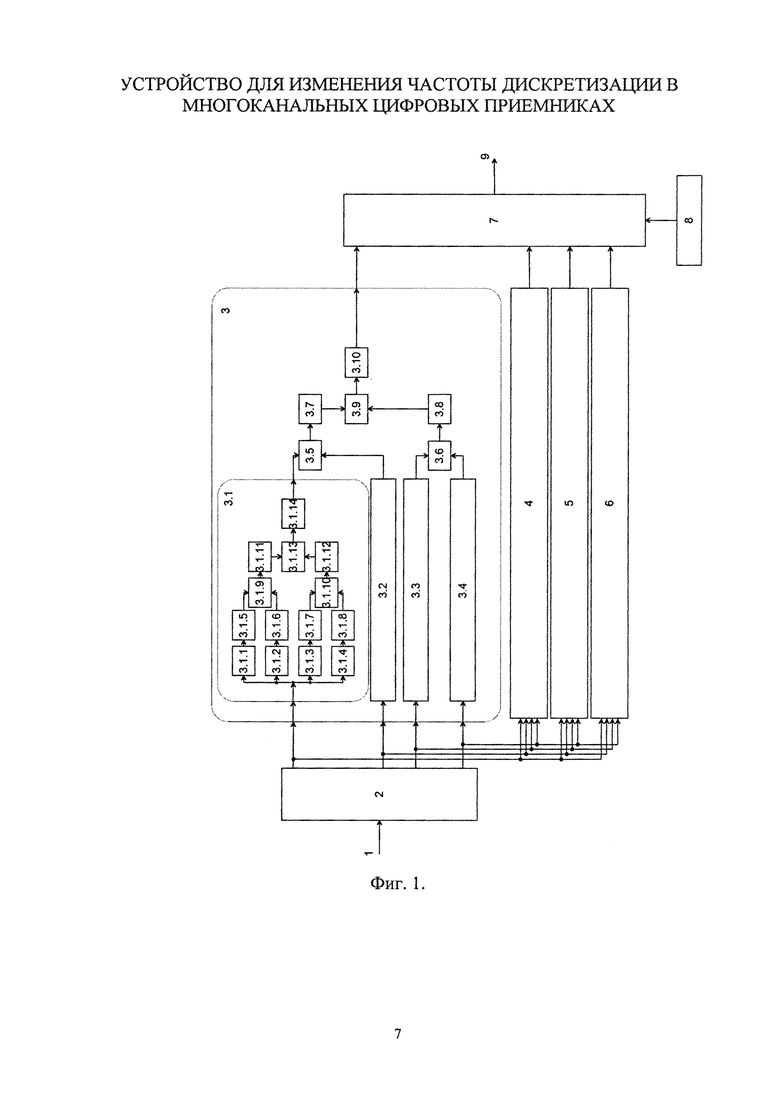

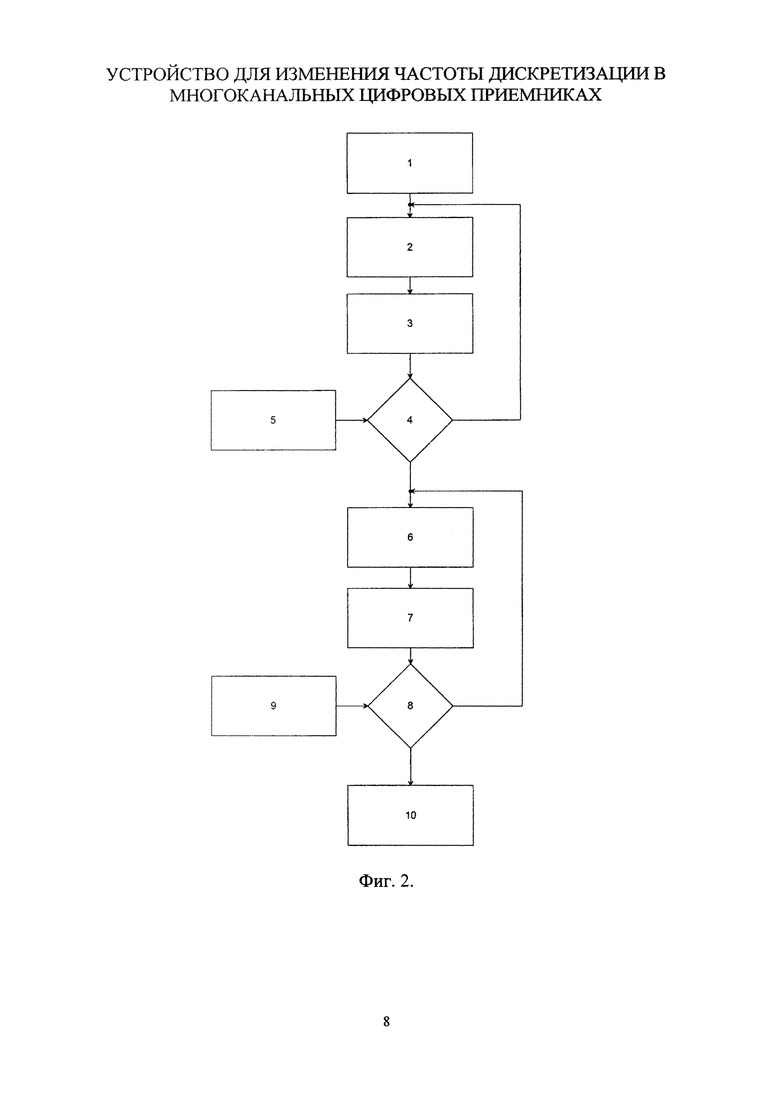

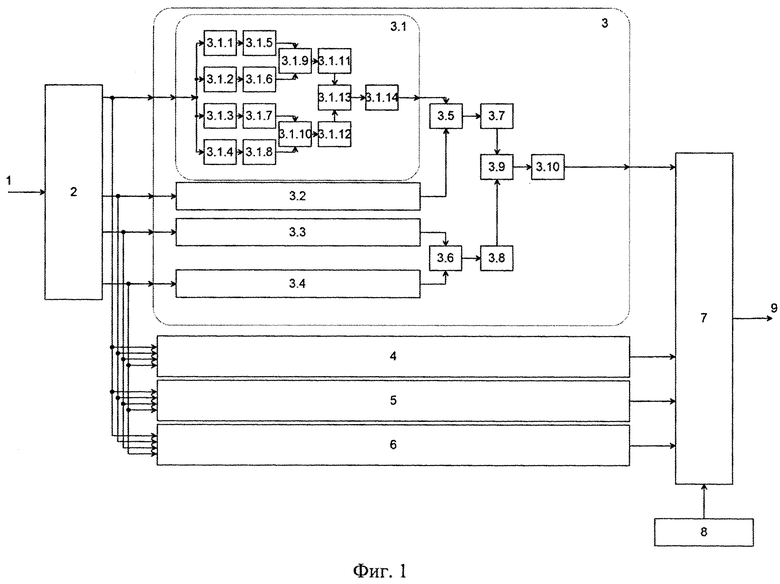

На фиг. 1 представлена структурная схема предлагаемого устройства. На фиг. 2 представлен алгоритм, в соответствии с которым производится определение индексов на устройствах сдвига.

На входе устройства для передискретизации присутствует входной цифровой сигнал 1. Сигнал 1 поступает на линию задержки 2. Линия задержки соединена с входами вычислителей 3, 4, 5, 6. Вычислитель 3 состоит из константных умножителей 3.1, 3.2, 3.3, 3.4, регистров 3.7, 3.8, 3.10, сумматоров 3.5, 3.6, 3.9. Входы константных умножителей 3.1, 3.2, 3.3, 3.4 соединены с соответствующими выходами линии задержки 2. Входы сумматоров 3.5, 3.6 соединены с выходами константных умножителей 3.1, 3.2, 3.3, 3.4. Выходы сумматоров 3.5, 3.6 соединены со входам регистров 3.7, 3.8, их выходы соединены со входами сумматора 3.9. Выход сумматора 3.9 соединен со входом регистра 3.10. Выход регистра 3.10 является выходом вычислителя 3. Каждый константный умножитель 3.1, 3.2, 3.3, 3.4 состоит из устройств сдвига 3.1.1, 3.1.2, 3.1.3, 3.1.4, регистров 3.1.5, 3.1.6, 3.1.7, 3.1.8, 3.1.11, 3.1.12, 3.1.14, сумматоров 3.1.9, 3.1.10, 3.1.13. Входы устройств сдвига 3.1.1, 3.1.2, 3.1.3, 3.1.4 объединены и представляют собой вход константного умножителя. Выходы сдвиговых устройств 3.1.1, 3.1.2, 3.1.3, 3.1.4 соединены со входами регистров 3.1.5, 3.1.6, 3.1.7, 3.1.8, их выходы соединены со входами сумматоров 3.1.9, 3.1.10, их выходы соединены со входами регистров 3.1.11, 3.1.12. Выходы регистров 3.1.11, 3.1.12 соединены со входами сумматора 3.1.13. Его выход соединен со входом регистра 3.1.14. Выход регистра 3.1.14 является выходом константного умножителя 3.1. Оставшиеся вычислители 4, 5, 6 устроены аналогично вычислителю 3, различие заключается в индексах устройств сдвига в константных умножителях вычислителей. Блоки 2, 3, 4, 5, 6 образуют БВКП. Выходы вычислителей 3, 4, 5, 6 соединены с соответствующими входами БВИП 7. Соответствующий вход БВИП 7 соединен с выходом БФВО 8. На выходе БВИП 7 присутствует выходной сигнал устройства для передискретизации 9.

В данном случае структурная схема устройства для передискретизации представлена для интерполятора 3-го порядка. В случае увеличения порядка интерполятора в составе устройства должно присутствовать количество вычислителей, превосходящее на 1 порядок интерполяции, а в составе каждого вычислителя присутствует число константных умножителей на 1 превосходящее порядок интерполяции. Структура константного умножителя аналогична приведенной на фиг. 1. Число входных сигналов БВИП 7 равно числу вычислителей.

Устройство работает следующим образом

На вход устройства подается цифровой сигнал 1 x(m) (фиг. 1). В вычислителях 3, 4, 5, 6 производится расчет коэффициентов интерполирующего полинома c0…cN по отсчетам входного сигнала 1. Для расчета коэффициентов c0…cN необходимо произвести операцию умножения отсчетов входного сигнала на набор весовых коэффициентов БВКП ki,j. Данная операция реализуется с помощью устройств сдвига и сумматоров в каждом вычислителе 3, 4, 5, 6. В БФВО 8 производится формирование нормированных временных отсчетов μ. По нормированным временным отсчетам μ и набору коэффициентов интерполирующего полинома в БВИП 7 производится вычисление отсчетов сигнала на новой частоте дискретизации y(n). Выражение (1) дает математическое описание работы устройства.

Для обеспечения постоянства структуры константных умножителей в вычислителях 3, 4, 5, 6 следует воспользоваться разработанным алгоритмом (фиг. 2). Входными данными для алгоритма является набор весовых коэффициентов БВКП в формате с плавающей точкой 1. Далее осуществляется итеративный алгоритм поиска минимальной разрядности коэффициентов, состоящий из этапов: 2 - операция ограничения разрядности коэффициентов, 3 - оценка уровня нелинейных искажений, 4 - сравнение с введенным допустимым значением 5. Затем производится формирование структуры константного умножителя. Данный алгоритм так же итеративный, он состоит из следующих этапов: 6 - представление коэффициентов с конечной разрядностью в виде суммы степеней числа 2, уменьшение числа слагаемых, 7 - оценка уровня нелинейных искажений, 8 - сравнение с допустимым уровнем искажений 9, 10 - набор весовых коэффициентов ki,j, представленный в виде суммы степеней числа 2, число слагаемых ограничено 4. В таком виде коэффициенты ki,j (константные умножители) пригодны для реализации на сумматорах и устройствах сдвига (фиг. 1).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| Способ управления лучом в активной фазированной антенной решетке | 2023 |

|

RU2805384C1 |

| Адаптивное устройство для сокращения избыточности цифровой информации | 1983 |

|

SU1136201A1 |

| Формирователь цифрового частотно-модулированного сигнала | 1983 |

|

SU1202068A1 |

| Способ пространственно-временной обработки радиосигналов для компенсации помех | 2024 |

|

RU2836610C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2701059C1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| СПОСОБ ЦИФРОВОЙ ФИЛЬТРАЦИИ СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2018 |

|

RU2743853C2 |

| СПОСОБ МНОГОПАРАМЕТРИЧЕСКОГО СЛЕЖЕНИЯ ЗА НАВИГАЦИОННЫМИ СИГНАЛАМИ И ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С МНОГОПАРАМЕТРИЧЕСКИМ УСТРОЙСТВОМ СЛЕЖЕНИЯ ЗА СЛАБЫМИ СИГНАЛАМИ В УСЛОВИЯХ СВЕРХВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2012 |

|

RU2551805C2 |

Изобретение относится к области радиотехники и может быть использовано в многоканальных цифровых мониторинговых приемниках, реализованных на ПЛИС, в качестве устройства для изменения частоты дискретизации. Технический результат - обеспечение реализации устройства без использования аппаратных умножителей, упрощение структуры блока вычисления коэффициентов полинома, как следствие снижение динамической потребляемой мощности устройства, обеспечение реализации многоканальных цифровых приемников для радиомониторинга. Устройство для изменения частоты дискретизации в многоканальных цифровых приемниках содержит бок вычисления коэффициентов полинома, содержащий линию задержки, вычислители, в состав которых входят устройства сдвига, регистры, сумматоры; блок формирования временных отсчетов; блок вычисления интерполирующего полинома. 2 ил.

Устройство для изменения частоты дискретизации в многоканальных цифровых приемниках, содержащее блок вычисления коэффициентов полинома (БВКП); линию задержки; блок формирования временных отсчетов (БФВО); блок вычисления интерполирующего полинома (БВИП), отличающееся тем, что блок вычисления коэффициентов полинома (БВКП) содержит вычислители, каждый вычислитель содержит константный умножитель, устройства сдвига, входы которых объединены между собой, а выходы через регистры подключены на входы двух параллельных сумматоров, выходом каждого константного умножителя является выходной сумматор, входы которого соединены через регистры с выходами двух параллельных сумматоров, каждый вычислитель своими входами подключен к соответствующему отводу линии задержки, а выходом к соответствующему входу БВИП.

| А.Ю | |||

| АБРАМЕНКО, УСТРОЙСТВО ФОРМИРОВАНИЯ УЗКОПОЛОСНЫХ РАДИОСИГНАЛОВ С ИСПОЛЬЗОВАНИЕМ АЛГОРИТМА ОПТИМАЛЬНОЙ ИНТЕРПОЛЯЦИИ | |||

| ТОМСК, 2014 | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| А.Б | |||

| СЕРГИЕНКО, ЦИФРОВАЯ ОБРАБОТКА СИГНАЛОВ | |||

| СПб.: ПИТЕР, 2002, 608 с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2018-04-04—Публикация

2015-03-23—Подача