Изобретение относится к вычислительной технике и может быть использовано при создании устройств обработки изображений и машинной графики.

Известно 03V, позволяющее осуществлять запись и считывание информационного слова из произвольной ячейки в соответствии с адресным кодом, установленным на входах адреса устройства.

Недостатком такого устройства является то, что процедуры заполнения областей памяти однотипной информацией выполняются в нем последовательно слово за словом, а процедура формирования битовых

плоскостей хранящегося в памяти информационного массива выполняется последовательно бит за битом и требует двух циклов обращения к устройству на один бит (чтение ячейки памяти - модификация требуемого бита - запись в ячейку памяти). Здесь и далее под битовой плоскостью следует понимать совокупность одноименных разрядов всех ячеек памяти ОЗУ. Например, 1-я битовая плоскость образована 1-ми разрядами всех ячеек памяти.

Наиболее близким к предлагаемому является устройство, содержащее блоки памяти, адресные входы которых являются адресными входами первой группы устройства, дешифратор, входы которого являются адресными входами второй группы устройства, информационные входы и выходы блоков памяти являются соответственно информационными входами и выходами устройства, элементы И первой группы, элементы И второй группы, причем выходы дешифратора подключены к первым входам соответствующих элементов И первой и второй групп, выходы элементов И первой группы подключены к входам чтения соответствующих блоков памяти, вторые входы элементов И первой группы объединены и являются входом чтения устройства, вторые входы элементов И второй группы объединены и являются входом записи устройства, элементы ИЛИ, выходы которых подключены к входам записи соответствующих блоков памяти, первые входы подключены к выходам элементов VI второй группы, а вторые входы объединены и являются входом групповой записи устройства. Данное устройство обеспечивает запись и считывание информационного слова из произвольной ячейки, а также одновременную запись одного и того же информационного слова в N ячеек, где N - число блоков памяти.

Недостатком известного устройства является то, что процедура формирования битовых плоскостей размещенного в памяти информационного массива может быть выполнено только последовательно бит за битом. При этом на каждый бит приходится два цикла обращения к устройству (чтение содержимого ячейки памяти - модификация требуемого бита - запись в ячейку памяти), Целью изобретения является повышение быстродействия при формировании в памяти битовых плоскостей за счет формирования за один цикл обращения к устройству N-разрядного фрагмента битовой плоскости, где N - разрядность входной информационной шины устройства. Здесь и далее под фрагментом битовой плоскости следует понимать совокупность последовательно расположенных одноразрядных элементов битовой плоскости.

Указанная цель достигается тем, что в устройство, содержащее N блоков памяти,

адресные входы которых объединены и являются адресным входом первой группы устройства, а выходы объединены и являются информационным выходом устройства, дешифратор, N элементов ИЛИ, N элементов

0 И первой группы, N элементов И второй группы, причем первые входы элементов И обеих групп попарно объединены и соединены с соответствующими выходами дешифратора, вторые входы элементов И

5 первой группы объединены и являются входом чтения устройства, а вторые входы элементов И второй группы объединены и являются входом записи устройства, выходы элементов И первой группы соединены с

0 входами чтения блоков памяти, выходы элементов И второй группы соединены с первыми входами элементов ИЛИ, вторые входы которых объединены и являются входом группой записи устройства, введены мультиплек5 сор, формирователь адреса, преобразователь данных, причем первый информационный вход мультиплексора является адресным входом второй группы устройства, управляющие входы мультиплексора и формирователя ад0 реса объединены и соединены с входом группой записи устройства, первый выход формирователя адреса соединен с вторым информационным входом мультиплексора и первым управляющим входом преобразова5 теля данных, второй управляющий вход преобразователя данных является входом режима битовой плоскости устройства, выход мультиплексора соединен с входом дешифратора, фиксатор маски, первый адресный вход

0 которого объединен с адресными входами блоков памяти, второй адресный вход объединен с первым информационным входом мультиплексора, управляющий вход является входом записи в порт устройства, а информационный

5 вход объединен с информационным входом преобразователя данных и является информационным входом устройства, N блоков маски и N регистров, тактовые входы которых соединены с соответствующими выходами

0 дешифратора, информационные входы объединены и соединены с выходом преобразователя данных, а информационные выходы которых соединены с информационными входам соответствующих блоков памяти, выход

5 фиксатора маски соединен с информационными входами блоков маски, первые управля- ющие входы которых соединены с выходами соответствующих элементов ИЛИ, вторые управляющие входы соединены с вторым выходом формирователя адреса, а выходы

соединены с входами записи соответствующих блоков памяти.

Сущность изобретения сводится к следующему. Мультиплексор 6 в зависимости от режима осуществляет передачу на вход дешифратора k-разрядного адреса, вырабатываемого формирователем адреса, или k- младших разрядов адресной шины (k log2N). Необходимость включения в схему мультиплексора б обусловлена тем, что в режимах блочной записи и записи битовой плоскости для выборки блоков памяти используется последовательность k-разряд- ных адресных кодов, вырабатываемых формирователем адреса.

Формирователь 7 адреса вырабатывает в режимах блочной записи и записи битовой плоскости последовательность k-разрядных адресных кодов от 00...О до 11...1, с помощью которой осуществляется последовательная выборка каждого из N регистров 11, фиксирующих данные, подлежащие записи в соответствующие блоки памяти. Кроме того, указанная последовательность используется в преобразователе данных для трансформации входного информационного слова в необходимый формат.

Преобразователь 8 данных осуществляет формирование данных, подлежащих записи в блоки памяти. При этом входное слово в зависимости от режима может либо передаваться на выход преобразователя без изменения, либо трансформироваться в последовательность из N слов в соответствии с определенными правилами в режиме записи битовой плоскости

Фиксатор 9 маски осуществляет защелкивание кода маски, с помощью которого маскируется запись произвольных разрядов во всех N-блоках памяти.

Блоки 10 маски в соответствии с кодом маски осуществляют блокирование записи в произвольные разряды блоков памяти. Наличие в схеме фиксатора маски и блоков маски позволяет в режиме записи битовой плоскости за один цикл обращения к устройству формировать фрагменты любой из N битовых плоскостей или любую их совокупность.

Регистры 11 осуществляют фиксацию данных, подлежащих записи в блоки памяти. Необходимость включения в схему регистров 11 обусловлена тем, что в режимах записи битовой плоскости и блочной записи данные, подлежащие записи в блоки памяти, формируются последовательно, а запись во все блоки памяти осуществляется одновременно по окончании формирования данных для всех блоков. Таким образом, необходимо обеспечить сохранение данных

с момента их формирования до момента записи, что и обеспечивает регистры 11.

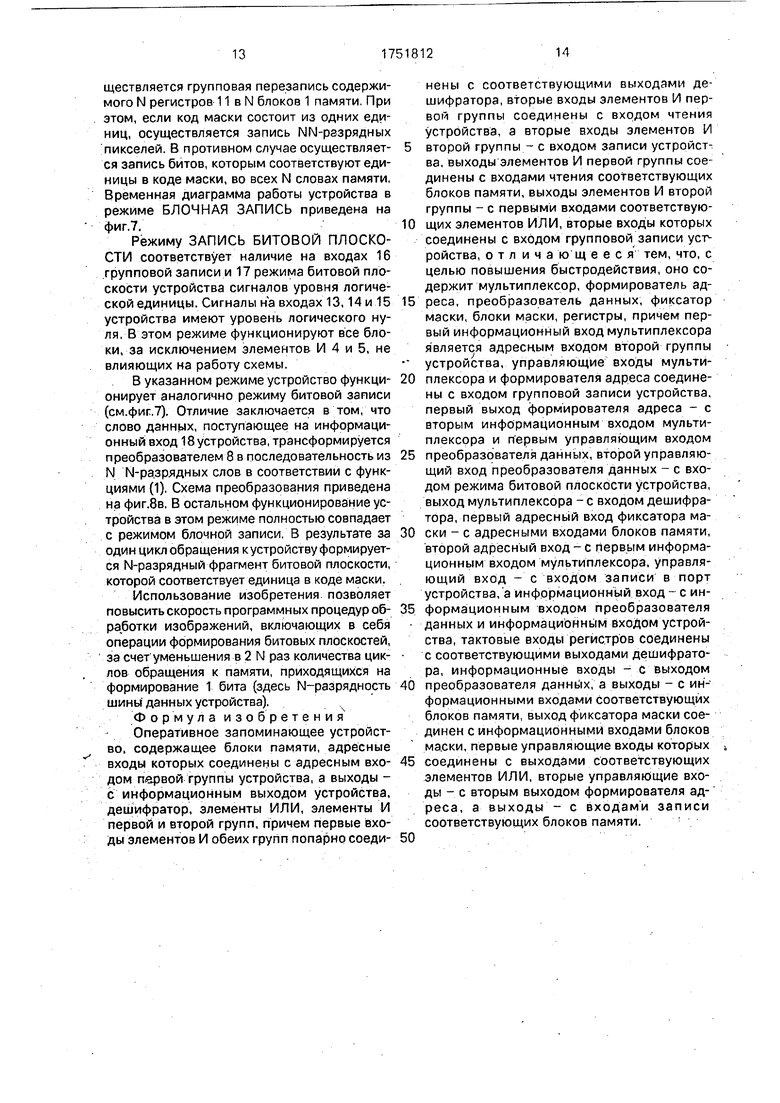

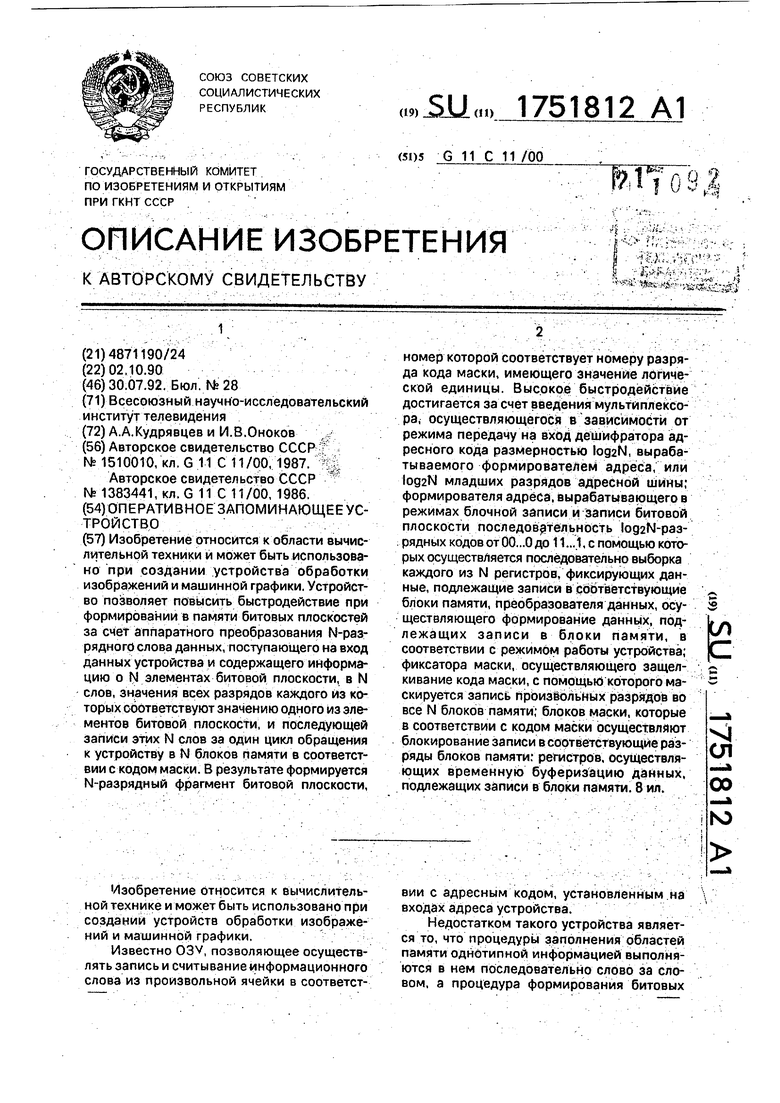

В предлагаемом устройстве производится преобразование N-разрядного слова, 5 поступающего на вход данных устройства, в соответствии со следующими правилами.

При записи пиксела слово данных без трансформации записывается в регистр, соответствующий блоку памяти, номер кото- 10 рого определяется младшими разрядами адресной шины. При блочной записи слово данных последовательно записывается в N регистров, фиксирующих данные, подлежащие записи в N блоков памяти, после чего- 15 происходит одновременная перезапись данных из регистров в соответствующие блоки памяти. При записи битовой плоскости входное слово данных преобразуется в последовательность из N слов таким обра- 0 зом, что первое слово содержит N бит, соответствующих первому разряду входного слова, второе слово содержит N бит, соответствующих второму разряду входного слова, и т.д. по N-e слово включительно. 5 Одновременно с формированием последовательности из N слов осуществляется запись ее в N регистров, фиксирующих данные, подлежащие перезаписи в блоки памяти. По окончании этого процесса происходит одно- 0 временная перезапись данных из регистров в соответствующие блоки памяти.

В зависимости от кода маски при записи содержимого N регистров в N блоков памяти могут быть сформированы N-раз- 5 рядные фрагменты любой из N битовых плоскостей.

Булевы функции, соответствующие описанным преобразованием, имеют следующий ВИД

0Овых1 Овх1 БПЛ VAk«Ak-1-..Ai Овх1х

хОвх1 БПЛ V Ak-APV. Ai Овх2 6HnV...Akx xAk-i...Ai DbVN-1 БПЛ V Ak Ak-j... Ai DexNx хБПЛ; Овьо 2 НОвх2 БПЛ VAkAk-i... DBXJX хБПЛ V Ak Ak-i..AiCex2 БПЛУ..Ас Ak-1...Aix 5 xDexN-- 1 БПЛ VAk .Ai DexN БПЛ; (1)

ОвыхЫ j; DsxN БПЛ V Ak Ak-l... БПЛх хОвх VAk Ak-1.. Ai БПЛ Dsx2 VAk Ak-l...Aix xDsxN БПЛ,

где Овых - 1-й бит выходных данных; 0DBXJ - 1-й бит входных данных;

БПЛ - признак режима битовой плоскости;

А - 1-й бит k-разрядного адресного кода, определяющего номер бита М-разрядно- 5 го фрагмента битовой плоскости ().

Повышение быстродействия устройства при формировании битовых плоскостей достигается за счет того, что N-разрядное слово данных, поступающее на вход устройства и содержащее информацию о N элементах

битовой плоскости, последовательно разворачивается в NN-разрядных слов, значение всех разрядов каждого из которых соответствует значению одного из элементов битовой плоскости, после чего эти N слов одно времен- но записываются в N блоков памяти, При этом в зависимости от содержимого регистра маски за один цикл обращения к устройству формируется N-разрядный фрагмент той или иной битовой плоскости.

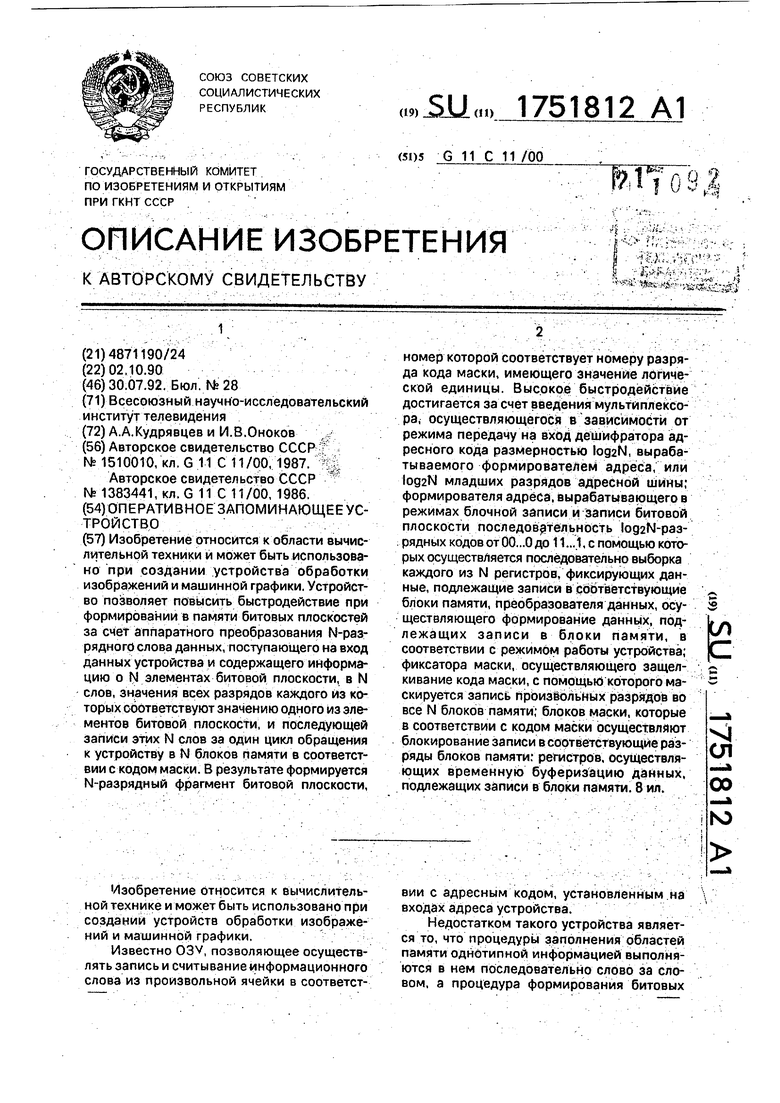

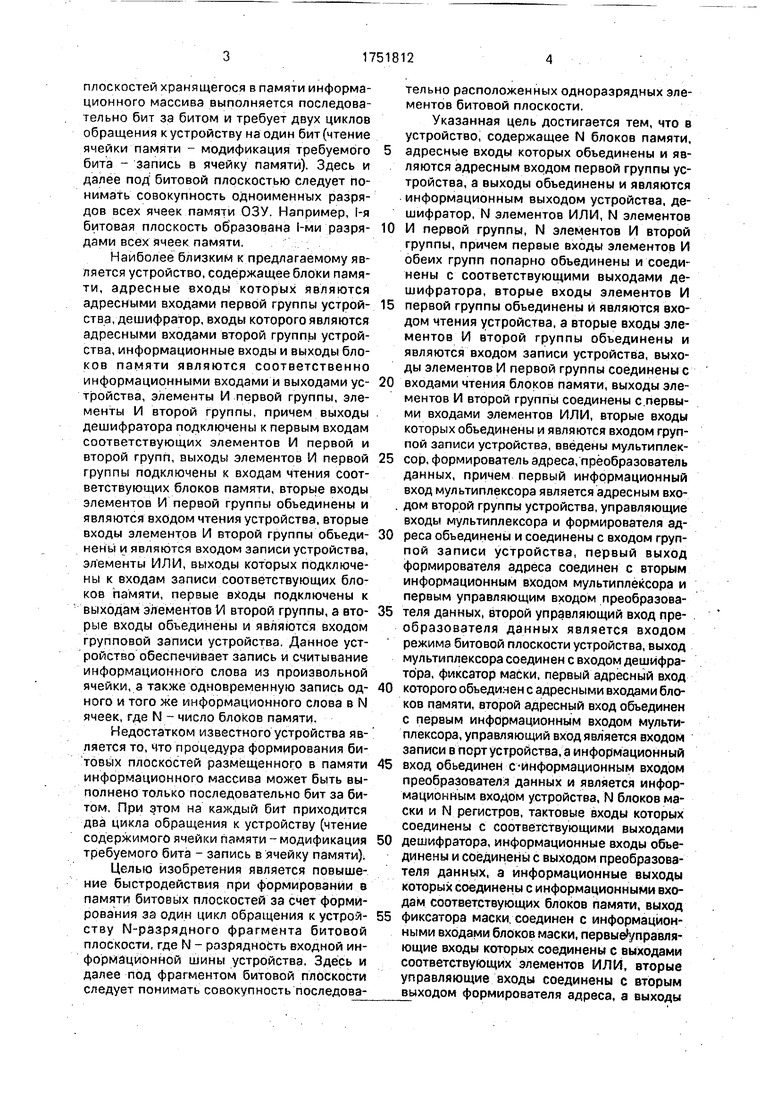

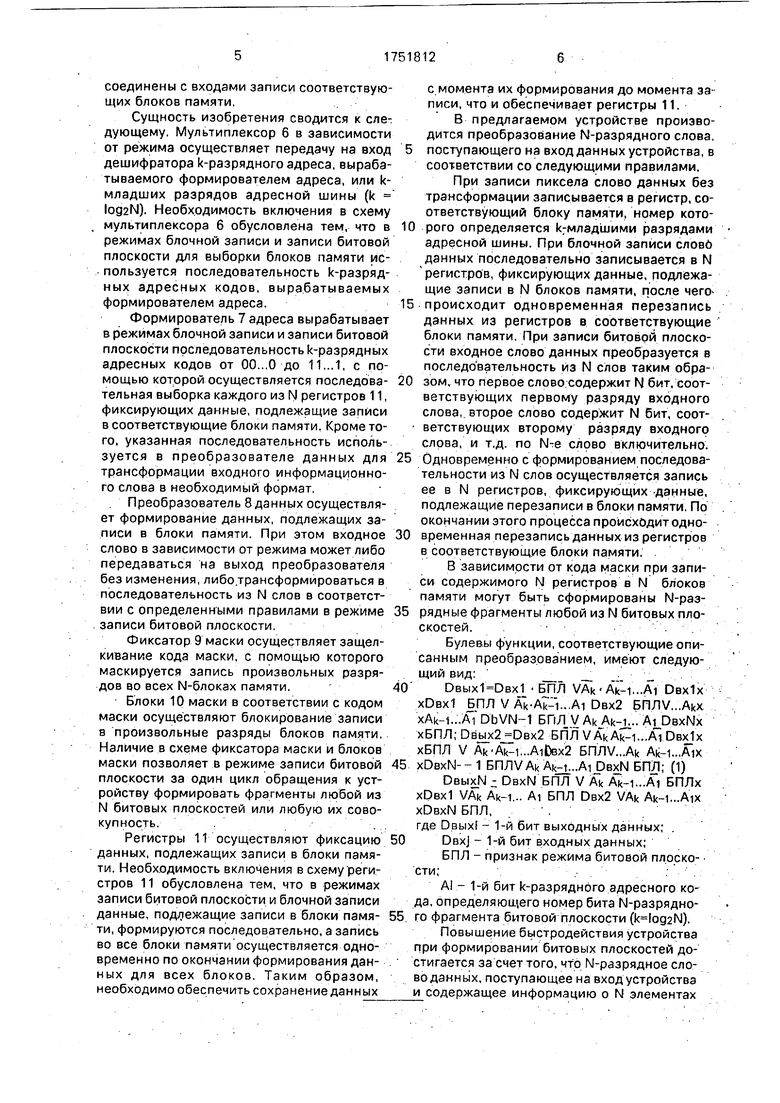

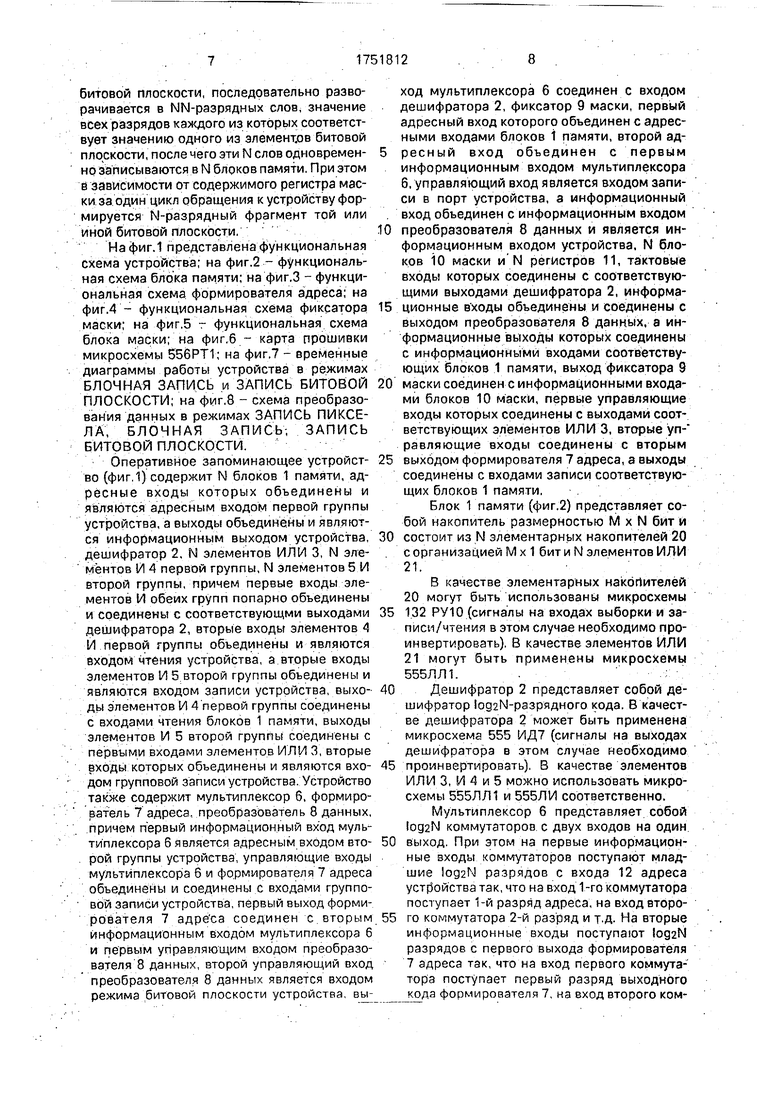

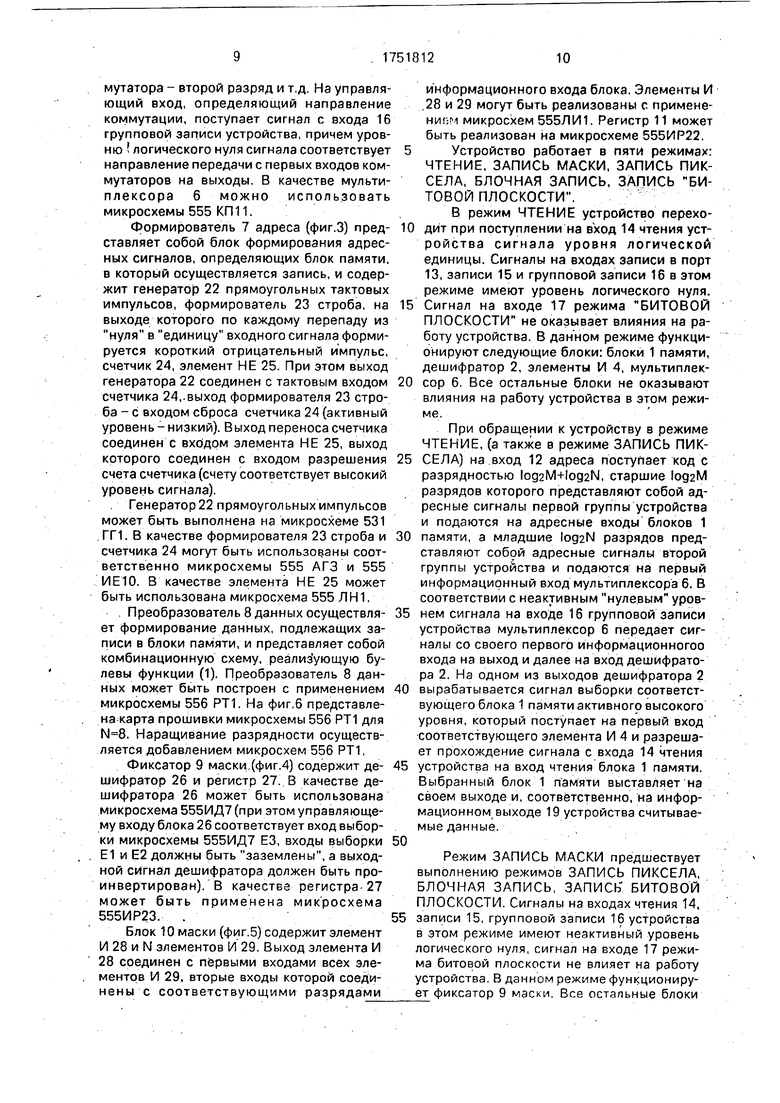

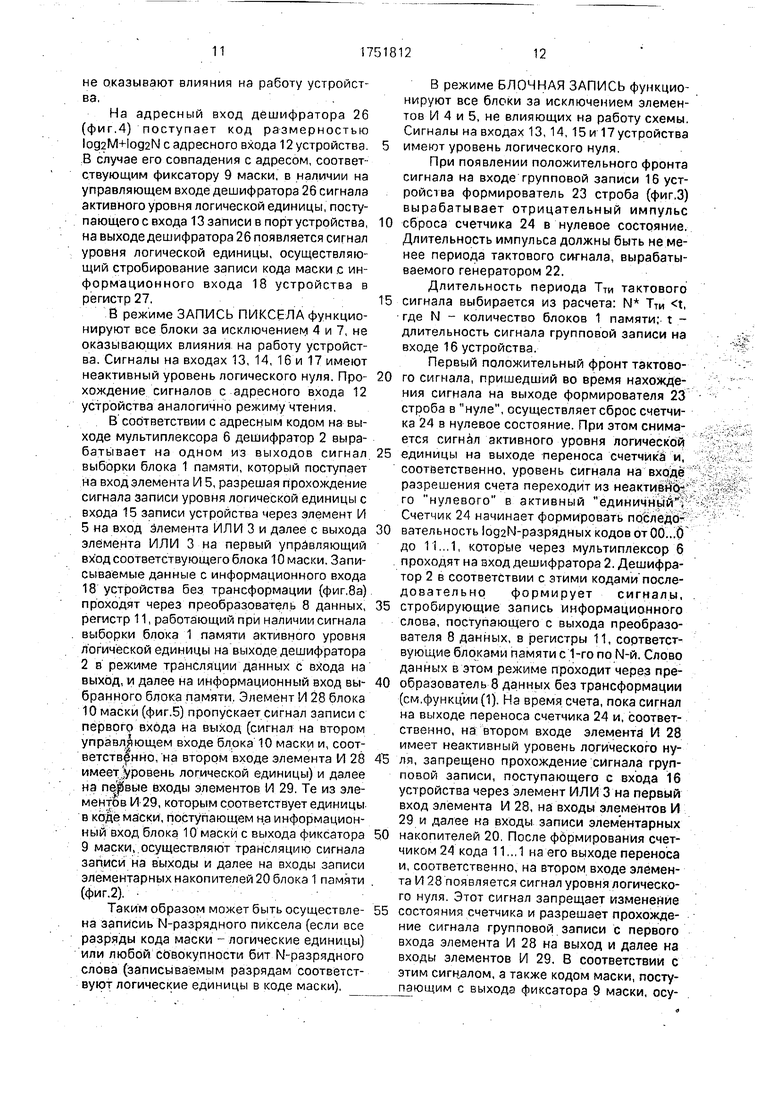

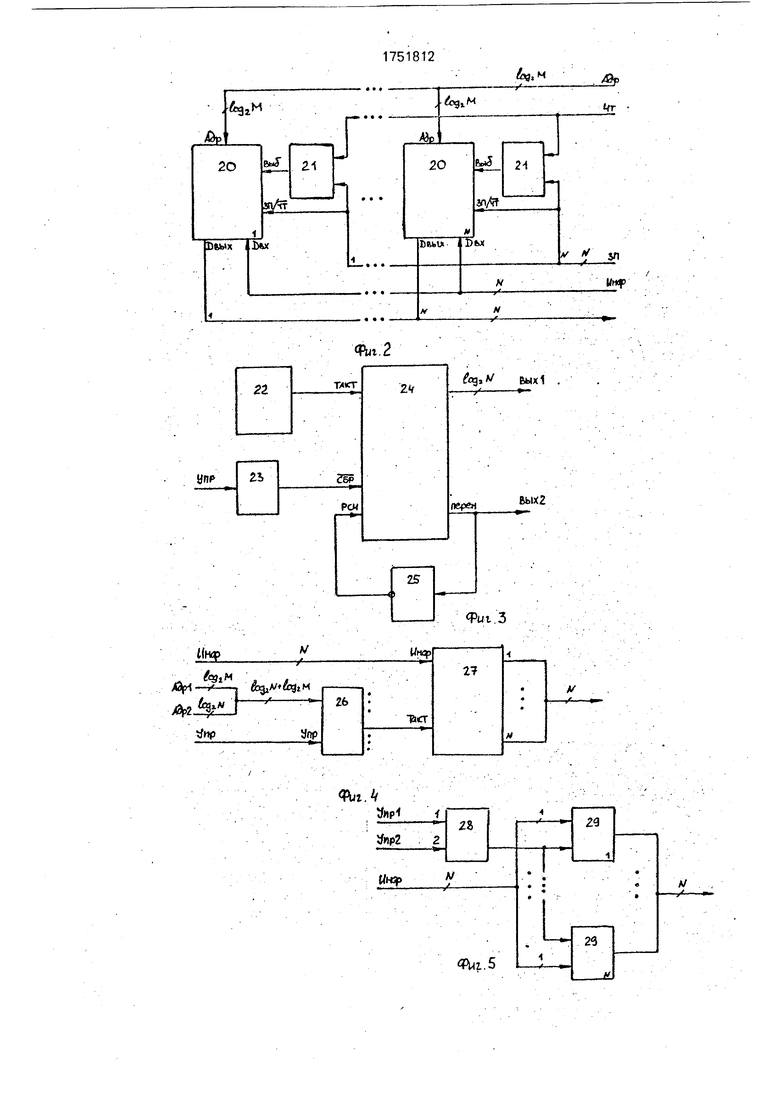

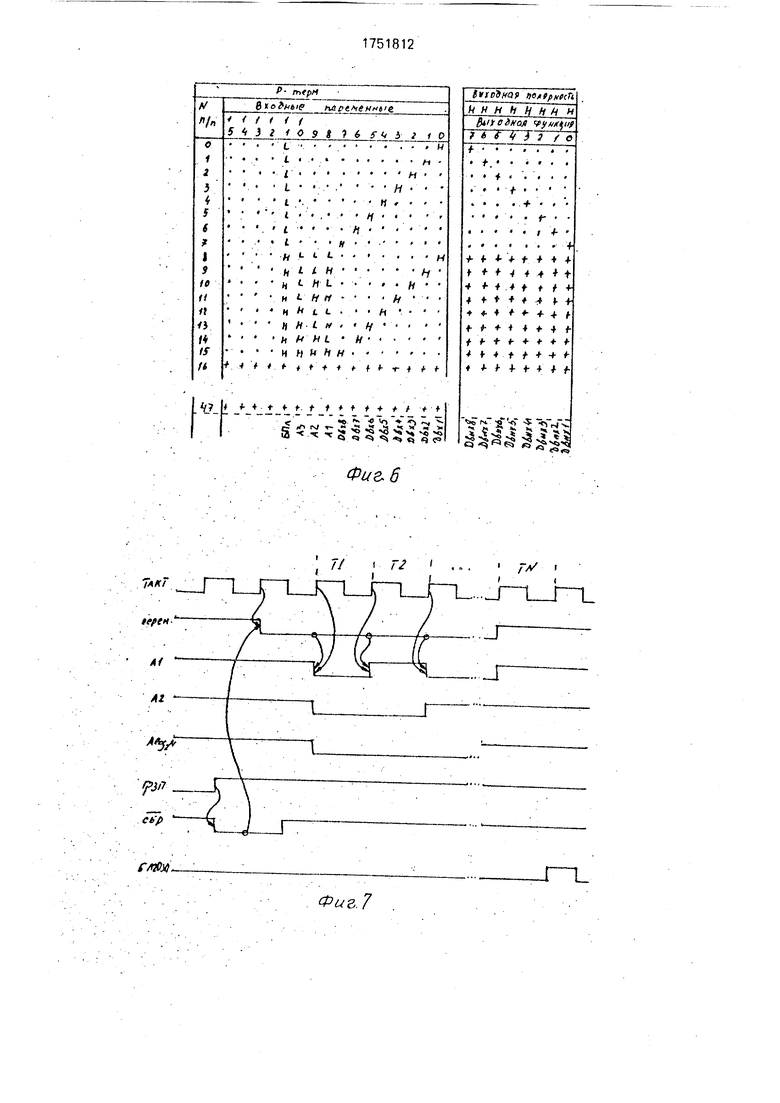

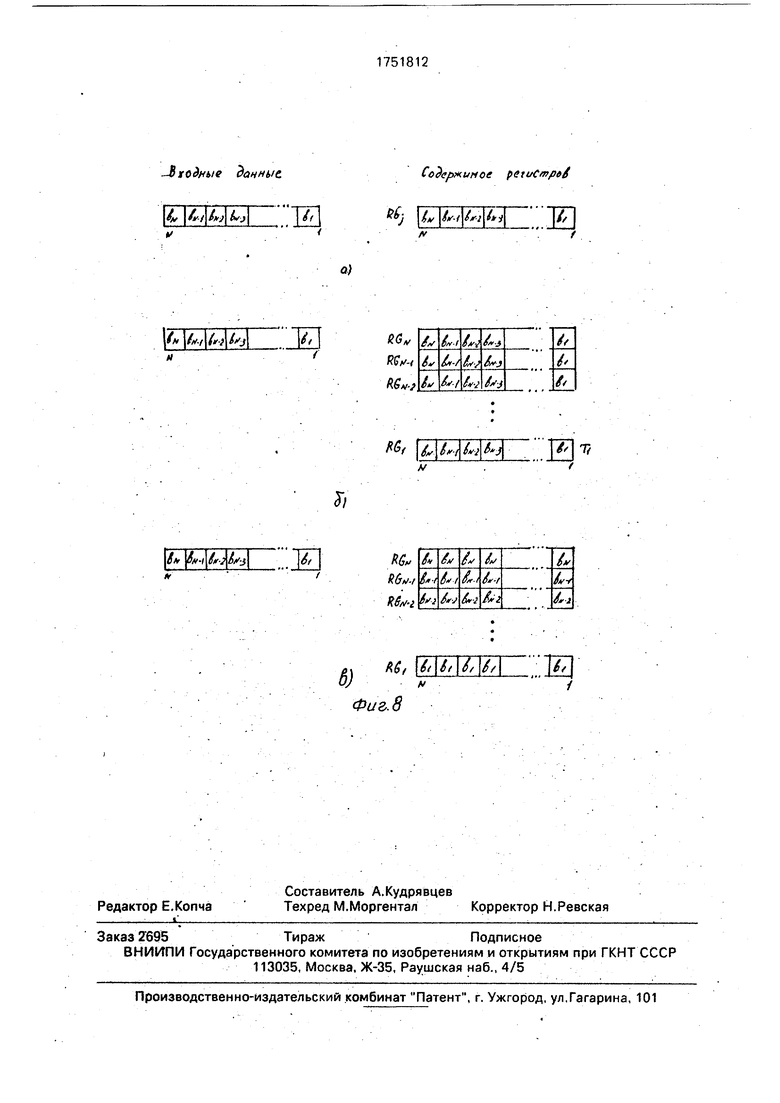

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока памяти; на фиг.З - функциональная схема формирователя адреса; на фиг.4 - функциональная схема фиксатора маски; на фиг.5 - функциональная схема блока маски; на фиг,б - карта прошивки микросхемы 556РТ1; на фиг.7 - временные диаграммы работы устройства в режимах БЛОЧНАЯ ЗАПИСЬ и ЗАПИСЬ БИТОВОЙ ПЛОСКОСТИ; на фиг.8 - схема преобразования данных в режимах ЗАПИСЬ ПИКСЕЛА, БЛОЧНАЯ ЗАПИСЬ, ЗАПИСЬ БИТОВОЙ ПЛОСКОСТИ.

Оперативное запоминающее устройст- во (фиг 1) содержит N блоков 1 памяти, адресные входы которых объединены и являются адресным входом первой группы устройства, а выходы объединены и являются информационным выходом устройства, дешифратор 2, N элементов ИЛИ 3, N элементов И 4 первой группы, N элементов 5 И второй группы, причем первые входы элементов И обеих групп попарно объединены и соединены с соответствующий выходами дешифратора 2, вторые входы элементов 4 И первой группы объединены и являются входом чтения устройства, а вторые входы элементов И 5 второй группы объединены и являются входом записи устройства, выхо- ды элементов И 4 первой группы соединены с входами чтения блоков 1 памяти, выходы элементов И 5 второй группы соединены с первыми входами элементов ИЛИ 3, вторые входы которых объединены и являются вхо- дом групповой записи устройства. Устройство также содержит мультиплексор б, формирователь 7 адреса преобразователь 8 данных, причем первый информационный вход мультиплексора 6 является адресным входом вто- рой группы устройства, управляющие входы мультиплексора б и формирователя 7 адреса объединены и соединены с входами групповой записи устройства, первый выход формирователя 7 адре са соединен с вторым информационным входом мультиплексора 6 и первым управляющим входом преобразователя 8 данных, второй управляющий вход преобразователя 8 данных является входом режима битовой плоскости устройства выход мультиплексора 6 соединен с входом дешифратора 2, фиксатор 9 маски, первый адресный вход которого объединен с адресными входами блоков 1 памяти, второй адресный вход объединен с первым информационным входом мультиплексора 6, управляющий вход является входом записи в порт устройства, а информационный вход объединен с информационным входом преобразователя 8 данных и является информационным входом устройства, N блоков 10 маски и N регистров 11, тактовые входы которых соединены с соответствующими выходами дешифратора 2, информационные входы объединены и соединены с выходом преобразователя 8 данных, а информационные выходы которых соединены с информационными входами соответствующих блоков 1 памяти, выход фиксатора 9 маски соединен с информационными входами блоков 10 маски, первые управляющие входы которых соединены с выходами соответствующих элементов ИЛИ 3, вторые уп- равляющие входы соединены с вторым выходом формирователя 7 адреса, а выходы соединены с входами записи соответствующих блоков 1 памяти.

Блок 1 памяти (фиг.2) представляет собой накопитель размерностью М х N бит и состоит из N элементарных накопителей 20 с организацией М х 1 бит и N элементов ИЛИ 21.

В качестве элементарных накопителей

20могут быть использованы микросхемы 132 РУ10 (сигналы на входах выборки и записи/чтения в этом случае необходимо про- инвертировать). В качестве элементов ИЛИ

21могут быть применены микросхемы 555ЛЛ1.

Дешифратор 2 представляет собой дешифратор 1од2 разрядного кода. В качестве дешифратора 2 может быть применена микросхема 555 ИД7 (сигналы на выходах дешифратора в этом случае необходимо проинвертировать), В качестве элементов ИЛИ 3, И А и 5 можно использовать микросхемы 555ЛЛ1 и 555ЛИ соответственно.

Мультиплексор 6 представляет собой log2N коммутаторов с двух входов на один выход. При этом на первые информационные входы коммутаторов поступают младшие logaN разрядов с входа 12 адреса устройства так, что на вход 1 -го коммутатора поступает 1-й разряд адреса, на вход второго коммутатора 2-й разряд и т.д. На вторые информационные входы поступают IOQ2N разрядов с первого выхода формирователя 7 адреса так, что на вход первого коммутатора поступает первый разряд выходного кола формирователя 7, на вход второго коммутатора - второй разряд и т.д. На управляющий вход, определяющий направление коммутации, поступает сигнал с входа 16 групповой записи устройства, причем уровню логического нуля сигнала соответствует направление передачи с первых входов коммутаторов на выходы. В качестве мультиплексора 6 можно использовать микросхемы 555 КП11.

Формирователь 7 адреса (фиг.З) представляет собой блок формирования адресных сигналов, определяющих блок памяти, в который осуществляется запись, и содержит генератор 22 прямоугольных тактовых импульсов, формирователь 23 строба, на выходе которого по каждому перепаду из нуля в единицу входного сигнала формируется короткий отрицательный импульс, счетчик 24, элемент НЕ 25. При этом выход генератора 22 соединен с тактовым входом счетчика 24,-выход формирователя 23 строба - с входом сброса счетчика 24 (активный уровень - низкий). Выход переноса счетчика соединен с входом элемента НЕ 25, выход которого соединен с входом разрешения счета счетчика (счету соответствует высокий уровень сигнала).

Генератор 22 прямоугольных импульсов может быть выполнена на микросхеме 531 ГГ1. В качестве формирователя 23 строба и счетчика 24 могут быть использованы соответственно микросхемы 555 АГЗ и 555 НЕЮ. В качестве элемента НЕ 25 может быть использована микросхема 555 ЛН1.

Преобразователь 8 данных осуществляет формирование данных, подлежащих записи в блоки памяти, и представляет собой комбинационную схему, реализующую булевы функции (1). Преобразователь 8 данных может быть построен с применением микросхемы 556 РТ1. На фиг,6 представлена карта прошивки микросхемы 556 РТ1 для . Наращивание разрядности осуществляется добавлением микросхем 556 РТ1.

Фиксатор 9 маски (фиг.4) содержит дешифратор 26 и регистр 27. В качестве дешифратора 26 может быть использована микросхема 555ИД7 (при этом управляющему входу блока 26 соответствует вход выборки микросхемы 555ИД7 ЕЗ, входы выборки Е1 и Е2 должны быть заземлены, а выходной сигнал дешифратора должен быть про- инвертирован). В качества регистра 27 может быть применена микросхема 555ИР23. .

Блок 10 маски (фиг.5) содержит элемент И 28 и N элементов И 29. Выход элемента И 28 соединен с первыми входами всех элементов И 29, вторые входы которой соединены с соответствующими разрядами

информационного входа блока. Элементы И 28 и 29 могут быть реализованы с применением микросхем 555ЛИ1. Регистр 11 может быть реализован на микросхеме 555ИР22, 5Устройство работает в пяти режимах:

ЧТЕНИЕ, ЗАПИСЬ МАСКИ, ЗАПИСЬ ПИКСЕЛА, БЛОЧНАЯ ЗАПИСЬ, ЗАПИСЬ БИТОВОЙ ПЛОСКОСТИ.

В режим ЧТЕНИЕ устройство перехо10 дит при поступлении на вход 14 чтения устройства сигнала уровня логической единицы. Сигналы на входах записи в порт 13, записи 15 и групповой записи 16 в этом режиме имеют уровень логического нуля.

15 Сигнал на входе 17 режима БИТОВОЙ ПЛОСКОСТИ не оказывает влияния на работу устройства. В данном режиме функционируют следующие блоки: блоки 1 памяти, дешифратор 2, элементы И 4, мультиплек0 сор 6. Все остальные блоки не оказывают влияния на работу устройства в этом режиме.

При обращении к устройству в режиме ЧТЕНИЕ, (а также в режиме ЗАПИСЬ ПИК5 СЕЛА) на вход 12 адреса поступает код с разрядностью log2M+log2N, старшие logaM разрядов которого представляют собой адресные сигналы первой группы устройства и подаются на адресные входы блоков 1

0 памяти, а младшие logaN разрядов представляют собой адресные сигналы второй группы устройства и подаются на первый информационный вход мультиплексора 6. В соответствии с неактивным нулевым уров5 нем сигнала на входе 16 групповой записи устройства мультиплексор 6 передает сигналы со своего первого информационногоо входа на выход и далее на вход дешифратора 2. На одном из выходов дешифратора 2

0 вырабатывается сигнал выборки соответствующего блока 1 памяти активного высокого уровня, который поступает на первый вход соответствующего элемента И 4 и разрешает прохождение сигнала с входа 14 чтения

5 устройства на вход чтения блока 1 памяти. Выбранный блок 1 памяти выставляет на своем выходе и, соответственно, на информационном выходе 19 устройства считываемые данные.

0

Режим ЗАПИСЬ МАСКИ предшествует выполнению режимов ЗАПИСЬ ПИКСЕЛА, БЛОЧНАЯ ЗАПИСЬ, ЗАПИСЬ БИТОВОЙ ПЛОСКОСТИ. Сигналы на входах чтения 14,

5 записи 15, групповой записи 16 устройства в этом режиме имеют неактивный уровень логического нуля, сигнал на входе 17 режима битовой плоскости не влияет на работу устройства В данном режиме функционирует фиксатор 9 маски. Все остальные блоки

не оказывают влияния на работу устройства,

На адресный вход дешифратора 26 (фиг.4) поступает код размерностью log2M+log2N с адресного входа 12 устройства В случае его совпадения с адресом, соответствующим фиксатору 9 маски, в наличии на управляющем входе дешифратора 26 сигнала активного уровня логической единицы, поступающего с входа 13 записи в порт устройства, на выходе дешифратора 26 появляется сигнал уровня логической единицы, осуществляющий стробирование записи кода маски с информационного входа 18 устройства в регистр 27,

В режиме ЗАПИСЬ ПИКСЕЛА функционируют все блоки за исключением 4 и 7, не оказывающих влияния на работу устройства. Сигналы на входах 13, 14, 16 и 17 имеют неактивный уровень логического нуля. Прохождение сигналов с адресного входа 12 устройства аналогично режиму чтения,

В соответствии с адресным кодом на выходе мультиплексора 6 дешифратор 2 вырабатывает на одном из выходов сигнал выборки блока 1 памяти, который поступает на вход элемента И 5, разрешая прохождение сигнала записи уровня логической единицы с входа 15 записи устройства через элемент И 5 на вход элемента ИЛИ 3 и далее с выхода элемента ИЛИ 3 на первый управляющий вход соответствующего блока 10 маски. Записываемые данные с информационного входа 18 устройства без трансформации (фиг.8а) проходят через преобразователь 8 данных, регистр 11, работающий при наличии сигнала выборки блока 1 памяти активного уровня логической единицы на выходе дешифратора 2 в режиме трансляции данных с входа на выход, и далее на информационный вход выбранного блока памяти. Элемент И 28 блока 10 маски (фиг.5) пропускает сигнал записи с первого входа на выход (сигнал на втором управляющем входе блока 10 маски и, соот- ветств нно, на втором входе элемента И 28 имеет уровень логической единицы) и далее на первые входы элементов И 29. Те из элементов И 29, которым соответствует единицы в коде маски, поступающем на информационный вход блока 10 маски с выхода фиксатора 9 маски, осуществляют трансляцию сигнала записи на выходы и далее на входы записи элементарных накопителей 20 блока 1 памяти (фиг.2).

Таким образом может быть осуществлена записиь N-разрядного пиксела (если все разряды кода маски - логические единицы) или любой совокупности бит М-разрядного слова (записываемым разрядам соответствуют логические единицы в коде маски),

В режиме БЛОЧНАЯ ЗАПИСЬ функционируют все блоки за исключением элементов И 4 и 5, не влияющих на работу схемы. Сигналы на входах 13,14, 15 и 17 устройства

имеют уровень логического нуля.

При появлении положительного фронта сигнала на входе групповой записи 16 устройства формирователь 23 строба (фиг.З) вырабатывает отрицательный импульс

сброса счетчика 24 в нулевое состояние. Длительность импульса должны быть не менее периода тактового сигнала, вырабатываемого генератором 22.

Длительность периода Т™ тактового

сигнала выбирается из расчета: N Т™ t, где N - количество блоков 1 памяти; t - длительность сигнала групповой записи на входе 16 устройства.

Первый положительный фронт тэктового сигнала, пришедший во время нахождения сигнала на выходе формирователя 23 строба в нуле, осуществляет сброс счетчика 24 в нулевое состояние. При этом снимается сигнап активного уровня логической

единицы на выходе переноса счетчика и, соотеетственно, уровень сигнала на входе разрешения счета переходит из неактивйо 1 го нулевого в активный единичный, Счетчик 24 начинает формировать последовательность 1од2М-раарядных кодов от 00...О до 11...1, которые через мультиплексор 6 проходят на вход дешифратора 2. Дешифратор 2 в соответствии с этими кодами после- довательно формирует сигналы,

стробирующие запись информационного слова, поступающего с выхода преобразователя 8 данных, в регистры 11, соответствующие блоками памяти с 1-го по N-й, Слово данных в этом режиме проходит через преобразователь 8 данных без трансформации (см.функции (1). На время счета, пока сигнал на выходе переноса счетчика 24 и, соответственно, на втором входе элемента И 28 имеет неактивный уровень логического нуля, запрещено прохождение сигнала групповой записи, поступающего с входа 16 устройства через элемент ИЛИ 3 на первый вход элемента И 28, на входы элементов И 29 и далее на входы записи элементарных

накопителей 20. После формирования счетчиком 24 кода 11...1 на его выходе переноса и, соответственно, на втором входе элемента И 28 появляется сигнал уровня логического нуля. Этот сигнал запрещает изменение

состояния счетчика и разрешает прохождение сигнала групповой записи с первого входа элемента И 28 на выход и далее на входы элементов И 29, В соответствии с этим сигналом, а также кодом маски, постулающим с выхода фиксатора 9 маски, осуществляется групповая перезапись содержимого N регистров 11 в N блоков 1 памяти. При этом, если код маски состоит из одних единиц, осуществляется запись NN-рззрядных пикселей. В противном случае осуществляет- 5 ся запись битов, которым соответствуют единицы в коде маски, во всех N словах памяти. Временная диаграмма работы устройства в режиме БЛОЧНАЯ ЗАПИСЬ приведена на фиг.7.10

Режиму ЗАПИСЬ БИТОВОЙ ПЛОСКОСТИ соответствует наличие на входах 16 групповой записи и 17 режима битовой плоскости устройства сигналов уровня логической единицы. Сигналы на входах 13,14 и 15 15 устройства имеют уровень логического нуля, В этом режиме функционируют все блоки, за исключением элементов И 4 и 5, не влияющих на работу схемы.

В указанном режиме устройство функци- 20 онирует аналогично режиму битовой записи (см.фиг.7). Отличие заключается в том, что слово данных, поступающее на информационный вход 18 устройства, трансформируется преобразователем 8 в последовательность из 25 N N-разрядных слов в соответствии с функциями (1). Схема преобразования приведена на фиг.8в, В остальном функционирование устройства в этом режиме полностью совпадает с режимом блочной записи. В результате за 30 один цикл обращения к устройству формируется N-разрядный фрагмент битовой плоскости, которой соответствует единица в коде маски.

Использование изобретения позволяет повысить скорость программных процедур об- 35 работки изображений, включающих в себя операции формирования битовых плоскостей, за счет уменьшения в 2 N раз количества цик- лов обращения к памяти, приходящихся на формирование 1 бита (здесь N-разрядность 40 шины данных устройства).

Формула изобретения4

Оперативное запоминающее устройство, содержащее блоки памяти, адресные входы которых соединены с адресным вхо- 45 дом парвой группы устройства, а выходы - с информационным выходом устройства, дешифратор, элементы ИЛИ, элементы И первой и второй групп, причем первые входы элементов И обеих групп попарно соеди- 50

нены с соответствующими выходами дешифратора, вторые входы элементов И первой группы соединены с входом чтения устройства, а вторые входы элементов И второй группы - с входом записи устройства, выходы элементов И первой группы соединены с входами чтения соответствующих блоков памяти, выходы элементов И второй группы - с первыми входами соответствующих элементов ИЛИ, вторые входы которых соединены с входом групповой записи устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит мультиплексор, формирователь адреса, преобразователь данных, фиксатор маски, блоки маски, регистры, причем первый информационный вход мультиплексора является адресным входом второй группы устройства, управляющие входы мультиплексора и формирователя адреса соединены с входом групповой записи устройства, первый выход формирователя адреса - с вторым информационным входом мультиплексора и первым управляющим входом преобразователя данных, второй управляющий вход преобразователя данных - с входом режима битовой плоскости устройства, выход мультиплексора - с входом дешифратора, первый адресный вход фиксатора маски - с адресными входами блоков памяти, второй адресный вход - с первым информационным входом мультиплексора, управляющий вход - с входом записи в порт устройства, а информационный вход- с информационным входом преобразователя данных и информационным входом устройства, тактовые входы регистров соединены с соответствующими выходами дешифратора, информационные входы - с выходом преобразователя данных, а выходы - с информационными входами соответствующих блоков памяти, выход фиксатора маски соединен с информационными входами блоков маски, первые управляющие входы которых соединены с выходами соответствующих элементов ИЛИ, вторые управляющие входы - с вторым выходом формирователя адреса, а выходы - с входами записи соответствующих блоков памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании устройства обработки изображений и машинной графики. Устройство позволяет повысить быстродействие при формировании в памяти битовых плоскостей за счет аппаратного преобразования N-раз- рядного слова данных, поступающего на вход данных устройства и содержащего информацию о N элементах битовой плоскости, в N слов, значения всех разрядов каждого из которых соответствуют значению одного из элементов битовой плоскости, и последующей записи этих N слов за один цикл обращения к устройству в N блоков памяти в соответствии с кодом маски. В результате формируется N-разрядный фрагмент битовой плоскости, номер которой соответствует номеру разряда кода маски, имеющего значение логической единицы. Высокое быстродействие достигается за счет введения мультиплексора, осуществляющегося в зависимости от режима передачу на вход дешифратора адресного кода размерностью logaN, вырабатываемого формирователем адреса, или log2N младших разрядов адресной шины; формирователя адреса, вырабатывающего в режимах блочной записи и записи битовой плоскости последовательность logaN-pas- рядных кодов от 00. ..О до 11... 1, с помощью которых осуществляется последовательно выборка каждого из N регистров, фиксирующих данные, подлежащие записи в соответствующие блоки памяти, преобразователя данных, осуществляющего формирование данных, подлежащих записи в блоки памяти, в соответствии с режимом работы устройства; фиксатора маски, осуществляющего защелкивание кода маски, с помощью которого маскируется запись произвольных разрядов во все N блоков памяти; блоков маски, которые в соответствии с кодом маски осуществляют блокирование записи в соответствующие разряды блоков памяти; регистров, осуществляющих временную буферизацию данных, подлежащих записи в блоки памяти. 8 ил. V| СП 00 го

ft

--Г N

И«А

K fty

21819 1

сЫ«

г

CM 00

in f-Brofauf данные.

6,

б)

Фиг.8

W, f

Содержимое pciuCmpet

MI W

L

t

M @5ЖМ,.И 7

л

W, ,f,

Ј)

| Запоминающее устройство | 1987 |

|

SU1510010A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1383441A1 |

Авторы

Даты

1992-07-30—Публикация

1990-10-02—Подача