Изобретение относится к вычислительной технике и может быть использовано в системах различного назначения, где требуется высокая надежность и радиационная стойкость. Основное предназначение - это ракетно-космическая техника, где кроме высокой надежности и радиационной стойкости требуется минимальное время на подключение резервного канала.

Известны [1, 2] резервированные вычислительные системы, в которых резервные каналы (элементы каналов), так же как и основного канала, находятся в рабочем состоянии («горячий» резерв). Подключение резервного канала, в случае отказа основного, позволяет повысить надежность системы. Кроме того, при «горячем» резерве обеспечивается быстрое использование результатов вычислений резервного канала. Однако такие системы не могут обеспечить высокую радиационную стойкость, так как элементы всех каналов находятся в рабочем состоянии и одинаково подвержены радиационным воздействиям.

Известна многоканальная резервированная вычислительная система, в которой резервный канал находится в выключенном состоянии (в «холодном» резерве) [3] и подключается при отказе основного. Использование «холодного» резервирования позволяет обеспечить высокую надежность, отказоустойчивость и радиационную стойкость, но применение систем с «холодным» резервом ограничивается большим временем подключения резервного канала. Основная составляющая времени подключения резервного канала определяется временем загрузки программного обеспечения. Кроме того, время подключения зависит от быстродействия используемого процессора, памяти (постоянного запоминающего устройства, оперативного запоминающего устройства), времени решения диагностической задачи и времени подключения напряжения питания от вторичного источника.

К некоторым системам управления [4], предназначенным для работы в условиях космического пространства, предъявляются повышенные требования по надежности, отказоустойчивости и радиационной стойкости. Одновременное выполнение указанных требований может быть обеспечено при использовании систем, в которых резервные каналы находятся в выключенном состоянии.

Однако применение «холодного» резервирования ограничивается требованиями к системам управления в части обеспечения непрерывности процесса управления.

Резервированная двухпроцессорная вычислительная система [1] (прототип), содержащая два идентичных канала, каждый из которых имеет в своем составе источник вторичного питания, процессор, системный генератор, схему начальной установки, коммутаторы, временной анализатор исправности, включающий в себя устройство аварийного запуска, импульсный генератор, временной анализатор исправности, счетчик сбоев, триггер, логический элемент ИЛИ, логический элемент ИЛИ-НЕ, в систему также входит схема сравнения. Процессор соединен с системным генератором, схемой начальной установки, временным анализатором исправности, первым и вторым коммутатором, первый коммутатор соединен со вторым коммутатором, который соединен с третьим коммутатором и устройством памяти. Процессор первого канала соединен с вторым коммутатором второго канала. Схема сравнения соединена с временным анализатором исправности первого и второго каналов. Выходы первых коммутаторов каналов соединены и являются выходом системы.

Система, в которой основной и резервный канал находятся в рабочем состоянии, может обеспечить быстрое подключение к выходу результатов вычислений резервного канала, но не может сохранить работоспособность в течение длительного срока эксплуатации в условиях радиационных воздействий, так как элементы активных каналов одинаково подвержены выходу из строя.

Техническим результатом предлагаемого решения является сокращение времени задействования резервной системы, находящейся в выключенном состоянии, при одновременном обеспечении высокой надежности, отказоустойчивости и радиационной стойкости.

Технический результат достигается тем, что в самодиагностируемую бортовую вычислительную систему с резервированием замещением, содержащую основную систему, включающую два идентичных канала основной и резервный, в каждом из которых имеется источник вторичного питания, процессор, системный генератор, схема начальной установки, коммутатор, при этом первый выход процессора подключен к входу коммутатора, выход системного генератора подключен к первому входу процессора, выход схемы начальной установки подключен ко второму входу процессора, выход коммутатора основного канала и выход коммутатора резервного канала объединен и является выходом информационных данных системы, введена аналогичная резервная система, а в каждый канал введена схема подключения вторичного питания, устройство резервирования. В каждом канале первый вход устройства резервирования подключен ко второму выходу процессора, второй вход устройства резервирования подключен ко второму выходу системного генератора. Третий вход устройства резервирования и второй вход коммутатора подключены к выходу схемы начальной установки. Выход источника вторичного питания подключен к первому входу схемы подключения вторичного питания. Вход источника вторичного питания подключен к выходу источника первичного питания. Кроме того, первый выход устройства резервирования основного канала основной системы подключен к третьему входу коммутатора основного канала основной системы. Второй выход устройства резервирования основного канала основной системы подключен к третьему входу коммутатора резервного канала основной системы и второму входу схемы подключения вторичного питания основного канала основной системы. Первый выход устройства резервирования резервного канала основной системы подключен ко второму входу схемы подключения вторичного питания резервного канала основной системы. Первый выход устройства резервирования основного канала резервной системы подключен к третьему входу коммутатора основного канала резервной системы. Второй выход устройства резервирования основного канала резервной системы подключен к третьему входу коммутатора резервного канала резервной системы. Четвертый вход коммутатора основного канала резервной системы подключен к первому выходу устройства резервирования резервного канала основной системы. Третий и четвертый выходы устройства резервирования основного канала основной системы подключены соответственно к первому и второму входу схемы подключения вторичного питания основного канала резервной системы и первому и второму входу схемы подключения вторичного питания резервного канала резервной системы. Второй и третий выходы устройства резервирования резервного канала основной системы подключены соответственно к третьему и четвертому входу схемы подключения вторичного питания основного канала резервной системы и третьему и четвертому входу схемы подключения вторичного питания резервного канала резервной системы. Выход основной и выход резервной системы соединены и являются выходом системы.

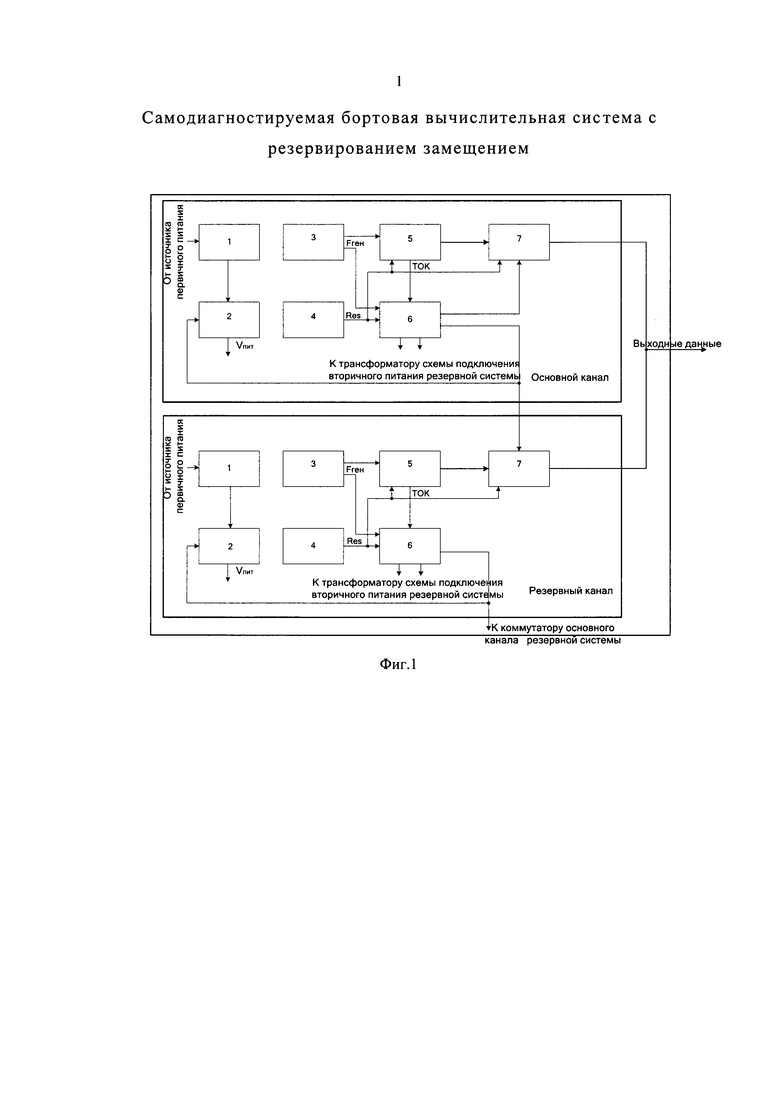

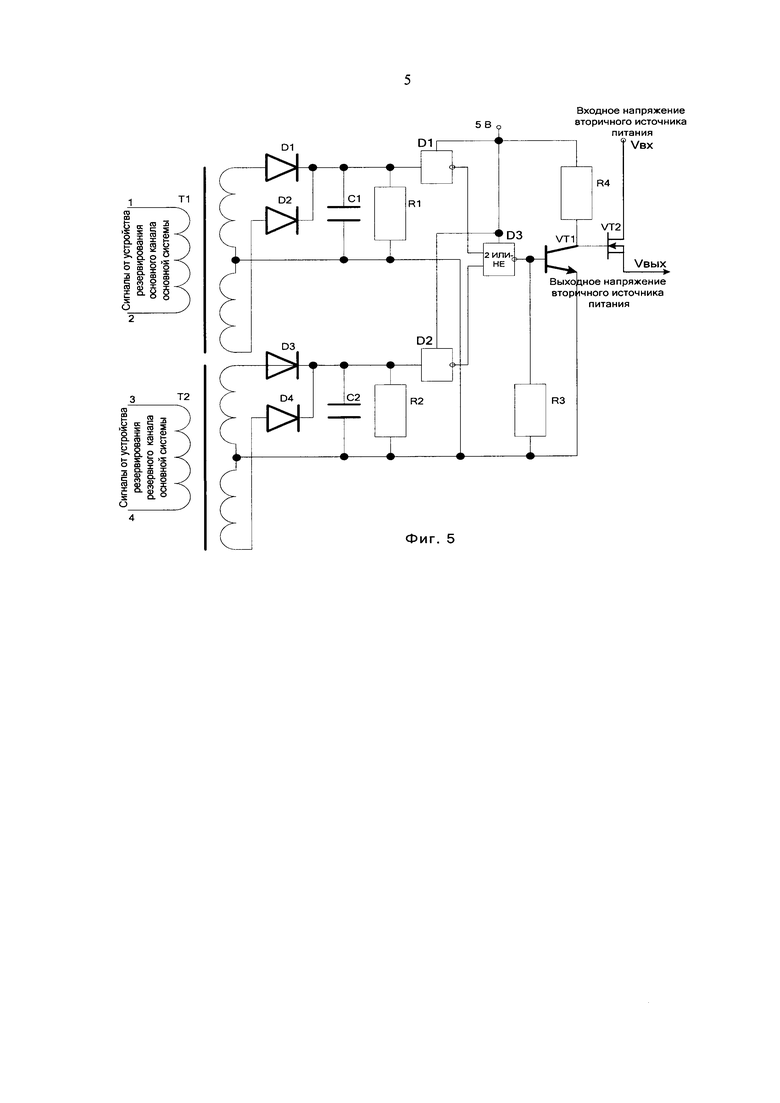

На фиг. 1 приведена структурная схема основной самодиагностируемой бортовой вычислительной системы.

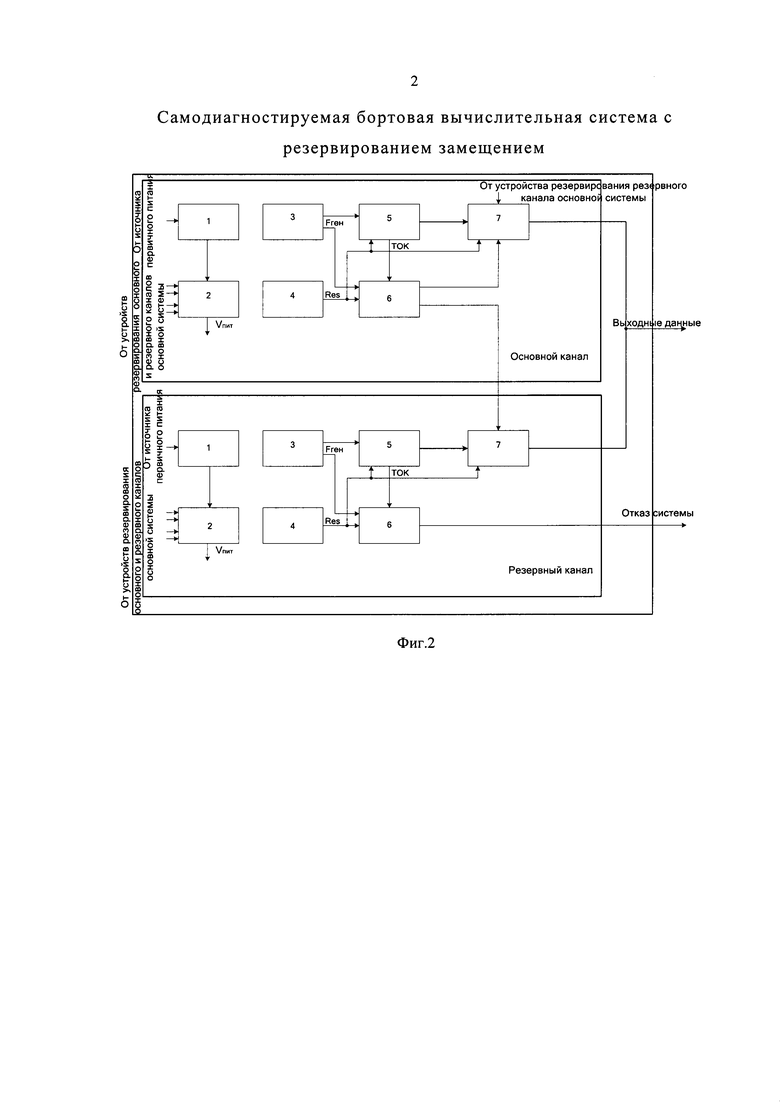

На фиг. 2 приведена структурная схема резервной самодиагностируемой бортовой вычислительной системы, которая аналогична основной системе.

Каждая система содержит два идентичных канала основной и резервный. Каждый канал содержит источник вторичного питания 1, схему подключения вторичного питания 2, системный генератор 3, схему начальной установки 4, процессор 5, устройство резервирования 6, коммутатор 7. В каждом канале источник вторичного питания 1 соединен со схемой подключения вторичного питания 2. Системный генератор 3 соединен с процессором 5, устройством резервирования 6. Схема начальной установки 4 соединена с процессором 5, устройством резервирования 6, коммутатором 7. Процессор 5 соединен с устройством резервирования 6, коммутатором 7. Устройство резервирования 6 соединено с коммутатором 7, схемой подключения вторичного питания 2 основного канала и коммутатором 7 резервного канала.

Кроме того, в системе устройства резервирования 6 основного и резервного каналов основной системы соединены со схемой подключения вторичного питания 2 основного и резервного каналов резервной системы. Выходы коммутаторов 7 всех каналов системы соединены и являются общим выходом.

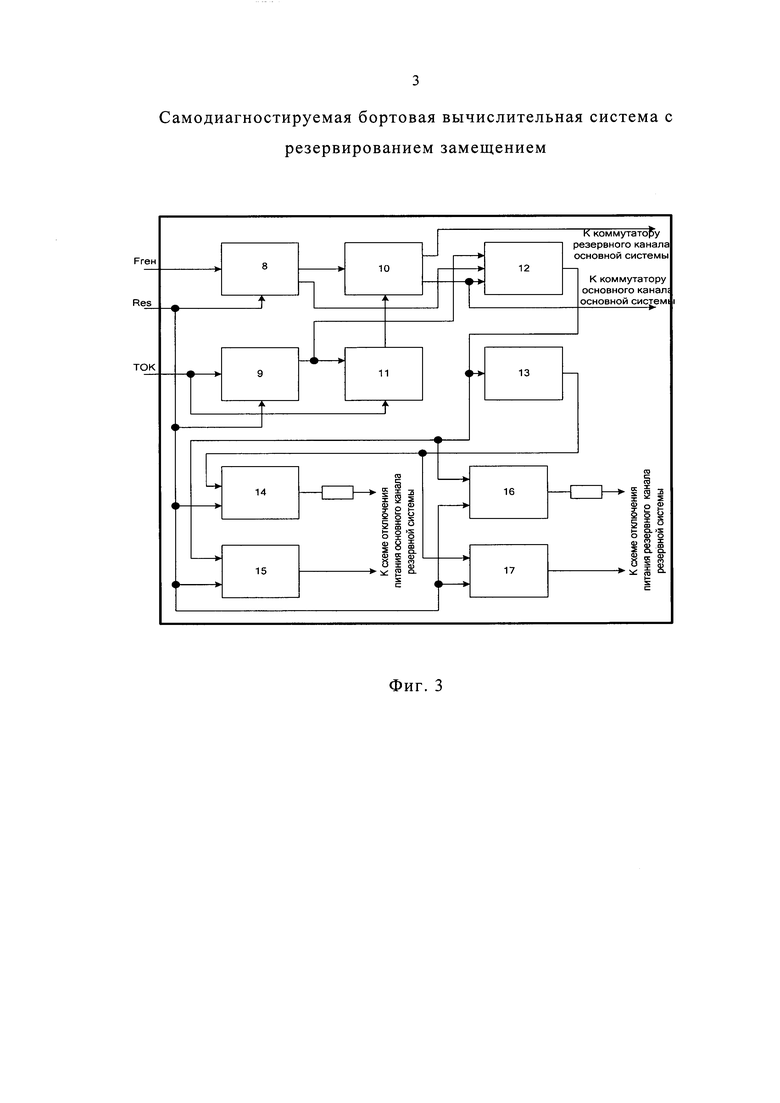

На фиг. 3 приведена структурная схема устройства резервирования.

Устройство резервирования содержит делитель частоты 8, счетчик импульсов 9, счетчик импульсов 10, логический элемент 2И 11, логический элемент 3И 12, логический элемент НЕ 13, логические элементы 2И 14-17.

Делитель частоты 8 соединен со счетчиком импульсов 10, логическим элементом 3И 12. Счетчик импульсов 9 соединен с логическим элементом 2И 11, логическим элементом 3И 12. Счетчик импульсов 10 соединен с логическим элементом 3И 12, логическим элементом 2И 11. Логический элемент 3И 12 соединен с логическим элементом НЕ 13, логическим элементом 2И 15, логическим элементом 2И 16. Логический элемент НЕ 13 соединен с логическим элементом 2И 14, логическим элементом 2И 17. Делитель частоты 8, счетчик импульсов 9, логические элементы 2И 14-17 соединены со схемой начальной установки 4 соответствующего канала. Делитель частоты 8 соединен с системным генератором 3 соответствующего канала.

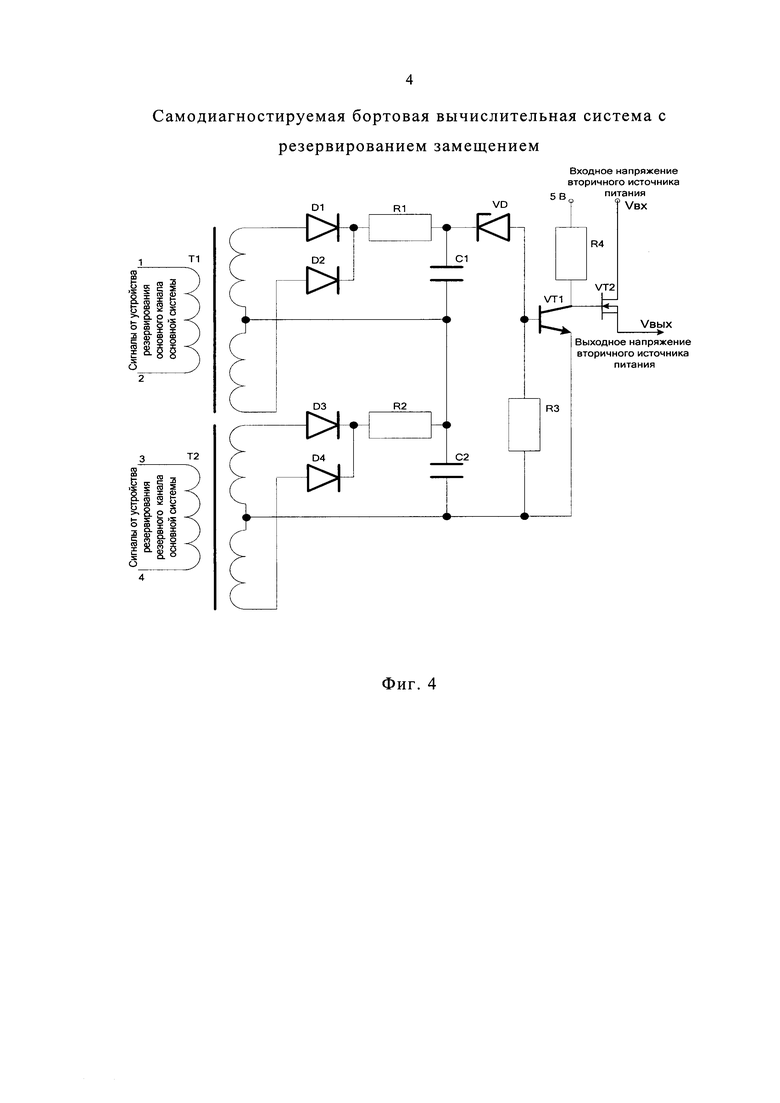

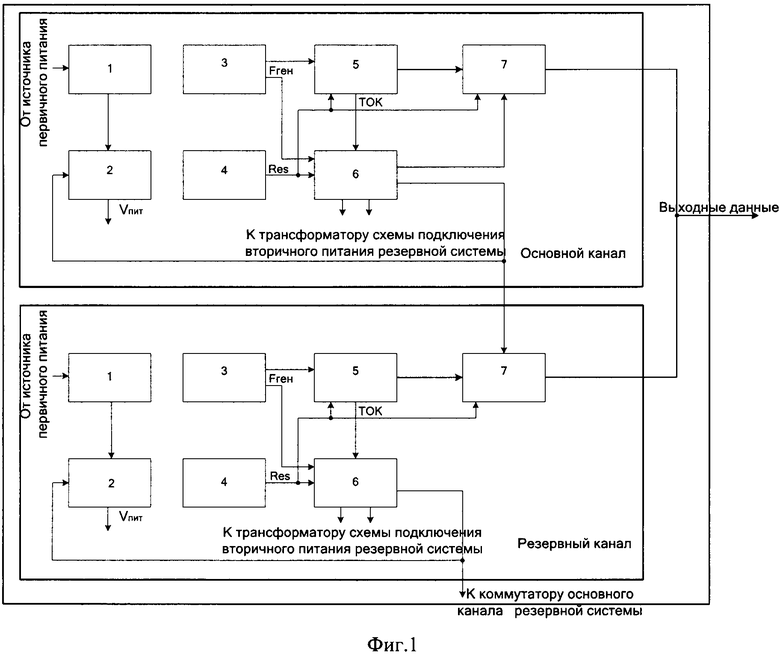

На фиг. 4, фиг. 5 приведены электрические принципиальные схемы подключения питания каналов резервной системы.

Предлагаемая система работает следующим образом.

В момент подачи на систему первичного питания сигналами начальной установки, формируемыми источниками вторичного питания 1, обеспечивается подключение напряжения питания ко всем каналам системы. Схемы начальной установки 4 каждого канала системы формируют сигнал Res установки в исходное состояние устройств резервирования 6, коммутаторов 7 (сигнал Res изменяется из логического «0» в логическую «1»). При достижении каждым сигналом Res определенного значения запускаются процессоры 5 всех каналов. За счет заранее выбранной длительности нарастания сигналов Res начальной установки первыми на режим выходят каналы основной системы и отключается напряжение от каналов резервной системы. При этом соответствующими сигналами с выхода устройства резервирования 6 основного канала основной системы разблокируется коммутатор 7 основного канала основной системы и блокируется коммутатор 7 резервного канала основной системы. При этом к выходу подключаются данные от основного канала основной системы. В случае отказа основного канала основной системы сигнал с устройства резервирования 6 основного канала основной системы изменяется из логического «0» в логическую «1». В этом случае отключается питание от основного канала основной системы, разблокируется коммутатор 7 резервного канала основной системы и к выходу подключаются данные от резервного канала основной системы.

При отказе любого канала основной системы (отсутствии переменного напряжения на одном из трансформаторов схемы подключения напряжения питания на резервную систему) к каналам резервной системы подключается напряжение от соответствующих вторичных источников питания. С данного момента каналы резервной системы находятся в «горячем» резерве с заблокированными коммутаторами.

После отказа резервного канала основной системы соответствующим сигналом с выхода устройства резервирования 6 резервного канала основной системы (логическая «1») отключится напряжение питания от резервного канала основной системы, разблокируется коммутатор 7 основного канала резервной системы и к выходу подключатся данные основного канала резервной системы. При отказе основного канала резервной системы соответствующими сигналами с выхода устройства резервирования 6 основного канала резервной системы заблокируется коммутатор 7 основного канала резервной системы и разблокируется коммутатор 7 резервного канала резервной системы. При этом к выходу подключатся данные резервного канала резервной системы.

Устройства резервирования каналов определяют наличие сигналов исправности (ТОК) соответствующих каналов и период их следования.

На устройства резервирования каналов системы подаются сигналы начальной установки Res (изменяется из «1» в «0»). От системного генератора частоты 3 поступают сигналы Fген. От процессора 5 поступают сигналы исправности канала ТОК, формируемые по результатам самодиагностики.

В момент подачи питания на устройства резервирования счетчик импульсов 9, счетчик импульсов 10 устанавливаются в исходное состояние (на выходе - логический «0»). При достижении сигналом Res определенной величины снимается блокировка со счетчиков 9, 10. После поступления на счетчик 9 определенного количества импульсов исправности ТОК от процессора 5 канала, счетчик 9 закроется по входу и на его «прямом» выходе будет логическая «1». С данного момента счетчик импульсов 10 каждым импульсом ТОК, проходящим через логический элемент 2И 11, будет устанавливаться в исходное состояние (на «прямом» выходе логический «0»). Так как на входы логического элемента 3И 12 поступают сигналы с прямого выхода счетчика импульсов 9 и инверсного выхода счетчика импульсов 10 (логические «1»), то в этом случае частотные сигналы, поступающие на вход логического элемента 3И 12, появятся на его выходе, а также на выходе логического элемента НЕ 13 и выходах логических элементов 2И 14-17. При этом переменное напряжение появится на обмотках трансформаторов T1, Т2 схем подключения питания резервного канала (фиг. 4). Выходное напряжение трансформаторов T1, Т2 преобразуется в постоянное и поступает на первый транзистор VT1, который управляет ключом VT2 коммутации первичного питания. В данном случае напряжение питания отключится от резервных каналов.

Следует отметить, что напряжения питания от каналов резервной системы отключаются при наличии сигналов, поступающих с устройств резервирования 6 основного и резервного каналов основной системы, и подключаются при отсутствии сигналов от устройства резервирования 6 одного из каналов основной системы (при выходе из строя одного из каналов основной системы).

Физическая суть предлагаемого решения заключается в том, что после отказа одного из каналов основной системы подключается резервная система, но к выходу подключаются данные от резервного канала основной системы. В этом случае резервный канал основной системы выполняет функции «подхватывающего» канала. После его отказа к выходу подключатся данные основного канала резервной системы, который уже находился в активном состоянии.

В случае отказа основного канала резервной системы к выходу подключатся данные от резервного канала резервной системы.

Устройство резервирования 6 может быть выполнено с использованием микросхем средней степени интеграции типа 5584, 1594. Счетчики импульсов 9, 10 (с «защелкой), входящие в устройство резервирования, целесообразно реализовать на J-K триггерах 1594 ТВ9Т.

Схема подключения напряжения питания на каналы резервной системы, представленная на фиг. 4, может быть реализована с использованием существующих элементов (трансформаторов, диодов, стабилитронов, конденсаторов, резисторов, транзисторов). В качестве ключа VT2 для подключения напряжения источника вторичного питания целесообразно использовать полевой транзистор типа 2П7190 (АЕЯР.432140.414 ТУ) с управлением логическим сигналом.

Схема подключения напряжения питания на каналы резервной системы, представленная на фиг. 5, может быть реализована добавлением в схему, представленную на фиг. 4, триггера Шмитта-инвертора 5584Л2 (элементы D1, D2) и логического элемента 5584ЛЕ1 (D3).

Использование схемы подключения напряжения питания на каналы, представленной на фиг. 5, позволяет подключать любой канал системы. Для этого необходимо преобразовать сигналы с устройства резервирования основного канала резервной системы в постоянное напряжение и через триггер Шмитта в логический сигнал «0» уровня. В результате логического анализа сигналов с выходов триггеров Шмитта основного канала основной системы, резервного канала основной системы, основного канала резервной системы можно сформировать логический сигнал для подключения/отключения напряжения питания от любого из каналов системы.

Схема подключения напряжения на каналы основной системы может быть реализована с использованием J-K триггера 1594 ТВ9Т и ключа типа 2П7190.

Коммутаторы системы могут быть реализованы с использованием приемопередатчиков типа 5584АП7Т с тремя состояниями на выходе и J-K триггера типа 1594 ТВ9Т.

Источники информации

1. Патент РФ №2460121, МКИ G06F 11/20, 2005 г. (прототип).

2. Антимиров В.М. Бортовые вычислительные системы семейства «Малахит» для работы в экстремальных условиях [Текст] / В.М. Антимиров, А.Б. Уманский, Л.Н. Шалимов // Вестник Самарского государственного аэрокосмического университета. - №4(42), 2013. - С. 19-27.

3. Патент РФ №2527191, МКИ G06F 11/20, 2013 г.

4. Поляхов Н.Д. Обзор способов практического применения активных магнитных подшипников / Н.Д. Поляхов, А.Д. Стоцкая // Научное приборостроение, 2012, том 22, №4, с. 15-18.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная самодиагностируемая вычислительная система с резервированием замещением и способ повышения ее отказоустойчивости (варианты) | 2016 |

|

RU2634189C1 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2460121C1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2011 |

|

RU2481619C1 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

Изобретение относится к вычислительной технике и может быть использовано в системах различного назначения, где требуется высокая надежность и радиационная стойкость. Техническим результатом является сокращение времени задействования резервной системы, находящейся в выключенном состоянии, при одновременном обеспечении высокой надежности, отказоустойчивости и радиационной стойкости. В самодиагностируемую бортовую вычислительную систему, содержащую основную систему, введена аналогичная резервная система, каждая из систем имеет два идентичных канала основной и резервный, в каждый канал введена схема подключения вторичного питания, устройство резервирования. В каждом канале входы устройства резервирования подключены к выходу процессора, к выходу системного генератора, к выходу схемы начальной установки. Выход процессора подключен к входу коммутатора, второй вход которого подключен к выходу схемы начальной установки. Выход источника вторичного питания подключен к входу схемы подключения вторичного питания, а вход - к выходу источника первичного питания. Выходы устройства резервирования основного канала основной системы подключены к третьим входам коммутаторов основного и резервного каналов и ко второму входу схемы подключения вторичного питания основного канала основной системы. Выход устройства резервирования резервного канала основной системы подключен ко второму входу схемы подключения вторичного питания резервного канала основной системы. Выходы устройства резервирования основного канала резервной системы подключены к третьим входам коммутаторов основного и резервного каналов резервной системы. Четвертый вход коммутатора основного канала резервной системы подключен к первому выходу устройства резервирования резервного канала основной системы. Третий и четвертый выходы устройства резервирования основного канала основной системы подключены соответственно к первому и второму входу схемы подключения вторичного питания основного канала резервной системы и первому и второму входу схемы подключения вторичного питания резервного канала резервной системы. Второй и третий выходы устройства резервирования резервного канала основной системы подключены соответственно к третьему и четвертому входу схемы подключения вторичного питания основного канала резервной системы и третьему и четвертому входу схемы подключения вторичного питания резервного канала резервной системы. Выход основной и резервной системы соединены и являются выходом системы. 5 ил.

Самодиагностируемая бортовая вычислительная система с резервированием замещением, содержащая основную систему, включающую два идентичных канала основной и резервный, в каждом из которых имеется источник вторичного питания, процессор, системный генератор, схема начальной установки, коммутатор, при этом первый выход процессора подключен к входу коммутатора, выход системного генератора подключен к первому входу процессора, выход схемы начальной установки подключен ко второму входу процессора, выход коммутатора основного канала и выход коммутатора резервного канала объединен и является выходом информационных данных системы, отличающаяся тем, что в систему введена аналогичная резервная система, а в каждый канал введена схема подключения вторичного питания и устройство резервирования, при этом в каждом канале первый вход устройства резервирования подключен ко второму выходу процессора, второй вход устройства резервирования подключен ко второму выходу системного генератора, третий вход устройства резервирования, второй вход коммутатора подключены к выходу схемы начальной установки, выход источника вторичного питания подключен к первому входу схемы подключения вторичного питания, вход источника вторичного питания подключен к выходу источника первичного питания, кроме того, первый выход устройства резервирования основного канала основной системы подключен к третьему входу коммутатора основного канала основной системы, второй выход устройства резервирования основного канала основной системы подключен к третьему входу коммутатора резервного канала основной системы и второму входу схемы подключения вторичного питания основного канала основной системы, первый выход устройства резервирования резервного канала основной системы подключен ко второму входу схемы подключения вторичного питания резервного канала основной системы, первый выход устройства резервирования основного канала резервной системы подключен к третьему входу коммутатора основного канала резервной системы, второй выход устройства резервирования основного канала резервной системы подключен к третьему входу коммутатора резервного канала резервной системы, четвертый вход коммутатора основного канала резервной системы подключен к первому выходу устройства резервирования резервного канала основной системы, третий и четвертый выходы устройства резервирования основного канала основной системы подключены соответственно к первому и второму входу схемы подключения вторичного питания основного канала резервной системы и первому и второму входу схемы подключения вторичного питания резервного канала резервной системы, второй и третий выходы устройства резервирования резервного канала основной системы подключены соответственно к третьему и четвертому входу схемы подключения вторичного питания основного канала резервной системы и третьему и четвертому входу схемы подключения вторичного питания резервного канала резервной системы, выход основной и выход резервной системы соединены и являются выходом системы.

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2460121C1 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| US 5008805 A, 16.04.1991. | |||

Авторы

Даты

2018-06-08—Публикация

2017-04-17—Подача