Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем.

Известна устойчивая к отказам вычислительная система [1] (аналог). Вычислительная система состоит из двух процессоров (каналов), схемы начальной установки, подключенной к входу процессора каждого канала, системного генератора, выход которого подключен к входу процессора каждого канала, и схемы управления. Каждый процессор может работать в автономном режиме главного процессора и в режиме подчиненного процессора, контролирующего работу другого процессора. В подчиненном режиме процессор выполняет те же инструкции, что и главный процессор, только все линии, по которым осуществляется вывод данных, отключены. Кроме того, в подчиненном режиме схема сравнения, встроенная в процессор, сверяет результаты выходных данных обоих процессоров. Схема управления через определенные интервалы времени осуществляет переключение режимов работы процессоров для контроля процессорами друг друга. Если возникает несоответствие, то подчиненный процессор сигнализирует схеме управления об ошибке. Схема управления пытается восстановить синхронность работы процессоров, вызывая в обоих процессорах внешнее прерывание. Если же процессор вышел из строя и был в это время подчиненным процессором, то в таком случае схема будет работать без подчиненного процессора в течение времени, равного периоду переключения режимов работы процессоров. Затем неисправный процессор будет переведен в режим главного, а исправный - в режим подчиненного, где неисправность главного процессора уже будет обнаружена.

Недостаток системы в том, что при отказе системного генератора, который является общим для двух процессоров, отказывает вся система. В случае использования отдельных генераторов для каждого процессора возникнет рассинхронизация. Рассинхронизация также может наступить при неодновременном поступлении входных данных от приемных устройств.

Кроме того, основной недостаток системы заключается в том, что подчиненный процессор только контролирует работоспособность главного и не выполняет его функции в случае отказа.

Известна резервированная двухпроцессорная вычислительная система [2] (прототип), содержащая схему сравнения и два идентичных канала, каждый из которых содержит системный генератор, выход которого подключен к первому входу процессора, первый выход процессора подключен к первому входу коммутатора, второй выход процессора подключен к первому входу элемента ИЛИ, выход которого подключен к первому входу временного анализатора исправности и первому входу триггера, выход которого подключен к первому входу элемента ИЛИ-НЕ, импульсный генератор, выход которого подключен ко второму входу временного анализатора исправности, выход которого подключен к первому входу счетчика сбоев и второму входу триггера, первый выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, схему начальной установки, выход которой подключен ко второму входу процессора, второму входу элемента ИЛИ, второму входу счетчика сбоев, второй выход которого подключен к первому входу схемы сравнения, второй вход которой подключен ко второму входу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы, к которому подключены необходимые внешние устройства (модули).

В известной резервированной двухпроцессорной вычислительной системе после поступления сигнала RES от схемы начальной установки все устройства системы устанавливаются в исходное состояние и к выходу подключается процессор первого канала, а второй канал отключается коммутатором. В каждом канале одновременно с основной задачей периодически в фиксированные интервалы времени решается диагностическая задача (осуществляется самодиагностика работоспособности устройств системы). В случае успешного выполнения диагностики формируются короткие импульсы исправности TestOK, которые обнуляют (устанавливают в исходное состояние) временной анализатор исправности. При этом сигналы с импульсного генератора на счетчик сбоев не поступят. В случае отсутствия сигналов TestOK (отказа в работе канала) счетчик сбоев будет заполняться сигналами импульсного генератора. Схема сравнения, анализируя коды счетчиков сбоев, формирует сигналы, которые поступают на коммутаторы. При этом подключается к выходу работоспособный процессор (канал), и отключается вышедший из строя. При работоспособных каналах, в случае многократных сбоев переключение осуществляется на тот канал, в котором меньше сбоев.

Известная резервированная двухпроцессорная вычислительная система обладает повышенной надежностью. Принятие решения на переключение возлагается на устройство резервирования, которое реализовано на логических элементах в составе базового матричного кристалла, обладающего высокой надежностью. Переключение на работоспособный канал происходит после поступления с импульсного генератора на временной анализатор исправности не менее двух импульсов. При этом период частоты импульсного генератора не может быть меньше времени выхода процессора на рабочий режим после подачи на него напряжения питания. Время выхода процессора на рабочий режим (время появления сигналов TestOK) определяется временем достижения напряжением номинального значения от момента подачи (зависит от источника вторичного питания и емкостной нагрузки системы) и временем инициализации процессора (зависит от объема инициализируемых устройств). Время переключения на работоспособный канал может превышать требуемую величину, необходимую, например, при использовании системы на объектах, движущихся с высокой скоростью, или на объектах с быстропротекающими процессами. В случае короткого замыкания по выходу (в шине межмодульного обмена) система выходит из строя.

Недостатки системы [2] заключаются в значительном времени переключения на резервный канал и отказе в случае короткого замыкания по выходу (в шине межмодульного обмена).

Технический результат - уменьшение времени переключения на резервный канал и повышение надежности системы за счет введения дополнительных устройств и связей.

Технический результат достигается тем, что в резервированную двухпроцессорную вычислительную систему, содержащую два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу первого коммутатора; системный генератор, выход которого подключен к первому входу процессора; триггер, выход которого подключен к первому входу элемента ИЛИ-НЕ, выход которого подключен ко второму входу первого коммутатора; импульсный генератор, подключенный через временной анализатор исправности к первому входу триггера и первому входу счетчика сбоев, первый выход которого подключен ко второму входу элемента ИЛИ-НЕ; схему начальной установки, выход которой подключен ко второму входу процессора, второму входу счетчика сбоев, первому входу элемента ИЛИ, причем выходы элемента ИЛИ подключены ко второму входу временного анализатора исправности и второму входу триггера; схему сравнения, первый вход которой подключен ко второму выходу счетчика сбоев первого канала, второй вход - ко второму выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, а второй - к третьему входу элемента ИЛИ-НЕ второго канала, в каждый из каналов введены устройство аварийного запуска, два коммутатора, устройство памяти, при этом выход схемы начальной установки подключен к первому входу импульсного генератора и первому входу устройства аварийного запуска, второй вход которого подключен к второму выходу процессора, а выходы - к второму входу импульсного генератора и второму входу элемента ИЛИ; первый вход второго коммутатора первого канала подключен к третьему выходу процессора первого канала, четвертый выход которого подключен к первому входу третьего коммутатора второго канала, выход первого коммутатора первого канала подключен ко второму входу третьего коммутатора второго канала, второму входу второго коммутатора первого канала и является выходом первого канала системы; выход второго коммутатора первого канала подключен к выходу третьего коммутатора первого канала и входу устройства памяти первого канала; первый вход второго коммутатора второго канала подключен к третьему выходу процессора второго канала, четвертый выход которого подключен к первому входу третьего коммутатора первого канала; выход первого коммутатора второго канала подключен ко второму входу второго коммутатора второго канала, второму входу третьего коммутатора первого канала и является выходом второго канала системы; выход второго коммутатора второго канала подключен к выходу третьего коммутатора второго канала и входу устройства памяти второго канала.

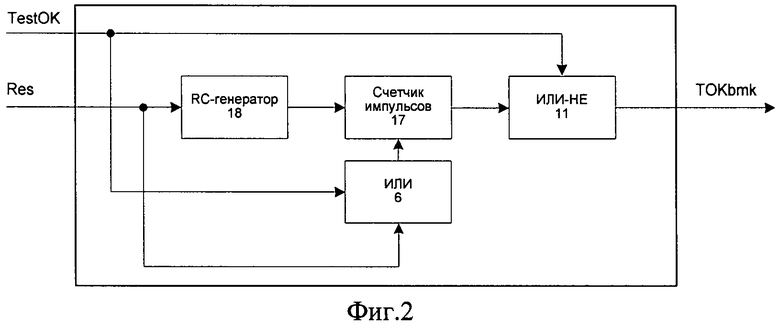

На фиг.1 приведена структурная схема предлагаемой системы.

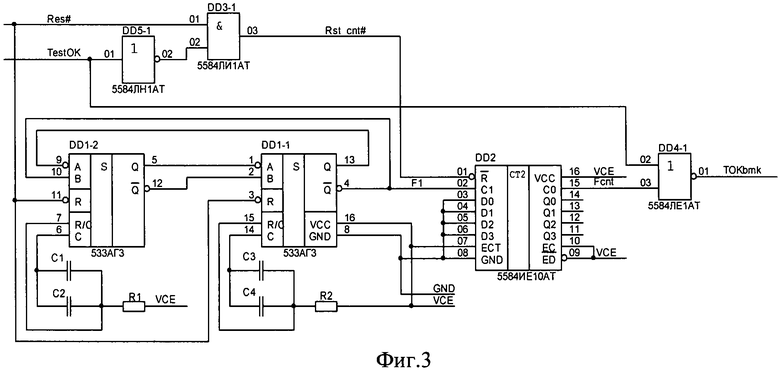

На фиг.2 приведена структурная схема устройства аварийного запуска.

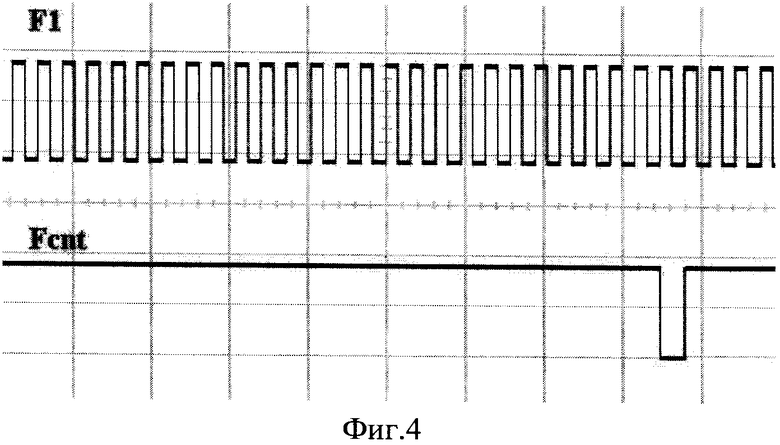

На фиг.3 приведен вариант реализации устройства аварийного запуска.

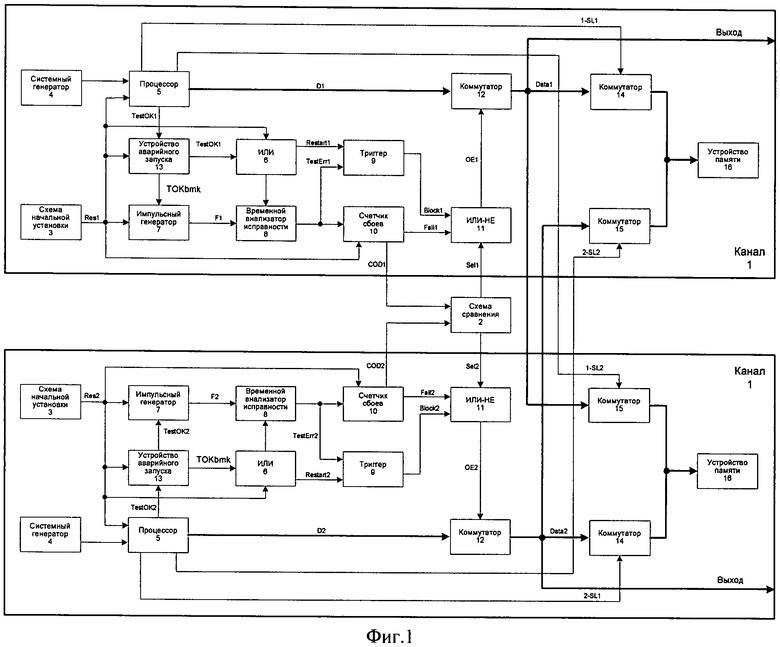

На фиг.4 приведена временная диаграмма работы устройства аварийного запуска.

Резервированная двухпроцессорная вычислительная система, представленная на фиг.1, содержит два идентичных канала 1, схему сравнения 2. Каждый канал содержит схему начальной установки 3, системный генератор 4, процессор 5, элемент ИЛИ 6, импульсный генератор 7, подключенный к схеме начальной установки 3, временному анализатору исправности 8, который подключен к триггеру 9, счетчику сбоев 10 и элементу ИЛИ 6, соединенному со схемой начальной установки 3, элемент ИЛИ-НЕ 11, подключенный к счетчику сбоев 10, соединенному со схемой начальной установки 3, триггеру 9, соединенному с элементом ИЛИ 6, и к коммутатору 12, соединенному с процессором 5, который подключен к системному генератору 4, схеме начальной установки 3, устройству аварийного запуска 13, коммутатору 14, подключенному к коммутатору 15 и устройству памяти 16. К схеме сравнения 2 подключены счетчики сбоев 10 и элементы ИЛИ-НЕ 11 каждого канала 1. Также в системе соответствующее устройство аварийного запуска 13 подключено к схеме начальной установки 3, элементу ИЛИ 6, импульсному генератору 7 соответствующего канала 1. Кроме того, в каждом канале процессор 5 соединен с коммутатором 15 другого канала, коммутатор 12 первого канала 1 соединен с коммутатором 15 второго канала 1, коммутатором 14 первого канала 1 и является выходом первого канала 1, а коммутатор 12 второго канала 1 соединен с коммутатором 15 первого канала 1, коммутатором 14 второго канала 1 и является выходом второго канала 1.

Устройство аварийного запуска 13, представленное на фиг.2, содержит счетчик импульсов 17, к которому подключены RC-генератор 18, элемент ИЛИ 6, элемент ИЛИ-НЕ 11.

В момент подачи напряжения на систему схема начальной установки 3 формирует сигнал Res# (изменение состояния из логического нуля в логическую единицу). При этом разблокируются RC-генератор 18 и счетчик импульсов 17 устройства аварийного запуска 13, импульсный генератор 7, временной анализатор исправности 8, счетчик сбоев 10, триггер 9.

RC-генератор 18 устройства аварийного запуска 13 начинает формировать последовательность импульсов с частотой F1, которая поступает на вход счетчика импульсов 17. Если через определенный интервал времени от процессора 5 из-за его неисправности, не поступят сигналы TestOK, то счетчик импульсов 17 не сбросится, заполнится и сформирует импульс Fcnt (фиг.4).

Импульс Fcnt с выхода счетчика импульсов 18 через элемент 11 поступает на импульсный генератор 7 и через элемент 6 на временной анализатор исправности 8. По переднему фронту импульса Fcnt разблокируется по выходу импульсный генератор 7. Импульсы с выхода импульсного генератора 7 поступают на временной анализатор исправности 8. При отсутствии импульсов TestOK (на выходе процессора логический ноль) временной анализатор исправности 8, реализованный в виде счетчика импульсов, оказывается разблокированным и будет заполняться сигналами, поступающими с выхода импульсного генератора 7. При заполнении временного анализатора исправности 8 формируется сигнал ошибки TestErr, который поступает на счетчик сбоев 10, увеличивая его значение на единицу.

Схема сравнения 2, анализируя коды счетчика сбоев первого канала (01) и счетчика сбоев второго канала (00), формирует сигналы Sel1, Sel2, которые поступают соответственно на элементы 11 схем анализа исправности основного и резервного каналов. Сигналы с выходов элементов 11 управляют коммутаторами 12 шин PCI. В данном случае к шине PCI подключается резервный канал (процессор), в котором сбоев меньше, а канал, в котором произошел сбой, отключается. При этом для обмена становятся доступными внешние устройства (модули) резервного канала. Промежуточные результаты вычислений периодически записываются в устройства памяти обоих каналов. Второй канал, являющийся резервным, в случае выхода из строя основного начинает выполнение задачи, используя информацию, записанную в устройство памяти резервного канала. Это позволяет продолжить решение задачи без потери информации. Так как для быстропротекающих процессов время решения задачи должно быть минимальным, то с целью сокращения потерь процессорного времени время решения диагностической задачи также должно быть минимальным. Для известного периода Т диагностической задачи частота F импульсного генератора выбирается из соотношения F<(N-1)FTestOK (1), где N - максимальное число импульсов, необходимое для заполнения счетчика временного анализатора исправности. Таким образом, в предлагаемой системе время переключения на резервный канал будет минимальным, так как зависит от времени решения диагностической задачи, которое также минимально.

Если процессор выходит на режим не позднее определенного времени, то импульсы TestOK, поступая на установочные входы счетчика импульсов 17 устройства аварийного запуска 13 и временного анализатора исправности 8 (последовательность импульсов отрицательной полярности), будут их обнулять. В этой ситуации хотя импульсный генератор 7 будет разблокирован, временной анализатор исправности 8 не накопит максимального числа импульсов и, следовательно, не сформирует сигнал ошибки на выходе. Так как информация счетчика сбоев 10 не изменится, то работа будет продолжаться на первом канале.

В случае повторяющихся сбоев схема сравнения 2, анализируя коды счетчиков сбоев 10 работающего и резервного каналов, изменяет состояние выходных сигналов Sel1, Sel2 таким образом, что к работе подключается тот канал, где сбоев меньше. При заполнении счетчика сбоев 10 до максимального значения процессор отключается от шины PCI. Заполнение счетчиков сбоев обоих каналов принимается за отказ системы.

Принципиальное отличие предлагаемой резервированной двухпроцессорной вычислительной системы, представленной на фиг.1, от прототипа заключается во введении устройства аварийного запуска, запрещающего переключение на резервный канал в интервале времени от момента подачи питания до прогнозируемого момента появления первого импульса TestOK и формирующего сигнал для переключения на резервный канал в случае дальнейшего отсутствия импульсов сигнала исправности TestOK. Дополнительное отличие - введение коммутаторов и устройств памяти, что позволило сделать раздельными выходы каналов и, следовательно, исключить отказ системы при коротком замыкании на выходе одного из каналов.

Вновь введенные коммутаторы построены на микросхемах приемопередатчиков типа 5584АП7Т со схемой удержания информации на входе. В качестве устройств памяти использованы статические оперативно запоминающие устройства (СОЗУ) типа НРУ5509, обладающие требуемыми объемом памяти, быстродействием. RC-генератор 18 вновь введенного устройства аварийного запуска 13 (фиг.3) построен на микросхеме одновибратора с повторным запуском DD1 533АГ3, резисторах R1-R2, конденсаторах С1-С4. Счетчик импульсов 18 построен на микросхеме DD2 5584ИЕ10АТ. Логический элемент 6 построен на микросхемах 5584ЛН1АТ, 5584ЛИ1АТ. Логический элемент 11 построен на микросхеме 5584ЛЕ1АТ.

Источники информации

1. Патент 94296302, США, МКИ G06F 11/00, 1994 г. (аналог).

2. Патент №2264648, РФ, МКИ G06F 11/20, 2005 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2011 |

|

RU2481619C1 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| Самодиагностируемая бортовая вычислительная система с резервированием замещением | 2017 |

|

RU2657166C1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| Многоканальная самодиагностируемая вычислительная система с резервированием замещением и способ повышения ее отказоустойчивости (варианты) | 2016 |

|

RU2634189C1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Устройство для автоматического переключения каналов связи | 1987 |

|

SU1494240A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем. Техническим результатом является уменьшение времени переключения на резервный канал и повышение надежности системы за счет введения дополнительных устройств и связей. Система содержит схему сравнения и два идентичных канала, каждый из которых содержит процессор, три коммутатора, системный генератор, триггер, элемент ИЛИ-НЕ, импульсный генератор, временной анализатор исправности, счетчик сбоев, схему начальной установки, элемент ИЛИ, устройство аварийного запуска, устройство памяти. 4 ил.

Резервированная двухпроцессорная вычислительная система, содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу первого коммутатора; системный генератор, выход которого подключен к первому входу процессора; триггер, выход которого подключен к первому входу элемента ИЛИ-НЕ, выход которого подключен ко второму входу первого коммутатора; импульсный генератор, подключенный через временной анализатор исправности к первому входу триггера и первому входу счетчика сбоев, первый выход которого подключен ко второму входу элемента ИЛИ-НЕ; схему начальной установки, выход которой подключен ко второму входу процессора, второму входу счетчика сбоев, первому входу элемента ИЛИ, причем выходы элемента ИЛИ подключены ко второму входу временного анализатора исправности и второму входу триггера; схему сравнения, первый вход которой подключен ко второму выходу счетчика сбоев первого канала, второй вход - ко второму выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, а второй - к третьему входу элемента ИЛИ-НЕ второго канала, отличающаяся тем, что в каждый из каналов введены устройство аварийного запуска, два коммутатора, устройство памяти, при этом выход схемы начальной установки подключен к первому входу импульсного генератора и первому входу устройства аварийного запуска, второй вход которого подключен к второму выходу процессора, а выходы - к второму входу импульсного генератора и второму входу элемента ИЛИ; первый вход второго коммутатора первого канала подключен к третьему выходу процессора первого канала, четвертый выход которого подключен к первому входу третьего коммутатора второго канала, выход первого коммутатора первого канала подключен ко второму входу третьего коммутатора второго канала, второму входу второго коммутатора первого канала и является выходом первого канала системы; выход второго коммутатора первого канала подключен к выходу третьего коммутатора первого канала и входу устройства памяти первого канала; первый вход второго коммутатора второго канала подключен к третьему выходу процессора второго канала, четвертый выход которого подключен к первому входу третьего коммутатора первого канала; выход первого коммутатора второго канала подключен ко второму входу второго коммутатора второго канала, второму входу третьего коммутатора первого канала и является выходом второго канала системы; выход второго коммутатора второго канала подключен к выходу третьего коммутатора второго канала и входу устройства памяти второго канала.

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Резервированная вычислительная система | 1989 |

|

SU1624470A1 |

| US 5136704 A, 04.08.1992 | |||

| US 5491787 A, 13.02.1996. | |||

Авторы

Даты

2012-08-27—Публикация

2011-08-22—Подача