Предлагаемое изобретение относится к вычислительной технике и может быть использовано в системах различного назначения, где требуется повышенная надежность и радиационная стойкость, в частности в ракетно-космической, авиационной технике.

В изделиях ответственного применения до настоящего времени для обеспечения повышенной надежности и отказоустойчивости, в основном, используются многоканальные бортовые цифровые вычислительные системы (БЦВС), принцип работы которых основан на мажорировании, т.е. использовании 2n+1 каналов и схемы голосования, отбирающей те выходные данные, которые представляют большинство.

Наибольшее применение находят трехканальные БЦВС с выбором правильной информации по правилу «2 из 3-х» [1, 2].

Повышение надежности системы, рассмотренной в [1], обеспечивается за счет одновременного проведения вычислений на всех идентичных вычислительных каналах, включенных параллельно и реализующих одну и ту же функцию сравнения результатов вычислений, получаемых в фиксированный момент времени на выходе первого и второго, второго и третьего, первого и третьего каналов, выборе правильной информации по мажоритарному принципу.

Используемые системы обеспечивают работоспособность при выходе из строя одного из каналов.

Применение БЦВС в различных комплексах космических аппаратов (КА) показало, что они обладают требуемой надежностью при работе в широком диапазоне изменения температуры окружающей среды, механических, электромагнитных воздействиях. Недостатком указанных систем является ускоренный выход из строя всех каналов в условиях повышенной радиации.

В многоканальной вычислительной системе, рассмотренной в [2], к трем вычислительным каналам добавлен дополнительный канал (дополнительная грань), находящийся в «холодном» резерве, который менее подвержен воздействию радиации. Используемый блок контроля работоспособности каналов анализирует работоспособность каналов и, в случае выхода из строя любых двух каналов, подключает резервный канал.

Следует отметить, что повышение радиационной стойкости возможно только в случае, когда радиационная стойкость блока контроля работоспособности каналов превышает радиационную стойкость каналов. В резервированных системах с замещением блок контроля является последовательным звеном между каналами и может стать определяющим в надежности системы. Для обеспечения высокой достоверности определения отказа канала сложность блока контроля может превысить сложность всей системы. При воздействии повышенной радиации могут одновременно выйти из строя все каналы БЦВС и блок контроля, так как они находятся в активном режиме и одинаково подвержены воздействию радиации. В этом случае резервный канал не подключится.

Известен способ обеспечения отказоустойчивости вычислительных систем [3], заключающийся в маскировании сбоев путем резервирования и включающий определение наличия сбоев, идентификацию и блокировку неисправных каналов, для маскирования сбоев используют независимую одновременную работу N каналов, число которых на единицу больше кратности маскируемых сбоев, сигналы которых подают на общий выход, и по сигналам, полученным от детекторов сбоев, входящих в состав каждого канала, производят блокировку прохождения сигналов от каналов, в которых произошли сбои, и пропускают на выход тот из сигналов от исправных каналов, который приходит первым по времени.

Так как все каналы одновременно находятся в рабочем режиме, то использование данного способа не позволяет повысить радиационную стойкость систем.

В [4] рассматривается самодиагностируемая трехканальная резервированная вычислительная система (прототип). Повышение надежности, отказоустойчивости обеспечивается за счет диагностирования работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи в фиксированные интервалы времени, аналогичной штатной с заданными исходными данными, сравнения результата решения диагностической задачи с заранее известным результатом, и, в случае совпадения, формирования процессором импульса исправности активного канала, анализа периода следования импульсов исправности и формирования сигнала для подключения резервного канала, в случае выхода из строя любого работающего канала.

Недостатки прототипа заключаются в необходимости использования устройства формирования сигналов выборки канала, устройства аварийного запуска, что, в случае выхода их из строя в процессе старения или радиационного воздействия, не позволяет подключить резервный канал и, следовательно, приводит к снижению надежности, отказоустойчивости и радиационной стойкости системы.

Техническим результатом предлагаемого решения является повышение надежности, отказоустойчивости и радиационной стойкости, упрощение многоканальной вычислительной системы, а также повышение пожарной безопасности за счет обеспечения возможности разнесения каналов по объекту.

Технический результат достигается тем, что в многоканальной самодиагностируемой вычислительной системе с резервированием замещением, содержащей три идентичных канала, каждый из которых содержит вторичный источник питания, память, системный генератор, выход которого подключен к первому входу процессора; схему начальной установки, выход которой подключен ко второму входу процессора, в каждый канал введены устройство отключения питания, устройство обращения к памяти, выход которого подключен к памяти, а вход подключен к первому выходу процессора устройство резервирования, первый вход которого подключен к выходу схемы начальной установки, второй вход подключен ко второму выходу процессора, третий вход подключен к выходу системного генератора; первый выход устройства резервирования первого канала подключен к первому входу устройства отключения питания третьего канала, второй выход подключен к первому входу устройства отключения питания второго канала; первый выход устройства резервирования второго канала подключен к первому входу устройства отключения питания первого канала, второй выход подключен к второму входу устройства отключения питания третьего канала; первый выход устройства резервирования третьего канала подключен ко второму входу устройства отключения питания второго канала, второй выход подключен ко второму входу устройства отключения питания первого канала; третий выход процессора первого канала подключен ко второму входу устройства обращения к памяти второго канала, четвертый выход подключен ко второму входу устройства обращения к памяти третьего канала; третий выход процессора второго канала подключен к второму входу устройства обращения к памяти первого канала, четвертый выход процессора второго канала подключен к третьему входу устройства обращения к памяти третьего канала; третий выход процессора третьего канала подключен к третьему входу устройства обращения к памяти первого канала, а четвертый выход подключен к третьему входу устройства обращения к памяти второго канала.

Кроме того, устройство резервирования содержит делитель частоты, первый вход которого подключен к системному генератору, а второй - к схеме начальной установки, первому входу первого счетчика импульсов, первым входам первого, второго, третьего и четвертого логических элементов 2И; первый выход делителя частоты подключен к первому входу второго счетчика импульсов, а второй - к первому входу логического элемента ЗИ; выход второго счетчика импульсов подключен ко второму входу логического элемента ЗИ; второй вход первого счетчика импульсов подключен к процессору и второму входу второго счетчика импульсов; выход первого счетчика импульсов подключен к третьему входу логического элемента ЗИ, выход которого подключен к входу логического элемента НЕ, вторым входам второго и третьего логических элементов 2И; выход логического элемента НЕ подключен к вторым входам первого и четвертого логических элементов 2И.

Кроме того, устройство резервирования содержит делитель частоты, первый вход которого подключен к системному генератору, а второй к схеме начальной установки, первому входу первого счетчика импульсов, первым входам первого, второго, третьего и четвертого логических элементов 2И; первый выход делителя частоты подключен к первому входу второго счетчика импульсов, а второй к первому входу логического элемента 3И; выход второго счетчика импульсов подключен ко второму входу логического элемента 3И; второй вход первого счетчика импульсов подключен к процессору и второму входу второго счетчика импульсов; выход первого счетчика импульсов подключен к третьему входу логического элемента 3И, выход которого подключен к входу LVDS-передатчика; выход LVDS-передатчика подключен к входу LVDS-приемника; выход LVDS-приемника подключен к входу логического элемента НЕ, вторым входам второго и третьего логических элементов 2И; выход логического элемента НЕ подключен ко вторым входам первого и четвертого логических элементов 2И.

Технический результат достигается тем, что в способе повышения отказоустойчивости многоканальной самодиагностируемой вычислительной системы с резервированием замещением, заключающемся в диагностировании работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи, аналогичной штатной, с заранее выбранными начальными данными, сравнении результата решения диагностической задачи с заранее известным результатом и, в случае совпадения, формировании процессором импульсов исправности активного канала, анализе поступления импульсов исправности и их периода следования, по результатам анализа импульсов исправности и периода их следования формируют последовательность логических сигналов. Преобразуют их в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала.

Технический результат достигается тем, что для повышения пожарной безопасности в способе повышения отказоустойчивости многоканальной самодиагностируемой вычислительной системы с резервированием замещением, заключающемся в диагностировании работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи, аналогичной штатной, с заранее выбранными начальными данными, сравнении результата решения диагностической задачи с заранее известным результатом и, в случае совпадения, формировании процессором импульсов исправности активного канала, анализе поступления импульсов исправности и их периода следования, по результатам анализа импульсов исправности и периода их следования формируют последовательность логических сигналов. Преобразуют их в токовые сигналы противоположного направления, затем в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала.

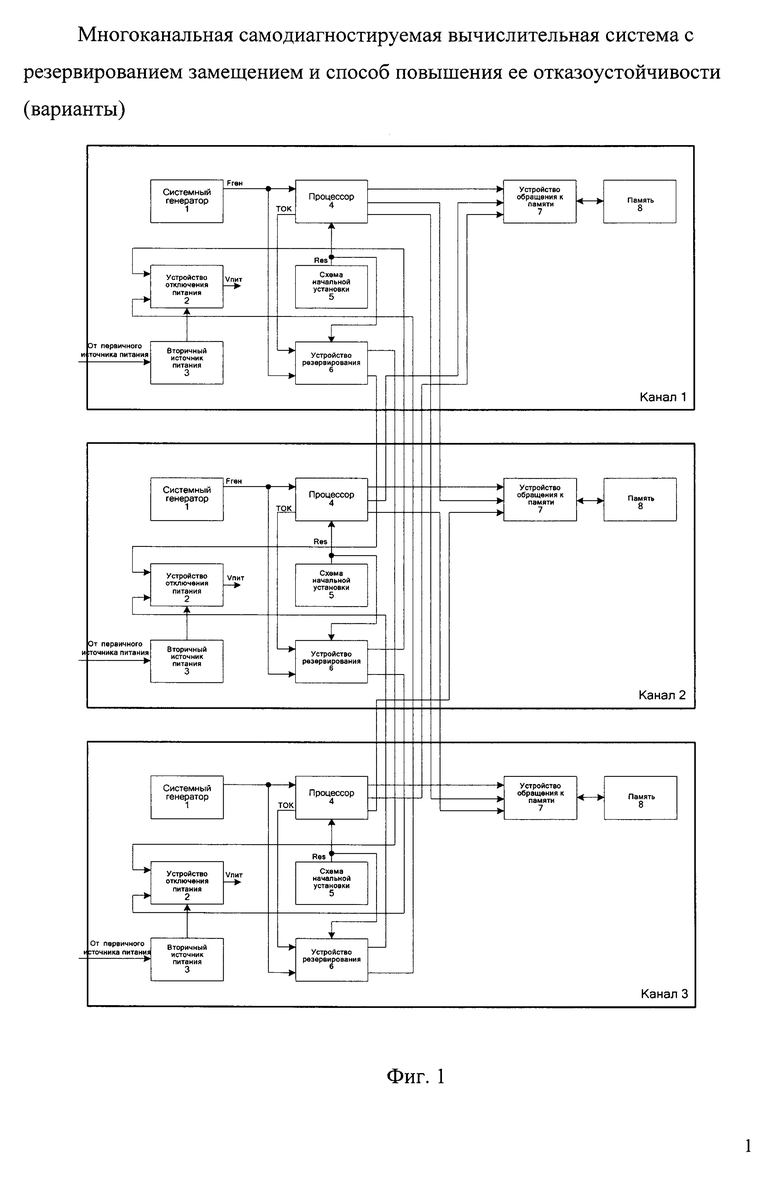

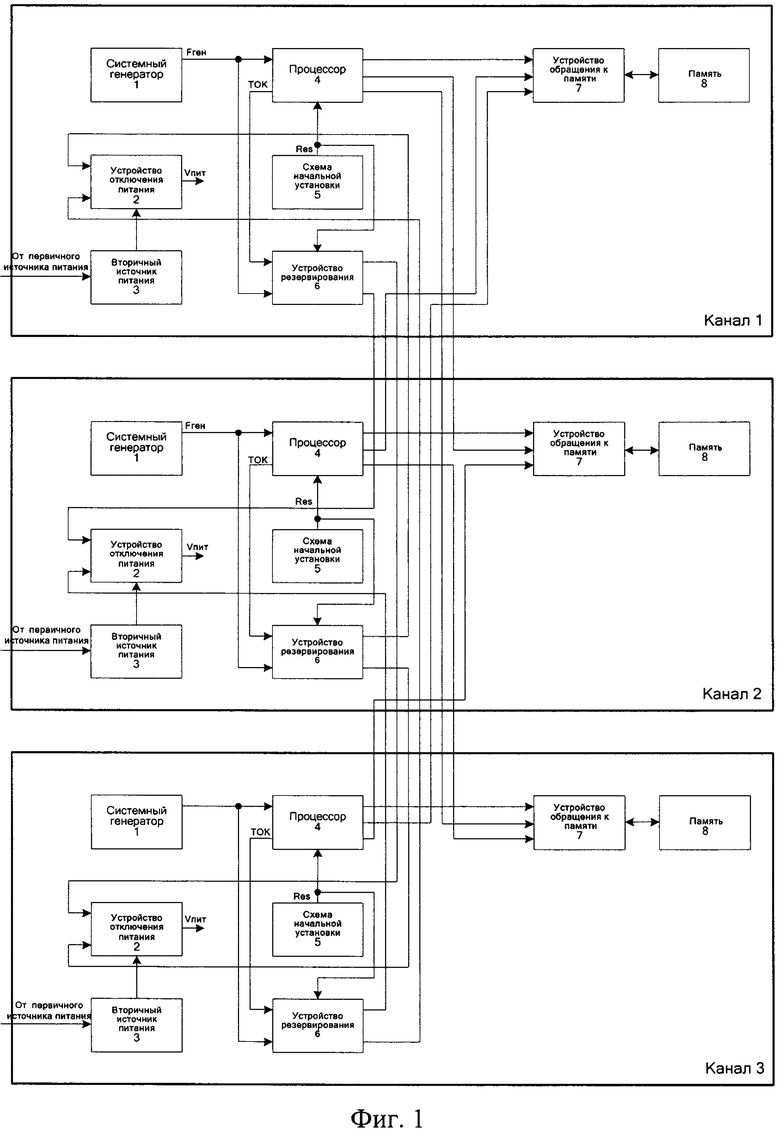

На фиг. 1 приведена структурная схема многоканальной самодиагностируемой системы с резервированием замещением.

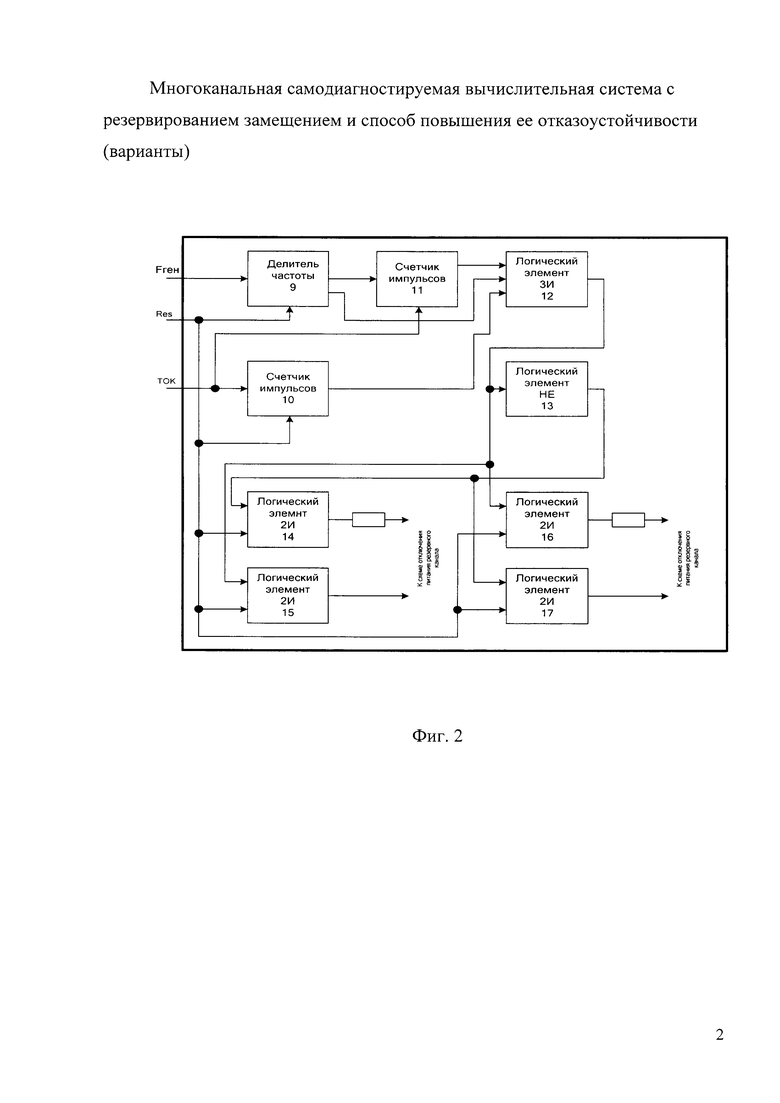

На фиг. 2 приведена структурная схема устройства резервирования.

На фиг. 3 приведен вариант устройства отключения питания резервного канала.

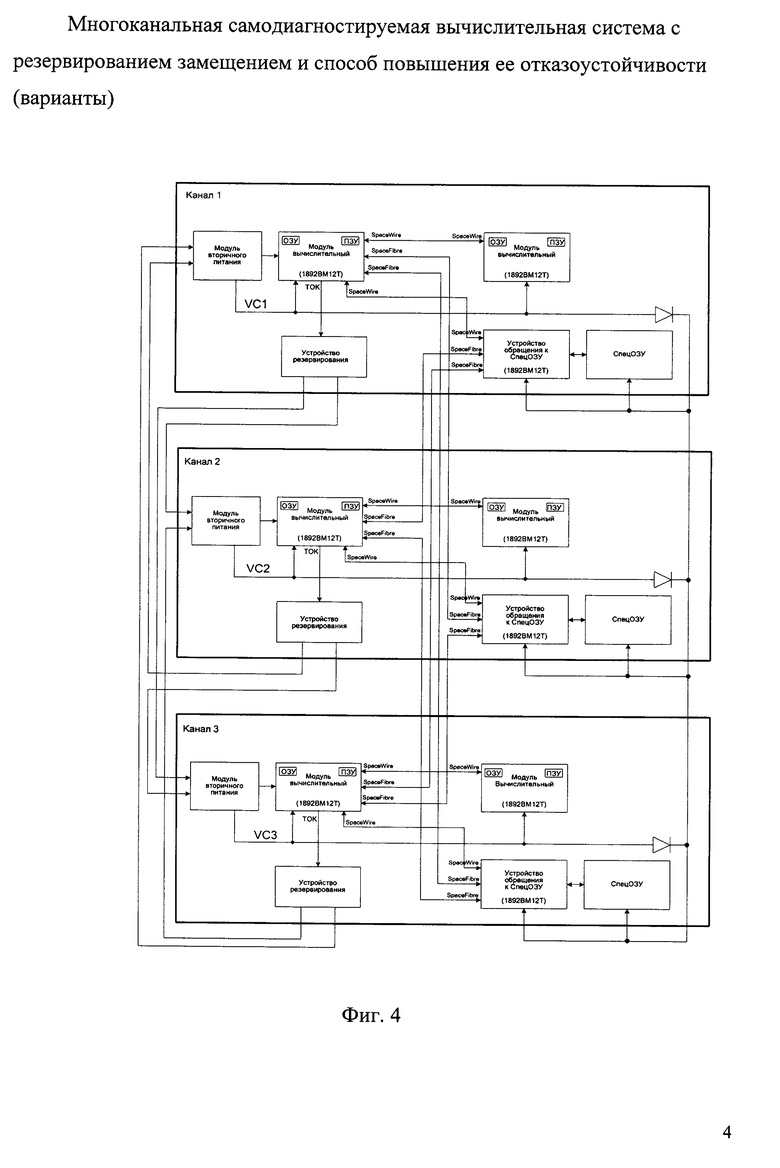

На фиг. 4 приведен возможный вариант реализации системы при использовании процессора 1892 ВМ12Т.

На фиг. 5 приведен вариант устройства резервирования, в котором последовательности импульсов исправности преобразуют в токовые сигналы противоположного направления для передачи через LVDS-интерфейс.

Многоканальная самодиагностируемая вычислительная система с резервированием замещением, представленная на фиг. 1, содержит три идентичных канала. Каждый канал содержит системный генератор 1, устройство отключения питания 2, вторичный источник питания 3, процессор 4, схему начальной установки 5, устройство резервирования 6, устройство обращения к памяти 7, память 8. Системный генератор 1 соединен с процессором 4 и устройством резервирования 6. Процессор 4 соединен со схемой начальной установки 5, устройством резервирования 6 и устройством обращения к памяти 7, которое соединено с памятью 8. Вторичный источник питания 3 соединен с устройством отключения питания 2. Кроме того, устройство резервирования 6 первого канала соединено с устройством отключения питания 2 второго и третьего канала, устройство резервирования 6 второго канала соединено с устройством отключения питания 2 первого и третьего канала; устройство резервирования 6 третьего канала соединено с устройством отключения питания 2 первого и второго канала; процессор 4 первого канала соединен с устройствами обращения к памяти 7 второго и третьего канала; процессор 4 второго канала соединен с устройствами обращения к памяти 7 первого и третьего канала; процессор 4 третьего канала соединен с устройствами обращения к памяти 7 первого и второго канала.

Устройство резервирования, схема которого приведена на фиг. 2, содержит делитель частоты 9, первый вход которого подключен к системному генератору 1, а второй к схеме начальной установки 5, первому входу первого счетчика импульсов 10, первым входам первого 14, второго 15, третьего 16 и четвертого 17 логических элементов 2И; первый выход делителя частоты 9 подключен к первому входу второго счетчика импульсов 11, а второй к первому входу логического элемента 3И 12; выход второго счетчика импульсов 11 подключен ко второму входу логического элемента 3И 12; второй вход первого счетчика импульсов 10 подключен к процессору 4 и второму входу второго счетчика импульсов 11; выход первого счетчика импульсов 10 подключен к третьему входу логического элемента 3И 12, выход которого подключен к входу логического элемента НЕ 13, вторым входам второго 15 и третьего 16 логических элементов 2И; выход логического элемента НЕ 13 подключен к вторым входам первого 14 и четвертого 17 логических элементов 2И.

В представленном на фиг. 3 варианте устройства отключения питания резервного канала трансформатор Т1 соединен с диодами Dl, D2, резистором R1, конденсатором С1; резистор R1 соединен с резистором R2, транзистором VT1; транзистор VT1 соединен с резистором R2, резистором R3, который соединен с транзистором VT2, резистором R4; транзистор VT2 соединен с резистором R4, диодом D3.

Устройство резервирования, схема которого приведена на фиг. 5, содержит делитель частоты 9, первый вход которого подключен к системному генератору 1, а второй к схеме начальной установки 5, первому входу первого счетчика импульсов 10, первым входам первого 14, второго 15, третьего 16 и четвертого 17 логических элементов 2И; первый выход делителя частоты 9 подключен к первому входу второго счетчика импульсов 11, а второй к первому входу логического элемента 3И 12; выход второго счетчика импульсов 11 подключен ко второму входу логического элемента 3И 12; второй вход первого счетчика импульсов 10 подключен к процессору 4 и второму входу второго счетчика импульсов 11; выход первого счетчика импульсов 10 подключен к третьему входу логического элемента 3И 12, выход которого подключен к входу LVDS-передатчика; выход LVDS-передатчика 18 подключен к входу LVDS-приемника 19; выход LVDS-приемника подключен к входу логического элемента НЕ 13, вторым входам второго 15 и третьего 16 логических элементов 2И; выход логического элемента НЕ 13 подключен ко вторым входам первого 14 и четвертого 17 логических элементов 2И.

В предлагаемой многоканальной самодиагностируемой вычислительной системе с резервированием замещением осуществляется:

- диагностирование работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи, аналогичной штатной, с заранее выбранными начальными данными;

- сравнение результата решения диагностической задачи с заранее известным результатом и, в случае совпадения, осуществляется формирование процессором импульсов исправности активного канала;

- анализ поступления импульсов исправности и их периода следования;

- по результатам анализа импульсов исправности и периода их следования осуществляется формирование последовательности логических сигналов противоположной полярности;

- преобразование логических сигналов противоположной полярности в синусоидальное напряжение;

- преобразование синусоидального напряжения в постоянное для управления ключом отключения напряжения вторичного источника питания резервного канала.

В каждом канале системы, структурная схема которой представлена на фиг. 1, напряжение от вторичного источника питания 3 подается постоянно на устройство отключения питания 2. На устройство обращения к памяти 7 и память 8 напряжение подается постоянно от вторичных источников питания 3 всех каналов по схеме «ИЛИ» через развязывающие диоды (на фиг. 1 не показано).

В момент подачи напряжения на систему вторичный источник питания 3 каждого канала формирует сигнал начальной установки Res (изменяется из логического «0» в логическую «1»). При достижении сигналом определенного уровня разрешается работа системы. В этом случае тот процессор 4, который первым выйдет на режим, будет периодически в фиксированное время решать диагностическую задачу с заранее выбранными начальными данными и известным результатом.

В случае совпадения результата решения диагностической задачи с известным результатом процессор 4 формирует сигнал исправности канала ТОК. При периодическом решении диагностической задачи процессор 4 формирует последовательность импульсов, которые поступают на устройство резервирования.

Устройство резервирования анализирует наличие импульсов исправности работы канала и периода их следования. При исправном канале устройство резервирования формирует последовательность импульсов, которая преобразуется в логические сигналы противоположной полярности, затем в синусоидальное напряжение, постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала.

При пропадании импульсов исправности ТОК или изменении периода их следования (выходе из строя канала) устройство резервирования прекращает формирование последовательности импульсов для отключения вторичных источников питания 2 резервных каналов. При этом на резервные каналы будет подано напряжение от вторичных источников питания 2 и подключится один из резервных каналов, который раньше сформирует импульсы исправности ТОК. Таким образом, один резервный канал окажется в рабочем режиме, а другие будут в «холодном» резерве. В процессе работы необходимые результаты вычислений периодически сохраняются в памяти 8 всех каналов. Подключенный канал продолжит вычисления с учетом информации, сохраненной в памяти 8, что позволяет ускорить решение требуемых задач.

При работоспособном канале устройство резервирования обеспечивает отключение питания от резервных каналов.

На устройство резервирования 6 от схемы начальной установки 5 подается сигнал Res (изменяется из «0» в «1»). От системного генератора 1 на делитель частоты 9 поступают частотные сигналы Fген. От процессора 4 поступают сигналы исправности канала ТОК, формируемые по результатам самодиагностики.

В момент подачи питания на устройство резервирования 6, при достижении сигналом Res определенной величины, снимается блокировка с делителя частоты 9, логических элементов 2И 14-17. Счетчик импульсов 10 устанавливается в исходное состояние (на выходе счетчика 10 - логический «0»). Выход счетчика 11 может быть в произвольном состоянии. К моменту выхода процессора на режим на счетчик импульсов 11 поступит определенное количество импульсов от делителя частоты 9, на его выходе появится логическая «1» и он закроется по входу. До момента появления импульсов ТОК на входах и выходе логического элемента 3И 12 будут логические уровни. В момент появления сигналов исправности ТОК (первым импульсом), счетчик импульсов И установится в исходное состояние (на выходе логический «0»). При поступлении на счетчик импульсов 10 определенного количества импульсов ТОК он закроется по входу и на его выходе появится логический «0». В этом случае частотные сигналы от делителя частоты 9 появятся на выходе логического элемента 3И 12 и инверсные на выходе логического элемента НЕ 13. Сигналы с выхода элемента 3И 12 и выхода элемента НЕ 13 поступят на входы логических элементов 2И 14-17, а с выходов элементов 2И 14-17 на трансформатор Т1 устройства отключения питания соответствующих резервных каналов.

Устройство отключения питания, структурная схема которого представлена на фиг.3, преобразует переменное напряжение в постоянное, которое поступает на транзистор VT1. При этом он открывается и закрывает транзистор VT2. В данном случае напряжение питания отключится от резервного канала.

В предложенной многоканальной самодиагностируемой вычислительной системе отсутствует логический элемент ИЛИ и устройство формирования сигналов выборки канала, которые являются последовательным звеном между основным и резервными каналами, а также уменьшается число линий связи, используемых для подключения резервных каналов.

Возможный вариант реализации системы с использованием отечественного высокопроизводительного процессора 1892 ВМ12Т представлен на фиг. 4. Обращение к памяти активного канала осуществляется по последовательному высокоскоростному порту SpaceWire, а к памяти резервных каналов по последовательному высокоскоростному порту SpaceFibre, обеспечивающему гальваническую развязку.

Устройство резервирования, схема которого представлена на фиг. 2, реализуется на логических элементах и содержит делитель частоты, счетчики импульсов, логические элементы 2И, логический элемент 3И, логический элемент НЕ, резисторы, конденсаторы, трансформаторы, диоды, транзисторы. Перечисленные элементы существуют в виде самостоятельных малогабаритных изделий.

Устройство обращения к памяти может быть выполнено с использованием микропроцессора 1892 ВМ12Т.

Устройство отключения питания может быть реализовано с использованием транзисторов типа 2Т690АС9, 2Т689АС9, диодов 2Д803АС9.

Вторичный источник питания целесообразно реализовать с использованием радиационно-стойкого ШИМ-контроллера 1359ЕУ034.

В качестве памяти целесообразно использовать оперативно запоминающее устройство 1620РЕ4У, обладающее высокой радиационной стойкостью.

В предложенной системе подключение резервных каналов происходит как при отказе канала, отказе устройства резервирования, обрыве линий связи устройства резервирования с устройством подключения вторичного питания резервного канала.

Реализация способа осуществляется за счет введения в устройство резервирования логического элемента НЕ, логических элементов 2И, трансформаторов, диодов, резисторов, конденсаторов, транзисторов.

Вариант устройства резервирования, представленный на фиг. 5, с LVDS-передатчиком и LVDS-приемником, в котором последовательности импульсов исправности преобразуют в токовые сигналы противоположного направления для передачи через LVDS-интерфейс, а затем в импульсы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала, обеспечит гальваническую развязку между каналами и значительно упростит техническую реализацию вторичных источников питания.

В этом случае повышение пожарной безопасности достигается тем, что в многоканальной самодиагностируемой вычислительной системе с резервированием замещением после формирования переменных логических сигналов по результатам анализа импульсов исправности и периода их следования осуществляется:

- преобразование переменных логических сигналов в токовые сигналы противоположного направления;

- преобразование токовых сигналов противоположного направления в логические сигналы;

- преобразование логических сигналов в логические сигналы противоположной полярности;

- преобразование логических сигналов противоположной полярности в синусоидальное напряжение;

- преобразование синусоидального напряжения в постоянное для управления ключом отключения напряжения вторичного источника питания резервного канала.

Использование LVDS-интерфейса для связи с резервным каналом (передача сигналов исправности не уровнем напряжения, а направлением тока) обеспечивает подключение резервных каналов, удаленных друг от друга на значительные расстояния, и, следовательно, повышает пожаробезопасность.

Литература

1. Антимиров В.М. Бортовые вычислительные системы семейства «Малахит» для работы в экстремальных условиях / В.М. Антимиров, А.Б. Уманский, Л.Н. Шалимов // Вестник Самарского государственного аэрокосмического университета. - №4(42), 2013. - С. 19-27.

2. Бортовые системы управления космическими аппаратами: Учебное пособие / Бровкин А.Г., Бурдыгов Б.Г., Гордийко С.В. и др. Под редакцией А.С. Сырова - М.: Изд-во МАИ-ПРИНТ, 2010. - 304 с.

3. Патент на изобретение RU 2047899 C1, G06F 11/18. Способ обеспечения отказоустойчивости вычислительных систем.

4. Патент №2527191, Российская федерация, МПК G06F 11/20. Резервированная многоканальная вычислительная система.

5. Русанов В.Н. Самодиагностируемая трехканальная бортовая вычислительная система с резервированием замещением / В.Н. Русанов, А.Ю. Киселев, Н.В. Сильянов // Авиакосмическое приборостроение. - М., изд. «Научтехлитиздат», - 2015. - №2 С. 23-33.

6. Русанов, В.Н. Диагностическая модель резервированной бортовой вычислительной системы / В.Н. Русанов, С.А. Королев // Приборы и системы. Управление, контроль, диагностика. - М., изд. «Научтехлитиздат», - 2014. - №11. - С. 59-64.

| название | год | авторы | номер документа |

|---|---|---|---|

| Самодиагностируемая бортовая вычислительная система с резервированием замещением | 2017 |

|

RU2657166C1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2460121C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2011 |

|

RU2481619C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| Вычислительная система с холодным резервом | 2021 |

|

RU2771211C1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1987 |

|

SU1434504A1 |

| Способ резервирования источников питания | 1988 |

|

SU1647770A1 |

Изобретение относится к вычислительной технике и может быть использовано в ракетно-космической и авиационной технике. Технический результатом заключается в повышении надежности и отказоустойчивости многоканальной вычислительной системы. Технический результат достигается за счет диагностирования работоспособности активного канала процессором самого канала, формировании импульсов исправности активного канала, по результатам анализа которых и периода их следования формируют последовательность логических сигналов, преобразования их в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала. По результатам анализа импульсов исправности и периода их следования формируют последовательность логических сигналов, преобразуют их в токовые сигналы противоположного направления, затем в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала. 3 н. и 2 з.п. ф-лы, 5 ил.

1. Многоканальная самодиагностируемая вычислительная система с резервированием замещением, содержащая три идентичных канала, каждый из которых содержит вторичный источник питания, память, системный генератор, выход которого подключен к первому входу процессора; схему начальной установки, выход которой подключен ко второму входу процессора, отличающаяся тем, что в каждый канал введены устройство отключения питания, устройство обращения к памяти, выход которого подключен к памяти, а вход подключен к первому выходу процессора; устройство резервирования, первый вход которого подключен к выходу схемы начальной установки, второй вход подключен ко второму выходу процессора, третий вход подключен к выходу системного генератора; первый выход устройства резервирования первого канала подключен к первому входу устройства отключения питания третьего канала, второй выход подключен к первому входу устройства отключения питания второго канала; первый выход устройства резервирования второго канала подключен к первому входу устройства отключения питания первого канала, второй выход подключен ко второму входу устройства отключения питания третьего канала; первый выход устройства резервирования третьего канала подключен ко второму входу устройства отключения питания второго канала, второй выход подключен ко второму входу устройства отключения питания первого канала; третий выход процессора первого канала подключен ко второму входу устройства обращения к памяти второго канала, четвертый выход подключен ко второму входу устройства обращения к памяти третьего канала; третий выход процессора второго канала подключен ко второму входу устройства обращения к памяти первого канала, четвертый выход процессора второго канала подключен к третьему входу устройства обращения к памяти третьего канала; третий выход процессора третьего канала подключен к третьему входу устройства обращения к памяти первого канала, четвертый выход подключен к третьему входу устройства обращения к памяти второго канала.

2. Система по п. 1, отличающаяся тем, что устройство резервирования содержит делитель частоты, первый вход которого подключен к системному генератору, а второй - к схеме начальной установки, первому входу первого счетчика импульсов, первым входам первого, второго, третьего и четвертого логических элементов 2И; первый выход делителя частоты подключен к первому входу второго счетчика импульсов, а второй - к первому входу логического элемента 3И; выход второго счетчика импульсов подключен ко второму входу логического элемента 3И; второй вход первого счетчика импульсов подключен к процессору и второму входу второго счетчика импульсов; выход первого счетчика импульсов подключен к третьему входу логического элемента 3И, выход которого подключен к входу логического элемента НЕ, вторым входам второго и третьего логических элементов 2И; выход логического элемента НЕ подключен ко вторым входам первого и четвертого логических элементов 2И.

3. Система по п. 1, отличающаяся тем, что устройство резервирования содержит делитель частоты, первый вход которого подключен к системному генератору, а второй - к схеме начальной установки, первому входу первого счетчика импульсов, первым входам первого, второго, третьего и четвертого логических элементов 2И; первый выход делителя частоты подключен к первому входу второго счетчика импульсов, а второй - к первому входу логического элемента 3И; выход второго счетчика импульсов подключен ко второму входу логического элемента 3И; второй вход первого счетчика импульсов подключен к процессору и второму входу второго счетчика импульсов; выход первого счетчика импульсов подключен к третьему входу логического элемента 3И, выход которого подключен к входу LVDS-передатчика; выход LVDS-передатчика подключен к входу LVDS-приемника; выход LVDS-приемника подключен к входу логического элемента НЕ, вторым входам второго и третьего логических элементов 2И; выход логического элемента НЕ подключен ко вторым входам первого и четвертого логических элементов 2И.

4. Способ повышения отказоустойчивости многоканальной самодиагностируемой вычислительной системы с резервированием замещением, заключающийся в диагностировании работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи, аналогичной штатной, с заранее выбранными начальными данными, сравнении результата решения диагностической задачи с заранее известным результатом, и, в случае совпадения, формировании процессором импульсов исправности активного канала, анализе поступления импульсов исправности и их периода следования, отличающийся тем, что по результатам анализа импульсов исправности и периода их следования формируют последовательность логических сигналов, преобразуют их в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала.

5. Способ повышения отказоустойчивости многоканальной самодиагностируемой вычислительной системы с резервированием замещением, заключающийся в диагностировании работоспособности активного канала процессором самого канала в процессе периодического решения диагностической задачи, аналогичной штатной, с заранее выбранными начальными данными, сравнении результата решения диагностической задачи с заранее известным результатом и, в случае совпадения, формировании процессором импульсов исправности активного канала, анализе поступления импульсов исправности и их периода следования, отличающийся тем, что по результатам анализа импульсов исправности и периода их следования формируют последовательность логических сигналов, преобразуют их в токовые сигналы противоположного направления, затем в логические сигналы противоположной полярности, которые затем преобразуют в синусоидальное напряжение и в постоянное напряжение для управления ключом отключения напряжения вторичного источника питания резервного канала.

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1998 |

|

RU2132083C1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Способ измерения давления на контактах релейных пружин | 1961 |

|

SU149603A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2017-10-24—Публикация

2016-12-09—Подача