Изобретение относится к контрольно-измерительной технике, предназначено для допускового контроля уровня переменных сигналов, в том числе амплитуды сигналов индукционных фазочувствительных датчиков, и может быть использовано в системах автоматики и телемеханики, где требуется высокая точность, быстродействие и помехоустойчивость.

Известно двухпороговое устройство контроля уровня напряжения, описанное в авторском свидетельстве SU 995003 с приоритетом от 07.08.1981 г., содержащее делитель опорного напряжения, инвертор, три пороговых элемента, соединенные первыми входами с соответствующими выводами делителя опорного напряжения, а вторыми - с входной клеммой устройства, два триггера, первые входы которых соединены с выходами соответствующих пороговых элементов, элемент совпадения, входы которого соединены с выходами соответствующих триггеров, и исполнительный орган, в котором выход третьего порогового элемента соединен с входом инвертора и первым входом исполнительного органа, выход инвертора соединен со вторыми входами триггеров, а второй вход исполнительного органа соединен с выходом элемента совпадения.

Недостатком устройства является восприимчивость к импульсным помехам в измерительных цепях, вызывающих ложные срабатывания устройства и нечувствительность к фазе контролируемого сигнала.

Прототипом является двухпороговое устройство контроля уровня напряжения, описанное в авторском свидетельстве SU 625167 с приоритетом от 03.04.1975 г., содержащее делитель напряжения, выходы которого подключены к входам двух пороговых устройств соответственно, элемент совпадения и исполнительный орган, при этом в него введены генератор тактовых импульсов, дифференцирующая цепь, элемент запрета и два триггера, каждый из которых включен между выходом соответствующего порогового устройства и входом элемента совпадения, выход которого через элемент запрета соединен с входом исполнительного органа, причем выход генератора тактовых импульсов подключен ко второму входу элемента запрета и через дифференцирующую цепь соединен с установочными входами триггеров.

Недостатком прототипа является его восприимчивость к импульсным помехам в измерительных цепях, вызывающих ложные срабатывания устройства и нечувствительность к фазе контролируемого сигнала.

Задача изобретения - контроль уровня сигналов фазочувствительных датчиков при высокой помехоустойчивости устройства и сохранении высокого быстродействия устройства.

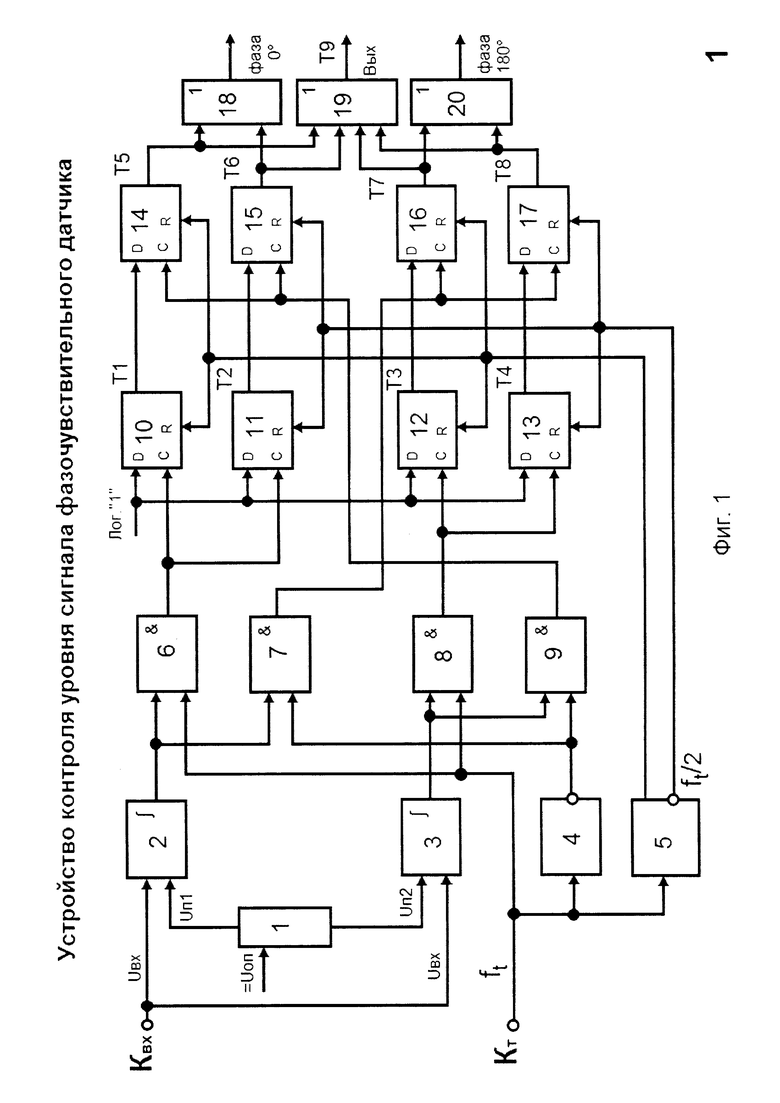

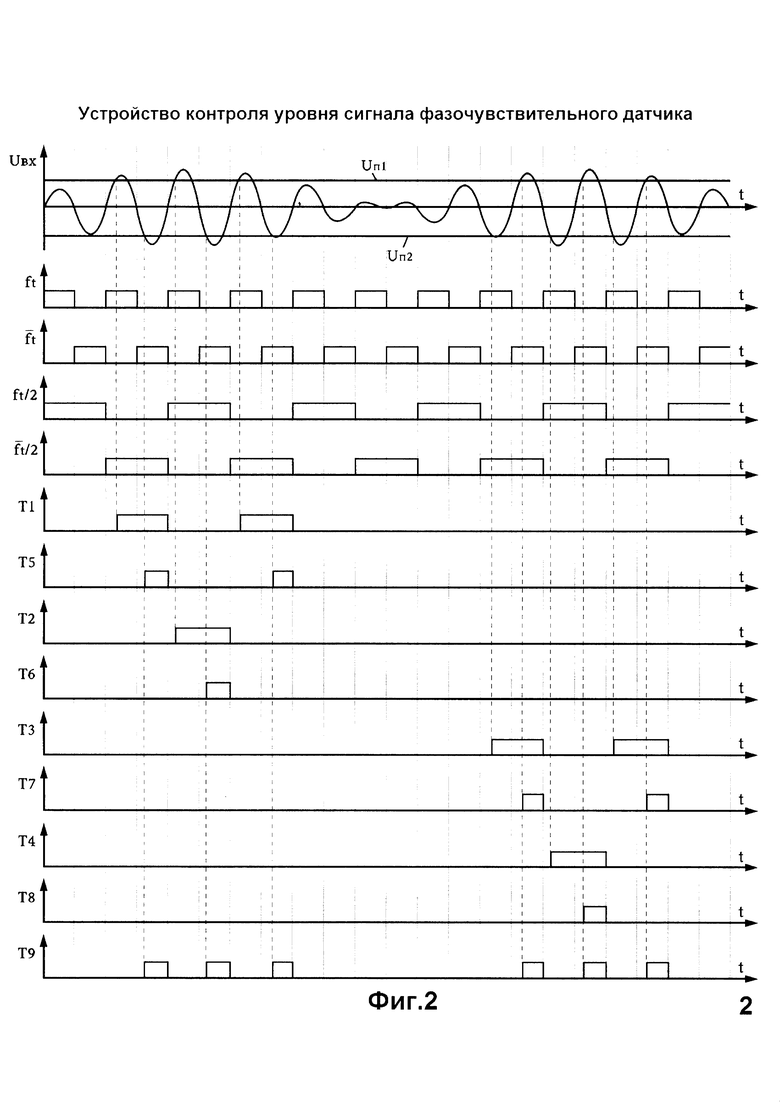

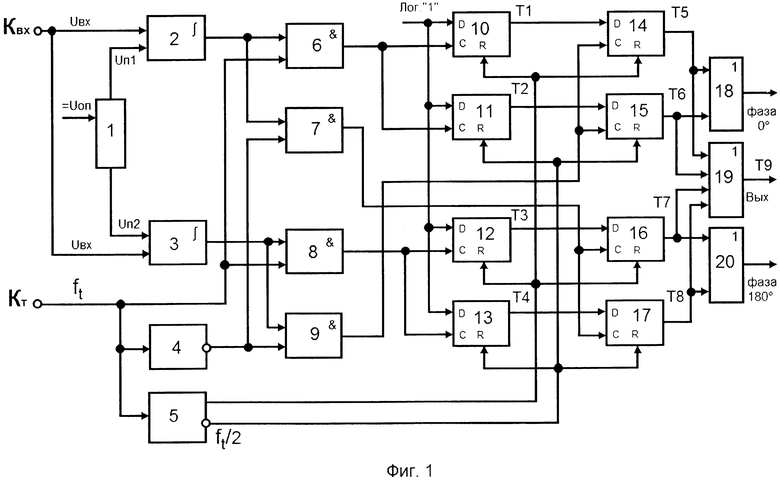

На фиг. 1 изображена функциональная схема устройства, на фиг. 2 - графики напряжений в различных точках схемы.

Устройство контроля уровня сигнала фазочувствительного датчика содержит (фиг. 1):

Квх входная клемма;

Кт клемма тактового сигнала;

1. Делитель опорного напряжения;

2. Первый пороговый элемент;

3. Второй пороговый элемент;

4. Инвертор;

5. Делитель частоты на два;

6. Первый элемент совпадения;

7. Второй элемент совпадения;

8. Третий элемент совпадения;

9. Четвертый элемент совпадения;

10. Первый триггер;

11. Второй триггер;

12. Третий триггер;

13. Четвертый триггер;

14. Пятый триггер;

15. Шестой триггер;

16. Седьмой триггер;

17. Восьмой триггер;

18. Первый элемент ИЛИ;

19. Исполнительный орган;

20. Второй элемент ИЛИ.

Элементы на схеме устройства контроля уровня сигнала фазочувствительного датчика имеют следующие связи:

Первый и второй выходы делителя опорного напряжения (1) подключены к первым входам первого (2) и второго (3) пороговых элементов, вторые входы которых соединены с входной клеммой (Квх) устройства. Выход первого порогового элемента (2) соединен с первыми входами первого (6) и второго (7) элементов совпадения, а выход второго порогового элемента (3) соединен с первыми входами третьего (8) и четвертого (9) элементов совпадения. Входы инвертора (4), делителя частоты на два (5) и вторые входы первого (6) и третьего (8) элементов совпадения подключены к клемме тактового сигнала (Кт). Вторые входы второго (7) и четвертого (9) элементов совпадения подключены к выходу инвертора (4). Выход первого элемента совпадения (6) соединен с входами синхронизации первого (10) и второго (11) триггеров, выход второго элемента совпадения (7) соединен с входами синхронизации седьмого (16) и восьмого (17) триггеров, выход третьего элемента совпадения (8) соединен с входами синхронизации третьего (12) и четвертого (13) триггеров, выход четвертого элемента совпадения (9) соединен с входами синхронизации пятого (14) и шестого (15) триггеров. На установочные входы первого (10), второго (11), третьего (12) и четвертого (13) триггеров подается сигнал логической единицы, а их выходы соединены с установочными входами пятого (14), шестого (15), седьмого (16) и восьмого (17) триггеров соответственно. Входы сброса первого (10), третьего (12), пятого (14) и седьмого (16) триггеров соединены с прямым выходом делителя частоты на два (5), инверсный выход которого соединен с входами сброса второго (11), четвертого (13), шестого (15) и восьмого (17) триггеров. Выходы пятого (14) и шестого (15) триггеров соединены соответственно с первым и вторым входами первого элемента ИЛИ (18) и исполнительного органа (19). Выходы седьмого (16) и восьмого (17) триггеров соединены соответственно с первым и вторым входами второго элемента ИЛИ (20), а также с третьим и четвертым входами исполнительного органа (19), выход которого является выходом устройства. Выходы первого (18) и второго (20) элементов ИЛИ являются дополнительными выходами устройства.

Триггеры устройства образуют четыре пары, осуществляющие селекцию уровня сигнала:

- первый (10) и пятый (14) триггеры - первая пара триггеров;

- второй (11) и шестой (15) триггеры - вторая пара триггеров;

- третий (12) и седьмой (16) триггеры - третья пара триггеров;

- четвертый (13) и восьмой (17) триггеры - четвертая пара триггеров.

Устройство работает следующим образом (фиг. 2).

Контролируемый переменный сигнал Uвх с фазой 0° (Uвх0) или с фазой 180° (Uвх180) и с частотой fs подается на первый (2) и второй (3) пороговые элементы, в которых производится сравнение с пороговыми напряжениями, поступающими с делителя опорного напряжения (1).

В первом полупериоде сигнал Uвх0 сравнивается со значением верхнего порогового уровня Uп1, а во втором полупериоде - нижнего Uп2, a Uвх180, наоборот, в первом полупериоде сравнивается с пороговым напряжением нижнего уровня Uп2, а во втором - верхнего Uп1. Значения Uп1 и Uп2 выбираются из условия допустимых уровней в положительном и отрицательном полупериодах сигнала Uвх.

При Uп1>Uвх>Uп2 на выходах первого (2) и второго (3) пороговых элементов, а также первого (6), второго (7), третьего (8) и четвертого (9) элементов совпадения будет сигнал логического «0».

На клемму тактового сигнала (Кт) подаются прямоугольные тактовые импульсы с частотой ft=fs, которые являются синфазными с Uвх0 и противофазными к Uвх180. Они поступают на входы инвертора (4), делителя частоты на два (5), первого (6) и третьего (8) элементов совпадения. В первом полупериоде ft равен логической «1», а во втором полупериоде - логическому «0». Инвертор (4) преобразует входную логическую «1» в «0», а логический «0» в «1». Выходной сигнал инвертора поступает на входы второго (7) и четвертого (9) элементов совпадения.

Таким образом, первый (6) и четвертый (9) элементы совпадения реагируют на сигнал Uвх0 и управляют первой и второй парами триггеров, а второй (7) и третий (8) - на сигнал Uвх180 и управляют третьей и четвертой парой триггеров.

На установочные входы первого (10), второго (11), третьего (12) и четвертого (13) триггеров постоянно подается сигнал логической «1».

Через период Uвх делитель частоты на два (5) формирует сигнал логической «1» на прямом выходе, который по входам сброса устанавливает в исходное состояние первую и третью пары триггеров, подготавливая их к приему информации со схем совпадения. На инверсном выходе в это время будет сигнал логического «0», разрешающий работу второй и четвертой парам триггеров. В следующий период Uвх на прямом выходе делителя частоты на два (5) устанавливается логический «0», разрешающий работу первой и третьей парам триггеров, а логическая «1» на инверсном выходе сбрасывает в исходное состояние вторую и четвертую пары триггеров.

Благодаря такому построению схемы исполнительный орган (четырехвходовый элемент ИЛИ) выдает сигнал логической «1» при превышении напряжением Uвх порогового уровня в каждом периоде входного сигнала, обеспечивая тем самым высокое быстродействие устройства.

Воздействие знакопостоянной или низкочастотной импульсной помехи может привести к переключению триггеров лишь в одном из полупериодов Uвх и поэтому не окажет влияния на выходные сигналы пятого (14), шестого (15), седьмого (16) и восьмого (17) триггеров. Благодаря этому достигается помехоустойчивость устройства.

Первый (18) и второй (20) двухвходовые элементы ИЛИ при этом формируют сигналы о фазе Uвх. Логическая «1» на выходе первого элемента ИЛИ (18) свидетельствует о том, что фаза Uвх равна 0°, а сигнал логической «1» с выхода второго элемента ИЛИ (20) свидетельствует о том, что фаза Uвх равна 180°.

Прохождение сигналов при Uвх0 (Фиг. 2).

В первом периоде Uвх сигнал ft, при помощи делителя частоты на два (5) устанавливает логический «0» на входах сброса второй и четвертой пар триггеров, что позволяет им принимать информацию, при этом на входах сброса первой и третьей пар триггеров действует логическая «1», что закрывает их для приема информации.

Если с входной клеммы (Квх) поступает сигнал Uвх0 и его амплитуда превысит в положительный полупериод значение Uп1, то первый пороговый элемент (2) установит логическую «1» на первом входе первого элемента совпадения (6), который при наличии логической «1» на первом и втором входах установит логическую «1» на входе синхронизации второго триггера (11). Наличие логической «1» на установочном входе и входе синхронизации второго триггера (11) переведет его выход и установочный вход шестого триггера (15) в состояние логической «1».

Если во втором полупериоде амплитуда Uвх0 достигнет нижнего уровня Uп2, то второй пороговый элемент (3) установит логическую «1» на первом входе четвертого элемента совпадения (9), который при наличии логической «1» с выхода инвертора на втором входе сформирует логическую «1» на входе синхронизации шестого триггера (15), вследствие чего выход триггера (15) перейдет в состояние логической «1» и активизирует первый элемент ИЛИ (18) и исполнительный орган (19).

Если превышения допустимых значений Uп1 и Uп2, не было или было превышено только одно из них, то первый элемент ИЛИ (18) и исполнительный орган (19) не активируются и начнется анализ сигнала Uвх0 в следующем периоде.

В следующем периоде Uвх0 сигнал ft, поступающий на вход блока делителя частоты на два (5), устанавливает логический «0» на входах сброса первой и третьей пар триггеров, что позволяет им принимать информацию, при этом на входы сброса второй и четвертой пар триггеров поступит логическая «1», что закроет их для приема информации. При этом работа устройства будет идентична предыдущему периоду, но сигналы с первого (6) и четвертого (9) элементов совпадения будут проходить через первую пару триггеров.

Таким образом, если в первом и втором полупериодах было зафиксировано превышение допустимых значений сигналов Uп1 и Uп2, то на установочном входе и входе синхронизации пятого триггера (14) установятся логические «1», что приведет к активации первого элемента ИЛИ (18) и исполнительного органа (19). Если превышения допустимых значений Uп1 и Uп2 не было зафиксировано или было превышено только одно из них, то на выходе пятого триггера (14) останется логический «0», первый элемент ИЛИ (18) и исполнительный орган (19) не активируются и начнется анализ сигнала Uвх в следующем периоде.

Прохождение сигналов при Uвх180 (Фиг. 2).

В первом периоде Uвх делитель частоты на два (5) под действием сигнала ft устанавливает логический «0» на входах сброса первой и третьей пар триггеров, что позволяет им принимать информацию, при этом на входы сброса второй и четвертой пар триггеров поступает логическая «1», что закрывает их для приема информации.

Если амплитуда сигнала Uвх180 на входной клемме (Квх) возрастет и достигнет нижнего значения Uп2, то второй пороговый элемент (3) сформирует логическую «1» на первом входе третьего элемента совпадения (8), который при наличии логической «1» на первом и втором входах установит логическую «1» на входе синхронизации третьего триггера (12). Наличие логической «1» на установочном входе и входе синхронизации третьего триггера (12) переведет его выход и установочный вход седьмого триггера (16) в состояние логической «1».

В следующем полупериоде на выходе инвертора (4) устанавливается логическая «1», которая поступает на второй вход второго элемента совпадения (7).

Если в этот полупериод амплитуда Uвх180 превысит верхнее значение Uп1, то первый пороговый элемент (2) сформирует логическую «1» на первом входе второго элемента совпадения (7), который при наличии логической «1» на первом и втором входах установит логическую «1» на входе синхронизации седьмого триггера (16), что приведет к активации второго элемента ИЛИ (20) и исполнительного органа (19).

Если превышения допустимых значений Uп2 и Uп1 не было зафиксировано или было превышено только одно из них, то на выходе седьмого триггера (16) остается логический «0», второй элемент ИЛИ (20) и исполнительный орган (19) не активируются и начнется анализ сигнала Uвх в следующем периоде.

В следующем периоде сигнала Uвх180 делитель частоты на два (5) устанавливает логический «0» на входах сброса второй и четвертой пар триггеров, что позволяет им принимать информацию, при этом на входы сброса первой и третьей пар триггеров поступает логическая «1», что закрывает их для приема информации. В результате этого работа устройства будет аналогична предыдущему периоду, но сигналы со второго (7) и третьего (8) элементов совпадения будут проходить через четвертую пару триггеров.

Таким образом, если в первом и втором полупериодах было зафиксировано превышение допустимых значений сигналов Uп2 и Uп1, то на установочном входе, входе синхронизации и выходе восьмого триггера (17) установятся логические «1», что приведет к активации второго элемента ИЛИ (20) и исполнительного органа (19). Если превышения допустимых значений Uп2 и Uп1 не было зафиксировано или было превышено только одно из них, то на выходе восьмого триггера (17) остается логический «0», второй элемент ИЛИ (20) и исполнительный орган (19) не активируется и начинается анализ сигнала Uвх в следующем периоде.

Техническим результатом изобретения является возможность порогового контроля уровня сигналов с разными фазами (0° или 180°) относительно тактового напряжения при высокой помехоустойчивости устройства, выражающейся в его защите от ложных срабатываний при воздействии низкочастотных и знакопостоянных импульсных помех.

Технический результат достигается тем, что в устройство контроля уровня сигнала фазочувствительного датчика, содержащее делитель опорного напряжения (1), выходы которого подключены к первым входам первого (2) и второго (3) пороговых элементов, которые соединены вторыми входами с входной клеммой (Квх) устройства, первый (10) и пятый (14) триггеры и исполнительный орган (19), введены инвертор (4), делитель частоты на два (5), первый (6), второй (7), третий (8) и четвертый (9) элементы совпадения, второй (11), третий (12), четвертый (13), шестой (15), седьмой (16) и восьмой (17) триггеры, первый (18) и второй (20) элементы ИЛИ, причем выход первого порогового элемента (2) соединен с входами первого (6) и второго (7) элементов совпадения, а выход второго (3) порогового элемента соединен с входами третьего (8) и четвертого (9) элементов совпадения, второй вход первого (6) и третьего (8) элементов совпадения, входы инвертора (4) и делителя частоты на два (5) соединены с клеммой тактового напряжения (Кт), выход инвертора (4) соединен со вторыми входами второго (7) и четвертого (9) элементов совпадения, на установочные входы первого (10), второго (11), третьего (12) и четвертого (13) триггеров подается сигнал логической единицы, входы синхронизации первого (10) и второго (11) триггеров соединены с выходом первого элемента совпадения (6), входы синхронизации третьего (12) и четвертого (13) триггеров соединены с выходом третьего элемента совпадения (8), выходы первого (10) и второго (11) триггеров соединены с установочными входами пятого (14) и шестого (15) триггеров соответственно, входы синхронизации которых соединены с выходом четвертого элемента совпадения (9), выходы третьего (12) и четвертого (13) триггеров соединены с установочными входами седьмого (16) и восьмого (17) триггеров соответственно, входы синхронизации которых соединены с выходом второго элемента совпадения (7), прямой выход делителя частоты на два (5) соединен с входами сброса первого (10), третьего (12), пятого (14) и седьмого (16) триггеров, а его инверсный выход соединен с входами сброса второго (11), четвертого (13), шестого (15) и восьмого (17) триггеров, выходы пятого (14) и шестого (15) триггеров соединены с входами первого элемента ИЛИ (18) и исполнительного органа (19), выходы седьмого (16) и восьмого (17) триггеров соединены с входами исполнительного органа (19) и второго элемента ИЛИ (20), выход исполнительного органа (19) является основным, а первого (18) и второго (20) элементов ИЛИ - дополнительными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля уровня переменного напряжения | 2017 |

|

RU2658564C1 |

| УСТРОЙСТВО ОДНОКРАТНОГО ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ | 1996 |

|

RU2145154C1 |

| СЛЕДЯЩИЙ ИНВЕРТОР С ДВУХПОЛЯРНОЙ ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 2001 |

|

RU2202144C2 |

| Система автоматического управления очистным комбайном в профиле пласта | 1985 |

|

SU1270321A1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| Устройство для измерения площади непрозрачных плоских фигур | 1989 |

|

SU1663431A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для измерения внутреннего угла синхронной машины | 1984 |

|

SU1226331A1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2016 |

|

RU2636750C1 |

| Способ управления подачей инструмента на электроэрозионном станке с емкостным генератором импульсов и устройство для его осуществления | 1980 |

|

SU1351523A3 |

Изобретение относится к контрольно-измерительной технике, предназначено для допускового контроля уровня переменных сигналов, в том числе амплитуды сигналов индукционных фазочувствительных датчиков, и может быть использовано в системах автоматики и телемеханики, где требуется высокая точность, быстродействие и помехоустойчивость. Задача изобретения - контроль уровня сигналов фазочувствительных датчиков при высокой помехоустойчивости устройства и сохранении высокого быстродействия устройства. Устройство контроля уровня переменного напряжения содержит делитель опорного напряжения, выходы которого подключены к первым входам первого и второго пороговых элементов, которые соединены вторыми входами с входной клеммой устройства, первый и пятый триггеры и исполнительный орган. Согласно изобретению в устройство введены инвертор, делитель частоты на два, первый (6), второй, третий и четвертый элементы совпадения, второй, третий, четвертый, шестой, седьмой и восьмой триггеры, первый и второй элементы ИЛИ, причем выход первого порогового элемента соединен с входами первого и второго элементов совпадения, а выход второго порогового элемента соединен с входами третьего и четвертого элементов совпадения, второй вход первого и третьего элементов совпадения, входы инвертора и делителя частоты на два соединены с клеммой тактового напряжения, выход инвертора соединен со вторыми входами второго и четвертого элементов совпадения, на установочные входы первого, второго, третьего и четвертого триггеров подается сигнал логической единицы, входы синхронизации первого и второго триггеров соединены с выходом первого элемента совпадения, входы синхронизации третьего и четвертого триггеров соединены с выходом третьего элемента совпадения, выходы первого и второго триггеров соединены с установочными входами пятого и шестого триггеров соответственно, входы синхронизации которых соединены с выходом четвертого элемента совпадения, выходы третьего и четвертого триггеров соединены с установочными входами седьмого и восьмого триггеров соответственно, входы синхронизации которых соединены с выходом второго элемента совпадения, прямой выход делителя частоты на два соединен с входами сброса первого, третьего, пятого и седьмого триггеров, а его инверсный выход соединен с входами сброса второго, четвертого, шестого и восьмого триггеров, выходы пятого и шестого триггеров соединены с входами первого элемента ИЛИ и исполнительного органа, выходы седьмого и восьмого триггеров соединены с входами исполнительного органа и второго элемента ИЛИ, выход исполнительного органа является основным, а первого и второго элементов ИЛИ - дополнительными выходами устройства. Техническим результатом изобретения является возможность порогового контроля уровня сигналов с разными фазами (0° или 180°) относительно тактового напряжения при высокой помехоустойчивости устройства, выражающейся в его защите от ложных срабатываний при воздействии низкочастотных и знакопостоянных импульсных помех. 2 ил.

Устройство контроля уровня сигнала фазочувствительного датчика, содержащее делитель опорного напряжения, выходы которого подключены к первым входам первого и второго пороговых элементов, которые вторыми входами соединены с входной клеммой устройства, первый и пятый триггеры и исполнительный орган, отличающееся тем, что в него введены инвертор, делитель частоты на два, первый, второй, третий и четвертый элементы совпадения, второй, третий, четвертый, шестой, седьмой и восьмой триггеры, первый и второй элементы ИЛИ, причем выход первого порогового элемента соединен с входами первого и второго элементов совпадения, а выход второго порогового элемента соединен с входами третьего и четвертого элементов совпадения, второй вход первого и третьего элементов совпадения, входы инвертора и делителя частоты на два соединены с клеммой тактового напряжения, выход инвертора соединен со вторыми входами второго и четвертого элементов совпадения, на установочные входы первого, второго, третьего и четвертого триггеров подается сигнал логической единицы, входы синхронизации первого и второго триггеров соединены с выходом первого элемента совпадения, входы синхронизации третьего и четвертого триггеров соединены с выходом третьего элемента совпадения, выходы первого и второго триггеров соединены с установочными входами пятого и шестого триггеров соответственно, входы синхронизации которых соединены с выходом четвертого элемента совпадения, выходы третьего и четвертого триггеров соединены с установочными входами седьмого и восьмого триггеров соответственно, входы синхронизации которых соединены с выходом второго элемента совпадения, прямой выход делителя частоты на два соединен с входами сброса первого, третьего, пятого и седьмого триггеров, а его инверсный выход соединен с входами сброса второго, четвертого, шестого и восьмого триггеров, выходы пятого и шестого триггеров соединены с входами первого элемента ИЛИ и исполнительного органа, выходы седьмого и восьмого триггеров соединены с входами исполнительного органа и второго элемента ИЛИ, выход исполнительного органа является основным, а выходы первого и второго элементов ИЛИ - дополнительными выходами устройства.

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОТКЛОНЕНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1990 |

|

RU2029312C1 |

| Универсальное устройство для контроля напряжения | 1983 |

|

SU1170359A1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| US 0004538194 A1, 27.08.1985 | |||

| US 4797608 A1, 10.01.1989 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2018-06-21—Публикация

2017-07-03—Подача