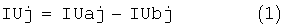

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения функции адресной коммутации на два цифровых информационных выхода с уровнем транзисторно-транзисторной логики множества входных цифровых дифференциальных (разностных) сигналов

любого двухполярного двухуровневого или трехуровневого самосинхронизирующегося последовательного двоичного кода в сложной помеховой обстановке при значительных величинах синфазной помехи

искажающей обе компоненты

сигнала IUj, т.е. при высоких значениях показателя помехоустойчивости

где j=1,..., N - номер канала коммутируемого входного сигнала IUj;

IUaj и IUbj - соответственно первая и вторая компоненты входного сигнала IUj, измеряемые относительно общей шины (корпуса);

|X|max - здесь и далее оператор выделения максимального значения модуля величины X, т.е. в (5) величины X=IUcj/IUj*;

/ - здесь и далее знак оператора арифметической операции деления;

IUj* - величина действующего (ненулевого) входного сигнала IUj.

Изобретение может использоваться, например, при построении многоканальных устройств для ввода последовательной информации в любом двухполярном двухуровневом или трехуровневом самосинхронизирующемся двоичном коде (NRZ - без возвращения к нулевому потенциалу при передаче избыточным кодом типа 4В/5В, фазоманипулированном коде Миллера, RZ - с возвращением к нулевому потенциалу, фазоманипулированном коде “Манчестер-2”, фазоманипулированном дифференциальном манчестерском коде и т.п., [1, с.47, рис.3.6]) в сложной помеховой обстановке при значительных величинах синфазной помехи, в частности, при построении многоканальных устройств типа [2] для ввода информации в системах проводной цифровой связи.

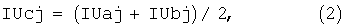

Известно [1, с.41], что практически никакие методы экранирования и разнесения проводов линий цифровой связи от энергетических проводов не могут гарантировать отсутствие в линии связи наводок. Это означает, что полезный сигнал IUj всегда существует совместно с помехами и задача заключается в гарантированном, т.е. с определенным запасом устойчивости, выделении сигнала на фоне помех. С учетом реальной естественной помеховой обстановки, например, в [1, с.41] считают, что условием бесперебойной работы аппаратуры является сигнал наводки в линии связи, не превышающий 10-20 В.

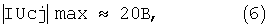

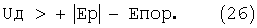

Таким образом, можно принять

где ≈ - здесь и далее знак приближенного равенства.

Однако в общем случае допустимая величина (6) синфазной помехи для многих применений может быть явно заниженной [3, с.283], и в частности, разработан измерительный усилитель с допустимым уровнем синфазной помехи до 50 В [3, с.279, рис.7.7 г].

На основании изложенного выше можно сказать, что создание коммутатора цифровых дифференциальных сигналов с требуемыми характеристиками (необходимым быстродействием при приемлемых аппаратурных затратах и помехоустойчивостью, с запасом удовлетворяющей условию (6)) для сигнала любого двухполярного двухуровневого или трехуровневого самосинхронизирующего кода представляет актуальную техническую задачу, разрешение которой позволит в целом повысить качество разрабатываемых устройств для ввода информации, например, типа [2], являющихся составными частями современных систем проводной цифровой связи.

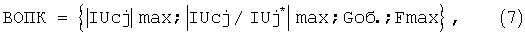

Представляется логичным качество коммутатора (и/или устройства для ввода информации) оценивать вектором основных (т. е. учитываемых в процессе разработки) показателей качества

координатами которого являются:

|IUcj|max - максимальное значение модуля синхронной помехи;

|lUcj/IUj*|max - показатель помехоустойчивости (5);

Goб. - объем оборудования;

Fmax - максимальная битовая скорость (частота) приема информации.

Объем оборудования коммутатора можно оценивать, например, с помощью формулы

в количестве Goб. эквивалентных корпусов, где за единицу измерения принят, например, корпус микросхемы 590КН6, а остальные электронные компоненты сравниваются с единицей измерения по площади, занимаемой на печатной плате, причем G1, G2 и G3 - эквивалентные объемы оборудования, приходящиеся на микросхемы, резисторы и конденсаторы соответственно.

Для решения задачи приема и коммутации информации в коде RZ разработана специализированная двухканальная интегральная микросхема (ИС) 1567АП1 входного формирователя последовательного кода RZ по ГОСТ 18977 (ARING), представляющая собой устройство для приема двух дифференциальных цифровых сигналов U1 и U2 с разрешаемой коммутацией любого из них на два цифровых выхода с открытым коллектором (выход D0 информации и выход С0 синхронизации).

Как функционально законченное устройство ИС 1567АП1 содержит [1, с.80-83] входы первых и вторых компонент двух дифференциальных сигналов U1 и U2, цифровые выходы с открытым коллектором информационного сигнала D0 и сигнала С0 синхронизации, контрольные выходы OR1 и OR2 первого и второго внутренних резисторов соответственно, вход С1 для подключения внешнего конденсатора для задержки импульса С0 синхронизации, цифровые входы сигнала СЕ разрешения приема (выходы D0 и С0 при СЕ=1 разрешены, а при СЕ=0 запрещены) и сигнала SED выбора канала приемника (выбирается при SED=0 канал приемника сигнала U1, а при SED=1 - канал приемника сигнала U2), вход общей шины (корпуса), вход от источника положительного напряжения Uп1=(5±0,5) В и вход от источника отрицательного напряжения Uп2∈[-16,5 В, -4,5 В], где ∈ - здесь и далее знак принадлежности величины, находящейся слева от знака, отрезку, находящемуся справа от знака.

Основными параметрами ИС 1567АП1 являются: минимальное положительное дифференциальное напряжение срабатывания Umin=+5 В; максимальное отрицательное дифференциальное напряжение срабатывания Umax=-5 В; входное сопротивление для каждой компоненты любого дифференциального входа Rвх.≥20 кОм; модуль входного синфазного сигнала по любому каналу |Uc|≤15 В; частота приема входного дифференциального сигнала RZ кода по любому каналу F∈[10 кГц, 1 МГц].

Для обеспечения работы ИС 1567АП1 на входы питания необходимо подать от источников напряжения питания Uп1 и Uп2 с подключением к контактам микросхемы для каждого источника фильтрующего конденсатора Сф=0,1 мкФ, контакт С1 подключить через внешний конденсатор Сз задержки к корпусу, а выходы D0 и С0 через внешние резисторы подключить к питанию Uп1.

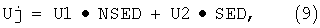

С учетом изложенного выше и [1, с.81, табл. 5] функционирование устройства (ИС 1567АП1 с дополненными внешними резисторами и конденсаторами) логически можно описать следующим образом.

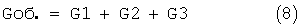

По входному сигналу SED в устройстве для последующей обработки выбирается дифференциальное напряжение одного из каналов

где

NSED - инверсное значение цифрового сигнала SED;

• - здесь и далее знак оператора арифметической операции умножения.

Далее по дифференциальному напряжению (9) выбранного канала и входному цифровому сигналу СЕ разрешения приема устройство формирует выходные цифровые сигналы D0 и С0 в соответствии с выражениями

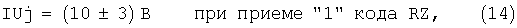

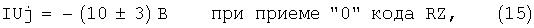

По ГОСТ 18977-79 и РТМ 1495-75 (см., например, [4, с.57-54]) в коде RZ каждый бит информации передается дифференциальным сигналом IUj в течение битового периода Т=Т1+Т2 при Т1=Т2 так, что в активной части Т1=Т/2 битового периода на входах устройства

а при возврате к нулю в части Т2=Т/2 битового периода или в течение паузы

определяется величиной

где Т - период частоты следования импульсов битовой синхронизации передачи информации.

По уровню синхронной помехи ИС 1567АП1 не удовлетворяет требованию (6), но имеет (см. (12) и (13)) минимальный модуль порога срабатывания |Ucp.|min=5 В значительно меньше минимального модуля |IUj|*min=7 В входного сигнала IUj кода RZ, принимаемого в периоде Т1 согласно ГОСТ 18977 - см. выражения (14)-(17). В подобном случае для повышения помехоустойчивости и расширения динамического диапазона на входе каждой компоненты дифференциального входа приемника целесообразно [1, с.47, рис.4.13] установить делитель напряжения с коэффициентом деления Кд=5,5/7, обеспечивающий при |IUj*|min=7 В формирование на каждом дифференциальном входе ИС 1567АП1 модуля дифференциального напряжения величины |Uj|min=5,5 В. В этом случае помехоустойчивость устройства можно оценить максимальной величиной синфазной помехи

и показателем помехоустойчивости

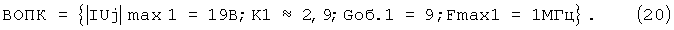

Таким образом, из уровня современной техники следует, что на основе ИС 1567АП1 легко построить качественный (с показателями помехоустойчивости (18) и (19) и Fmax1=1 МГц) коммутатор сигналов IUj кода RZ, содержащий N/2 ИС 1567АП1, каждая из которых снабжена тремя конденсаторами (два из которых необходимы для фильтрации напряжений Uп1 и Uп2 питания и один - для задержки импульса С0), два аттенюатора, каждый из которых содержит N делителей напряжения с коэффициентом деления Кд=5,5/7, входы первых и вторых компонент цифровых дифференциальных сигналов, через первый и второй аттенюаторы согласованно связанные с дифференциальными входами всех ИС, два резистора, первые вводы которых соединены с шиной положительного напряжения питания, цифровой информационный выход, соединенный с выходами D0 информации всех ИС и вторым выводом первого резистора, цифровой выход синхронизации, соединенный с выходами С0 синхронизации всех ИС, дешифратор и n-разрядный кодовый вход адреса (где 2 в степени n равно N), вход младшего разряда которого соединен с входами SED всех ИС, входы СЕ разрешения приема которых согласованно соединены с выходами дешифратора, входы которого соединены с входами старших разрядов кодового входа адреса.

Для N=8 объем оборудования описываемого коммутатора, содержащего шесть микросхем (четыре ИС 1567АП1 в корпусе типа 4105.14-05 и две ИС дешифратора, например, серии 1533 (ЛИ1 - четыре логических элемента 2И и ЛН1 - шесть логических элементов НЕ) в корпусе с 14 контактами, 34 резистора типа P1-12-0,25 и 14 конденсаторов типа К10-73-1 в, оценивается величиной

Goб.1=G1+G2+G3=5+2+2=9,

а качество данного коммутатора характеризуется вектором

Основным недостатком описанного коммутатора является низкая помехоустойчивость (т.е. показатель |Uj|max1=19 В практически не удовлетворяет условию (6)) и ограниченные функциональные возможности, обусловленные специализацией устройства для работы только с входным сигналом IUj кода RZ, который, согласно (14) и (15), имеет значительный действующий уровень |IUj*|=(7-13)В.

Известные коммутаторы сигналов типа [5], [6] и [7] не смогут обеспечить (например, два коммутатора по двум каналам) коммутацию сигнала (1) при условии (6), так как по каждому каналу могут передать компоненту сигнала (1) при низком уровне помехи, т.е. при показателе (5) меньшем единицы.

Из известных технических решений наиболее близким по технической сущности к предлагаемому является коммутатор цифровых дифференциальных сигналов [8], содержащий первый и второй компараторы, выходы которых являются первым и вторым цифровыми выходами коммутатора соответственно, первый и второй мультиплексоры-демультиплексоры, формирователи положительного и отрицательного пороговых напряжений, выходы которых соединены соответственно с инверсным входом первого компаратора и прямым входом второго компаратора, дифференциальный усилитель, выход которого соединен с прямым входом первого компаратора и инверсным входом второго компаратора, кодовый вход адреса коммутируемого канала, соединенный с адресными входами первого и второго мультиплексоров, первый и второй многоканальные аттенюаторы и входы первых и вторых компонент цифровых дифференциальных сигналов, связанные через каналы первого и второго аттенюаторов с информационными входами соответственно первого и второго мультиплексоров-демультиплексоров, выходы которых соединены с неинвертирующим и инвертирующим входами дифференциального усилителя соответственно, причем каждый из аттенюаторов в каждом канале содержит делитель напряжения, образованный двумя резисторами, первый вывод первого из которых соединен с входом канала, а второй вывод первого резистора соединен с выходом канала и первым выводом второго резистора, второй вывод которого соединен с общей шиной (корпусом).

Работа коммутатора [8] описана при приеме кода RZ (определен выражениями (14)-(17)) для N=8 при реализации дифференциального усилителя и компараторов на основе трех операционных усилителей (ОУ).

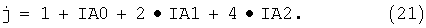

В процессе функционирования коммутатор [8] по входному коду IA(0:2)=IA0 IA1 IA2 адреса, первым IUa(1:8) и вторым IUb(1:8) компонентам входных дифферециальных сигналов IU(1:8) вырабатывает на первом (или втором) цифровом информационном выходе цифровой сигнал Z1 приема “1” (или Z2 приема “0”) кода RZ для выбранного канала

Сопротивления резисторов делителей аттенюаторов (R1=5,1 кОм, R2=2,7 кОм) и параметры дифференциального усилителя выбраны такими, что напряжение IUj выбранного канала (21) передается через аттенюаторы и мультиплексоры на выход дифференциального усилителя с заградительной фильтрацией и коэффициентом усиления Ку≈0,3 согласно выражению

т.е. в идеальном случае в напряжении (22) на выходе дифференциального усилителя синфазная помеха отсутствует.

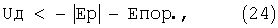

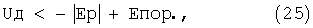

Напряжение (22) поступает на прямой (или инверсный) вход первого (или второго) компаратора, выполненного как триггер Шмитта на основе ОУ с напряжением |2•Ер| ширины петли гистерезиса, и сравнивается с положительным +Епор. (или отрицательным -Епор.) пороговым напряжениям. В этой связи первый или второй компаратор переключает из “0” в “1” выходной цифровой сигнал Z1 или Z2 соответственно при условиях

и, наоборот, первый или второй компаратор переключает из “1” в “0” выходной сигнал Z1 или Z2 соответственно при следующих условиях:

Из описания работы коммутатора [8] видно, что в процессе приема и преобразования каждый выбранный входной дифференциальный сигнал IUj проходит два уровня обработки: сначала линейный согласно (22) с заградительной фильтрацией синфазной помехи IUcj с помощью дифференциального усилителя, а затем нелинейный с помощью первого (или второго) компаратора согласно (23) и (25) (или (24) и (26)). В этой связи быстродействие коммутатора [8] определяется быстродействием двух последовательных уровней обработки на ОУ.

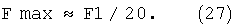

Быстродействие ОУ определяется частотой единичного усиления F1 - значением частоты входного сигнала, при котором значение коэффициента усиления напряжения ОУ падает до единицы [9, с.333].

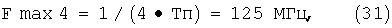

Быстродействие коммутатора [8], с учетом характеристики F1 и двойной последовательной обработки сигнала IUj на основе ОУ, можно оценить формулой

При величинах источников питания Е=+15В, -Е=-15В и Кд=R2/(R1+R2)=2,7/7,8≈0,35 помехоустойчивость коммутатора [8] для обработки выбранного сигнала IUj кода RZ определяется величинами |IUcj|max=35 В, К=5.

На современной элементной базе возможны две основные практические реализации коммутатора [8]: первая с использованием одной четырехканальной микросхемы типа 1401УД1 с F1=2,5 МГц - см. в [9, табл. 5.8 на с 358, 359]; вторая с использованием трех микросхем типа 544УД2 с F1=15 МГц-см. в [9, табл. 5.4 на с 349].

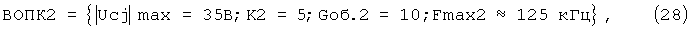

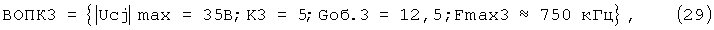

Для N=8 первая (или вторая) реализация коммутатора [8] содержит две ИС 590КН6, ИС 2ДС627А диодной матрицы из восьми диодов, 46 резисторов типа Р1-12-0,25 с допуском ±2%, четыре прецизионных резистора типа С2-29В-10 кOм ±0,1%, два переменных резистора типа С5-16ВА-0,25-300 Ом ±10%, одну ИС 1401УД1 (или три ИС 544УД2), два конденсатора типа К10-17а-М47-51 пФ ±10% для компараторов и шесть (или 10) конденсаторов типа К10-73-1в для фильтрации напряжений питания +Е=15В и -Е=-15В. По формуле (8) оцениваем объем оборудования Goб.2=10 первой и Goб.3=12,5 второй реализации коммутатора [8] с учетом того, что одному эквивалентному корпусу соответствует каждая ИС и каждая совокупность следующих электронных компонент: 16 резисторов P1-12-0,25; четыре резистора С2-29В-0.25 и два конденсатора К10-17а-М47; два резистора С5-16ВА-0,25; восемь конденсаторов К10-73-1в.

Таким образом, качество реализации коммутатора [8] с использованием ИС 1401УД1 оценивается вектором

а с использованием трех ИС 544УД2 – вектором

Из сравнения векторов (20) и (28) (или (29)) видно, что по сравнению с первым описанным техническим решением коммутатор [8] имеет высокую помехоустойчивость при больших аппаратурных затратах и меньшем быстродействии.

Основным недостатком коммутатора [8] является аппаратурная сложность и низкое быстродействие, обусловленные недостаточным использованием функциональных возможностей компараторов и реализацией их на основе традиционных ОУ, что привело к последовательной двойной обработке выбранного дифференциального сигнала (сначала линейной согласно (22), а затем нелинейной согласно (23)÷(26)).

В современном представлении [3, с.139-144] компаратор - прежде всего элемент для перехода от аналогового сигнала к цифровому, который является быстродействующим дифференциальным усилителем постоянного тока с большим усилением, малым дрейфом и сдвигом и логическим выходом. Входной каскад компаратора должен обладать большим коэффициентом ослабления синфазного сигнала (КОСС) и способностью выдерживать большие синфазные и дифференциальные сигналы на входах, не насыщаясь, не попадая в режимы, из которых компаратор долго будет выходить.

Известно [10, с.201-303], что компараторы, специально разработанные для преобразования непрерывных сигналов в дискретные (цифровые), имеют ряд преимуществ по сравнению с обычными ОУ и переключаются гораздо быстрее их. Поэтому построение компаратора на основе традиционного ОУ приводит к дополнительным аппаратурным затратам, например, в прототипе [8]: подключению входов компаратора к входам ОУ через элемент защиты ОУ от перегрузок через двухсторонний ограничитель, содержащий два резистора и два диода; подключению выхода компаратора к выходу ОУ через элемент перехода от аналогового сигнала к цифровому через двухсторонний диодный ограничитель, содержащий два резистора и два диода.

Предлагаемым изобретением решается задача повышения быстродействия коммутатора и его упрощения за счет исключения дифференциального усилителя и формирователей пороговых напряжений и использования функциональных возможностей компараторов как для заградительной фильтрации синхронной помехи, так и для перехода от аналогового сигнала к цифровому.

Для достижения этого технического результата в коммутатор цифровых дифференциальных сигналов, содержащий два многоканальных аттенюатора, каждый канал каждого из которых образован двумя резисторами, через первый из которых вход канала связан с выходом канала, который через второй резистор связан с общей шиной (корпусом) коммутатора, двухпортовый мультиплексор-демультиплексор (может быть реализован, например, для N=4 на одной двухпортовой ИС типа 590КН3, а для N=8 или на одной двухпортовой ИС типа 591КН2, либо на двух однопотровых ИС типа 590КН6), входы первых и вторых компонент цифровых дифференциальных сигналов, связанные соответственно через каналы первого и второго аттенюаторов с информационными входами каналов первого и второго портов мультиплексора-демультиплексора, кодовый вход адреса коммутируемого канала, соединенный с адресным входом мультиплексора-демультиплексора, два компаратора и первый и второй цифровые информационные выходы, являющиеся выходами первого и второго компараторов соответственно, дополнительно введено десять резисторов, а неинвертирующий и инвертирующий входы первого компаратора связаны через первый и второй резисторы соответственно с выходами первого и второго портов мультиплексора-демультиплексора, выходы второго и первого портов которого связаны через третий и четвертый резисторы с неинвертирующим и инвертирующим входами второго компаратора соответственно, шина источника положительного напряжения коммутатора связана через пятый и шестой резисторы соответственно с инвертирующими входами первого и второго компараторов, общая шина коммутатора связана через седьмой и восьмой резисторы соответственно с неинвертирующими входами первого и второго компараторов, выходы которых связаны с их ненинвертирующими входами через девятый и десятый резисторы соответственно, причем сопротивления резисторов с первого по четвертый равны между собой, сопротивления пятого, седьмого и девятого резисторов равны сопротивлениям шестого, восьмого и десятого резисторов соответственно, и сопротивление пятого или шестого резистора равно сопротивлению параллельного соединения резисторов седьмого и девятого или восьмого и десятого сооветственно.

Автору неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение десяти резисторов, таких, что сопротивления резисторов с первого по четвертый равны между собой, сопротивления пятого, седьмого и девятого резисторов равны сопротивлениям шестого, восьмого и десятого резисторов соответственно, и сопротивление пятого или шестого резистора равно сопротивлению параллельного соединения резисторов седьмого и девятого или восьмого и десятого соответственно) предлагаемого коммутатора, обеспечивающие ему и повышение быстродействия, и сокращение объема оборудования.

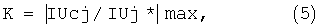

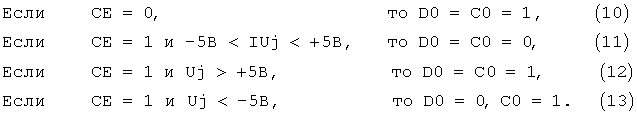

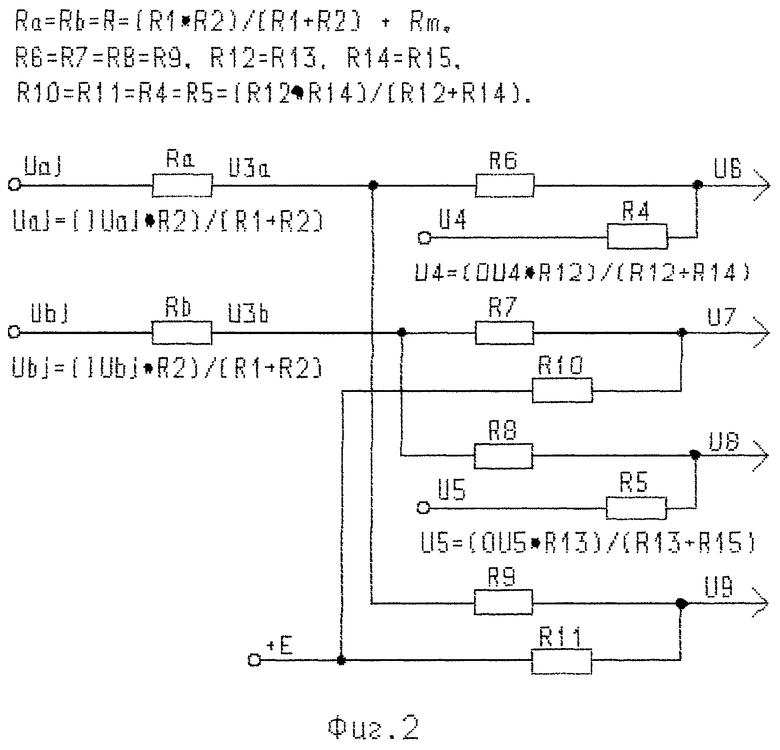

На фиг.1 приведена электрическая функциональная схема коммутатора цифровых дифференциальных сигналов, а на фиг.2 приведена эквивалентная электрическая функциональная схема коммутатора для его расчета и описания, полученная на основе метода эквивалентного генератора заменой выбранных трактов прохождения компонент IUaj и IUbj выбранного канала j и портов мультиплексора-демультиплексора, на соответствующие эквивалентные напряжения Uaj и Ubj и сопротивления Ra=Rb=R, и заменой первого (или второго) компаратора, седьмого (или восьмого) резистора и девятого (или десятого) резистора на соответствующие эквивалентные напряжение и резистор.

Коммутатор цифровых дифференциальных сигналов (фиг.1) содержит первый 1 и второй 2 многоканальные аттенюаторы, каждый канал каждого из которых образован двумя резисторами, через первый из которых вход канала связан с выходом канала, который через второй резистор связан с общей шиной (корпусом) коммутатора, двухпортовый мультиплексор-демультиплексор 3, входы первых и вторых компонент цифровых дифференциальных сигналов, связанные через каналы аттенюаторов 1 и 2 соответственно с информационными входами каналов первого и второго портов мультиплексора-демультиплексора 3, кодовый вход адреса коммутируемого канала, соединенный с адресным входом мультиплексора-демультиплексора 3, первый 4 и второй 5 компараторы, десять резисторов 6-15. Через первый 6 и второй 7 резисторы неинвертирующий и инвертирующий входы компаратора 4 связаны соответственно с выходами первого и второго портов мультиплексора-демультиплексора 3, выходы второго и первого портов которого связаны через третий 8 и четвертый 9 резисторы с неинвертирующим и инвертирующим входами компаратора 5 соответственно, шина источника положительного напряжения +Е коммутатора связана через пятый 10 и шестой 11 резисторы соответственно с инвертирующими входами компараторов 4 и 5, общая шина коммутатора связана через седьмой 12 и восьмой 13 резисторы соответственно с неинвертирующими входами компараторов 4 и 5, выходы которых связаны с их ненинвертирующими входами через девятый 14 и десятый 15 резисторы соответственно, причем сопротивления резисторов с первого 6 по четвертый 9 равны между собой (т.е. R6=R7=R8=R9), сопротивления пятого 10, седьмого 12 и девятого 14 резисторов равны сопротивлениям шестого 11, восьмого 13 и десятого 15 резисторов соответственно (т.е. R10=R11, R12=R13 и R14=R15), и сопротивление пятого 10 или шестого 11 резистора равно сопротивлению параллельного соединения резисторов седьмого 12 и девятого 14 или восьмого 13 и десятого 15 (т.е. R10=(R12•R14)/(R12+R14) или R11=(R13•R15)/(R13+R15)).

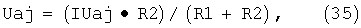

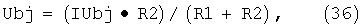

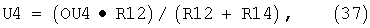

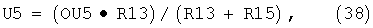

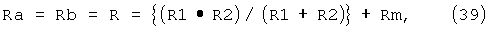

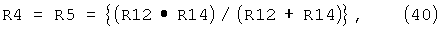

Эквивалентная функциональная электрическая схема коммутатора (фиг.2) для его расчета при любом выбранном канале j содержит входы эквивалентных напряжений Uaj=(IUaj•R2)/(R1+R2) и Ubj= (IUbj•R2)/(R1+R2), связанные через эквивалентные резисторы Ra= [(R1•R2)/(R1+R2)+Rm] и Rb=Ra с выходами напряжений первого U3a и второго U3b портов мультиплексора-демультиплексора 3 соответственно, (где R1 и R2 - сопротивления первого и второго резисторов любого канала аттенюатора 1 или 2; Rm - сопротивление между информационным входом выбранного канала первого или второго порта и выходом первого или второго порта мультиплексора-демультиплексора 3), выходы напряжений U6 и U7, являющихся напряжениями на неинвертирующем и инвертирующем входах компаратора 4, выходы напряжений U8 или U9, являющихся напряжениями на неинвертирующем и инвертирующем входах компаратора 5, резисторы R6 и R7, через которые выходы U3a и U3b связаны с выходами U6 и U7 соответственно, резисторы R8 и R9), через которые выходы U3b и U3a связаны с выходами напряжений U8 и U9 соответственно, входы эквивалентных напряжений U4=(OU4•R12)/(R12+R14) и U5=(OU5•R13)/(R13+R15), где OU4 и OU5 - напряжения на выходах компараторов 4 и 5 соответственно, и эквивалентные сопротивления R4=(R12•R14)/(R12+R14) и R5=(R13•R15)/(R13+R15), через которые входы эквивалентных напряжений U4 и U5 связаны с выходами напряжений U6 и U8 соответственно.

Эквивалентная схема (фиг.2) коммутатора получена на основе метода эквивалентного генератора [11, с.64-66], примененного, например, для получения эквивалентных U4 и R4 в такой последовательности: в схеме фиг.1 точку соединения резисторов R12 и R14 мысленно отключаем от точки соединения резистора R6 с неинвертирующим входом компаратора 4; в изолированной точке соединения резисторов R12 и R14 находим эквивалентное напряжение U4=OU4•R12/(R12+R14); изолированную точку соединения резисторов R12 и R14 мысленно соединяем с общей шиной и находим ток короткого замыкания Io=OU4/R14; вычисляем эквивалентное сопротивление R4= U4/Io=R12•R14/(R12+R14). Таким образом, напряжение OU4 (т.е. компаратор 4) и резисторы R12 и R14 представлены в схеме фиг.2 эквивалентными U4 и R4.

Для приема и обработки кода RZ при N=8 (т.е. n=3), напряжениях питания +Е=+15 В, -Е=-15В составные части коммутатора (фиг.1) реализованы так, что двухпортовый мультиплексор-демультиплексор выполнен на двух ИС 590КН6 (одна ИС 590КН6 позволяет адресно коммутировать напряжение с любого из восьми информационных каналов входного порта на информационный выходной порт в диапазоне напряжений от -Е до +Е при сопротивлении открытого канала Rm=300 Ом), компаратор 4 (или 5) содержит интегральный компаратор с открытым коллекторным выходом (ИС К554САЗ с параметрами [9, табл. 5.9 на с.362, 363]: напряжение смещения нуля Uсм=±3 мВ; входной ток Iвх=0,1 мкА; разность входных токов dIвх=0,01 мкА; коэффициент усиления по напряжению Кu=150000; время переключения Тп=200 нc, определяемое задержкой срабатывания и временем изменения выходного сигнала от уровня “1” до уровня “0” или наоборот; напряжения питания +Е=+15 В и -Е=-15 В) и резистор типа P1-12-0,25-1,5 кОм ±5%-М-А, первый вывод которого соединен с шиной напряжения питания +5 В, а второй вывод соединен с выходом интегрального компаратора, являющегося выходом компаратора 4 (или 5), инвертирующим и неинвертирующим выходами которого являются инвертирующий и неинвертирующий входы интегрального компаратора, в качестве 32 резисторов аттенюаторов 1 и 2 и резисторов 6-15 использованы резисторы типа Р1-16П-0,25 с допуском ±0,25%. Кроме того, в составе коммутатора имеется восемь конденсаторов типа К10-73-1в для фильтрации напряжений питания +Е=+15 В, -Е=-15 В для каждой ИС. Для данной реализации предлагаемого коммутатора объем оборудования оценивается числом эквивалентных корпусов

а быстродействие величиной

где Тп=200 нc - время переключения компаратора 4 (или 5), определяемое временем переключения ИС К554СА3.

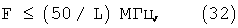

Передача информации прямоугольным дифференциальным сигналом Uj кода RZ формально определена выражениями (14)÷(17), но для реализации рекомендуется [1, с.34, рис.2.3] трапецеидальная форма дифференциального сигнала IUj, такая, что в каждом битовом интервале Т=Т1+Т2 период Т1 (или Т2) состоит из равных Т/4 по длительности переднего фронта и вершины (или заднего фронта и времени возврата к нулю). В этом случае содержание высших гармоник в спектре сигнала IUj уменьшается, а пропускная способность линии связи возрастает в восемь раз по сравнению с прямоугольной формой сигнала IUj. Для линии связи, несогласованной с нагрузкой, средняя пропускная способность передачи информации трапецеидальным дифференциальным сигналом Uj оценивается выражением

где L - длина линии связи в метрах.

Описание функционирования коммутатора и его расчет ведется далее с помощью обозначений, положений и методики расчета, определенных в следующих пунктах.

1. На входах каналов аттенюатора 1 (или 2) сигналы представлены в виде вектора IUa(1:N) (или IUb(1:N)), число координат в котором равно N=8.

2. При n=3 по сигналам входного кода адреса IА(0:2) мультиплексор-демультиплексор 3 подключает выход первого (или второго) порта через внутреннее сопротивление Rm=300 Ом выбранного канала j входного первого (или второго) порта и делитель напряжения j-го канала аттенюатоpa 1 (или 2) к входу напряжения IUaj (или IUbj), где номер канала j определен согласно (21).

3. Формируемое на выходе компаратора 4 (или 5) напряжение OU4 (или OU5) определяет цифровой информационный выходной сигнал Z4 (или Z5) коммутатора согласно выражениям

4. С помощью метода эквивалентного генератора величины эквивалентных напряжений и сопротивлений, приведенных на расчетной схеме (фиг.2) для выбранного канала j, определены формулами

где

R1 и R2 - сопротивления соответственно первого и второго резисторов канала j аттенюатора 1 (или 2);

Rm=300 Ом - сопротивление между выбранным входным каналом и выходом первого или второго порта мультиплексора-демультиплексора 3.

5. В общем случае при расчете коммутатора для выбранного канала j необходимо знать разность (U6-U7) (или (U8-U9)) как функцию напряжений Uaj, Ubj, +E и U4 (или U5) и сопротивлений резисторов R, R6-R15.

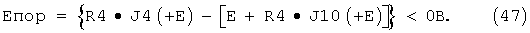

Далее с использованием метода наложения, справедливого для всех линейных электрических цепей [11, с.44, 45], определяем, например, разность (U6-U7) выражением

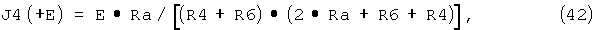

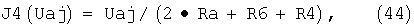

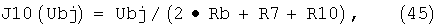

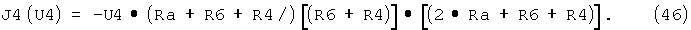

где J4=J4(+E)+J4(Uaj)+J4(U4) (или J10=J10(+E)+J10(Ubj)) - ток, текущий через сопротивление R4 (или R10) с положительным направлением от U6 к U4 (или U7 к +E).

По методу наложения при Uaj=Ubj=U4=U5=0 В определяем токи

при U4=U5=0 В и мысленном подключении к корпусу шины источника питания +E определяем токи

и при Uaj=0 и мысленном подключении к корпусу шины источника питания +E определяем ток

В установившемся состоянии в течение Т2 или паузы Тп коммутатор находится в состоянии возврата к нулю и между неинвертирующим и инвертирующим входами компаратора 4 (или 5) действует отрицательное напряжение (U6-U7) (или (U8-U9)), которое при Uaj=Ubj=U4=U5=0 В определим как пороговое

Подставляя в (47) J4(+E) из (42) и J10(+Е) из (43), с учетом Ra=Rb=R, R6=R7=R8=R9, R4=R5=R10=R11, после несложных преобразований получаем простое основное выражение

для расчета коммутатора вариацией величин Епор и R6 после определения R1 и R2.

6. На основе фиг.2, выражений (14)÷(17) и (33)÷(48) расчет коммутатора можно осуществить в следующей последовательности.

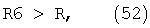

6.1. Расчет R1 и R2 проводится при известных значениях входного сопротивления Rвх канала и величине |IUcj| max и известном диапазоне изменения величины |IUj|. Например, определим R1 и R2 при условиях: (R1+R2)=Rвх∈[5,1 кOм, 8,2 кОм], |IUcj| max=(45-50) В, |Uaj| max (или |Ubj| max)≤+E=+15 В, |IUj| max)=+13 В, |IUj*| min=+7 В.

Подставляя в (35) исходные данные Uaj=+15 В и IUaj=(51,5÷56,5)В, получаем оценку величины

Кд=R2/(R1+R2)=15/(51,5÷56,5)=0,265÷0,291,

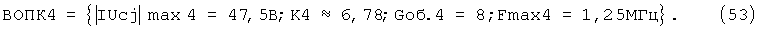

на основании которой методом последовательных приближений выбираем R1=3,9 кОм, R2=1,5 кОм и вычисляем: Кд=1,5/5,4≈0,277, Rвх=5,4 кOм, |IUcj| max4≈47,5 B, K4=6,78, Ra=Rb=R≈1,4 кOм (с учетом Rm=300 Ом), |Uj*| min=|IUj*| min•Кд=(7В)•0,277=1,9 В.

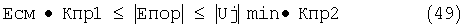

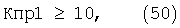

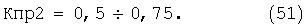

6.2. В общем случае определение величины Епор (47) следует проводить с учетом значений величин величины |Uj*| min=1,9 В (определена в п.6.1) и величины Есм=3 мВ (параметр ИС 554СА3 компаратора 4 или 5) с соблюдением ограничения

с коэффициентами пропорциональности, определяемыми, например, выражениями

В результате проведения п.6.2, с использованием (49)÷(51), должна быть определена величина Епор, которую выбираем равной Епор=-1 В.

6.3. Выбор и расчет сопротивлений R6=R7=R8=R9 и R10=R11= R4=R5 проводится с учетом определенных ранее R=1,4 кОм и Епор=-1 В на основе (49)÷(50) с желательным выполнением условия

позволяющего обеспечить близкий к единице коэффициент передачи напряжения Uaj (или Ubj) на выход напряжения U6 (или U7).

С учетом (52) выбираем R6=R7=R8=R9=2 кOм, по формуле (48) вычисляем R10=R11=28 кОм и на основании полученного результата выбираем R12=R13=R14=R15=56 кОм, а в качестве резистора R10 (или R11) выбираем последовательное соединение двух резисторов с номиналами Р10.1(или R11.1)=13 кОм и Р10.2 (или Р11.2)=15 кОм.

Таким образом, R1=3,9 кОм, R2=1,5 кОм, R=1,4 кОм (при Rm=300 Ом), (R6=R7=R8=R9=2 кOм, R10=R11=(13+15) кOм, R12=R13=R14=R15= 56 кOм, а качество рассчитанного варианта реализации коммутатора оценивается вектором

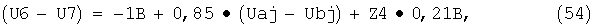

7. На основании метода наложения (см. (41)÷(48)) для данного варианта реализации коммутатора разность напряжений между неинвертирующим и инвертирующим входами компараторов 4 и 5 определяется выражениями

где -1В=Епор=(-E•R6)/(R6+R10); 0,85=R4/(2•R+R4+R6); 0,21 В={2•(1-R4•(R+R4+R6)/[(R4+R6)•(2•R+R4+R6)]}В=Ег - напряжение ширины петли гистерезиса; выходные цифровые переменные Z4 и Z5 коммутатора определены выражениями (33) и (34).

Предлагаемый коммутатор работает следующим образом.

По сигналам кода IА(0:2) мультиплексор-демультиплексор 3 для выбранного канала j (21) с помощью аттенюаторов 1 и 2 подключает напряжение Uaj= 0,277•IUaj через резистор Ra к точке U3a соединения резисторов R6 и R9 и напряжение Ubj=0,277•IUbj через резистор Rb к точке U3b соединения резисторов R7 и R8 - см. фиг.1 и 2. В этой связи с коэффициентом передачи 0,85 разности сигналов (Uaj-Ubj) и (Ubj-Uaj) участвуют согласно (54) и (55) в формировании разностей напряжений (U6-U7) и (U8-U9) между неинвертирующим и инвертирующим входами компараторов 4 и 5 соответственно.

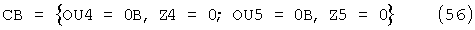

В зависимости от значений величин Uaj (35) и Ubj (36) в процессе работы коммутатора можно выделить три состояния. В течение паузы Тп или периода Т2 возврата к нулю |Uaj-Ubj|<(0÷277) В, (U6-U7)<0 В, (U8-U9)<0 В и коммутатор находится в состоянии возврата (СВ)

с заградительной фильтрацией на входах компаратора 4 или 5 синхронной помехи до |Ux|≤(47,5•0,277•0,85) В=11,18 В, где х=6÷9.

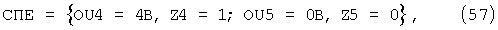

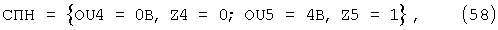

Во время периода Т1 коммутатор при {|Uaj-Ubj|+Епор}>0 В переключается из СВ или в состояние приема единицы (СПЕ)

соответствующее приему “1” кода RZ при {Uaj-Ubj+Епор}>0 В, либо в состояние приема нуля (СПН)

соответствующее приему “0” кода RZ при {Ubj-Uaj+Епор>0 В, а при переходе от периода Т1 к периоду Т2 или Тп коммутатор из СПЕ или СПН возвращается в СВ.

При переходе из СВ в состояние СПЕ (или СПН) или наоборот из состояния СПЕ (или СПН) в СВ по изменению (U6-U7) (или (U8-U9)) начавшееся изменение OU4 (или U05) по петле положительной обратной связи ускоряет процесс перехода, и если β•Кu=(0,21/4)•Кu - усиление по петле обратной связи больше единицы (для К554СА3 коэффициент усиления по напряжению равен Кu=150000), то скорость каждого переключения ограничивается только свойствами внутренних цепей компаратора 4 (или 5) - см., например, [3, с.141].

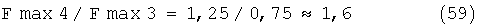

Сравнивая качество (53) предлагаемого коммутатора с качеством (29) прототипа [8] получаем, что предлагаемый коммутатор по сравнению с прототипом [8] имеет более высокое быстродействие

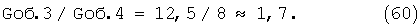

при меньшем объеме оборудования

Таким образом, по сравнению с прототипом [8] предлагаемый коммутатор благодаря его существенным признакам обладает и более высоким быстродействием (см. оценку (59)) и меньшим объемом оборудования (см. оценку (60)) при отсутствии регулировок.

Источники информации

1. Основы организации систем цифровых связей в сложных иформационно-измерительных комплексах/ В.А.Ацюковский, В.Г.Бобров, А.Л.Невдяева и др. - М: Энергоатомиздат, 2001. - 96 с. ил. (Б-ка энергетика).

2. А.с. СССР №1786491 A1, G 06 F 13/00. Устройство для ввода информации. Д.Ю.Гусев, Ю.В.Крюков. Опубл. 17.01.1993 г. БИ №1.

3. Гальперин М.В. Электронная техника: Учебник. - М: ФОРУМ: ИНФРА-М, 2003. - 304 с.: ил. - (Серия “Профессиональное образование”).

4. Хвощ С. Т и др. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т.Хвощ, В.В.Дорошенко, В.В.Горовой. Под общ. Ред. С.Т.Хвоща. - Л: Машиностроение, Ленингр. отд-ние, 1989. - 271 с., ил.

5. А.с. СССР №661798, Н 03 К 17/80. Многоканальный коммутатор аналоговых сигналов/ А.А.Редкокаша. Опубл. 1979. БИ №17.

6. А.с. СССР №729844, Н 03 17/02. Коммутатор/ Ю.Н.Цыбин. Опубл. 1980. БИ №15.

7. Патент RU №2159006, Н 03 К 17/74. Коммутатор цифровых сигналов/ Киселев Е.Ф., Палочкин Ю.П. Опубл. 10.11. 2000, БИ №31.

8. Патент RU №2190927, 7 Н 03 К 17/16, G 06 F 13/00, 3/00. Коммутатор цифровых дифференциальных сигналов. Киселев Е.Ф., Зуев А.И. Опубл. 10.10.2002. БИ №28. Прототип.

9. Цифровые и аналоговые интегральные микросхемы: Справочник/ С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др.; Под ред. С.В.Якубовского. - М.: Радио и связь, 1989. - 496 с. ил.

10. Гутников B.C. Интегральная электроника в измерительных устройствах. - 2-е изд., перераб. и доп. - Л: Энергоатомиздат. Ленингр. отд-ние, 1988. - 304 с.: ил.

11. Л.А.Бессонов. Теоретические основы электротехники (электрические цепи). - 9-е изд., перераб. и доп. - М: Высшая школа, 1996. - 638 с., ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| КОММУТАТОР ЦИФРОВЫХ СИГНАЛОВ | 1999 |

|

RU2159006C1 |

| Многоканальный сигнализатор температуры | 1989 |

|

SU1753307A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЛЯ СЪЕМА, РЕГИСТРАЦИИ И АНАЛИЗА ЭЛЕКТРОФИЗИОЛОГИЧЕСКИХ СИГНАЛОВ И БЛОК ЗАЩИТЫ ОТ АВАРИЙНЫХ ТОКОВ ПАЦИЕНТА | 1995 |

|

RU2102004C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ РЕЗИСТИВНЫХ ДАТЧИКОВ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1994 |

|

RU2097777C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения функции адресной коммутации на два цифровых информационных выхода с уровнем транзисторно-транзисторной логики множества входных цифровых дифференциальных (разностных) сигналов любого двухполярного двухуровневого или трехуровневого самосинхронизирующегося последовательного двоичного кода и может быть использовано, например, при построении многоканальных устройств для ввода информации в системах проводной цифровой связи. Технический результат заключается в повышении быстродействия и упрощении коммутатора. Коммутатор содержит первый и второй многоканальные аттенюаторы, двухпортовый мультиплексор-демультиплексор, входы первых и вторых компонент цифровых дифференциальных сигналов, два компаратора и два цифровых информационных выхода, а также десять резисторов, причем сопротивления резисторов с первого по четвертый равны между собой, сопротивления пятого, седьмого и девятого резисторов равны сопротивлениям шестого, восьмого и десятого резисторов соответственно, и сопротивление пятого или шестого резистора равно сопротивлению параллельного соединения резисторов седьмого и девятого или восьмого и десятого соответственно. 2 ил.

Коммутатор цифровых дифференциальных сигналов, содержащий два многоканальных аттенюатора, каждый канал каждого из которых образован двумя резисторами, через первый из которых вход канала связан с выходом канала, который через второй резистор связан с общей шиной (корпусом) коммутатора, двухпортовый мультиплексор-демультиплексор, входы первых и вторых компонент цифровых дифференциальных сигналов, связанные соответственно через каналы первого и второго аттенюаторов с информационными входами каналов первого и второго портов мультиплексора-демультиплексора, кодовый вход адреса коммутируемого канала, соединенный с адресным входом мультиплексора-демультиплексора, два компаратора и первый и второй цифровые информационные выходы, являющиеся выходами первого и второго компараторов соответственно, отличающийся тем, что он дополнительно содержит десять резисторов, а неинвертирующий и инвертирующий входы первого компаратора связаны через первый и второй резисторы соответственно с выходами первого и второго портов мультиплексора-демультиплексора, выходы второго и первого портов которого связаны через третий и четвертый резисторы с неинвертирующим и инвертирующим входами второго компаратора соответственно, шина источника положительного напряжения коммутатора связана через пятый и шестой резисторы соответственно с инвертирующими входами первого и второго компараторов, общая шина коммутатора связана через седьмой и восьмой резисторы соответственно с неинвертирующими входами первого и второго компараторов, выходы которых связаны с их неинвертирующими входами соответственно через девятый и десятый резисторы, причем сопротивления резисторов с первого по четвертый равны между собой, сопротивления пятого, седьмого и девятого резисторов равны сопротивлениям шестого, восьмого и десятого резисторов соответственно и сопротивление пятого или шестого резистора равно сопротивлению параллельного соединения резисторов седьмого и девятого или восьмого и десятого соответственно.

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| КОММУТАТОР ЦИФРОВЫХ СИГНАЛОВ | 1999 |

|

RU2159006C1 |

| Многоканальный коммутатор | 1986 |

|

SU1401590A1 |

| US 5900767 А, 04.05.1999 | |||

| ЕР 0438228 А1, 24.07.1991. | |||

Авторы

Даты

2005-07-20—Публикация

2003-11-24—Подача