Изобретение относится к области автоматики, измерительной и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления.

Известен широкополосный микрополосковый переключатель СВЧ (пат. 2339126 С1, Российская Федерация, МПК Н01Р 1/15 (2006.01), заявл. 15.02.2007, опубл. 20.11.2008), содержащий pin-диоды, участки токонесущего проводника микрополосковой линии. Недостаток - низкое быстродействие.

Известен СВЧ переключатель на pin-диодах с фильтрующими свойствами (пат. 2504869 С2, Российская Федерация, МПК Н01Р 1/00 (2006.01), заявл. 06.04.2012, опубл. 20.01.2014), содержащий емкости, индуктивности, резисторы, pin-диоды, сигнальные выводы устройства, источники управляющего напряжения. Недостаток - низкое быстродействие.

Наиболее близким к заявляемому является изобретение (фиг. 2, пат. 2594378 С1, Российская Федерация, МПК G01R 29/02 (2006.01), заявл. 05.06.2015, опубл. 20.08.2016), содержащее генератор непрерывного СВЧ-сигнала, делитель, линии передачи, эталонный фазовращатель, контролируемый фазовращатель, генератор импульсов переключения фазы, сумматор, аттенюатор, детектор, осциллограф. Недостаток - низкие функциональные возможности, ограниченные применением устройства только для измерения времени переключения фазы.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в расширении функциональных возможностей.

Технический результат выражается в увеличении возможностей применения устройства от измерительной до области автоматики и вычислительной техники.

Технический результат достигается тем, что в фазированный ключ по модулю m, содержащий первый сумматор, аттенюатор, детектор, введены первый и второй информационные входы устройства, синхронизирующий вход устройства, блок разности фаз, m-1 блоков умножения на константу, m-1 блоков выборки фазы, второй сумматор, измерительный и информационный выходы устройства, при этом первый и второй информационные входы устройства объединены с соответствующими входами блока разности фаз, выход которого соединен с первым входом блоков умножения на константу, выход которых соединен с первым входом соответствующих блоков выборки фазы, выход которых соединен с соответствующим входом первого сумматора, выход которого соединен с входом аттенюатора, выход которого соединен с первым входом второго сумматора и входом детектора, выход которого объединен с измерительным выходом устройства, при этом синхронизирующий вход устройства объединен с третьим входом блока разности фаз, вторым входом блоков умножения на константу, блоков выборки фазы и второго сумматора, выход которого объединен с информационным выходом устройства.

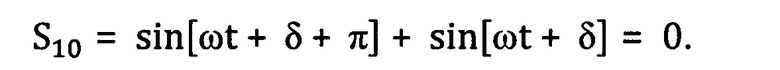

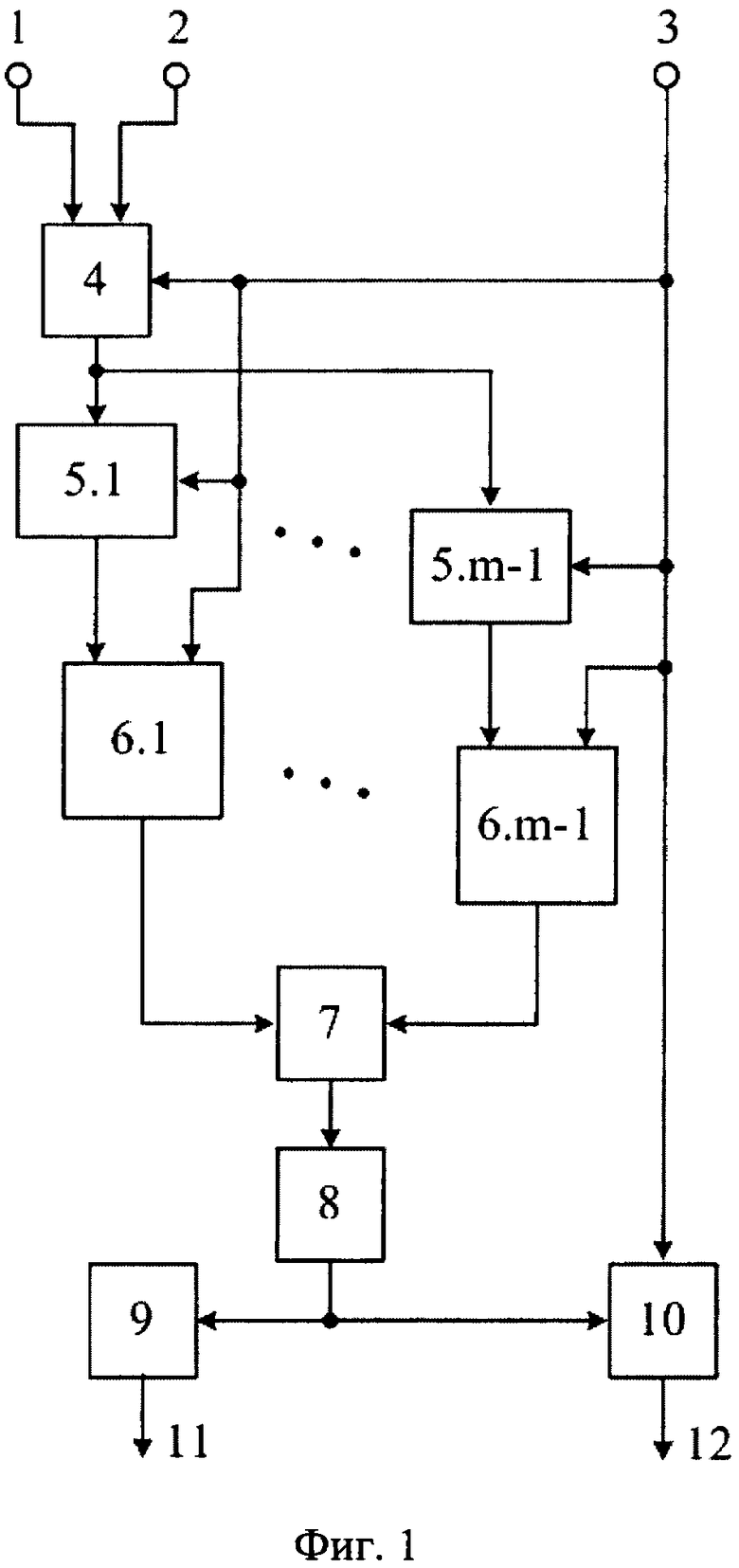

На фиг. 1 представлена структурная схема фазированного ключа по модулю m.

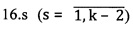

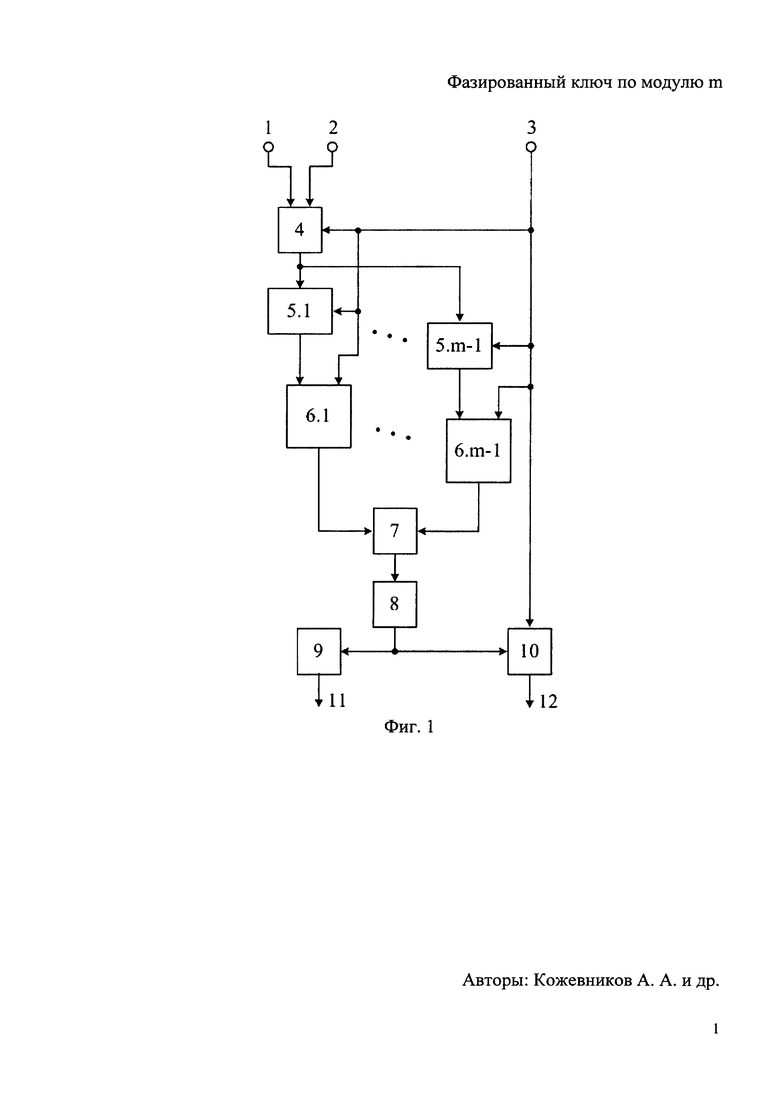

На фиг. 2 приведена схема блока умножения на константу для k≥2.

На фиг. 3 приведена схема блока умножения на константу для k=1.

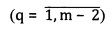

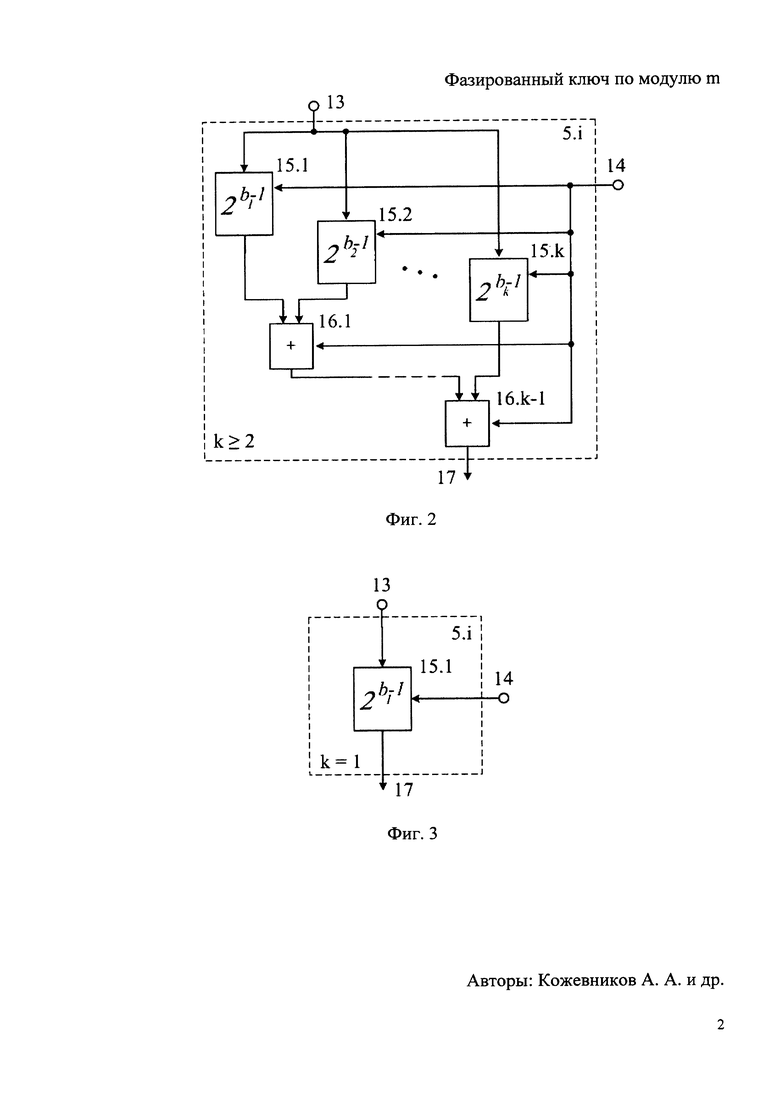

На фиг. 4 приведена схема блока выборки фазы.

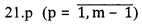

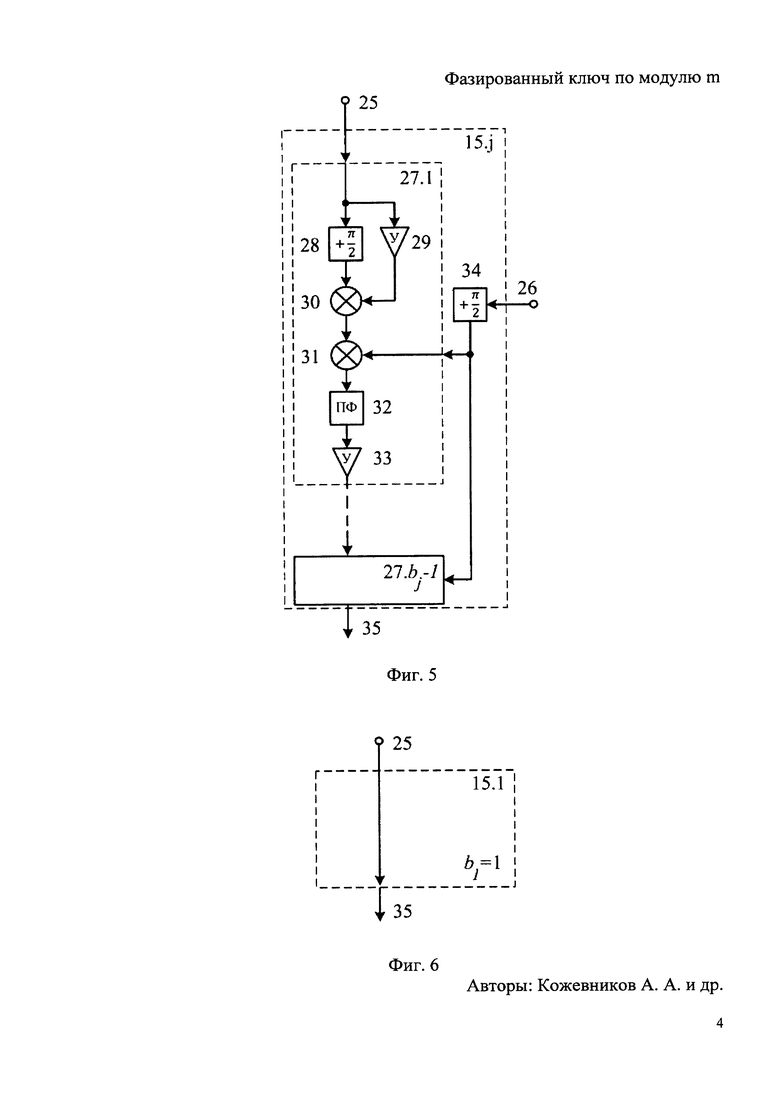

На фиг. 5 приведена схема блока умножения на два в степени для bj≥2.

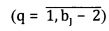

На фиг. 6 приведена схема блока умножения на два в степени для j=1 и b1=1.

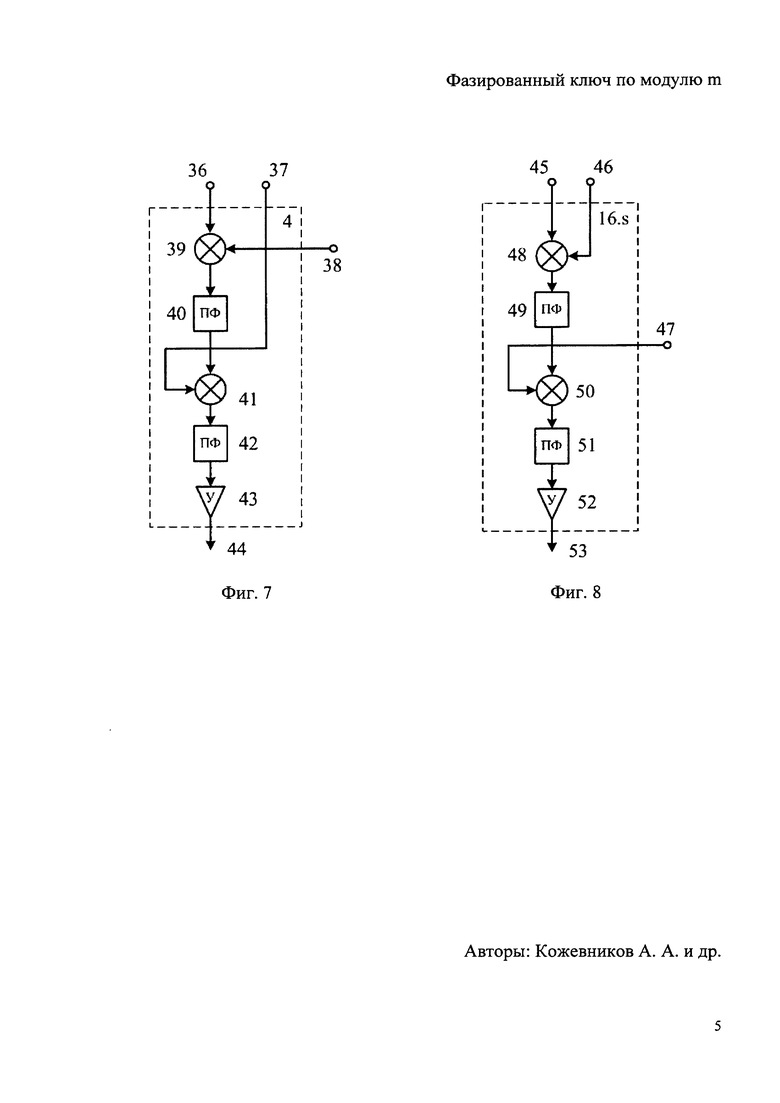

На фиг. 7 приведена схема блока разности фаз.

На фиг. 8 приведена схема блока сложения фаз.

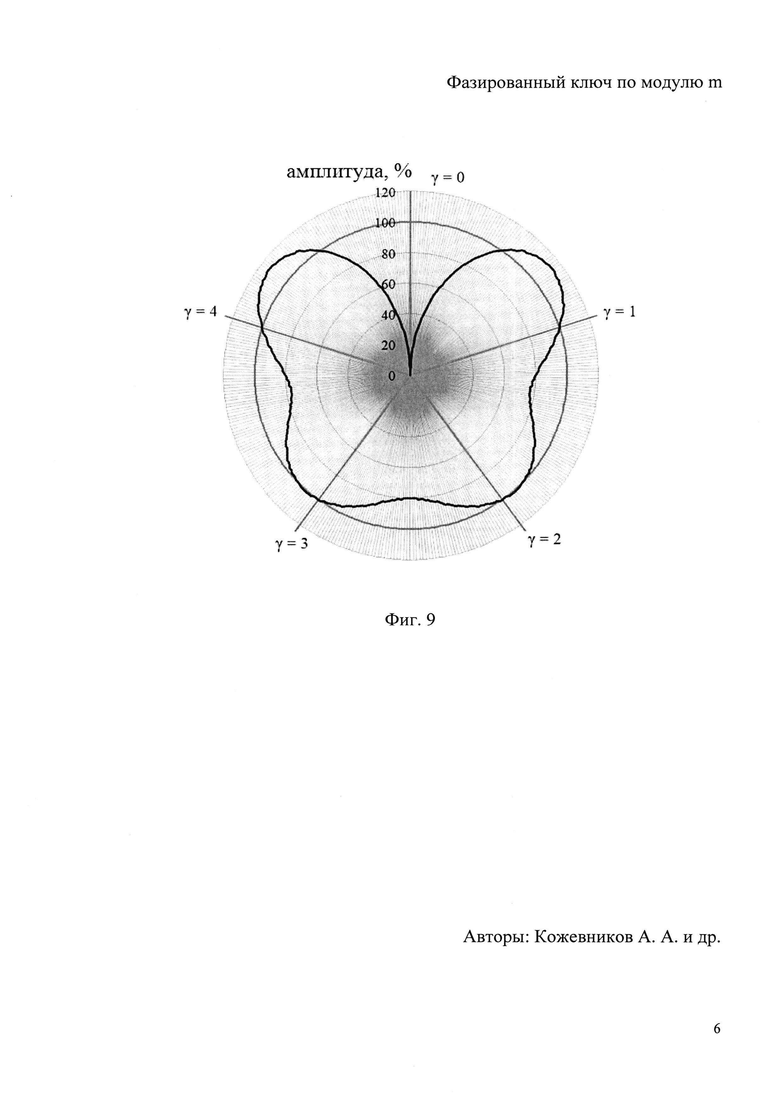

На фиг. 9 представлена зависимость амплитуды сигнала на выходе аттенюатора от разности фаз информационных гармоник для m=5.

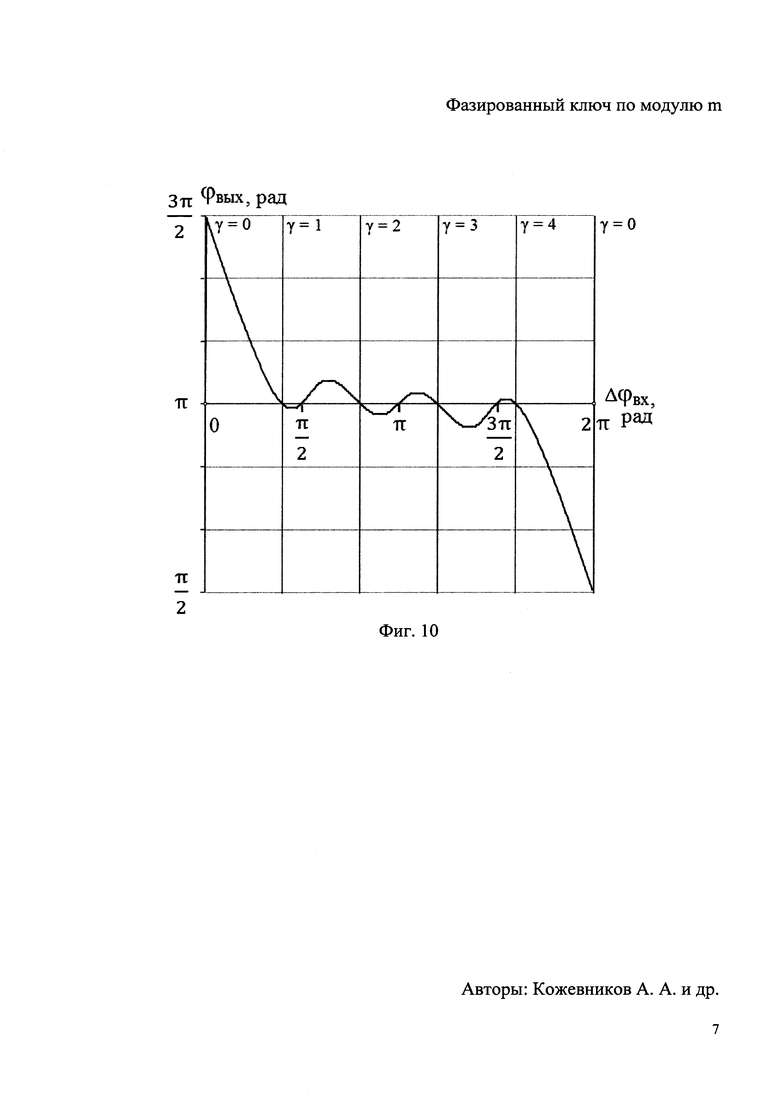

На фиг. 10 представлена зависимость фазы сигнала на выходе аттенюатора относительно синхронизирующего от разности фаз информационных гармоник для m=5.

Сущность изобретения заключается в синтезе синусоидального сигнала, находящегося в противофазе к синхронизирующему или равного по амплитуде нулю в точках, жестко заданных дискретными состояниями разности фаз управляющих (информационных) гармоник. Результаты работы такого устройства удобно рассмотреть на примере значений параметров выходного сигнала на аттенюаторе 8 (фиг. 1) для m=5 при условии, что все входные гармоники имеют одинаковую амплитуду. Представленные на фиг. 9 и фиг. 10 примеры показывают, что в точках при разности фаз, равных 2π⋅γ/m, γ∈[1,m-1] - целое положительное, наблюдается единичный уровень амплитуды сигнала и значение фазы, равное π. При нулевой разности фаз по входу, на выходе аттенюатора - ноль. В промежуточных состояниях в основном наблюдается почти единичная амплитуда и почти противофаза.

На детекторе 9 (фиг. 1) формируется уровень напряжения, равный или пропорциональный амплитуде синтезируемого сигнала, поэтому подключив к выходу 11 осциллограф, к входу 1 - эталонный перестраиваемый фазовращатель, а к входу 2 - исследуемый фазовращатель, можно осуществить измерение времени переключения фазы например так. С помощью эталонного фазовращателя необходимо настроиться на нулевую разность фаз и после переключении исследуемого фазовращателя зафиксировать на осциллографе установившийся постоянный уровень. Время нарастания фронта сигнала на осциллографе позволит определить искомый параметр.

Реализуемое устройство по сравнению с прототипом расширяет возможность своего применения на область автоматики и вычислительной техники, функционирующей в системе остаточных классов (СОК) в дискретно-фазированной форме представления чисел. При установлении дискретных значений разности фаз по информационным (управляющим) входам 2π⋅γ/m, γ∈[1,m-1] - разность остатков (γ=γ1-γ2≠0) по основанию m СОК, сигнал с аттенюатора в силу своей противофазы нейтрализует на сумматоре 10 (фиг. 1) синхронизирующую гармонику, устанавливая на выходе 12 ноль. Если же сигналы на входах 1 и 2 равны по фазе (γ=0), то синхронизирующая гармоника, сложившись с нулем, проходит дальше. Так выполняется ключевая функция устройства. Реализуемое устройство при рабочей частоте 100 ГГц производит включение\выключение на один-два порядка быстрее по сравнению с рассмотренными аналогами, т.к. даже самые быстродействующие полупроводниковые ключи, работающие с сигналами в СВЧ диапазоне, осуществляют данную операцию в течение единиц наносекунд (стр. 12, Щаврук Н.В. Проектирование и изготовление микроэлектромеханических переключателей на подложках GaAs для СВЧ диапазона: дис.… канд. техн. наук: 05.27.01 / Москва. 2015. 130 с.).

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1, 2, 4 и 5 должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Дополнительным эффектом является возможность построения устройств для сравнения модулярных чисел в дискретно-фазированной форме. Также дополнительным эффектом является определение набега фазы (задержки) в исследуемой схеме при условии применения на одном из управляющих входов устройства перестраиваемого эталонного фазовращателя и того факта, что, например, для m=5 в пределах ±15° от нуля практически линейна зависимость амплитуды сигнала на выходе аттенюатора от разности фаз управляющих гармоник.

Показанный на фиг. 1 фазированный ключ по модулю m содержит первый 1 и второй 2 информационные входы устройства, синхронизирующий вход устройства 3, блок разности фаз 4, блоки умножения на константу 5.1-5.(m-1), блоки выборки фазы 6.1-6.(m-1), первый сумматор 7, аттенюатор 8, детектор 9, второй сумматор 10, измерительный 11 и информационный 12 выходы устройства.

Первый 1 и второй 2 информационные входы устройства объединены с соответствующими входами блока разности фаз 4, выход которого соединен с первым входом блоков умножения на константу 5.1-5.(m-1), выход которых соединен с первым входом соответствующих блоков выборки фазы 6.1-6.(m-1), выход которых соединен с соответствующим входом первого сумматора 7, выход которого соединен с входом аттенюатора 8, выход которого соединен с первым входом второго сумматора 10 и входом детектора 9, выход которого объединен с измерительным выходом устройства 11, при этом синхронизирующий вход устройства 3 объединен с третьим входом блока разности фаз 4, вторым входом блоков умножения на константу 5.1-5.(m-1), блоков выборки фазы 6.1-6.(m-1) и второго сумматора 10, выход которого объединен с информационным выходом устройства 12.

Показанная на фиг. 2 схема блока умножения на константу для k≥2 содержит первый 13 и второй 14 входы, блоки умножения фазы на два в степени 15.1-15.k, блоки сложения фаз 16.1-16.(k-1), выход 17.

Первый вход 13 объединен с первым входом блоков умножения фазы на два в степени 15.1-15.k, второй вход 14 объединен с вторым входом блоков умножения фазы на два в степени 15.1-15.k и третьим входом блоков сложения фаз 16.1-16.(k-1), выход блока умножения фазы на два в степени  соединен с вторым входом блока сложения фаз 16.j, выход блока умножения фазы на два в степени 15.1 соединен с первым входом блока сложения фаз 16.1, выход блока сложения фаз

соединен с вторым входом блока сложения фаз 16.j, выход блока умножения фазы на два в степени 15.1 соединен с первым входом блока сложения фаз 16.1, выход блока сложения фаз  соединен с первым входом блока сложения фаз 16.(s+1), выход блока сложения фаз 16.(k-1) объединен с выходом 17.

соединен с первым входом блока сложения фаз 16.(s+1), выход блока сложения фаз 16.(k-1) объединен с выходом 17.

Показанная на фиг. 3 схема блока умножения на константу для k=1 содержит первый 13 и второй 14 входы, блок умножения фазы на два в степени 15.1, выход 17.

Первый вход 13 объединен с первым входом блока умножения фазы на два в степени 15.1, при этом второй вход 14 объединен с вторым входом блока умножения фазы на два в степени 15.1, выход которого объединен с выходом 17.

Показанная на фиг. 4 схема блока выборки фазы содержит первый 18 и второй 19 входы, фазовращатель на фиксированное значение π 20, фазовращатели на фиксированное значение 2π/m 21.1-21.(m-1) и 22.1-22.(m-1), сумматор 23 и выход 24.

Первый вход 18 объединен с входом фазовращателя на фиксированное значение π 20, выход которого соединен входом фазовращателя на фиксированное значение 2π/m 21.1, второй вход 19 объединен с входом фазовращателя на фиксированное значение 2π/m 22.1, выход фазовращателя на фиксированное значение 2π/m  соединен с первой группой соответствующих входов сумматора 23, выход фазовращателя на фиксированное значение 2π/m 22.р соединен с второй группой соответствующих входов сумматора 23, выход которого объединен с выходом 24, выход фазовращателя на фиксированное значение 2π/m 21.q

соединен с первой группой соответствующих входов сумматора 23, выход фазовращателя на фиксированное значение 2π/m 22.р соединен с второй группой соответствующих входов сумматора 23, выход которого объединен с выходом 24, выход фазовращателя на фиксированное значение 2π/m 21.q  также соединен с входом фазовращателя на фиксированное значение 2π/m 21.(q+1), выход фазовращателя на фиксированное значение 2π/m 22.q также соединен с входом фазовращателя на фиксированное значение 2π/m 22.(q+1).

также соединен с входом фазовращателя на фиксированное значение 2π/m 21.(q+1), выход фазовращателя на фиксированное значение 2π/m 22.q также соединен с входом фазовращателя на фиксированное значение 2π/m 22.(q+1).

Показанная на фиг. 5 схема блока умножения на два в степени для bj≥2 содержит первый 25 и второй 26 входы, блоки умножения на два 27.1-27.(bj-1), фазовращатель на фиксированное значение π/2 34, выход 35.

Первый вход 25 объединен с первым входом блока умножения на два 27.1, второй вход 26 объединен с входом фазовращателя на фиксированное значение π/2 34, выход которого соединен с вторым входом блоков умножения на два 27.1-27.(bj-1), при этом выход блока умножения на два 27.q  соединен с первым входом блока умножения на два 27.(q+1), выход блока умножения на 27.(bj-1) объединен с выходом 35.

соединен с первым входом блока умножения на два 27.(q+1), выход блока умножения на 27.(bj-1) объединен с выходом 35.

Блок умножения на два содержит фазовращатель на фиксированное значение π/2 28, усилитель 29, смеситель 30, смеситель 31, полосовой фильтр 32, усилитель 33.

Второй вход блока умножения на два объединен с вторым входом смесителя 31, первый вход блока умножения на два объединен с входом фазовращателя на фиксированное значение π/2 28 и усилителя 29, выход которого соединен с вторым входом смесителя 30, при этом выход фазовращателя на фиксированное значение π/2 28 соединен с первым входом смесителя 30, выход которого соединен с первым входом смесителя 31, выход которого соединен с входом полосового фильтра 32, выход которого соединен с входом усилителя 33, выход которого является выходом блока умножения на два.

Показанная на фиг. 6 схема блока умножения на два в степени для j=1 и b1=1 содержит вход 25 и выход 35, при этом вход 25 объединен с выходом 35.

Показанная на фиг. 7 схема блока разности фаз содержит первый 36, второй 37 и третий 38 входы, смеситель 39, полосовой фильтр 40, смеситель 41, полосовой фильтр 42, усилитель 43, выход 44.

Второй вход 37 объединен с первым входом смесителя 41, первый вход 36 объединен с первым входом смесителя 39, третий вход 38 объединен с вторым входом смесителя 39, выход которого соединен с входом полосового фильтра 40, выход которого соединен с вторым входом смесителя 41, выход которого соединен с входом полосового фильтра 42, выход которого соединен с входом усилителя 43, выход которого объединен с выходом 44.

Показанная на фиг. 8 схема блока сложения фаз содержит первый 45, второй 46 и третий 47 входы, смеситель 48, полосовой фильтр 49, смеситель 50, полосовой фильтр 51, усилитель 52 и выход 53.

Третий вход 47 объединен с первым входом смесителя 50, первый вход 45 объединен с первым входом смесителя 48, второй вход 46 объединен с вторым входом смесителя 48, выход которого соединен с входом полосового фильтра 49, выход которого соединен с вторым входом смесителя 50, выход которого соединен с входом полосового фильтра 51, выход которого соединен с входом усилителя 52, выход которого объединен с выходом 53.

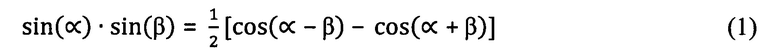

Рассмотрим работу устройства, с точки зрения выполнения функции ключа. На синхронизирующий вход 3 поступает гармонический сигнал Sc=sin(ωt+δ). На информационные входы 1 и 2 поступают соответственно дискретно-фазированные гармоники S1=sin(ωt+2π⋅γ1/m) и S2=sin(ωt+2π⋅γ2/m), где γ1,2 ∈ [0, m-1], а m - модуль применяемой системы остаточных классов. На блоке разности фаз 4 осуществляется процесс вычитание и синхронизации следующим образом (фиг. 7). На смесителе 39 производится перемножение сигналов S1 и Sc. Из известного тригонометрического выражения

следует, что после полосовой фильтрации высокочастотной составляющей на блоке 40 формируется промежуточный результат:

Гармонический сигнал S2, перемножается смесителем 41 с промежуточной гармоникой. Реализация тригонометрического выражения

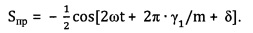

после полосовой фильтрации более низкочастотной составляющей на блоке 42 и усиления в блоке 43 дает результат в виде гармоники с единичной амплитудой и фазой смещенной относительно синхронизирующего сигнала на 2π⋅(γ1-γ2)/m:

Полученная гармоника поступает на блоки 5.i умножения на константу, где  Значение константы равно индексу i. Для осуществления операции умножения число i представляется в виде блоков, реализующих сумму значимых степеней двойки полинома:

Значение константы равно индексу i. Для осуществления операции умножения число i представляется в виде блоков, реализующих сумму значимых степеней двойки полинома:

общий случай которого приведен на фиг. 2. Здесь буквой k обозначено общее количество единиц в разрядах β, a bj - порядковый номер разряда, равного 1, в двоичном слове, при этом bj≥1, a  В частном случае, когда к=1, отпадает необходимость в блоках сложения фаз (фиг. 3).

В частном случае, когда к=1, отпадает необходимость в блоках сложения фаз (фиг. 3).

Рассмотрим аппаратную реализацию нескольких первых констант. Блок 5.1 содержит один блок 15.1 (фиг. 3), в котором отсутствуют блоки умножения на два (фиг. 6). Блок 5.2 содержит один блок 15.1 (фиг. 3), который в свою очередь содержит один блок умножения на два 27.1 (фиг. 5). Блок 5.3 содержит блоки умножения на два в степени 15.1 и 15.2, а также один блок сложения фаз 16.1 (фиг. 2), при этом в блоке 15.1 отсутствуют блоки умножения на два (фиг. 6), а блок 15.2 содержит один блок умножения на два 27.1 (фиг. 5). Блок 5.4 содержит один блок 15.1 (фиг. 3), который в свою очередь содержит блоки умножения на два 27.1 и 27.2 (фиг. 5). Таким же образом, согласно реализации полинома (3), формируются по необходимости все следующие блоки умножения на константу.

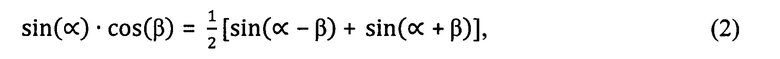

Рассмотрим работу блоков умножения на константу на примере 5.3 (фиг. 2). Синхронизирующий сигнал (Sc) через вход 14 проходит на второй вход блоков 15.1, 15.2, и третий вход блока сложения фаз 16.1. Полученный ранее сигнал блока разности фаз 4 (S4) через вход 13 поступает на блоки 15.1 и 15.2, при этом согласно фиг. 6 он проходит без изменений блок 15.1 (т.е. S15.1 = S4), а в 15.2 подвергается однократному умножению на два. Попадая в блок умножения на два 27.1 (фиг. 5), фазированная гармоника S4 увеличивает фазу на π/2 в блоке 28, а в параллельной линии - амплитуду в два раза на усилителе 29, после чего оба сигнала поступают на входы смесителя 30, где реализуется известное тригонометрическое выражение:

Полученная промежуточная гармоника удвоенной частоты

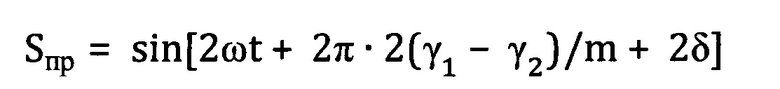

перемножается на смесителе 31 с синхронизирующей гармоникой, фаза которой увеличена на π/2 блоком 34 (т.е. S34 = cos(ωt+δ)). При этом, согласно тригонометрическому выражению (2) после полосовой фильтрации более низкочастотной составляющей на блоке 32 и усиления в блоке 33 получается результат в виде гармоники с единичной амплитудой и фазой смещенной относительно синхронизирующего сигнала на 2π⋅2(γ1-γ2)/m:

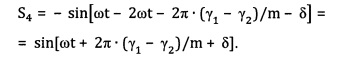

Далее происходит сложение сигналов S15.1 и S15.2 на блоке 16.1. При этом данные гармоники сначала перемножаются на смесителе 48 (фиг. 8). Из известного тригонометрического выражения (1) следует, что после полосовой фильтрации высокочастотной составляющей на блоке 49 формируется промежуточный результат:

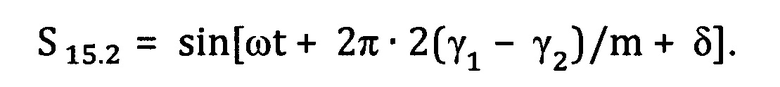

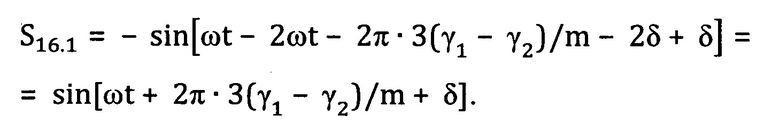

Синхронизирующий сигнал (Sc) с входа 47 перемножается смесителем 50 с промежуточной гармоникой. Реализация тригонометрического выражения (2) после полосовой фильтрации более низкочастотной составляющей на блоке 51 и усиления в блоке 52 дает результат в виде гармоники с единичной амплитудой и фазой смещенной относительно синхронизирующего сигнала на 2π⋅3(γ1-γ2)/m:

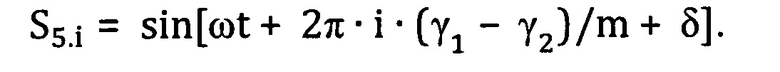

Этот результат поступает на выход 17 (фиг. 2), т.е. S5.3=S16.1. По аналогии, результатом на выходе блоков 5.i будет гармоника:

Полученные сигналы S5.i поступают па первый вход блоков выборки фазы 6.i (фиг. 4), где  ко вторым входам которых подведен синхронизирующий сигнал Sc=sin(ωt+δ].

ко вторым входам которых подведен синхронизирующий сигнал Sc=sin(ωt+δ].

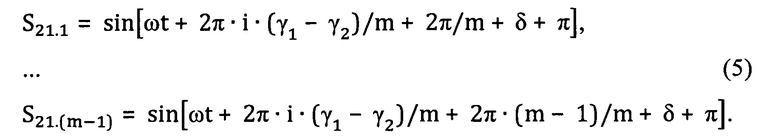

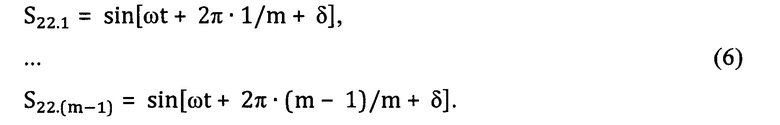

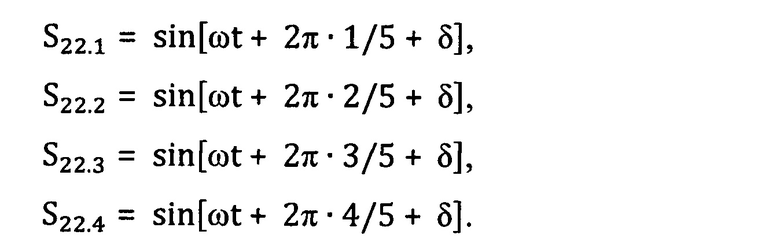

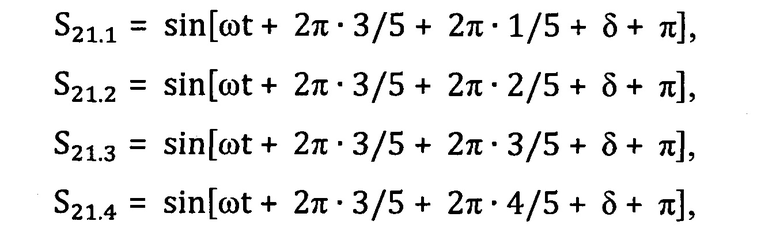

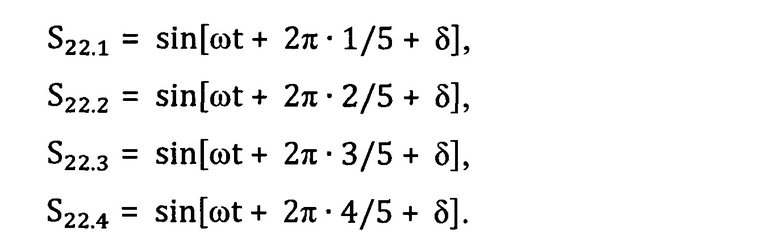

Фазовращатели на фиксированное значение π 20 и 2π/m 21.1-21.(m-1) преобразуют в соответствии со своей функцией сигналы S5.i:

Фазовращатели на фиксированное значение 2π/m 22.1-22.(m-1) преобразуют в соответствии со своей функцией сигнал Sc:

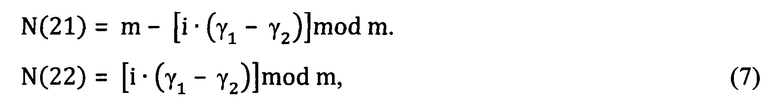

Полученные гармоники складываются на сумматоре мощности 23. Если фазы приходящих на входы 18 и 19 (фиг. 4) гармонических сигналов равны, то на выходе 24 наблюдается ноль. В противном случае большая часть гармоник, находясь в противофазе, дает при сложении ноль, оставляя сумму двух сигналов, по одному из каждой ветки. При этом порядковые номера фазовращателей на фиксированное значение 2π/m, дающих ненулевой вклад в итоговый сигнал можно рассчитать по формулам:

Исходя из выражений (5) и (6) получается, что на выходе 24 формируется сигнал:

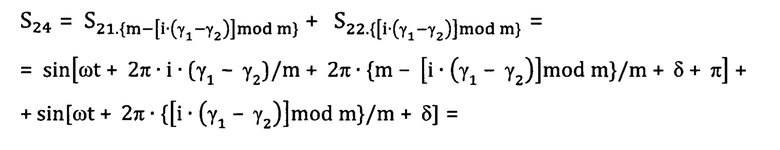

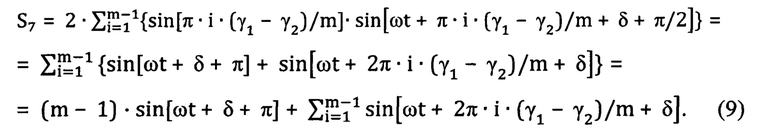

Таким образом, после прохождения блоков выборки фазы 6.1-6.(m-1) происходит сложение гармоник, описанных выражением (8), на сумматоре 7:

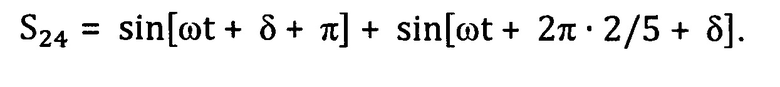

Далее аттенюатор 8 уменьшает полученную сумму в m раз, и полученный сигнал детектируется блоком 9 для проведения измерений и складывается с синхронизирующей гармоникой на блоке 10, реализуя ключевую функцию.

Пример

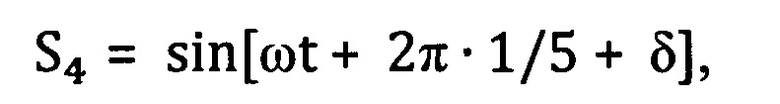

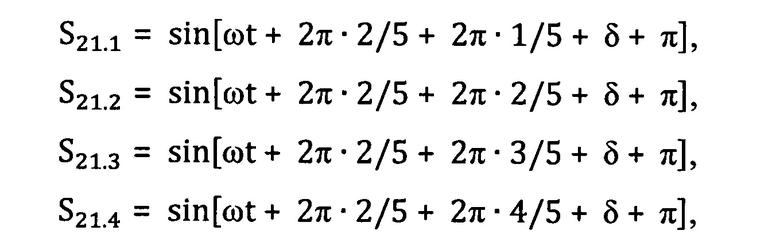

Рассмотрим фазированный ключ по модулю m=5. Такое устройство содержит по четыре блока умножения на константу 5.1-5.4 и выборки фазы 6.1-6.4. Если γ1-γ2=0, то согласно уравнения (9), S7=0, поэтому рассмотрим ситуацию, когда нет такого равенства, и для простоты пусть γ1-γ2=1. Этому соответствует гармоника на выходе блока разности фаз 4:

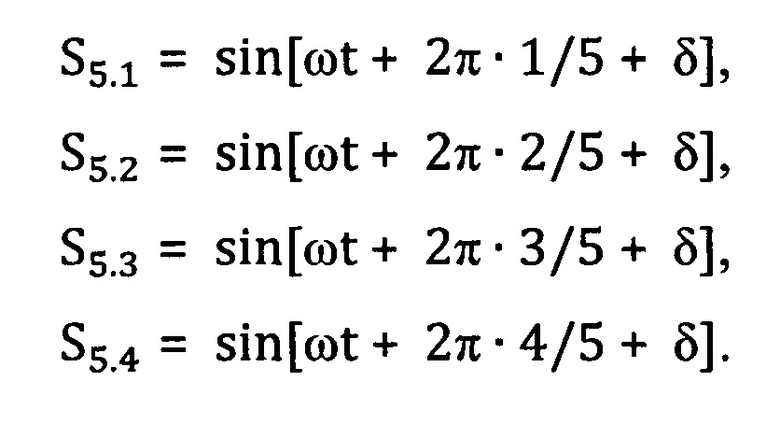

которая поступает на блоки умножения на константы, на выходе которых соответственно формируются сигналы:

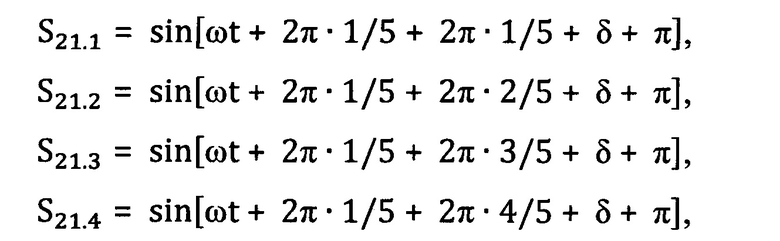

Далее на блоках 6.1-6.4 происходит выборка фаз и формирование итоговых сигналов, согласно выражений (5)-(8) следующим образом.

Блок 6.1

и

После сложения и взаимной аннигиляции гармоник в противофазе, формируется сумма:

Блок 6.2

и

После сложения и взаимной аннигиляции гармоник в противофазе, формируется сумма:

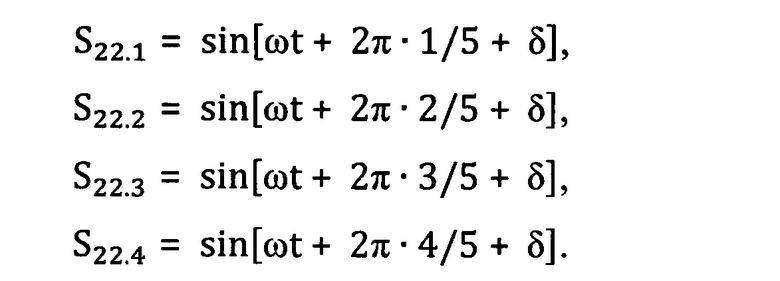

Блок 6.3

и

После сложения и взаимной аннигиляции гармоник в противофазе, формируется сумма:

Блок 6.4

и

После сложения и взаимной аннигиляции гармоник в противофазе, формируется сумма:

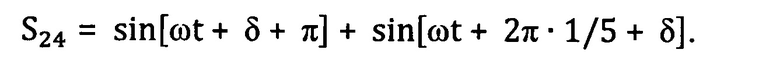

Полученные сигналы суммируются на блоке 7:

Далее аттенюатор 8 уменьшает полученную сумму в m=5 раз, и полученный сигнал детектируется блоком 9 для проведения измерений. На блоке 10 уменьшенная сумма складывается с синхронизирующей гармоникой:

Таким образом, при γ1=γ2, синхронизирующая (управляемая) гармоника проходит через фазированный ключ, а если γ1≠γ2, - не проходит, что реализует ключевую функцию.

Полученное устройство отражает принципы построения устройств вычислительной техники на основе системы остаточных классов, работающих с дискретно-фазированной формой представления чисел. С точки зрения практического применения, появляется возможность реализовать аналоговые арифметические устройства на основе табличных вычислителей в СВЧ диапазоне, превосходящих по быстродействию современный уровень ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| НЕЛИНЕЙНЫЙ РАДАР ДЛЯ ДИСТАНЦИОННОГО МОНИТОРИНГА ПРОДУКТОПРОВОДОВ | 2007 |

|

RU2343499C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ШИРОКОПОЛОСНЫМ НЕПРЕРЫВНЫМ ЛИНЕЙНО ЧАСТОТНО-МОДУЛИРОВАННЫМ ИЗЛУЧЕНИЕМ | 2010 |

|

RU2460087C2 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ | 2007 |

|

RU2386159C2 |

| Устройство для измерения средней скорости изменения частоты и линейности модуляционных характеристик частотно-модулированных генераторов | 1991 |

|

SU1781632A1 |

Изобретение относится к области автоматики, измерительной и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления. Целью изобретения является расширение функциональных возможностей устройства. Сущность изобретения заключается в синтезе синусоидального сигнала, находящегося в противофазе к синхронизирующему или равного по амплитуде нулю в точках, жестко заданных дискретными состояниями разности фаз управляющих (информационных) гармоник. Дополнительным эффектом является возможность построения устройств для сравнения модулярных чисел в дискретно-фазированной форме. Фазированный ключ по модулю m содержит первый сумматор, аттенюатор, детектор, первый и второй информационные входы устройства, синхронизирующий вход устройства, блок разности фаз, m-1 блоков умножения на константу, m-1 блоков выборки фазы, второй сумматор, измерительный и информационный выходы. 10 ил.

Фазированный ключ по модулю m, содержащий первый сумматор, аттенюатор, детектор, отличающийся тем, что введены первый и второй информационные входы устройства, синхронизирующий вход устройства, блок разности фаз, m-1 блоков умножения на константу, m-1 блоков выборки фазы, второй сумматор, измерительный и информационный выходы устройства, при этом первый и второй информационные входы устройства объединены с соответствующими входами блока разности фаз, выход которого соединен с первым входом блоков умножения на константу, выход которых соединен с первым входом соответствующих блоков выборки фазы, выход которых соединен с соответствующим входом первого сумматора, выход которого соединен с входом аттенюатора, выход которого соединен с первым входом второго сумматора и входом детектора, выход которого объединен с измерительным выходом устройства, при этом синхронизирующий вход устройства объединен с третьим входом блока разности фаз, вторым входом блоков умножения на константу, блоков выборки фазы и второго сумматора, выход которого объединен с информационным выходом устройства.

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕНИ ПЕРЕКЛЮЧЕНИЯ ФАЗЫ СВЕРХВЫСОКОЧАСТОТНОГО СИГНАЛА | 2015 |

|

RU2594378C1 |

| СВЧ ПЕРЕКЛЮЧАТЕЛЬ НА PIN-ДИОДАХ С ФИЛЬТРУЮЩИМИ СВОЙСТВАМИ | 2012 |

|

RU2504869C2 |

| I" БИБЛИОТКК^ | 0 |

|

SU365041A1 |

| US 20110090022 A1, 21.04.2011 | |||

| US 4219770 A1, 26.08.1980 | |||

| DE 3907781 A, 20.09.1990. | |||

Авторы

Даты

2018-07-04—Публикация

2017-05-24—Подача