Изобретение относится к области автоматики, информационно-измерительной и вычислительной техники, и может быть использовано для преобразования модулярного кода в аналоговый электрический сигнал.

Известно устройство (пат. 2253943 С1 Российская Федерация, МПК Н03М1/66 (2006.01). заявл. 22.12.2003; опубл. 10.06.2005.), содержащее информационные входы, устройства отображения, генератор гармонического колебания, фазовращатель на угол π/2, управляемые фазовращатели, аналоговый перемножитель, интегратор, выход. Недостаток - низкие функциональные возможности.

Известно устройство (пат. 2289881 С1 Российская Федерация, МПК Н03М1/66 (2006.01). заявл. 19.07.2005; опубл. 20.12.2006.), содержащее информационные входы, генератор гармонического колебания, управляемые фазовращатели, фазовращатель на угол π/2, аттенюатор, балансный фазовый детектор, выход. Недостаток - низкие функциональные возможности.

Наиболее близким к заявляемому является изобретение (пат. 2290754 Российская Федерация, МПК Н03М1/66 (2006.01). заявл. 11.07.2005; опубл. 27.12.2006), содержащее информационные входы вычетов, генератор гармонического колебания, управляемые фазовращатели, фазовращатель на угол π/2, аттенюатор, балансный фазовый детектор, выход. Недостаток - низкие функциональные возможности, определенные алгоритмом преобразования только модулярного цифрового кода.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в реализации универсального способа формирования выходного аналогового эквивалента входной цифровой величины, заданной как в модулярном, так и позиционном представлении.

Технический результат выражается в расширении функциональных возможностей.

Технический результат достигается тем, что в цифроаналоговый преобразователь, содержащий n входов вычетов устройства, где n - количество оснований системы остаточных классов, n управляемых фазовращателей, генератор гармонического колебания, первый фазовращатель на угол π/2, выход устройства, введены позиционный вход устройства, первая и вторая группы из n блоков умножения фазы, n блоков памяти, сумматор фаз, второй фазовращатель на угол π/2, первый и второй аналоговые перемножители, первый и второй фильтры низких частот, вход постоянного сигнала устройства, сумматор сигналов, при этом выход генератора гармонического колебания соединен с первыми входами управляемых фазовращателей, первыми входами блоков умножения фазы первой и второй группы, первым входом сумматора фаз, вторыми входами первого и второго аналоговых перемножителей, выходы которых соединены с входами соответствующих фильтров низких частот, выходы которых соответственно соединены с вторым и третьим входами сумматора сигналов, при этом вход постоянного сигнала устройства объединен с первым входом сумматора сигналов, выход которого объединен с выходом устройства, позиционный вход устройства объединен с третьими входами блоков умножения фазы первой группы, выходы блоков памяти соединены с третьими входами соответствующих блоков умножения фазы второй группы, при этом входы вычетов устройства объединены с вторыми входами соответствующих управляемых фазовращателей, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы первой группы, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы второй группы, при этом выход i-го  блока умножения фазы второй группы соединен с i+1-ым входом сумматора фаз, выход которого соединен с входом первого фазовращателя на угол π/2, выход которого соединен с первым входом первого аналогового перемножителя, а также через второй фазовращатель на угол π/2 соединен с первым входом второго аналогового перемножителя.

блока умножения фазы второй группы соединен с i+1-ым входом сумматора фаз, выход которого соединен с входом первого фазовращателя на угол π/2, выход которого соединен с первым входом первого аналогового перемножителя, а также через второй фазовращатель на угол π/2 соединен с первым входом второго аналогового перемножителя.

На фиг.1 представлена структурная схема цифроаналогового преобразователя.

На фиг.2 приведены две функциональные зависимости для значений угла в первой координатной четверти.

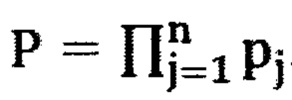

Сущность изобретения сводится к промежуточному преобразованию цифрового модулярного или позиционного кода в дискретно-фазированную форму представления чисел в системе остаточных классов с дальнейшим переходом к выходному аналоговому эквиваленту в виде тока или напряжения. Пусть задана система остаточных классов по взаимно простым основаниям p1, … pn с объемом чисел  , тогда модулярная форма числа Α=(γ1, … γn) через управляемые фазовращатели или позиционное двоичное представление А через дополнительную функцию блоков умножения фазы (патент РФ №2653310) преобразуется в дискретные фазы 2π⋅γj/pj

, тогда модулярная форма числа Α=(γ1, … γn) через управляемые фазовращатели или позиционное двоичное представление А через дополнительную функцию блоков умножения фазы (патент РФ №2653310) преобразуется в дискретные фазы 2π⋅γj/pj  гармонических сигналов одной частоты. В первом случае управляемые фазовращатели из унитарного кода вычетов формируют набег фазы. Несмотря на то, что данная операция осуществляется на линиях задержки, где результатом является величина с отрицательным знаком, в силу периодичности гармоники и табличного способа коммутации ключей в самом блоке (патент РФ №2253943, фиг.2) возможно сформировать любой положительный сдвиг фазы. На первых блоках умножения фазы осуществляется операция, где в качестве операндов выступают сигналы от фазовращателей и двоичный код соответствующий "1". Во втором случае - набор фаз, соответствующий "1" в формате выбранной системы остаточных классов, и двоичный код преобразуемого числа А. Далее посредством суммирования формируется единый фазовый эквивалент числа А:

гармонических сигналов одной частоты. В первом случае управляемые фазовращатели из унитарного кода вычетов формируют набег фазы. Несмотря на то, что данная операция осуществляется на линиях задержки, где результатом является величина с отрицательным знаком, в силу периодичности гармоники и табличного способа коммутации ключей в самом блоке (патент РФ №2253943, фиг.2) возможно сформировать любой положительный сдвиг фазы. На первых блоках умножения фазы осуществляется операция, где в качестве операндов выступают сигналы от фазовращателей и двоичный код соответствующий "1". Во втором случае - набор фаз, соответствующий "1" в формате выбранной системы остаточных классов, и двоичный код преобразуемого числа А. Далее посредством суммирования формируется единый фазовый эквивалент числа А:

где μj - вес ортогонального базиса, полученный из решения сравнения  . Реализация арифметических операций выражения (1)

. Реализация арифметических операций выражения (1)

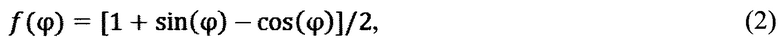

осуществляется (фиг.1) блоками умножения фазы 6.1-6.n (патент РФ №2653310) и сумматором фаз 8 (патент РФ №2653312). Формирование на выходе аналогового эквивалента для входной цифровой величины определяется функциональной зависимостью (фиг.2):

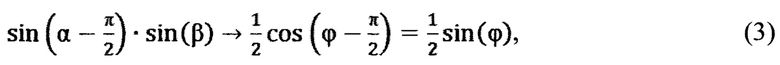

где ϕ - угол, изменяющийся в пределах от 0 до π/2. Такое ограничение фазы отражается в возможности использования чисел только из первой четверти диапазона (А≤Р/4), но дает максимальное отклонение от идеальной линейной характеристики около 2.1%, что в разы лучше, чем у прототипа. Формирование составных частей выходного аналогового эквивалента числа А осуществляется через низкочастотную фильтрацию результата перемножения тональных гармоник с аргументами α=ωt+ϕ и β=ωt.:

Полученные составные части складываются с постоянным уровнем сигнала, равным половине амплитуды используемых тональных гармоник, что приводит к выполнению выражения (2). Таким образом, реализуется заявленное расширение функциональных возможностей.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг.1 должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схемы данные элементы опущены.

Дополнительным эффектом является повышение точности преобразования, что, как было замечено выше, в разы лучше, чем у прототипа.

Показанный на фиг.1 цифроаналоговый преобразователь содержит генератор гармонического колебания 1, входы вычетов устройства 2.1-2.n, позиционный вход устройства 3, управляемые фазовращатели 4.1-4.n, первая группа блоков умножения фазы 5.1-5.n, вторая группа блоков умножения фазы 6.1-6.n, блоки памяти 7.1-7.n, сумматор фаз 8, первый и второй фазовращатель на угол π/2 9, первый и второй аналоговые перемножители 10, вход постоянного сигнала 11, первый и второй фильтры низких частот 12, сумматор сигналов 13, выход устройства 14.

Выход генератора гармонического колебания 1 соединен с первыми входами управляемых фазовращателей 4.1-4.n, первыми входами блоков умножения фазы 5.1-5.n и 6.1-6.n, первым входом сумматора фаз 8, вторыми входами первого и второго аналоговых перемножителей 10, выходы которых соединены с входами соответствующих фильтров низких частот 12, выходы которых соответственно соединены с вторым и третьим входами сумматора сигналов 13, при этом вход постоянного сигнала устройства 11 объединен с первым входом сумматора сигналов 13, выход которого объединен с выходом устройства 14, позиционный вход устройства 3 объединен с третьими входами блоков умножения фазы 5.1-5.n, выходы блоков памяти 7.1-7.n соединены с третьими входами соответствующих блоков умножения фазы 6.1-6.n, при этом входы вычетов устройства 2.1-2.n объединены с вторыми входами соответствующих управляемых фазовращателей 4.1-4.n, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы 5.1-5.n, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы 6.1-6.n, при этом выход блока умножения фазы 6.i  соединен с i+1-м входом сумматора фаз 8, выход которого соединен с входом первого фазовращателя на угол π/2 9, выход которого соединен с первым входом первого аналогового перемножителя 10, а также через второй фазовращатель на угол π/2 9 соединен с первым входом второго аналогового перемножителя 10.

соединен с i+1-м входом сумматора фаз 8, выход которого соединен с входом первого фазовращателя на угол π/2 9, выход которого соединен с первым входом первого аналогового перемножителя 10, а также через второй фазовращатель на угол π/2 9 соединен с первым входом второго аналогового перемножителя 10.

Работа устройства осуществляется в двух режимах: преобразование модулярного или позиционного кода. Пусть задана система остаточных классов по n взаимно простым основаниям p1, … pn с объемом чисел  , тогда в первом случае модулярная форма числа А=(γ1, … γn), при условии что А≤Р/4, подается на входы вычетов 2.1-2.n. В то же время на позиционный вход устройства 3 подается двоичный код соответствующий "1". Тональный сигнал от генератора гармонического колебания 1 с нулевой начальной фазой разбивается на отдельные гармоники и подается на первые входы управляемых фазовращателей 4.1-4.n, где формируются соответствующие набеги фаз 2π⋅γj/pj

, тогда в первом случае модулярная форма числа А=(γ1, … γn), при условии что А≤Р/4, подается на входы вычетов 2.1-2.n. В то же время на позиционный вход устройства 3 подается двоичный код соответствующий "1". Тональный сигнал от генератора гармонического колебания 1 с нулевой начальной фазой разбивается на отдельные гармоники и подается на первые входы управляемых фазовращателей 4.1-4.n, где формируются соответствующие набеги фаз 2π⋅γj/pj  . После умножения на "1" на блоках 5.1-5.n все готово для окончательного преобразования к аналоговому выходному эквиваленту. Во втором случае на входы вычетов 2.1-2.n подаются значения остатков соответствующие "1": (1, … 1), что приводит к формированию набегов фаз равных 2π/pj, а на позиционный вход устройства - двоичное представление числа

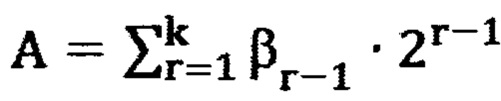

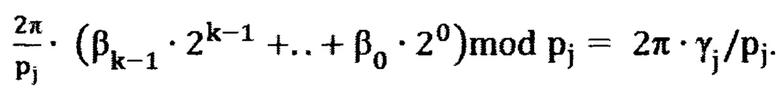

. После умножения на "1" на блоках 5.1-5.n все готово для окончательного преобразования к аналоговому выходному эквиваленту. Во втором случае на входы вычетов 2.1-2.n подаются значения остатков соответствующие "1": (1, … 1), что приводит к формированию набегов фаз равных 2π/pj, а на позиционный вход устройства - двоичное представление числа  , где β - разряды числа ("0" или "1"), а к определяется как наименьшее при выполнении условия 2k>Р/4. Умножение на блоках 5.1-5.n соответствует равенству:

, где β - разряды числа ("0" или "1"), а к определяется как наименьшее при выполнении условия 2k>Р/4. Умножение на блоках 5.1-5.n соответствует равенству:

Поскольку определена система остаточных классов, то известны и коэффициенты uj для выражения (1). Полученные любым вариантом исходные набеги фаз преобразуются на блоках 6.1-6.n и сумматоре 8 в единый эквивалент числа Α: ϕ. Далее на блоках 10 происходит перемножение сигналов так, что за счет фазовращателей 9 на первый из них гармоника приходит с дополнительной задержкой -π/2, а на второй - -π. После чего осуществляется низкочастотная фильтрация на 12, что соответствует выполнению выражений (3) и (4). Сложение на 13 с постоянной со входа 11 величиной сигнала (тока или напряжения) приводит к реализации выражения (2) и формированию на выходе 14 аналогового эквивалента входной цифровой величины.

Пример.

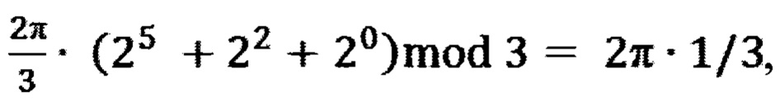

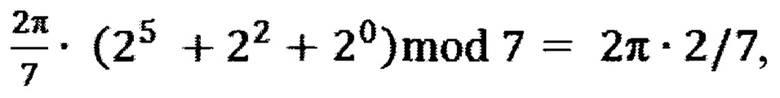

Пусть задана система остаточных классов по четырем взаимно простым основаниям 3, 5, 7 и 4 с объемом чисел  , тогда в первом случае модулярная форма числа А=37=(1, 2, 2, 1), при условии, что А≤Р/4 (37<105), подается на входы вычетов 2.1-2.4. В то же время на позиционный вход устройства 3 подается двоичный код соответствующий "1". Тональный сигнал от генератора гармонического колебания 1 с нулевой начальной фазой разбивается на отдельные гармоники и подается на первые входы управляемых фазовращателей 4.1-4.4, где формируются соответствующие набеги фаз 2π⋅γj/pj 2π⋅1/3, 2π⋅2/5, 2π⋅2/7, 2π⋅1/4. После умножения на "1" на блоках 5.1-5.4 все готово для окончательного преобразования к аналоговому выходному эквиваленту. Во втором случае на входы вычетов 2.1-2.4 подаются значения остатков соответствующие "1": (1,1,1,1), что приводит к формированию набегов фаз равных 2π/pj: 2π/3, 2π/5, 2π/7, 2π/4, а на позиционный вход устройства - двоичное представление числа Α=37=0⋅26+1⋅25+0⋅24+0⋅23+1⋅22+0⋅21+1-20, где k=7, поскольку определяется как наименьшее при условии 2k>Р/4 (27>105). Умножение на блоках 5.1-5.4 соответствует равенствам:

, тогда в первом случае модулярная форма числа А=37=(1, 2, 2, 1), при условии, что А≤Р/4 (37<105), подается на входы вычетов 2.1-2.4. В то же время на позиционный вход устройства 3 подается двоичный код соответствующий "1". Тональный сигнал от генератора гармонического колебания 1 с нулевой начальной фазой разбивается на отдельные гармоники и подается на первые входы управляемых фазовращателей 4.1-4.4, где формируются соответствующие набеги фаз 2π⋅γj/pj 2π⋅1/3, 2π⋅2/5, 2π⋅2/7, 2π⋅1/4. После умножения на "1" на блоках 5.1-5.4 все готово для окончательного преобразования к аналоговому выходному эквиваленту. Во втором случае на входы вычетов 2.1-2.4 подаются значения остатков соответствующие "1": (1,1,1,1), что приводит к формированию набегов фаз равных 2π/pj: 2π/3, 2π/5, 2π/7, 2π/4, а на позиционный вход устройства - двоичное представление числа Α=37=0⋅26+1⋅25+0⋅24+0⋅23+1⋅22+0⋅21+1-20, где k=7, поскольку определяется как наименьшее при условии 2k>Р/4 (27>105). Умножение на блоках 5.1-5.4 соответствует равенствам:

Поскольку определена система остаточных классов, то известны и коэффициенты μj для выражения (1): μ1=2, μ2=4, μ3=2, μ4=1. Полученные любым вариантом исходные набеги фаз преобразуются на блоках 6.1-6.4 и сумматоре 8 в единый эквивалент числа А:

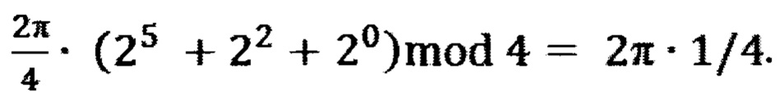

Далее на блоках 10 происходит перемножение сигналов так, что за счет фазовращателей 9 на первый из них гармоника приходит с дополнительной задержкой -π/2, а на второй - -π. После чего осуществляется низкочастотная фильтрация на 12, что соответствует выполнению выражений (3) и (4):

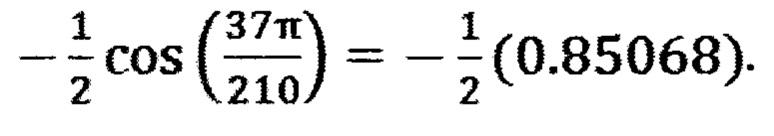

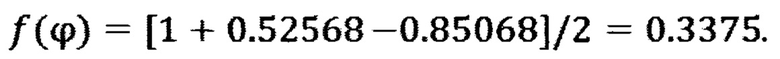

Сложение на 13 с постоянной со входа 11 величиной сигнала (тока или напряжения) приводит к реализации выражения (2) и формированию на выходе 14 аналогового эквивалента входной цифровой величины:

Для оценки второго положительного эффекта реализации устройства - точности преобразования - сравним результат с идеальной величиной, полученной как деление числа А=37 на объем применяемых чисел Р/4=105: 37/105=0.3524. Расхождение составляет 1.5%, что укладывается в заявленную точность.

Полученное устройство отражает принципы построения ЦАП на основе свойств системы остаточных классов. С точки зрения практического применения преобразователь реализует возможность вывода информации в аналоговой форме из цифровых модулярных и позиционных двоичных вычислительных структур с максимально возможным быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2020 |

|

RU2744337C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| ФАЗИРОВАННЫЙ КЛЮЧ ПО МОДУЛЮ m | 2017 |

|

RU2659866C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2231822C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2001 |

|

RU2192092C1 |

Изобретение относится к области автоматики, информационно-измерительной и вычислительной техники, и может быть использовано для преобразования модулярного и позиционного кода в аналоговый электрический сигнал. Технический результат заключается в обеспечении возможности формировать аналоговый эквивалент входной цифровой величины, заданной как в модулярном, так и позиционном представлении. Сущность изобретения сводится к промежуточному преобразованию цифрового модулярного или позиционного кода в дискретно-фазированную форму представления чисел в системе остаточных классов с дальнейшим переходом к выходному аналоговому эквиваленту в виде тока или напряжения. 2 ил.

Цифроаналоговый преобразователь, содержащий n входов вычетов устройства, где n - количество оснований системы остаточных классов, n управляемых фазовращателей, генератор гармонического колебания, первый фазовращатель на угол π/2, выход устройства, отличающийся тем, что введены позиционный вход устройства, первая и вторая группы из n блоков умножения фазы, n блоков памяти, сумматор фаз, второй фазовращатель на угол π/2, первый и второй аналоговые перемножители, первый и второй фильтры низких частот, вход постоянного сигнала устройства, сумматор сигналов, при этом выход генератора гармонического колебания соединен с первыми входами управляемых фазовращателей, первыми входами блоков умножения фазы первой и второй группы, первым входом сумматора фаз, вторыми входами первого и второго аналоговых перемножителей, выходы которых соединены с входами соответствующих фильтров низких частот, выходы которых соответственно соединены с вторым и третьим входами сумматора сигналов, при этом вход постоянного сигнала устройства объединен с первым входом сумматора сигналов, выход которого объединен с выходом устройства, позиционный вход устройства объединен с третьими входами блоков умножения фазы первой группы, выходы блоков памяти соединены с третьими входами соответствующих блоков умножения фазы второй группы, при этом входы вычетов устройства объединены с вторыми входами соответствующих управляемых фазовращателей, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы первой группы, выходы которых соединены с вторыми входами соответствующих блоков умножения фазы второй группы, при этом выход i-го  блока умножения фазы второй группы соединен с i+1-м входом сумматора фаз, выход которого соединен с входом первого фазовращателя на угол π/2, выход которого соединен с первым входом первого аналогового перемножителя, а также через второй фазовращатель на угол π/2 соединен с первым входом второго аналогового перемножителя.

блока умножения фазы второй группы соединен с i+1-м входом сумматора фаз, выход которого соединен с входом первого фазовращателя на угол π/2, выход которого соединен с первым входом первого аналогового перемножителя, а также через второй фазовращатель на угол π/2 соединен с первым входом второго аналогового перемножителя.

| СПОСОБ ПРЕОБРАЗОВАНИЯ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В НАПРЯЖЕНИЕ | 2003 |

|

RU2253943C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В НАПРЯЖЕНИЕ | 2005 |

|

RU2289881C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В НАПРЯЖЕНИЕ | 2005 |

|

RU2290754C1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1989 |

|

SU1742997A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| ЦИФРОВОЙ ФИЛЬТР В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2291557C1 |

| US 4963869 A1, 16.10.1990 | |||

| JP 61029208 A, 10.02.1986. | |||

Авторы

Даты

2021-03-10—Публикация

2020-08-05—Подача