Изобретение относится к цифровой вычислительной технике и предназначено для решения задачи функционального тестирования статических оперативных запоминающих устройств (ОЗУ) как на стадии их производства, так и на стадии их эксплуатации, например, в микропроцессорных системах.

Наиболее близким по технической сути является способ тестирования ОЗУ, представленный в [пат. РФ №2455712, МПК8 - G11C 29/20; опубл. 27.06.2012; Бюл. №18].

Данный способ тестирования ОЗУ заключается в том, что путем использования Р-разрядного генератора псевдослучайных чисел на основе циклического регистра сдвига с линейной обратной связью и периодом повторения М, структуру которого предварительно определяют на основе системы неравенств

М = (2P - 1) ≥ N*L, К ≥ int[Log2 (N*L) + 0.5],

где L - разрядность тестируемого ОЗУ;

N - количество ячеек тестируемого ОЗУ;

int[X] - целая часть X,

проводят подряд не менее К циклов тестирования, в каждом из которых выполняют, последовательно чередуя, процедуру записи тестовых L-разрядных псевдослучайных чисел во все N ячейки ОЗУ, а затем процедуру чтения из каждой ячейки ОЗУ записанных в них данных и сравнения их с тестовыми псевдослучайными числами, причем для формирования тестовых псевдослучайных чисел сначала в генератор псевдослучайных чисел записывают новое, отличное от нуля, начальное двоичное Р-разрядное число, на основе которого формируют и позже используют первое L-разрядное тестовое число, затем последовательно осуществляют (М - 1) циклических сдвигов в регистре сдвига с линейной обратной связью и таким образом формируют все N L-разрядные тестовые числа, причем в процедуру генерации тестовых псевдослучайных чисел включают операцию селекции, при которой из подряд формируемых псевдослучайных чисел в качестве тестовых выбирают только те, которые отстоят друг от друга точно на L псевдослучайных чисел по следующей зависимости

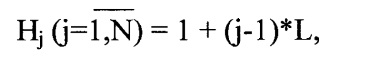

где j - номер ячейки ОЗУ,

Hj - номер псевдослучайного числа, записываемого в j-ю ячейку ОЗУ.

При данном способе тестирования ОЗУ выполняется необходимое и достаточное условие функционального тестирования ОЗУ, сформулированное в статье [Акинина Ю.С., Тюрин С.В. Об одном подходе к формализации понятий «необходимость» и «достаточность» функциональных тестов ОЗУ // Вестник ВГТУ. Научно-технический журнал. Выпуск 8.1. Воронеж, 2001 г. - С. 50-52], и заключающееся в обеспечении индивидуальной различимости каждого элемента (бита) памяти. Под различимостью понимается то, что в каждый отдельный элемент памяти будет записываться отличный от всех других элементов памяти К-разрядный последовательный код, формируемый в них за К циклов тестирования. Обеспечение такой различимости элементов памяти гарантирует обнаружение всех константных неисправностей и способствует обнаружению неисправностей, обусловленных информационным взаимовлиянием элементов памяти, так как для произвольно выбранной пары элементов памяти будет обеспечен их «бинарный антагонизм» - одновременно в один из элементов будет записываться 1, а в другой - 0.

Недостатком данного способа тестирования ОЗУ является то, что из-за выполнения операции селекции возникает зависимость времени тестирования от разрядности L тестируемого ОЗУ, что, с увеличением разрядности ОЗУ, снижает частоту записи/чтения и, таким образом, снижает эффективность обнаружения неисправностей, обусловленных информационным взаимовлиянием элементов памяти.

Изобретение направлено на максимизацию эффективности обнаружения неисправностей, обусловленных информационным взаимовлиянием элементов памяти, путем устранения зависимости времени тестирования от разрядности L тестируемого ОЗУ.

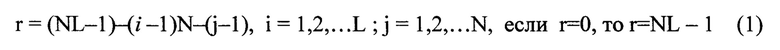

Это достигается тем, что в процедуре генерации тестовых L-разрядных псевдослучайных чисел значение каждого разряда в них одновременно формируют непосредственно или путем свертки по модулю два из текущих значений разрядов Р - разрядного генератора псевдослучайных чисел таким образом, что в каждом i-ом разряде j-oro тестового слова формируют r-ый символ псевдослучайной последовательности с периодом повторения М, на основе следующего соотношения

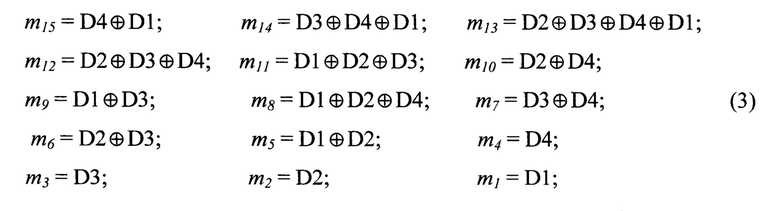

На фиг. 1 представлен 4-х разрядный генератор псевдослучайной двоичной последовательности (т.е. Р=4), период повторения которого М = 2P - 1 = 15 и который реализован на циклическом регистре сдвига с сумматором по модулю 2 (⊕) в цепи обратной связи. Полином, порождающий псевдослучайную последовательность максимальной длины (М-последовательность), имеет следующий вид 1 + Х + Х4 и, следовательно, определяет условие подключения к входам сумматора по модулю 2 выходов первого (D1) и четвертого (D4) разрядов циклического регистра сдвига. На этой же фиг. 1 показана сама периодическая псевдослучайная М-последовательность как в битовом (0,1), так и в символьном (mr) виде.

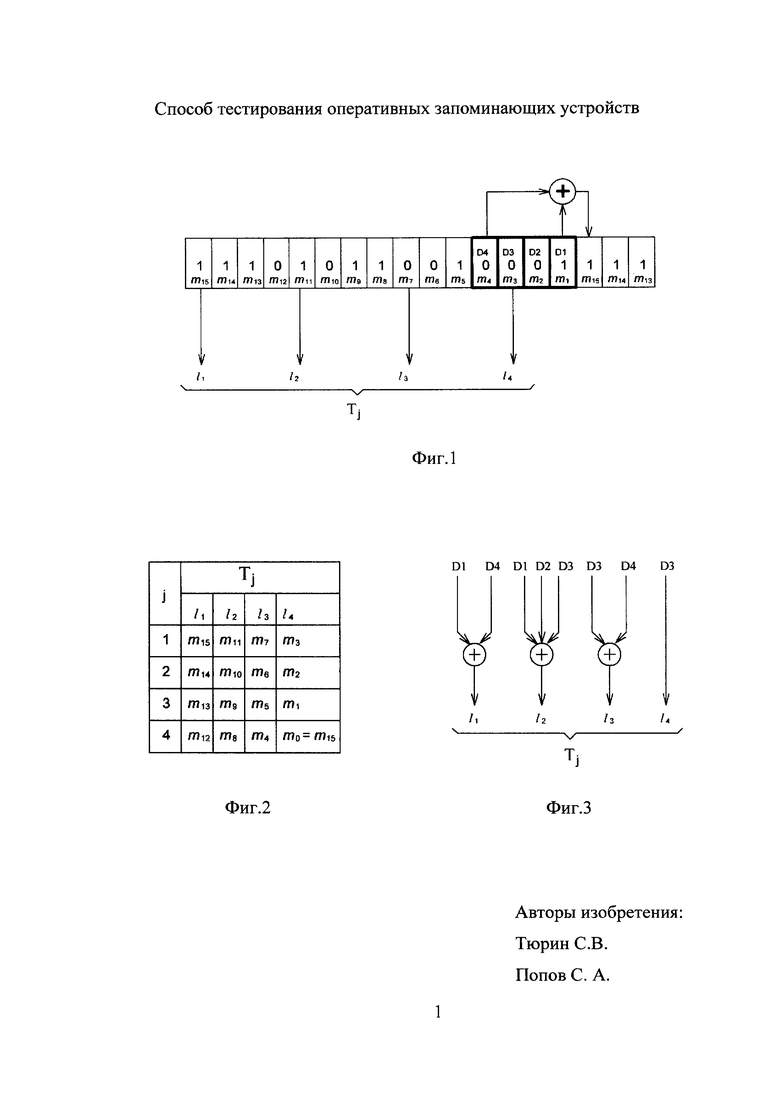

На фиг. 2 показана последовательность 4-рахрядных двоичных псевдослучайных чисел Tj, которые формируется по заявляемому способу в случае тестирования ОЗУ с организацией L = 4 и N = 4, т.е. с организацией 4 ячейки памяти по 4 разряда.

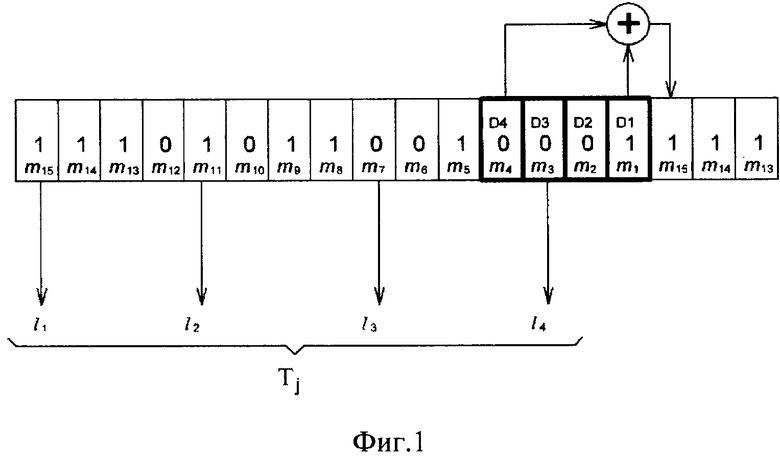

На фиг. 3 показан вариант реализации схемы формирования тестовых слов по заявляемому способу тестирования на примере ОЗУ с организацией 4 ячейки памяти по 4 разряда и 4-х разрядного генератора псевдослучайной двоичной последовательности с порождающим полиномом 1 + Х + Х4. Практическая реализация предлагаемого способа тестирования оперативных запоминающих устройств базируется на широко известном свойстве М-последовательностей, а именно на свойстве «сдвига и суммирования по модулю два», изложенном, например, в книге [Корн Г.А. Моделирование случайных процессов на аналоговых и аналогово-цифровых машинах. - М.: Мир, 1968, - 315 с.]. Данное свойство заключается в том, что если М-последовательность почленно суммировать по модулю 2 с любым ее циклическим сдвигом в течение периода этой последовательности, то образуется новая М-последовательность, отличающаяся только сдвигом от порождающих ее последовательностей. При использования Р-разрядного генератора псевдослучайных чисел на основе циклического регистра сдвига с линейной обратной связью, параллельно порождающего (Р + 1) сдвинутых относительно друг друга М-последовательностей, можно сформировать любую отсутствующую из ((2Р - 1) - Р - 1) М-последовательность с требуемым сдвигом, например по методике, изложенной в статье [Тюрин С.В. Многоканальный генератор коррелированных М-последовательностей // Техника и машиностроение. 2002. №4. С. 77-78].

Для реализации предлагаемого способа тестирования оперативных запоминающих устройств на каждом шаге тестирования требуется формировать L символов, каждый из которых является символом генерируемой М-последовательности, причем расстояние между двумя ближайшими по значению символами должно быть равно N, что формализуется зависимостью (1).

Суть предлагаемого способа тестирования ОЗУ наглядно демонстрирует фиг. 1: генерируемую Р-разрядным генератором М-последовательность, как бы «разрезают» на L равных подпоследовательностей, в каждой из которых содержится ровно по N символов, при этом символы каждой подпоследовательности одновременно формируют в отдельных разрядах  тестового слова Tj. В результате, как видно из фиг. 2, в каждом цикле тестирования ОЗУ в него записывают данные, которые при определенном и неизменном обходе бит ОЗУ будут являться последовательными символами генерируемой М-последовательности.

тестового слова Tj. В результате, как видно из фиг. 2, в каждом цикле тестирования ОЗУ в него записывают данные, которые при определенном и неизменном обходе бит ОЗУ будут являться последовательными символами генерируемой М-последовательности.

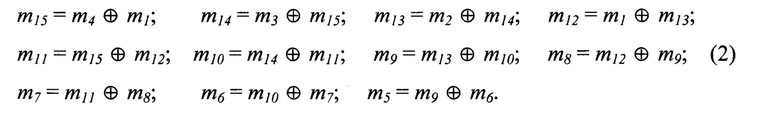

Для синтеза схемы формирования тестовых слов по заявляемому способу тестирования представим, что бинарные значения mr генерируемой М-последовательности зафиксированы в 2Р - 1 позициях воображаемой «ленты» и периодически повторены, как показано на фиг. 1. Вдоль такой «ленты» перемещается вправо сумматор по модулю 2 со всеми своими прямыми и обратными связями, расположение которых определяется примитивным полиномом, порождающим М-последовательность. Тогда можно составить следующую систему логических уравнений (2):

Учитывая, что символ m4 формируется с выхода генератора D4, символ m3 - с выхода D3, символ m3 - с выхода D3, символ m2 - с выхода D2, символ m1 - с выхода D1, система уравнений (2), с учетом последовательных подстановок и идемпотентного закона относительно операции сложения по модулю 2, перепишется следующим образом (3):

Как следуют из системы уравнений (3) для рассматриваемого на фиг. 1 и 2 примера реализации заявляемого способа тестирования ОЗУ необходимо формировать разряды  тестовых слов следующим образом:

тестовых слов следующим образом:

На фиг. 3 показан вариант реализации системы уравнений (4).

Техническим результатом от использования заявляемого изобретения является устранение зависимости времени тестирования от разрядности L тестируемого ОЗУ и, тем самым, максимизация эффективности обнаружения неисправностей, обусловленных информационным взаимовлиянием элементов памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ТЕСТИРОВАНИЯ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2009 |

|

RU2455712C2 |

| Устройство для формирования тестов | 1984 |

|

SU1226472A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Генератор тестов | 1986 |

|

SU1424020A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1091227A1 |

| Генератор равномерно распределенных псевдослучайных чисел | 1973 |

|

SU468231A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении эффективности обнаружения неисправностей, обусловленных информационным взаимовлиянием элементов памяти. Способ тестирования ОЗУ, в котором путем использования P-разрядного генератора псевдослучайных чисел на основе циклического регистра сдвига с линейной обратной связью и периодом повторения М, структуру которого предварительно определяют на основе системы неравенств, проводят подряд не менее К циклов тестирования, в каждом из которых выполняют, последовательно чередуя, процедуру записи тестовых L-разрядных псевдослучайных чисел во все N ячейки ОЗУ, а затем процедуру чтения из каждой ячейки ОЗУ записанных в них данных и сравнения их с тестовыми псевдослучайными числами, причем в процедуре генерации тестовых L-разрядных псевдослучайных чисел значение каждого разряда в них одновременно формируют непосредственно или путем свертки по модулю два из текущих значений разрядов P-разрядного генератора псевдослучайных чисел таким образом, что в каждом i-м разряде j-го тестового слова формируют r-й символ псевдослучайной последовательности с периодом повторения М. 3 ил.

Способ тестирования ОЗУ, заключающийся в том, что путем использования P-разрядного генератора псевдослучайных чисел на основе циклического регистра сдвига с линейной обратной связью и периодом повторения М, структуру которого предварительно определяют на основе системы неравенств

M=(2P-1)≥N*L, К≥int[Log2(N*L)+0.5],

где L - разрядность тестируемого ОЗУ;

N - количество ячеек тестируемого ОЗУ;

int[X] - целая часть X,

проводят подряд не менее К циклов тестирования, в каждом из которых выполняют, последовательно чередуя, процедуру записи тестовых L-разрядных псевдослучайных чисел во все N ячейки ОЗУ, а затем процедуру чтения из каждой ячейки ОЗУ записанных в них данных и сравнения их с тестовыми псевдослучайными числами, причем для формирования тестовых псевдослучайных чисел сначала в генератор псевдослучайных чисел записывают новое, отличное от нуля, начальное двоичное P-разрядное число, на основе которого формируют и позже используют первое L-разрядное тестовое число, затем последовательно осуществляют (М-1) циклических сдвигов в регистре сдвига с линейной обратной связью и таким образом формируют все N L-разрядные тестовые числа, отличающийся тем, что в процедуре генерации тестовых L-разрядных псевдослучайных чисел значение каждого разряда в них одновременно формируют непосредственно или путем свертки по модулю два из текущих значений разрядов P-разрядного генератора псевдослучайных чисел таким образом, что в каждом i-м разряде j-го тестового слова формируют r-й символ псевдослучайной последовательности с периодом повторения М, на основе следующего соотношения

r=(NL-1)-(i-1)N-(j-1),

где i=1, 2, …, L; j=1, 2, …, N, если r=0, то r=NL - 1.

| СПОСОБ ТЕСТИРОВАНИЯ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2009 |

|

RU2455712C2 |

| CN 101894591 A, 24.11.2010 | |||

| СИСТЕМА ФУНКЦИОНАЛЬНОГО ТЕСТИРОВАНИЯ КАРТ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ | 2012 |

|

RU2524858C2 |

| US 6006345 A1, 21.12.1999 | |||

| Способ определения качества минераловатных и стекловатных изделий | 1976 |

|

SU585435A1 |

Авторы

Даты

2018-07-06—Публикация

2017-02-20—Подача