Изобретение относится к испытательной технике и может быть использовано для диагностики функционирования и определения запасов надежности карт полупроводниковой памяти во всех отраслях промышленности как на этапе производства карт памяти, так и в процессе эксплуатации.

Актуальность проверки карт полупроводниковой памяти связана как с увеличением глубины выходного контроля при производстве, так и с необходимостью проведения дополнительных тестов при использовании карт в ответственных применениях. Устройства функционального тестирования можно разбить на два класса: универсальные устройства функционального тестирования электронных компонентов и специализированные устройства тестирования полупроводниковой памяти.

Существующие в настоящее время универсальные устройства функционального тестирования электронных компонентов (Л1-Л6) обладают рядом недостатков при выполнении функционального тестирования карт полупроводниковой памяти, а именно: для проведения тестирования необходимо формировать файлы функционального контроля в виде последовательности векторов определяющих или контролирующих состояние на каждом выводе карты памяти. Независимо от используемого алгоритма процедура тестирования заключается в многократной записи и чтении ячеек памяти. В отличие от микросхем памяти, для работы с картами полупроводниковой памяти используется последовательный интерфейс, с защитой передаваемых данных контрольной суммой (Л7). Для определения технологических запасов процедуру тестирования необходимо выполнять многократно, изменяя временные характеристики сигналов. Рассмотренные особенности функционального тестирования и определения технологических запасов карт полупроводниковой памяти приводят к тому, что процесс создания файлов функционального контроля значительно усложняется, возникают дополнительные требования к устройству тестирования на скорость его работы и объем памяти тестовых векторов.

Существующие в настоящее время специализированные устройства функционального тестирования полупроводниковой памяти также обладают рядом недостатков. Рассмотрим их более подробно.

Известно устройство «Система функционального тестирования корпусированных микросхем оперативно запоминающих устройств» (патент РФ №2438164 от 10.11.2009), того же назначения, что и предлагаемое, но не имеющее с ним общих признаков и содержащее микроконтроллер со встроенной flash-памятью и с двумя аналогово-цифровыми преобразователями (АЦП), преобразователь интерфейса USB в UART, генератор на 100 МГц, датчик температуры микроконтроллера, источники питания на 1,7 В, 2,5 В, 3,3 В, 5,0 В, блок выбора источника питания, блок измерения тока потребления, блок проверки контактирования выводов тестируемых микросхем ОЗУ, преобразователь уровня напряжения управляющих входов тестируемых микросхем ОЗУ, преобразователь уровня напряжения шины адреса тестируемых микросхем ОЗУ, персональный компьютер (ПК), блок питания, драйвер, компаратор, нагрузку для каждой из n линий шины данных тестируемых микросхем ОЗУ, m цифровых датчиков температуры микросхем ОЗУ, закрепленных на корпусе тестируемых микросхем ОЗУ.

Основные недостатки данного устройства заключаются в отсутствии возможности определения запаса надежности тестируемого устройства, а именно определения предельных временных параметров работы интерфейса карт полупроводниковой памяти и минимального значения напряжения питания.

Сущностью предлагаемого изобретения является система функционального тестирования карт полупроводниковой памяти с возможностью определения запаса надежности за счет измерения предельных временных параметров работы интерфейса карты полупроводниковой памяти и минимального значения напряжения питания.

Достигаемый технический результат заключается в увеличении функциональных возможностей систем тестирования, возможности определения запаса надежности тестируемого устройства.

Сопоставительный анализ с прототипом показывает, что предлагаемая система отличается наличием группы новых признаков: автомата управления, контроллера интерфейса Ethernet, оперативного запоминающего устройства, контроллера интерфейса карты полупроводниковой памяти, блока регистров управления, блока формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс, умножителя частоты на основе фазовой автоподстройки частоты, блока управления устройством ввода и устройством индикации, блока приемопередатчика последовательного интерфейса, программируемой логической интегральной схемы, микросхемы приемопередатчика интерфейса Ethernet, вторичного источника питания, постоянной перепрограммируемой памяти, преобразователя уровня напряжения интерфейса карты памяти, тактового генератора 25 МГц, устройства ввода, устройства индикации, датчика температуры карты памяти, управляемого источника питания с выходным напряжением от 1 В до 5 В, датчика тока и контактного устройства для подключения карты полупроводниковой памяти. Следовательно, устройство удовлетворяет критерию «новизна».

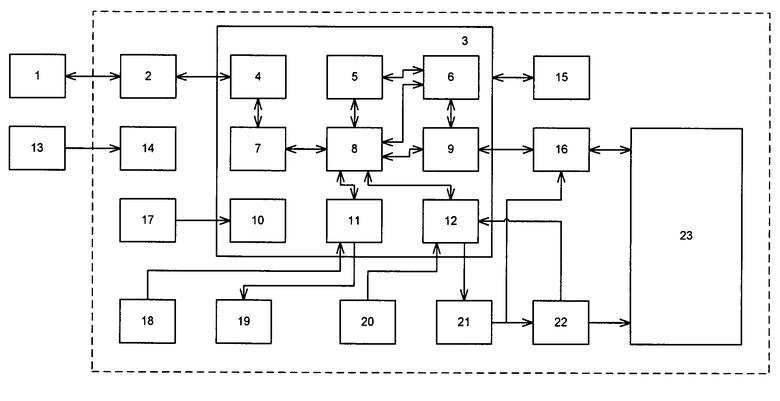

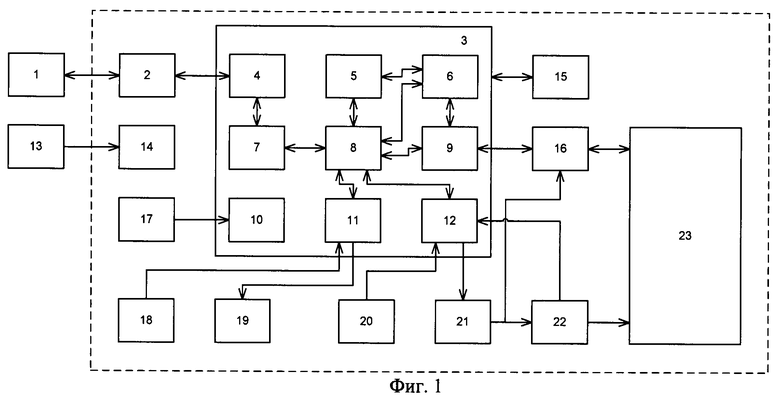

Изобретение поясняется следующим графическим материалом:

фиг.1 - структурная схема системы функционального тестирования карт

полупроводниковой памяти, в состав которой входят:

1 - персональный компьютер (ПК);

2 - микросхемы приемопередатчика интерфейса Ethernet;

3 - программируемая логическая интегральная схема;

4 - контроллер интерфейса Ethernet;

5 - оперативное запоминающее устройство;

6 - контроллер интерфейса карты полупроводниковой памяти;

7 - блок регистров управления;

8 - автомат управления;

9 - блок формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс;

10 - умножитель частоты на основе фазовой автоподстройки частоты;

11 - блок управления устройством ввода и устройством индикации;

12 - блок приемопередатчика последовательного интерфейса;

13 - блок питания на напряжение 5,0 В;

14 - вторичный источник питания;

15 - постоянная перепрограммируемая память;

16 - преобразователь уровня напряжения интерфейса карты памяти;

17 - тактовый генератор 25 МГц;

18 - устройство ввода;

19 - устройство индикации;

20 - датчик температуры карты памяти;

21 - управляемый источник питания с выходным напряжением от 1 В до 5 В;

22 - датчик тока;

24 - контактное устройство для подключения карты полупроводниковой памяти.

Система функционального тестирования карт полупроводниковой памяти состоит из автомата управления (8), контроллера интерфейса Ethernet (4), оперативного запоминающего устройства (5), контроллера интерфейса карты полупроводниковой памяти (6), блока регистров управления (7), блока формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс (9), умножителя частоты на основе фазовой автоподстройки частоты (10), блока управления устройством ввода и устройством индикации (11), блока приемопередатчика последовательного интерфейса (12), программируемой логической интегральной схемы (3), микросхемы приемопередатчика интерфейса Ethernet (2), вторичного источника питания (14), постоянной перепрограммируемой памяти (15), преобразователя уровня напряжения интерфейса карты памяти (16), тактового генератора 25 МГц (17), устройства ввода (18), устройства индикации (19), датчика температуры карты памяти (20), управляемого источника питания с выходным напряжением от 1 В до 5 В (21), датчика тока (22) и контактного устройства для подключения карты полупроводниковой памяти (23), причем автомат управления (8), контроллер интерфейса Ethernet (4), оперативное запоминающее устройство (5), контроллер интерфейса карты полупроводниковой памяти (6), блок регистров управления (7), блок формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс (9), умножитель частоты на основе фазовой автоподстройки частоты (10), блок управления устройством ввода и устройством индикации (11), блок приемопередатчика последовательного интерфейса (12) реализованы в программируемой логической интегральной схеме (3); персональный компьютер (1) через приемопередатчик интерфейса Ethernet (2) и контроллер интерфейса Ethernet (4) подключен к блоку регистров управления (7); автомат управления (8) через блок управления устройством ввода и устройством индикации (11) подключен к устройству ввода (18) и устройству индикации (19); автомат управления (8) через блок приемопередатчика последовательного интерфейса (12) подключен к датчику температуры карты памяти (20), управляемому источнику питания с выходным напряжением от 1 В до 5 В (21) и датчику тока (22); автомат управления (8) подключен к блоку формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс (9), контроллеру интерфейса карты полупроводниковой памяти (6), оперативному запоминающему устройству (5), блоку регистров управления (7); контроллер интерфейса карты полупроводниковой памяти (6) подключен к оперативному запоминающему устройству (5); контроллер интерфейса карты полупроводниковой памяти (6) подключен к контактному устройству для подключения карты полупроводниковой памяти (23) через блок формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс (9) и преобразователь уровня напряжения интерфейса карты памяти (16); управляемый источник питания с выходным напряжением от 1 В до 5 В (21) подключен к преобразователю уровня напряжения интерфейса карты памяти (16) и к контактному устройству для подключения карты полупроводниковой памяти (23) через датчик тока (22); тактовый генератор 25 МГц (17) подключен к умножителю частоты на основе фазовой автоподстройки частоты (10), тактовая частота с которого подается на все блоки, реализованные в программируемой логической интегральной схеме (3); вторичный источник питания (14) соединен со всеми элементами схемы.

Система функционального тестирования карт полупроводниковой памяти работает следующим образом. Тестируемая карта полупроводниковой памяти подключается к контактному устройству (23). После подачи питания в ПЛИС (3) загружается конфигурационная информация из постоянной перепрограммируемой памяти (15). По интерфейсу Ethernet с персонального компьютера (1) поступает информация о тестируемой карте памяти, а также об условиях проведения тестирования. Данная информация через микросхему приемопередатчика интерфейса Ethernet (2), выполняющую преобразование физического уровня сигналов интерфейса Ethernet в параллельную шину с логическими уровнями, необходимыми для работы ПЛИС, поступает в контроллер Ethernet (4) программируемой логической схемы (3). Контроллер интерфейса Ethernet обрабатывает полученную информацию и помещает ее в соответствующие регистры управления (7). Управляющий автомат (8) анализирует содержимое регистров управления и на основе их содержимого выполняет через блок приемопередатчика последовательного интерфейса (12) настройку управляемого источника питания (21), после этого автомат управления (8) производит считывание тока потребления карты памяти из блока измерения тока (22) через блок последовательного интерфейса (12) и сравнение его со значениями порогов П1 и П2 хранящимися в блоке регистров управления. При превышении тока потребления над порогом П1 автомат управления (8) отключает управляемый источник питания через последовательный интерфейс (12), выдает сообщения на устройство индикации (19) через блок управления (11) о превышении тока и передает соответствующее сообщение в персональный компьютер (1) через интерфейс Ethernet через блок регистров управления (7). Если значение тока ниже порога П2, автомат управления (8) отключает управляемый источник питания через последовательный интерфейс (12), выдает сообщения на устройство индикации (19) через блок управления (11) о том, что значение тока ниже порога и передает соответствующее сообщение в персональный компьютер (1) через интерфейс Ethernet через блок регистров управления (7). В противном случае автомат управления (8) выдает сообщения на устройство индикации (19) через блок управления (11) о том, чтобы начать выполнение теста. Оператор, видя сообщение о возможности начала теста, с помощью устройства ввода (18) посылает соответствующую команду через контроллер (11) в автомат управления (8). Автомат управления (8) на основе данных регистров управления (7) производит формирование наборов тестовых данных в оперативной памяти (5), инициализацию контроллера интерфейса карты полупроводниковой памяти (6), настройку блока формирования и измерения временных параметров (9) для проведения тестирования. Автомат управления (8) производит необходимое количество тестов с параметрами, хранящимися в блоке регистров управления (7). Во время проведения теста автомат управления (8) выполняет считывание значения тока потребления из блока измерения (22) и температуры карты памяти из датчика температуры (20) через блок приемопередатчика последовательного интерфейса (12). По окончании выполнения тестирования автомат управления передает результаты в персональный компьютер (1) через блок регистров управления (7, контроллер Ethernet (4) и микросхему приемопередатчика интерфейса Ethernet (2) для анализа полученных данных. После анализа данных персональный компьютер (1) формирует данные для отображения на индикаторе и передает их через микросхему приемопередатчика интерфейса Ethernet (2), блок контроллера Ethernet (4) в блок регистров управления (7). Управляющий контроллер (8) считывает данные из регистров управления (7) и через контроллер (11) отображает их на устройстве индикации (19) для оператора.

В результате предлагаемая система помимо основной функции тестирования карт полупроводниковой памяти позволяет получить предельные временные параметры работы интерфейса и значения минимального рабочего напряжения питания, что позволяет определить запас надежности.

Источники информации

1. «Formula 2К» фирмы «Форм», Россия (www.form.ru) - (Л1).

2. «Integra J750» фирмы «Teradyne», США (www.integra-tech.com) - (Л2).

3. «MicroATE Semicon Tester» фирмы «Qmax Test Equipments», США (www.qmaxtest.com) - (Л3).

4. «S680» фирмы «Keithley», США (www.keithley.com) - (Л4).

5. «ВТЦМ-32» фирмы Трейлер, Россия (www.stanok.cncinfo.ru) - (Л5).

6. «Волна» фирмы «ЦНИИИА», Россия (www.cime.ru) - (Л6).

7. Part 1 SD Physical Layer Simplified Specification Ver3.01

(https://ww.sdcard.org/downloads/pls/simplifid_specs/Part_1_Physical_Layer_Simplified_Specification_Ver_3.01_Final_100518.pdfi - (Л7).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| НАВИГАЦИОННЫЙ КОМПЛЕКС ЛЕТАТЕЛЬНОГО АППАРАТА | 2000 |

|

RU2170409C1 |

| АВТОМАТИЧЕСКАЯ НРЛС С УВЕЛИЧЕННЫМ НЕОБСЛУЖИВАЕМЫМ ПЕРИОДОМ АВТОНОМНОЙ РАБОТЫ | 2012 |

|

RU2522910C2 |

| УСТРОЙСТВО ПРОВЕРКИ РАБОТОСПОСОБНОСТИ СЕГМЕНТОВ ЛОКАЛЬНОЙ СЕТИ | 2003 |

|

RU2263342C2 |

| Промышленный контроллер | 2017 |

|

RU2642400C1 |

| ПРОГРАММНО-АППАРАТНЫЙ КОМПЛЕКС ТОПОПРИВЯЗЧИКА | 2011 |

|

RU2468338C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| Универсальный модульный IoT-контроллер для системы глобального мониторинга и управления энергопотреблением | 2019 |

|

RU2712111C1 |

| Многоканальная цифровая возбудительная система | 2018 |

|

RU2691757C1 |

| БЛОК ИНТЕРФЕЙСНЫЙ | 2007 |

|

RU2363980C2 |

Изобретение относится к испытательной технике и может быть использовано для диагностики функционирования и определения запасов надежности карт полупроводниковой памяти. Техническим результатом является обеспечение возможности определения запаса надежности тестируемого устройства. Система состоит из автомата управления, контроллера интерфейса Ethernet, оперативного запоминающего устройства, контроллера интерфейса карты полупроводниковой памяти, блока регистров управления, блока формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс, умножителя частоты на основе фазовой автоподстройки частоты, блока управления устройством ввода и устройством индикации, блока приемопередатчика последовательного интерфейса, программируемой логической интегральной схемы, микросхемы приемопередатчика интерфейса Ethernet, вторичного источника питания, постоянной перепрограммируемой памяти, преобразователя уровня напряжения интерфейса карты памяти, тактового генератора 25 МГц, устройства ввода, устройства индикации, датчика температуры карты памяти, управляемого источника питания с выходным напряжением от 1 В до 5 В, датчика тока и контактного устройства для подключения карты полупроводниковой памяти. 1 ил.

Система функционального тестирования карт полупроводниковой памяти, состоящая из автомата управления, контроллера интерфейса Ethernet, оперативного запоминающего устройства, контроллера интерфейса карты полупроводниковой памяти, блока регистров управления, блока формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс, умножителя частоты на основе фазовой автоподстройки частоты, блока управления устройством ввода и устройством индикации, блока приемопередатчика последовательного интерфейса, программируемой логической интегральной схемы, микросхемы приемопередатчика интерфейса Ethernet, вторичного источника питания, постоянной перепрограммируемой памяти, преобразователя уровня напряжения интерфейса карты памяти, тактового генератора 25 МГц, устройства ввода, устройства индикации, датчика температуры карты памяти, управляемого источника питания с выходным напряжением от 1 В до 5 В, датчика тока и контактного устройства для подключения карты полупроводниковой памяти, отличающаяся тем, что автомат управления, контроллер интерфейса Ethernet, оперативное запоминающее устройство, контроллер интерфейса карты полупроводниковой памяти, блок регистров управления, блок формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс, умножитель частоты на основе фазовой автоподстройки частоты, блок управления устройством ввода и устройством индикации, блок приемопередатчика последовательного интерфейса реализованы в программируемой логической интегральной схеме; персональный компьютер через приемопередатчик интерфейса Ethernet и контроллер интерфейса Ethernet подключен к блоку регистров управления; автомат управления через блок управления устройством ввода и устройством индикации подключен к устройству ввода и устройству индикации; автомат управления через блок приемопередатчика последовательного интерфейса подключен к датчику температуры карты памяти, управляемому источнику питания с выходным напряжением от 1 В до 5 В и датчику тока; автомат управления подключен к блоку формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс, контроллеру интерфейса карты полупроводниковой памяти, оперативному запоминающему устройству, блоку регистров управления; контроллер интерфейса карты полупроводниковой памяти подключен к оперативному запоминающему устройству, контроллер интерфейса карты полупроводниковой памяти подключен к контактному устройству для подключения карты полупроводниковой памяти через блок формирования и измерения временных параметров интерфейса карты памяти с разрешением 2,5 нс и преобразователь уровня напряжения интерфейса карты памяти; управляемый источник питания с выходным напряжением от 1 В до 5 В подключен к преобразователю уровня напряжения интерфейса карты памяти и к контактному устройству для подключения карты полупроводниковой памяти через датчик тока; тактовый генератор 25 МГц подключен к умножителю частоты на основе фазовой автоподстройки частоты, тактовая частота с которого подается на все блоки, реализованные в программируемой логической интегральной схеме; вторичный источник питания соединен со всеми элементами схемы.

| СИСТЕМА ФУНКЦИОНАЛЬНОГО ТЕСТИРОВАНИЯ КОРПУСИРОВАННЫХ МИКРОСХЕМ ОПЕРАТИВНО ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2009 |

|

RU2438164C2 |

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| Устройство для контроля интегральных микросхем памяти | 1983 |

|

SU1144154A1 |

| US 6715114 B2, 30.03.2004 | |||

| US 2012072790 A1, 22.03.2012 | |||

| WO 2012035651 A1, 22.03.2012 | |||

Авторы

Даты

2014-08-10—Публикация

2012-10-29—Подача