//, ,/

10

15

20

25

Изобретение относится к автомати- ке II вычислительной технике и может быть использовано для контроля мик- роЭВМ.

Цель изобретения - увеличение быстродействия.

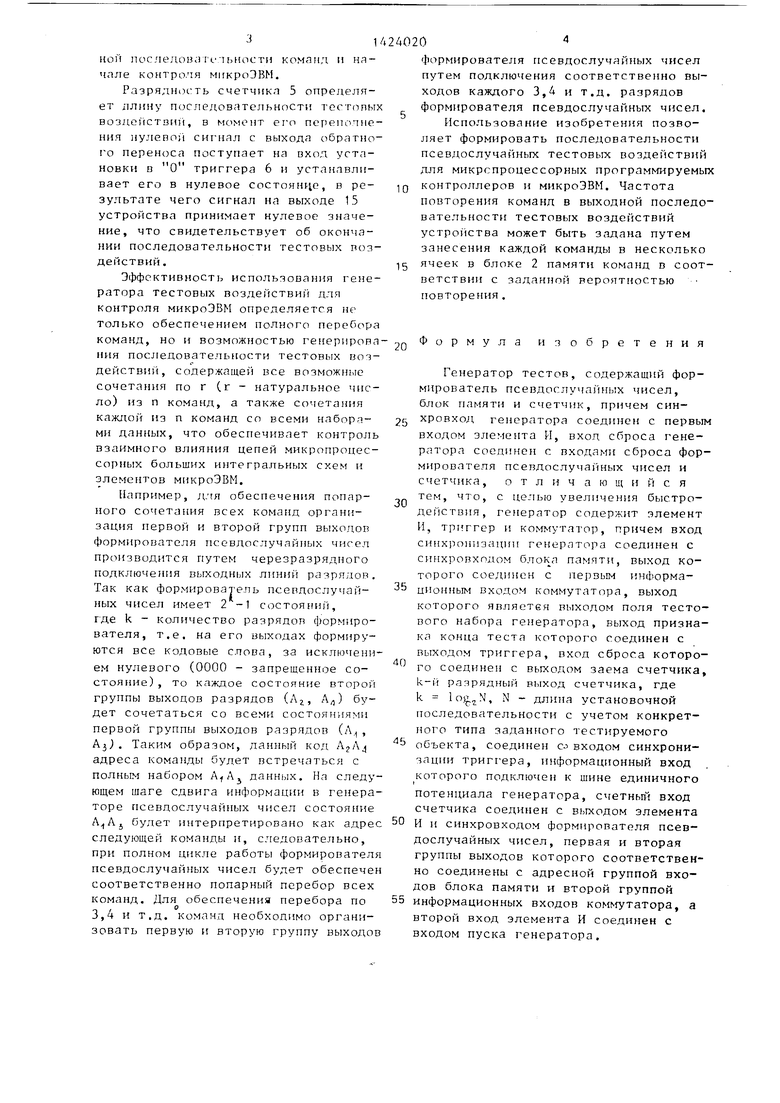

Па чертеже изображена блок-схема генератора.

Генератор содержит формирователь 1 псевдослучайных чисел, блок 2 памяти, коммутатор 3, элемент 4, счет- чиК 5, триггер 6, резистор 7, выходы 8 блока памяти, выходы 9 формирователя псевдослучайных чисел, вход 10 пуска генератора, вход 11 синхронизации генератора, вход 12 синхронизации коммутатора, выходы 13 поля тестового набора генератора, вход 14 сброса генератора, выход 15 признака конца теста генератора.

Формирователь 1 представляет собой регистр сдвига с линейной обратной связью и выполнен на стандартных логических элементах.

Коммутатор 3 содержит группу повторителей с тремя состояниями, выходы которых об11ед)П1ены и являются группой информационных входов, подключаемых к входу 8, и группой выходов, соединенных посредством выходов 13 с группой информационных выходов, а управляющие входы группы повторителей подключены к входу 12 коммутатора 3.

Блок 2 памяти может выполняться в виде постоянного или полупостоянного запоминающего устройства, где производится ра:: мещение кодов команд установочной последовательности п ячейках с адресами, определяемыми состояниями формирователя 1 псевдослучайных чисел на первых N шагах его работы. Остальные ячейки блока 2 заполняются кодами команд микроЭВМ (где N - число установок тестируемой ЭВМ) .

Генератор работает следующим образом.

Формирователь 1 и счетчик 5 устанавливаются в исходное состояние путем подачи на их входы сброса сигнаа Общий сброс с входа 14 устройства. Сигнал на этом входе может быть сформирован автоматически после включения питания или, например, появля- 5- ется в результате нажатия соответствующей кнопки на пульте управления. Нулевой сигнал с выхода заема счетчи30

35

40

45

50

0

5

0

5

-

0

5

0

5

0

ка 5 поступает на вход установки в О триггера 6 и устанавливает его в нулевое состояние, в результате чего сигнал, на выводе 15 устройства принимает нулевое значение.

При поступлении сигнала Цикл выборки команды на вход 11 устройства открывается элемент И 4, сигнал синхронизации поступает с Синхровхода 10 устройства на синхровходы формирователя 1 псевдослучайных чисел и счетчика 5, переводя их в следующие состояния, при зтом код адреса первой команды поступает с выходов формирователя 1 псевдослучайных чисел на Соответствующие входы группы адресных входов блока 2 памяти. Одновременно сигнал Цикл выборки команды поступает на вход выбор си кристалла блока 2 памяти и управляющий вход 12 коммутатора 3, переводя повторитель этого коммутатора в высокоимпедансное состояние. Первая команда поступает с выхода блока 2 памят.и по цепи вход 8 - выходы 13 на выходы генератора. После снятия сигнала Цикл выборки команды элемент И 4 закрывается, запрещая прохолодение синхросигнала на синхровходы формирователя 1 псевдослучайных чисел и счетчика 5, группы выходов блока 2 памяти устанавливают в высокоимпедансное состояние, группа повторителей ко -1мутатора 3 открывается и информация с выходов формирователя 1 псевдослучайных чисел поступает на выходы устройства.

Таким образом, в момент установки единичного значения сигнала Цикл выборки команды происходит изменение состояния формирователя t псевдослучайных чисел и счетчика 5 на один шаг и информация на выходы 8,13 поступает по шинам из блока 2, а при установке нулевого значения состояния формирователя 1 псевдослучайных чисел и счетчика 5 не изменяются, информация на выходы поступает с второй группы выходов разрядов формирователя псевдослучайных чисел, что может быть интерпретировано соответственно как первое, второе и последующие слова команды в диагностирующую микроэвм.

Через 2 шагов счетчика 5 сигнал с k-ro разряда счетчика поступает на синхровход триггера 6 и переводит его в единичное состояние, что свидетельствует об окончании установочной последов; (- льиости команд и ня- чпле контро. 1Я микроЭВМ.

Разрядность счетчикл 5 определяет ллину последовательности тестовых воздействии, в момент ег о переполнения нулепой сигнал с выхода обратного переноса поступает на вход установки в О триггера 6 и устанавливает его в нулевое состояние, в результате чего сигнал на выходе 15 устройства принимает нулевое значение, что свидетельствует об окончании последовательности тестовых воздействий .

Эффективность использования генератора тестовых воздействиГ для контроля микроэвм определяется не только обеспечением полного перебора команд, но и возможностью генерирования последовательности тестовых воз- действи, содержащей все возможные сочетания по г (г - натуральное число) из п команд, а также сочетания каждой из п команд со всеми наборами данных, что обеспечивает контроль взаимного влияния цепей микропроцессорных больших интегральных схем и элементов микроЭВМ.

Например, д.чя обеспечения попарного сочетания всех команд организация первой и второй групп выходов формирователя псевдослучайных чисел производится путем черезразрядного подключения выходных линиГ разрядов. Так как формирователь псевдослучайных чисел имеет 2 -1 состояни, где k - Количество разрядов формирователя, т.е. на его выходах формируются все кодовые слова, за исключением нулевого (0000 - запрещенное состояние) , то каждое состояние второй группы выходов разрядов (Л, А) будет сочетаться со всеми состояниями первой группы выходов разрядов (Л, , Aj). Таким образом, данный код AjAj адреса команды будет встречаться с полным набором данн|)1х. На следующем щаге сдвига информации в генераторе псевдослучайных чисел состояние будет интерпретировано как адре следующей команды и, с.чедовательно, при полном цикле работы формировател псевдослучайных чисел будет обеспече соответственно попарный перебор всех команд. Для обеспечения перебора по 3,4 н т.д. команд необходимо организовать первую и вторую группу выходо

формирователя псевдослучайных чисел путем подключения соответственно выходов каждого 3,4 и т.д. разрядов формирователя псевдослучайных чисел. Использование изобретения позволяет формировать последовательности псевдослучайных тестовых воздействий для микропроцессорных программируемых контроллеров и микроЭВМ. Частота повторения команд в выходной последовательности тестовых воздействий устро 1ства может быть задана путем занесения каждой команды в несколько ячеек в блоке 2 памяти команд в соответствии с заданной вероятностью повторения.

20

Формула изобретения

Генератор тестов, содержащий формирователь псевдослучайных чисел, блок памяти и счетчик, причем син- хровход генератора соединен с первым входом элемента И, вход сброса генератора соединен с входами сброса формирователя псевдослучайных чисел и счетчика, о т л и ч а ю щ и fi с я тем, что, с целью увеличения быстродействия, генератор содержит элемент Н, и коммутатор, причем вход синхронизации генератора соединен с синхровхпдом памяти, выход которого соед11 1ен с первым информационным входом коммутатора, выход которого являетея выходом поля тестового набора генератора, выход признака конца теста которого соединен с выходом триггера, вход сброса которого соединен с выходом заема счетчика, k-й разрядный выход счетчика, где k , N - длина установочной последовательности с учетом конкретного типа заданного тестируемого

объекта, соединен CJ входом синхронизации триггера, информационный вход которого подклю сен к шине единичного потенциала генератора, счетньш вход счетчика соединен с выходом элемента

И и синхровходом формирователя псевдослучайных чисел, первая и вторая группы выходов которого соответственно соединены с адресной группой входов блока памяти и второй группой

информационных входов кoм fyтaтopa, а второй вход элемента И соединен с входом пуска генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

Изобретение может быть использовано в аппаратуре контроля и диагностирования микропроцессорных програм-; мируемых контроллеров и микроЭВМ для выработки псевдослучайных последовательностей тестовых воздействий с заданными свойствами. Цель изобретения - увеличение быстродействия. Генератор тестовых воздействий содержит формирователь 1 псевдослучайных чисел, блок памяти 2, коммутатор 3, элемент И 4, счетчик 5, триггер 6 и резистор 7. При . генерации ; теста обеспечивается перебор всех сочетаний последовательно подаваемых команд тестируемой микроЭВМ из некоторого числа разрешенных команд. Перебор всех сочетаний создает условия для выявления псевдонеустойчивых неисправностей. 1 ил. с (Л

Авторы

Даты

1988-09-15—Публикация

1986-06-11—Подача