Область техники, к которой относится изобретение

Настоящее изобретение в общем относится к технологиям создания одного или нескольких соединительных каналов/линий, используемых в энергонезависимом запоминающем устройстве. Более конкретно, настоящее изобретение в общем относится к технологиям, в соответствии с которыми один или несколько каналов, используемых в энергонезависимом запоминающем устройстве, прокладывают через сквозное отверстие в матрице ячеек памяти, позволяющее получить доступ к нижележащим схемам. Рассмотрены также запоминающие устройства, использующие такие технологии, и способ создания таких сквозных отверстий и соединений в них.

Уровень техники

В технике известно множество типов полупроводниковых запоминающих устройств. Некоторые типы запоминающих устройств являются энергозависимыми и теряют записанную в них информацию в случае выключения питания. Другие типы запоминающих устройств являются энергонезависимыми и сохраняют информацию даже после отключения питания. Устройство флэш-памяти представляет собой один из видов энергонезависимых запоминающих устройств. В общем случае, в устройстве флэш-памяти сохраняют электрический заряд в области накопления заряда в ячейке памяти. В ячейке памяти с плавающим затвором для хранения заряда может быть использован электропроводный плавающий затвор, расположенный между управляющим затвором и каналом полевого транзистора структуры металл-оксид-полупроводник (МОП-транзистор (metal oxide semiconductor field effect transistor (MOSFET))). В ячейке флэш-памяти с ловушкой заряда (charge trap flash (CTF) cell) для сохранения затвора между управляющим затвором и каналом полевого МОП-транзистора может быть использован слой неэлектропроводного материала, такой как пленка нитрида. Пороговое напряжение ячейки флэш-памяти на основе МОП-транзистора можно изменять путем изменения количества заряда, находящегося в области накопления заряда в ячейке, и это пороговое напряжение можно использовать для индикации величины, записанной в этой ячейке.

Одной из архитектур, обычно используемых для устройств флэш-памяти, является логическая архитектура «И-НЕ» (NOT AND (NAND)). В типовой архитектуре И-НЕ две или более ячейки флэш-памяти соединены одна с другой исток к стоку, так что образована цепочка или блок ячеек памяти. Управляющие затворы индивидуальных ячеек соединены с линиями доступа (например, глобальными линиями управления), такими как числовые (словарные) шины. Вентили выбора, например, вентили выбора в цепи истока (select gate source (SGS)), вентили выбора в цепи стока (select gate drain (SGD) и т.п.) могут представлять собой полевые МОП-транзисторы (MOSFET), соединенные с каждым концом цепочки И-НЕ и соединяющие эту цепочку И-НЕ с истоковой шиной на одном конце цепочки и с шиной данных (например, разрядной шиной) на другом конце.

Некоторые устройства флэш-памяти типа И-НЕ содержат пакеты ячеек флэш-памяти, которые могут быть расположены одна над другой в вертикальном направлении (например, в вертикальных цепочках И-НЕ) и, в качестве опции, в трех измерениях (например, в трехмерных цепочках 3D И-НЕ (3D NAND)). В любом случае, такие устройства могут содержать пакет ячеек флэш-памяти, каждая из которых содержит исток, сток и канал, размещенные вертикально, так что эти ячейки расположены одна над другой для образования вертикальной цепочки (блока) И-НЕ. Вертикальная цепочка И-НЕ может быть расположена поверх одного из вентилей выбора (например, вентиля выбора в цепи стока (SGD), вентиля выбора в цепи истока (SGS) и т.п.), а другой вентиль выбора (например, вентиль SGD или вентиль SGS) может быть расположен поверх вертикальной цепочки И-НЕ.

Для удовлетворения потребности в более высокой емкости памяти разработчики и конструкторы запоминающих устройств постоянно прилагают усилия для повышения плотности размещения ячеек памяти, т.е. для увеличения числа ячеек памяти, находящихся в пределах конкретной области кристалла интегральной схемы. Один из способов увеличения плотности размещения ячеек памяти состоит в уменьшении размеров характерных элементов индивидуальных ячеек памяти и тем самым в уменьшении общего размера самих ячеек памяти. Хотя такой подход способен увеличить число ячеек памяти, которые можно разметить в некой конкретной области, уменьшение размеров элементов ячеек памяти может увеличить риск выхода устройства из строя и утечки заряда. Другой механизм увеличения плотности размещения ячеек памяти состоит в том, чтобы формировать вертикальные цепочки И-НЕ, как это отмечено выше. В таких случаях плотность размещения ячеек памяти может быть практически ограничена соображениями относительно размеров блока, которые могут возникать при проектировании, могут быть указаны в стандарте или могут представлять собой сочетание этих факторов. Подобно традиционным (например, планарным) устройствам типа И-НЕ плотность компоновки устройств И-НЕ вертикального типа может быть увеличена путем уменьшения размеров характерных элементов ячеек памяти в каждой вертикальной цепочке типа И-НЕ.

В любом случае увеличение плотности размещения ячеек памяти в матрице ячеек памяти типа И-НЕ может вызвать проблемы с маршрутизацией и созданием соединений разного рода линий доступа (например, числовых (словарных) шин), шин данных (например, разрядных шин) и других (например, истоковых, стоковых и т.п.) линий/каналов, которые могут быть использованы в устройстве. Это особенно справедливо, когда требования проектирования и/или стандарт ограничивают высоту блока в устройстве. Как будет рассмотрено ниже, технологии согласно настоящему изобретению направлены на решение различных аспектов этой проблемы, например, путем создания возможных альтернативных конфигураций соединений для энергонезависимых запоминающих устройств, таких как вертикальные и/или трехмерные (3D) устройства типа И-НЕ.

Краткое описание чертежей

Признаки и преимущества вариантов заявляемого предмета изобретения станут очевидными из последующего подробного описания и ссылок на чертежи, где одинаковые цифровые позиционные обозначения присвоены подобным компонентам и где:

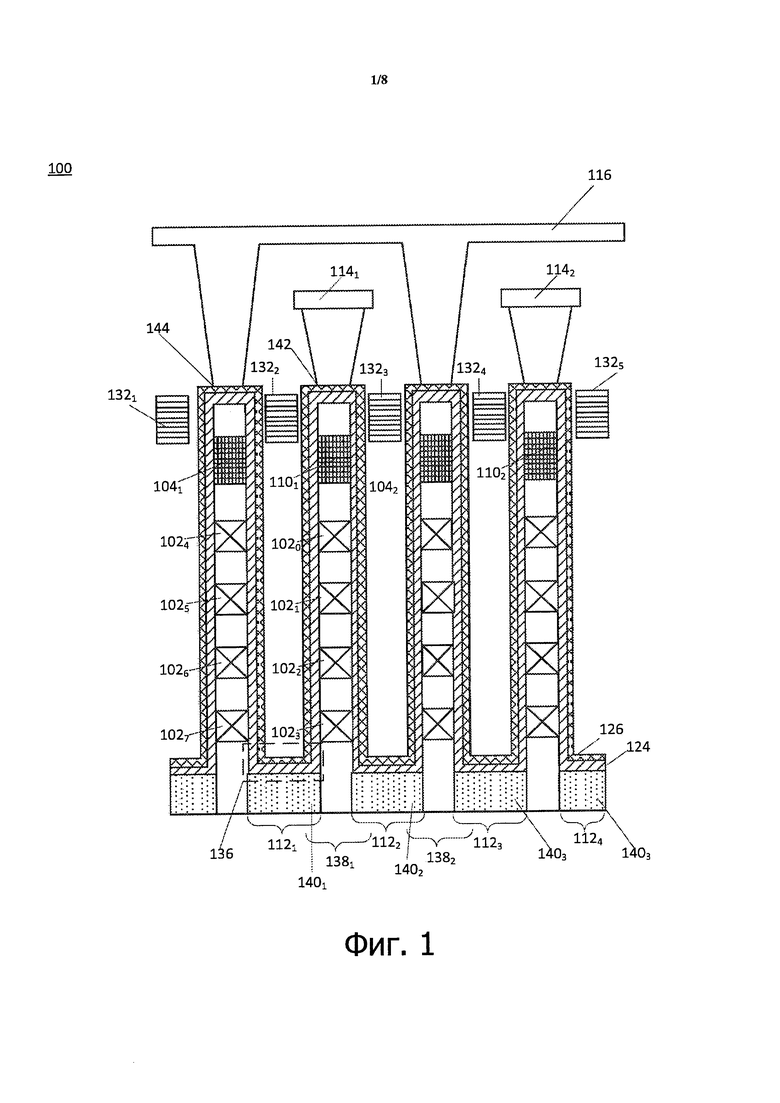

Фиг. 1 иллюстрирует вид в разрезе ячеек памяти в одном примере матрицы ячеек памяти согласно настоящему изобретению.

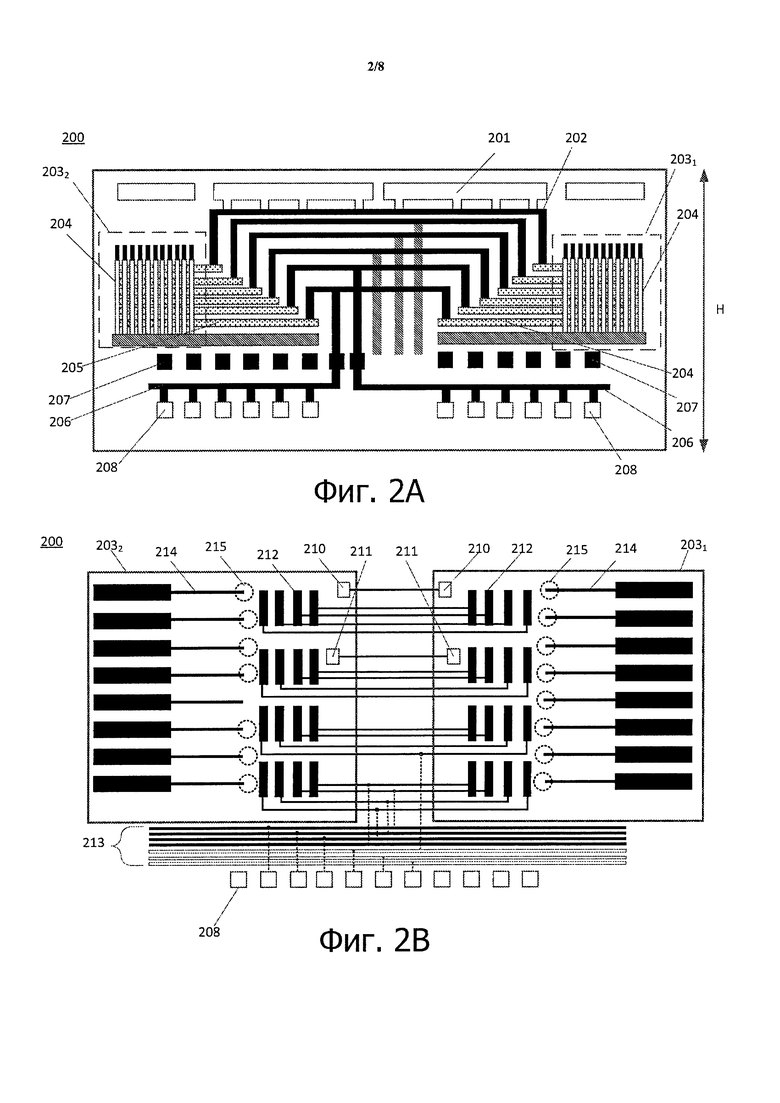

Фиг. 2A представляет один вид примера схемы соединений для матрицы ячеек памяти в энергонезависимом запоминающем устройстве;

Фиг. 2B представляет другой вид примера схемы соединений для матрицы ячеек памяти в энергонезависимом запоминающем устройстве;

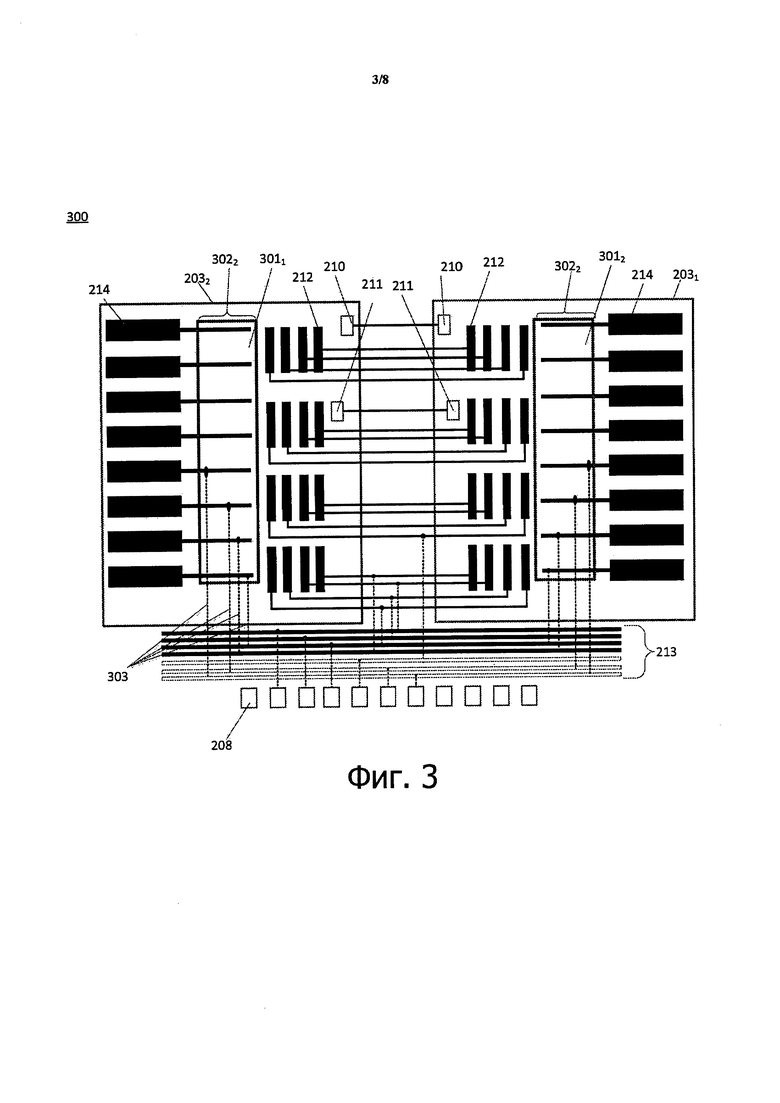

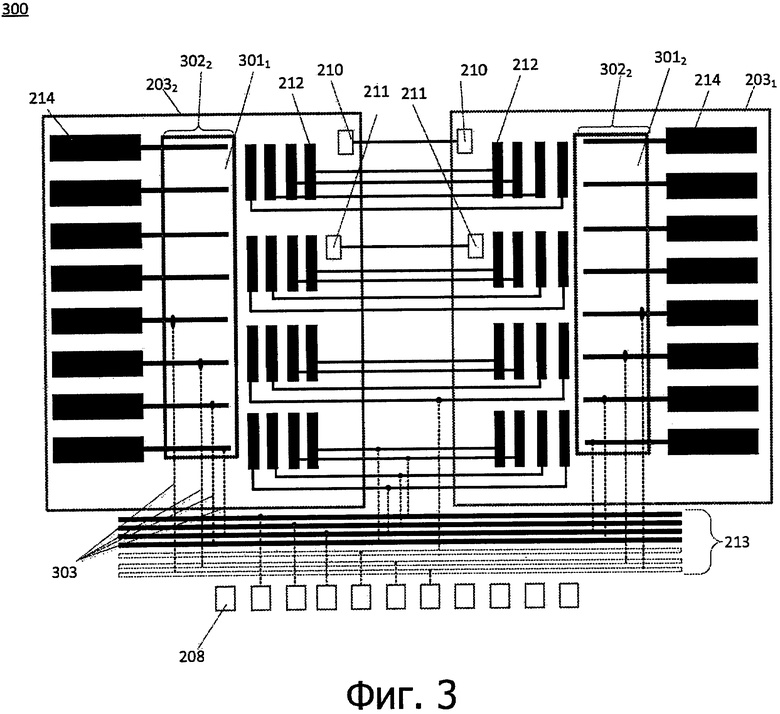

Фиг. 3 представляет пример схемы соединений для матрицы ячеек памяти в энергонезависимом запоминающем устройстве;

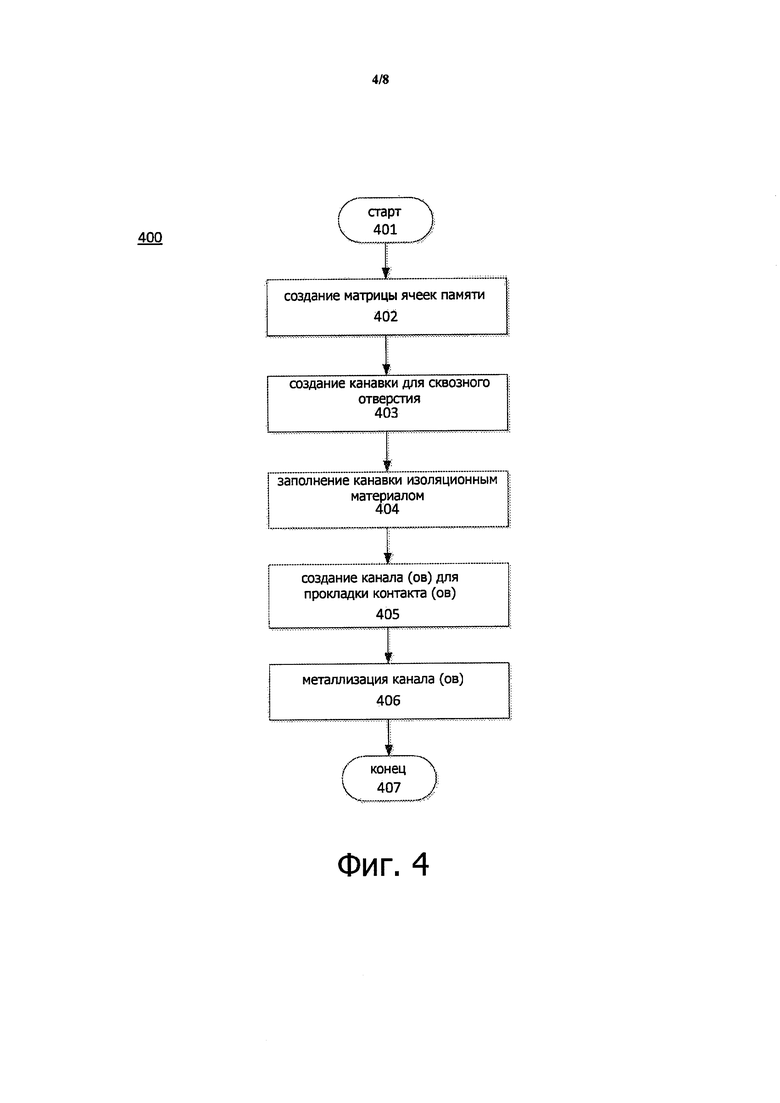

Фиг. 4 представляет логическую схему примера способа формирования проходящего сквозь матрицу ячеек памяти канала согласно настоящему изобретению;

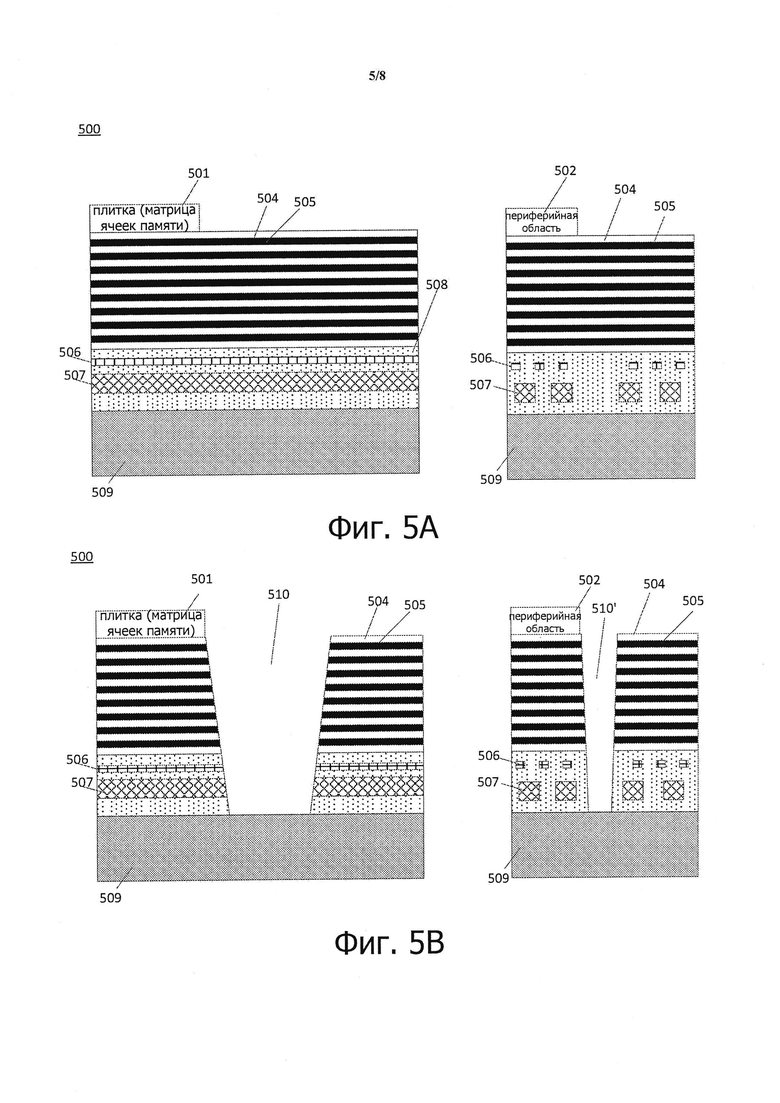

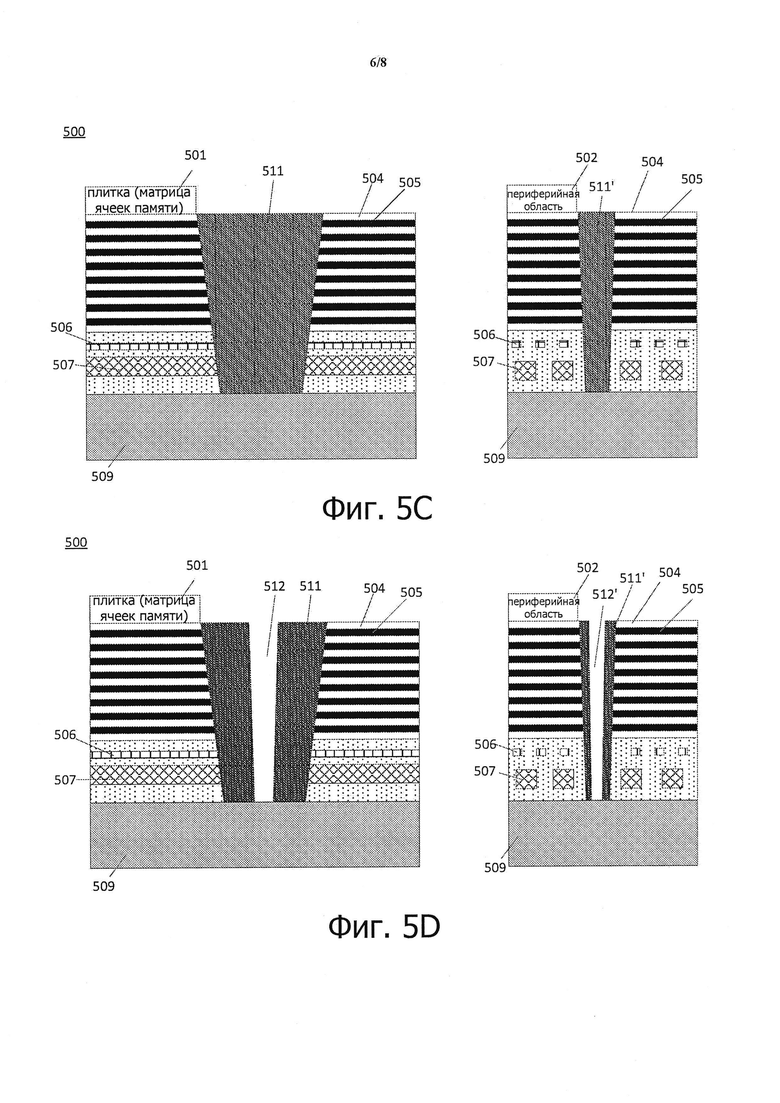

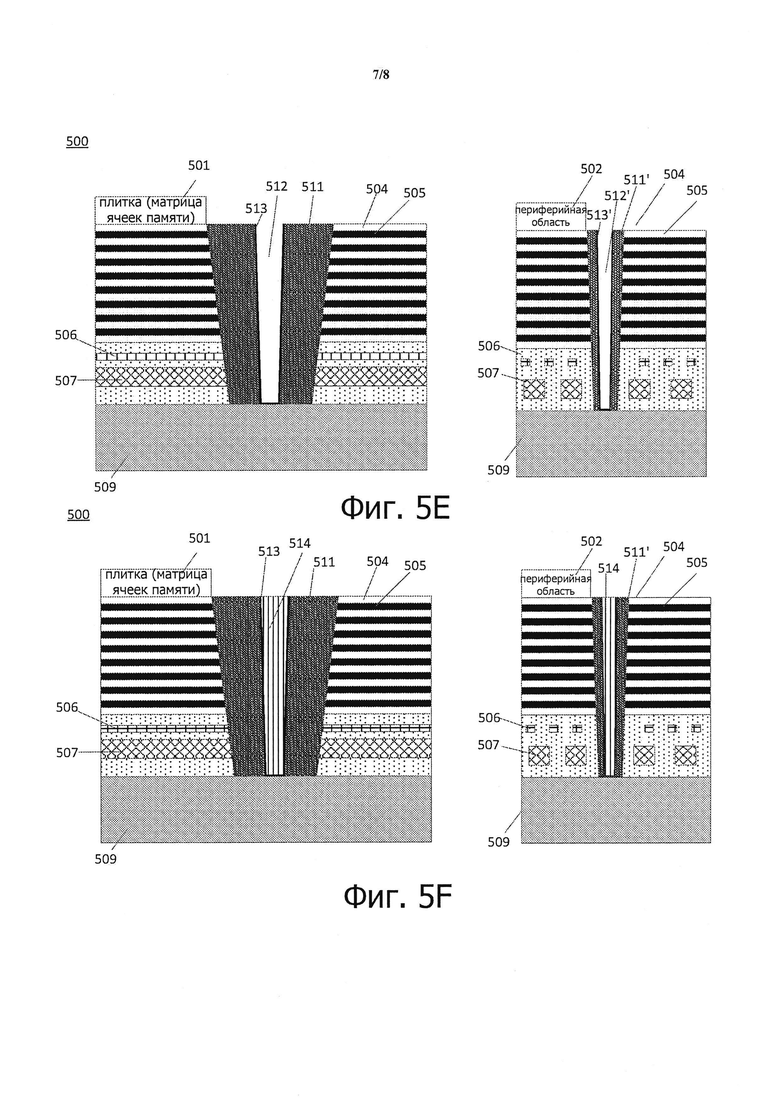

Фиг. 5A-5F представляют пошаговую иллюстрацию одного примера способа формирования проходящего сквозь матрицу ячеек памяти канала согласно настоящему изобретению.

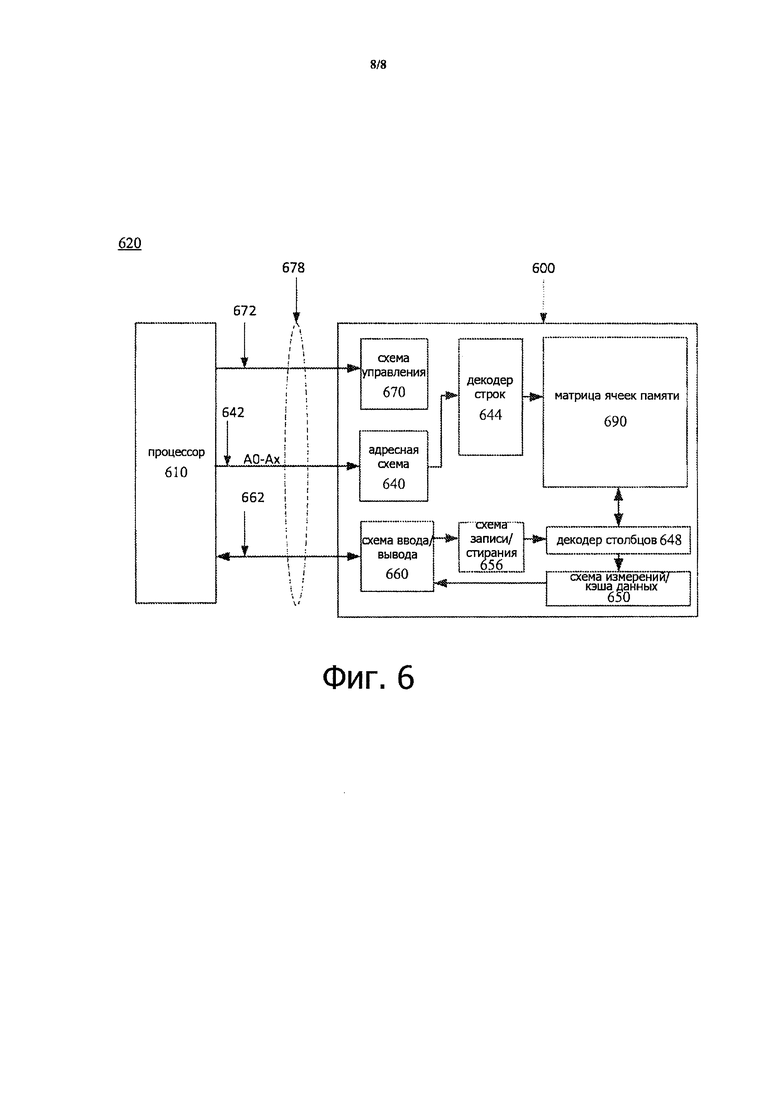

Фиг. 6 представляет упрощенную блок-схему одного примера запоминающего устройства, соединенного с корпусом, в качестве составной части электронной системы согласно настоящему изобретению.

Подробное описание

В последующем описании ссылки сделаны на прилагаемые чертежи, которые составляют часть этого описания и которые иллюстрируют различные примеры вариантов. Здесь подчеркивается, что иллюстрируемые варианты приведены только в качестве примеров, так что можно представить себе и другие варианты, отличные от описываемых здесь, но тем не менее подпадающие под действие настоящего изобретения. Такие другие варианты могут содержать структурные, логические и электрические изменения относительно иллюстрируемых вариантов, которые (изменения) могут быть сделаны, не отклоняясь от объема настоящего изобретения.

В контексте настоящего изобретения термин «полупроводник» следует понимать как обозначающий какую-либо полупроводниковую структуру, включая, но не ограничиваюсь, структуры в форме слоя материала, пластины или подложки. Без ограничений, термин «полупроводник» можно понимать как охватывающий технологию «кремний на сапфире» (silicon on sapphire (SOS)), технологию «кремний на диэлектрике» (silicon on insulator (SOI)), технологию тонкопленочных транзисторов (thin film transistor (TFT)), легированные и нелегированные полупроводники, эпитаксиальные слои кремния на базовой полупроводниковой структуре, другие полупроводниковые структуры, известные специалистам в рассматриваемой области, сочетания таких структур и т.п. Следует также понимать, что когда здесь используется термин «полупроводник», к рассматриваемому моменту уже могли быть выполнены разнообразные технологические операции для формирования областей, переходов и т.п. в структуре полупроводника.

Как используется здесь, прилагательные, указывающие направление, следует понимать как указание направления относительно поверхности подложки, на которой выполнен элемент (например, ячейка памяти). Например, под вертикальной структурой следует понимать структуру, выступающую прочь от поверхности подложки, на которой эта структура выполнена, так что нижний конец структуры находится рядом с поверхностью подложки. Следует также понимать, что вертикальная структура не должна быть обязательно перпендикулярной поверхности подложки, на которой она выполнена, и что к вертикальным структурам относятся также структуры, выступающие наклонно относительно подложки.

Стремление повысить плотность размещения ячеек памяти в энергонезависимом запоминающем устройстве подталкивает разработчиков запоминающих устройств к увеличению числа ячеек памяти, размещенных в пределах конкретной рассматриваемой области. По мере увеличения плотности размещения ячеек памяти становится все труднее прокладывать и выполнять различные линии доступа, шины данных и другие линии и шины, необходимые для работы устройства, без нежелательного неблагоприятного воздействия на характеристики устройства. Хотя можно добавить дополнительные соединительные и маршрутные каналы для энергонезависимого запоминающего устройства, например, выше или ниже матрицы ячеек памяти, для этого может быть необходимо увеличить высоту блока устройства, чтобы разместить такие каналы. В ситуациях, когда высота блока ограничена, например, в соответствии с техническим заданием или другими требованиями к проектированию, увеличение высоты блока может быть недопустимым или может оказаться нежелательным по какой-либо иной причине.

Настоящее изобретение направлено на решение этих проблем путем создания технологий, которые предоставили бы альтернативные механизмы для прокладки одной или нескольких линий доступа, шин данных и других линий и шин, которые могут быть использованы в энергонезависимом запоминающем устройстве. В общем случае, описываемые здесь технологии предлагают альтернативные механизмы для прокладки одной или нескольких шин или линий от контактов/дорожек, находящихся над матрицей ячеек памяти, к одному или нескольким контактам, расположенным ниже матрицы ячеек памяти, таким как контакты драйвера цепочки или другой поддерживающей схемы (например, комплементарной схемы металл-оксид полупроводник (КМОП (CMOS))), которая может быть выполнена посредством технологии «КМОП под матрицей» (CMOS under array (CUA)). Более конкретно, описываемые здесь технологии получают выигрыш от использования одного или нескольких сквозных отверстий, которые могут быть созданы сквозь часть матрицы ячеек памяти, например, в области собственно матрицы ячеек памяти и/или в периферийной области, чтобы обеспечить доступ к областям/схемам, которые могут быть выполнены под матрицей ячеек памяти. В таких сквозных отверстиях могут быть выполнены один или несколько каналов, заполненных электропроводным материалом, чтобы обеспечить электрическое соединение различных линий и шин со схемой, выполненной под матрицей ячеек памяти.

Ссылки теперь будут сделаны на Фиг. 1, которая иллюстрирует вид в разрезе ячеек памяти одного из примеров матрицы ячеек памяти, соответствующей настоящему изобретению. Как показано, матрица 100 ячеек памяти (далее, «матрица 100») содержит несколько ячеек памяти, выполненных в виде совокупности нескольких цепочек 1121…4 ячеек памяти, расположенных в соответствии с конфигурацией И-НЕ. Таким образом, можно понять, что на Фиг. 1 изображены ячейки памяти для одного примера запоминающего устройства типа И-НЕ согласно настоящему изобретению. Как показано, запоминающее устройство 100 содержит вентили 110 выбора в цепи истока ("SGS") и вентили 104 выбора в цепи стока ("SGD"), каждый из которых соединен с одной из цепочек 1121…4 ячеек памяти. Вентилем SGS 110 можно управлять посредством шины управления SGS, а вентилем SGD 104 можно управлять посредством шины управления SGD (не показано). В общем случае, вентиль SGD 104 и вентиль SGS 110 могут получать напряжение смещения во время выполнения одной или нескольких операций с запоминающим устройством 100 (например, операции считывания, операции записи, операции стирания и т.п.) с целью активизации и деактивации ячеек памяти или цепочек (блоков) таких ячеек во время выполнения указанных операций по отдельности или в сочетании с управляемым смещением вентиля 132 выбора цепочки, что будет описано ниже.

Цепочки 1121…4 в этом варианте выполнены в виде свернутой структуры, так что первая часть каждой цепочки расположена вдоль первого столбца 1381, а вторая часть этой же цепочки расположена вдоль соседнего (например, второго) столбца 1382. В этом смысле можно понимать, что «столбцы» 1381, 1382 охватывают цепочки ячеек памяти организованных в виде цепочки типа И-НЕ.

Цепочки 1121…4 построены в свернутой (например, U-образной) конфигурации и могут содержать несколько (например, 8, 16, 32 и т.д.) ячеек памяти. В качестве примера, каждая из цепочек 1121…4 может содержать восемь (8) ячеек памяти, где четыре ячейки памяти выполнены вдоль одного вертикального столбца (например, столбца 1121) и четыре ячейки памяти выполнены вдоль соседнего столбца ячеек памяти (например, столбца 1122), образуя тем самым U-образную структуру. Запоминающие устройства типа И-НЕ согласно настоящему изобретению могут содержать две или более таких U-образных цепочек, выполненных одна рядом с другой. Запоминающее устройство 100 может также содержать вентиль 132 выбора цепочки (string select gate (SSG)), который может быть выполнен между концами каждой из цепочек 1121…4.

Как далее показано на Фиг. 1, в разнообразных вариантах цепочки 1121…4 могут быть присоединены между шиной 116 данных (например, разрядной шиной) и двумя истоковыми шинами 1141,2, например, в контактных точках 144 разрядных шин и в контактных точках 142 истоковых шин. Соединением цепочки с разрядной шиной можно управлять посредством вентиля SSG 132, который может быть выполнен из электропроводного материала, такого как поликристаллический кремний. В общем случае, вентиль SSG 132 может получать смещение (быть активизирован) для соединения и/или разъединения первого конца выбранной цепочки 1121…4 с шиной 116 данных (разрядной шиной) и другого конца выбранной цепочки с истоковой шины 1141,2.

Следует понимать, что на Фиг. 1 показана только часть запоминающего устройства 100 и цепочек (блоков) 1121…4, и что энергонезависимые запоминающие устройства согласно настоящему изобретению не ограничиваются показанной конфигурацией. Действительно, запоминающее устройство 100 может содержать матрицу ячеек памяти, в состав которой входят больше или меньше цепочек (блоков) И-НЕ, чем это показано на Фиг. 1 в виде цепочек 1121…4. Более того, каждая цепочка может содержать больше или меньше, чем восемь ячеек памяти, какие-либо или все из которых могут быть соединены числовыми (словарными) шинами 1020…7 или другими числовыми шинами (не показаны). Например, в каждой из цепочек 1121…4 и/или в одной или нескольких дополнительных цепочках могут располагаться структуры дополнительных ячеек памяти. Такие дополнительные ячейки памяти могут содержать активные или неактивные (холостые) ячейки памяти, такие как описанные в заявке, опубликованной через 18 месяцев после даты приоритета (U.S. Pre-Grant Publication No. 2009/0168519). Действительно, в некоторых вариантах запоминающие устройства, описываемые здесь, могут представлять собой запоминающее устройство типа И-НЕ, которое содержит матрицу ячеек памяти, имеющую в составе 2n ячеек памяти, где n - целое число.

Как далее показано на Фиг. 1, запоминающее устройство 100 может дополнительно содержать структуру 124 для накопления и хранения заряда и канальную структуру 126. Структура 124 для накопления и хранения заряда может иметь форму одного или несколько непрерывных слоев, проходящих сквозь цепочки 1121…4 ячеек памяти, как показано. В некоторых вариантах, структура 124 для накопления и хранения заряда может содержать первый оксидный слой, слой нитрида поверх этого первого оксидного слоя и второй оксидный слой поверх слоя нитрида (все не показаны). Запоминающее устройство 100 может также содержать плоские затворы, которые на Фиг. 1 показаны, как несколько управляющих затворов 1401…4, каждый из которых может быть выполнен под цепочкой 1121…4 ячеек памяти. Без ограничений, управляющие затворы 1401…4 могут составлять часть схемы под матрицей ячеек 1121…4 памяти, которая может быть использована для управления цепочками 1121…4 ячеек памяти. Соответственно, управляющие затворы 1401…4 могут составлять часть драйверов числовых шин, которые могут быть выполнены под цепочками 1121…4 ячеек памяти и которые могут быть изготовлены по какой-либо подходящей технологии, такой как технология «КМОП под матрицей».

Хотя это не показано на чертежах, ячейки памяти запоминающего устройства 200 могут быть расположены в виде объемной трехмерной структуры (3D), так что они образуют 3D-матрицу ячеек памяти. Например, вентили SGS 1101-2, SGD 1041-2 и вентили 1321…5 выбора цепочки ("SSG") могут быть повторены как сзади (например, ниже), так и спереди (например, выше) относительно плоскости, показанной на Фиг. 1. Шины управления для таких вентилей также проходить перед или ниже плоскости, показанной на Фиг. 1. Более конкретно, можно понимать в таких вариантах, что числовые шины 1020…7 (в совокупность которых, могут входить линии доступа и локально структуры управляющих затворов каждой ячейки памяти) входят в и выходят из плоскости матрицы ячеек памяти из состава запоминающего устройства 100. Аналогично, вентили SGD 1041,2 SGS 1101-2 и SSG 1321…5 (каждый из которых может функционировать в качестве управляющей структуры локально в каждой цепочке 1121…4) могут также содержать шину сигнала управления, проходящую сквозь плоскость Фиг. 1. Плоский затвор (например, управляющие затворы 1401…4) может быть также повторен в трехмерной 3D-матрице.

Следует отметить, что целью Фиг. 1 является иллюстрация одной из конфигураций матрицы ячеек памяти типа И-НЕ, которая может быть использована согласно настоящему изобретению. Следует понимать, что настоящее изобретение предполагает использование различных видов энергонезависимых запоминающих устройств, включая запоминающее устройство типа И-НЕ, конфигурированное способом, отличным от запоминающего устройства 100, показанного на Фиг. 1, равно как и запоминающее устройство с архитектурой ИЛИ-НЕ (NOR). В любом случае, дополнительная информация относительно запоминающего устройства 100 и способов изготовления такого запоминающего устройства может быть найдена в патенте США No. 8,681,555, все содержание которого включено сюда посредством ссылки во всей своей полноте.

На Фиг. 2A и 2B, где приведены различные виды схемы прокладки линий доступа в матрице ячеек памяти для энергонезависимого запоминающего устройства согласно настоящему изобретению. Как применяется здесь, термины «линия доступа», «шины управления» и маршрутная линия используются взаимозаменяемо для обозначения линий и шин, которые могут быть использованы для передачи сигналов к и от одного или нескольких компонентов энергонезависимого запоминающего устройства. Линии доступа/управления могут поэтому представлять собой линии/каналы, которые могут быть использованы для передачи сигналов к и от одного или нескольким вентилей (например, вентилей выбора в цепи истока, вентилей выбора в цепи стока и т.п.), одну или несколько числовых (словарных) шин, могут входить в состав одной или нескольких ячеек памяти, драйверных схем, сочетаний таких схем и т.п., которые могут быть применены в энергонезависимом запоминающем устройстве. Как можно ожидать, линии доступа могут быть проложены через один или несколько каналов, созданных в энергонезависимом запоминающем устройстве.

Следует также отметить, что в целях иллюстрации схемы соединений, приведенные на Фиг. 2A и 2B, показывают пример, где энергонезависимое запоминающее устройство содержит несколько матриц ячеек памяти («плиток»), имеющих в составе цепочки (блоки) ячеек памяти, которыми могут управлять расположенные под ними драйверные схемы, совместно используемые каждой матрицей ячеек памяти. При таком подходе можно понимать, что на Фиг. 2A и 2B показаны разные виды схемы соединений для энергонезависимого запоминающего устройства (например, вертикального запоминающего устройства типа И-НЕ), использующего архитектуру с общим драйвером числовых (словарных) шин, который может быть создан под соответствующими матрицами ячеек памяти с применением технологии CUA. Одной из целей Фиг. 2A и 2B является иллюстрация различных проблем, с которыми можно столкнуться при прокладке различных линий доступа, шин данных и т.п., какие могут быть использованы в таком устройстве. Следует подчеркнуть, что такая иллюстрация является всего лишь примером, и что описываемые здесь технологии могут быть использованы в любом подходящем энергонезависимом запоминающем устройстве.

Как показано на Фиг. 2A и B, запоминающее устройство 200 может содержать несколько матриц ячеек памяти («плиток»). Эту концепцию иллюстрирует Фиг. 2, где показано запоминающее устройство 200, содержащее первую матрицу 2031 ячеек памяти (плитку) и вторую матрицу (плитку) 2032 ячеек памяти. Каждая матрица (плитка) 2031, 2032 ячеек памяти может быть в форме вертикальной матрицы ячеек памяти, такой, какая может быть использована в вертикальной или трехмерной (3D) архитектуре И-НЕ. В такой структуре каждая матрица 2031, 2032 ячеек памяти может содержать и/или может быть соединена с несколькими соответствующими каналами 204, к каждому из которых можно обращаться и получать доступ или управлять с использованием одного или нескольких электродов 205 линий доступа (числовых шин). Электроды 205 числовых шин могут быть соединены с электропроводными (например, из металла или поликристаллического кремния и т.п.) каналами (соединительные линии) 202, которые в свою очередь могут быть соединены с электропроводными соединениями 201, расположенными в области над матрицами 2031,2 ячеек памяти. Для облегчения создания соединений и прокладки электропроводных каналов (линий) 202 электроды 205 числовых (словарных) шин могут быть выполнены в виде многоярусной структуры, как показано на Фиг. 2A. Электропроводные каналы 202 могут также соединять электроды 205 числовых шин с одной или несколькими линиями доступа (числовыми шинами) и управления, например, через контакты 212 числовых (словарных) шин.

Описанную выше концепцию иллюстрирует Фиг. 2A, где показаны электропроводные линии 202 в виде соединений с первыми числовыми управляющими шинами 206 и/или вторыми числовыми управляющими шинами 207, которые в этом случае расположены в области под матрицами 2031,2 ячеек памяти. Запоминающее устройство 200 может также содержать соединительные элементы 209, которые могут быть выполнены из электропроводного материала и могут служить для электрического соединения двух или более электропроводных линий 202 и/или других компонентов запоминающего устройства 200 одного с другим.

Первые и/или вторые числовые управляющие шины 206, 207 могут быть соединены с драйверной схемой 208, как показано на Фиг. 2A и B. Как описано выше, драйверная схема 208 может совместно использоваться матрицами 2031,2 ячеек памяти и может служить для управления цепочками (блоками) ячеек памяти. Драйверная схема 208 может быть поэтому в некоторых вариантах конфигурирована в форме общей драйверной архитектуры для числовых (словарных) шин, которая, например, может быть создана под матрицами 2031,2 ячеек памяти посредством технологии CUA или каким-либо другим подходящим способом. Как показано на Фиг. 2B, первые и/или вторые числовые управляющие шины 206, 207 могут содержать, быть в форме и/или соединяться с соединительными каналами 213 схемы, которые могут быть электропроводными линиями (например, из металла, поликристаллического кремния или другого подобного материала, либо с содержанием электропроводного материала), обеспечивающими электрический контакт с драйверной схемой 208.

Как показано также на Фиг. 2B, запоминающее устройство 200 может содержать истоковые каналы 210, линии 211 вентилей SGS и линии 214 вентилей SGD. Истоковые каналы 210 могут быть выполнены из или содержать одну или несколько линий, имеющих в составе электропроводный материал, (например, металл, поликристаллический кремний и т.п.) и могут служить для соединения соответствующих вентилей SGS и SGD с драйверными схемами 208 или другими подходящими компонентами.

Как можно видеть на Фиг. 2A и 2B, разнообразные линии, шины и каналы, используемые в запоминающем устройстве 200, могут быть проложены в пределах высоты Н блока. В иллюстрируемых вариантах, например, числовые шины 206, 207, истоковые шины 210, линии 211 вентилей SGS и линии 214 вентилей SGD могут быть соединены с электропроводными линиями 202 и/или соединениями 209, некоторые или все из которых могут быть проложены к драйверной схеме 208. Более конкретно одна или несколько линий доступа могут быть проложены выше или ниже матриц 2031,2 ячеек памяти, т.е. в пределах высоты H блока в запоминающем устройстве 200. Хотя прокладка линий таким способом может быть эффективной, поскольку плотность размещения ячеек памяти увеличивается, могут потребоваться дополнительные линии доступа. Прокладка дополнительных линий доступа может быть затруднена или вообще невозможна, если высота Н блока ограничена, например, из-за требований к проектированию и/или норм стандарта, которые регламентируют максимальную высоту блока. Эту концепцию иллюстрирует Фиг. 2B, на котором показано, что линии 214 вентилей SGD не имеют соединения с драйверной схемой 213, например, в области 215. Как указано выше, линии 214 вентилей SGD могут быть проложены выше или ниже матриц 2031 или 2032 ячеек памяти, но для этого может потребоваться увеличить высоту H блока, что может оказаться нежелательным.

Обратимся теперь к Фиг. 3, где представлена альтернативная схема соединений для энергонезависимого запоминающего устройства согласно настоящему изобретению. Как показано на чертеже, запоминающее устройство 300 содержит много таких же компонентов, как и запоминающее устройство 200, показанное на Фиг. 2A и B. Когда природа и функции элементов, показанных на Фиг. 3, являются такими же, как функции и природа элементов, представленных на Фиг. 2A и B, такие элементы здесь, для краткости, повторно описаны не будут. С этой точки зрения запоминающее устройство 300 отличается от запоминающего устройства 200 тем, что оно содержит области 3011, 3012 сквозных отверстий в матрице, которые могут быть выполнены в соответствующих участках 3021, 3022 запоминающего устройства 300. В некоторых вариантов один или оба участка 3021, 3022 могут соответствовать области матрицы ячеек памяти в составе запоминающего устройства 300, т.е. области запоминающего устройства по меньшей мере частично занятой матрицей ячеек памяти, например, матрицей 2031, 2032 ячеек памяти, показанной на Фиг. 2A (не показана на Фиг. 3). В качестве альтернативы, один или оба участка 3021, 3022 могут соответствовать периферийной области запоминающего устройства 300, т.е. области запоминающего устройства 300, которая может быть создана вне и/или вокруг области матрицы ячеек памяти. В некоторых вариантах энергонезависимое запоминающее устройство может иметь общую площадь A, а термин «область матрицы ячеек памяти» может относиться к области, занятой матрицей ячеек памяти, в пределах этой области A. В таких случаях термин «периферийная область» может относиться к области в пределах площади A, которая (область) находится вне области матрицы ячеек памяти и которая может проходить от края области матрицы ячеек памяти на расстояние около 30% (например, примерно 25%, примерно 20%, примерно 15%) размера площади A. В некоторых вариантах периферийная область энергонезависимого запоминающего устройства имеет протяженность от некоторой величины больше 0 до примерно 25% общей площади A запоминающего устройства.

Без ограничений, в некоторых вариантах один или оба участка 3021, 3022 соответствуют периферийной области запоминающего устройства 300. В любом случае один или несколько сквозных каналов 303 могут быть выполнены в областях 3011, 3022 сквозных отверстий для соединения одного или нескольких каналов и соответствующих линий доступа запоминающего устройства с драйверной схемой 208. Например, в иллюстрируемом варианте линии 214 вентилей SGD могут быть соединены с драйверной схемой 208 или с другими компонентами запоминающего устройства 300 через сквозные каналы 303.

Следует отметить, что в целях иллюстрации и облегчения понимания на Фиг. 3 показана схема соединений, в которой линии 214 вентилей SGD могут быть соединены с драйверной схемой 208 или другими компонентами запоминающего устройства 300 посредством сквозных каналов 303. Необходимо подчеркнуть, что этот пример является только иллюстрацией, так что одна, все или какое-либо сочетание линий доступа для запоминающего устройства 300 (или 200) могут быть соединены с соответствующими компонентами посредством одного или нескольких сквозных каналов 303, выполненных через участки 3021, 3022 сквозных отверстий. Действительно, в некоторых вариантах один или несколько сквозных каналов 303 могут быть использованы для прокладки линий 214 вентилей SGD, соединительных каналов 213 схемы, линии 211 вентилей SGS, истоковых каналов 210, числовых управляющих шин 206, 207, сочетаний этих элементов и т.п. к соответствующим компонентам запоминающего устройства 300.

Как можно понять, прокладка различных линий доступа в энергонезависимом запоминающем устройстве с применением сквозных каналов 303 может позволить обойти пакет электродов числовых шин, который может быть использован в запоминающем устройстве 300, такой как, без ограничений, многоярусный пакет электродов 205 числовых шин в запоминающем устройстве 200, показанном на Фиг. 2B. Это может позволить осуществить доступ к драйверной схеме 208 и/или проложить дополнительные линии доступа без необходимости увеличения высоты H блока и, потенциально, без необходимости создавать и использовать дополнительные соединения для прокладки их вокруг других компонентов запоминающего устройства. Более конкретно использование сквозных отверстий 303, проходящих через матрицу ячеек памяти, открывает широкую дорогу к разнообразным альтернативным схемам соединений, которые могут обладать одним или несколькими преимуществами относительно других схем соединений, опирающихся на прокладку различных каналов выше и/или ниже матрицы ячеек памяти.

Следует снова отметить, что на Фиг. 2A, 2B и 3 показаны схемы прокладки соединений, которые могут быть конфигурированы для использования в энергонезависимом запоминающем устройстве, имеющем специальную конфигурацию матрицы ячеек памяти, топологию и расположенную под матрицей драйверную схему. Следует снова подчеркнуть, что такие иллюстрации предназначены служить только в качестве примеров и что технологии, описываемые здесь, могут быть использованы для того, чтобы позволить применить альтернативные технологии прокладки и создания соединений в самом широком спектре различных конфигураций энергонезависимых запоминающих устройств, включая, но не ограничиваясь, вертикальные и трехмерные (3D) конфигурации типа И-НЕ. Действительно, настоящее изобретение следует толковать как в широком смысле относящееся к использованию проходящих через матрицу ячеек памяти каналов/линий и ассоциированных с ними сквозных отверстий для осуществления функций прокладки и создания соединений в энергонезависимых запоминающих устройствах какого-либо подходящего типа.

Поэтому в некоторых вариантах настоящее изобретение относится к запоминающему устройству типа И-НЕ, содержащему область собственно матрицы ячеек памяти и область периферийных схем, где по меньшей мере одна матрица ячеек памяти, составленная из вертикальных цепочек ячеек памяти (например, вертикальных и/или трехмерных (3D) типа И-НЕ), выполнена в области собственно матрицы ячеек памяти и над драйверной схемой (например, драйверной схемой для цепочки) по меньшей мере для одной матрицы ячеек памяти, где это энергонезависимое запоминающее устройство содержит по меньшей мере одну область сквозных отверстий, проходящих через матрицу ячеек памяти, в которой имеется по меньшей мере один канал сквозь матрицу, конфигурированный для электрического соединения по меньшей мере одной линии доступа с драйверной схемой или с другим подходящим компонентом запоминающего устройстве. В этом контексте термин линия «доступа» означает одну или несколько шин управления (для вентилей SGS, SGD), истоковых шин, стоковых шин, числовых (словарных) шин и т.п., которые могут быть использованы в энергонезависимом запоминающем устройстве.

С учетом вышеизложенного другой аспект настоящего изобретения относится к проходящим сквозь матрицу ячеек памяти каналам в энергонезависимом запоминающем устройстве и к способам изготовления таких каналов. С этой целью ссылки теперь будут сделаны на Фиг. 4, где представлена логическая схема последовательности операций, которые могут быть выполнены в соответствии с одним из примеров способа создания проходящего сквозь матрицу ячеек памяти канала согласно настоящему изобретению. Для большей ясности и иллюстративности операции, показанные на Фиг. 4, будут описаны в сочетании с Фиг. 5А-5F, которые поэтапно иллюстрируют формирование примера проходящего сквозь матрицу ячеек памяти канала согласно настоящему изобретению в области собственно матрицы ячеек памяти и в периферийной области устройства типа И-НЕ. Хотя настоящее описание сосредоточено только на формировании сквозного отверстия через матрицу ячеек памяти, следует понимать, что сквозные отверстия через матрицу ячеек памяти согласно настоящему изобретению могут быть созданы до, после или во время формирования других компонентов энергонезависимого запоминающего устройства, включая одну или несколько матриц ячеек памяти, управляющие затворы, истоки, стоки, линии доступа и т.п. Без ограничений, проходящие сквозь матрицу ячеек памяти каналы согласно настоящему изобретению предпочтительно формируют в ходе выполнения других технологических операций, которые могут быть использованы для создания других компонентов энергонезависимого запоминающего устройства, например, с целью избежать или ограничить необходимость в дополнительных или других операциях маскирования, осаждения, очистки или других технологических операциях.

Как показано на Фиг. 4, способ 400 начинается с блока 401. После этого выполнение способа переходит к блоку 402, в котором может быть выполнена матрица ячеек памяти из состава энергонезависимого запоминающего устройства, например, на пластине или другом объекте. Эта матрица ячеек памяти может содержать область собственно матрицы ячеек памяти и периферийную область, как описано выше. Эту концепцию иллюстрирует Фиг. 5A, на котором показана область 501 собственно матрицы ячеек памяти и периферийная область 502 для части матрицы 500 ячеек памяти. Как показано, область 501 собственно матрицы ячеек памяти и периферийная область 502 могут содержать чередующиеся диэлектрические слои 504 и электропроводные слои 505. Диэлектрические слои 504 могут быть выполнены из или содержать какой-либо подходящий диэлектрический материал, включая, но, не ограничиваясь, диэлектрические нитриды и диэлектрические оксиды, такие как оксид кремния (SiOx) и оксид алюминия. Аналогично, электропроводные слои 505 могут быть выполнены из или содержать какой-либо подходящий электропроводный материал, такой как, но, не ограничиваясь, поликристаллический кремний, один или несколько металлов и/или нитридов металлов, таких как нитрид титана, сочетания этих материалов и т.п. Чередующиеся диэлектрические и электропроводные слои 504, 505 могут быть выращены или осаждены на изоляционный слой 508, который сам может быть выращен или осажден на или поверх структуры 509.

Изоляционный слой 508 может быть выполнен из или содержать диэлектрический и/или изоляционный оксидный материал, такой как, но не ограничиваясь, оксид кремния. Как показано на Фиг. 5A, одна или несколько соединительных линий, таких как первые и вторые соединительные линии 506, 507, могут быть выполнены в изоляционном слое 508. Эти первые и вторые соединительные линии могут представлять собой любые подходящие соединительные линии, которые могут быть использованы в энергонезависимом запоминающем устройстве, такие как один или несколько истоковых каналов, каналов для числовых (словарных) шин, линий для вентилей SGS, линий для вентилей SGD и т.п. Безусловно, согласно настоящему изобретению соединительные линии 506, 507 могут быть опущены, например, в тех случаях, когда такие линии могут быть проложены через другие участки матрицы 500 ячеек памяти, например, с использованием сквозных каналов согласно настоящему изобретению. Однако, в качестве примера, соединительные линии 506, 507 показаны в изоляционном слое 508 для иллюстрации, как эти проходящие через матрицу сквозные каналы, описываемые здесь, могут быть созданы таким образом, чтобы избежать помех и препятствий с соединительными линиями и другими компонентами в изоляционном слое 508 или в какой-либо другой части матрицы 500 ячеек памяти. Как будет обсуждаться позднее, проходящие сквозь матрицу каналы, описываемые здесь, предпочтительно формируют таким образом, чтобы они были изолированы от или по-другому избегали контактов с соединительными линиями и/или другими компонентами, которые могут присутствовать в составе матрицы 500 ячеек памяти, такие как, но, не ограничиваясь, соединительными линиями 506, 507, каковые могут находиться в слое 508.

Структура 509 может представлять собой электропроводную подложку или другую структуру (например, контактную площадку, электропроводную линию и т.п.), которая может служить для электрического соединения проходящего сквозь матрицу канала согласно настоящему изобретению с другим компонентом энергонезависимого запоминающего устройства, таким как драйверная схема, которая может быть выполнена под матрицей 500 ячеек памяти, например, посредством технологии CUA, как описано выше. С этой точки зрения, для формирования структуры 509 может быть использован любой подходящий электропроводный материал, включая, но, не ограничиваясь, металлы, такие как вольфрам, медь и алюминий, равно как другие электропроводные материалы, такие как поликристаллический кремний. Без ограничений, структура 509 предпочтительно выполнена в форме контактной площадки или электропроводной линии, которая создана из металла, такого как вольфрам.

Возвращаясь к Фиг. 4, способ может перейти к блоку 403, когда в матрице ячеек памяти могут быть выполнены одна или несколько канавок. Эту концепцию иллюстрирует Фиг. 5B, где показано формирование канавок 510, 510' в области 501 собственно матрицы ячеек памяти и в периферийной области 502 матрицы 500 ячеек памяти, соответственно. Канавки 510, 510' могут быть выполнены посредством какого-либо подходящего процесса, известного в технике, такого как, не ограничиваясь этим, влажное химическое травление, сухое травление, фотолитография, сочетание этих процессов и других подобных процессов. Без ограничений, одна или несколько канавок 510, 510' могут быть предпочтительно сформированы с применением сухого травления, такого как процесс сухого травления канавок с большим коэффициентом формы (high aspect ratio trench (HART)). Процессы сухого травления HART хорошо известны в технике, вследствие чего подробное описание такого процесса здесь приведено не будет. В некоторых вариантах процесс сухого травления HART может использовать «сухой» травитель, который может агрессивно травить материалы диэлектрических слоев 504 (например, SiOx), электропроводных слоев 505 (например, поликристаллический кремний), слоев 508 (например, SiOx) и (в качестве опции) соединительные линии 506, 507, но могут не травить или могут травить не агрессивно материал структуры 509 (например, металлы, такие как вольфрам). В качестве результата, процесс сухого травления может создать канавку, проходящую от верхней поверхности области 501 матрицы ячеек памяти и периферийной области 502 к структуре 509. Канавки 510, 510' могут поэтому обеспечить доступ к структуре 509.

Следует отметить, что в целях иллюстрации на Фиг. 5B-5F поэтапно показан вариант, где и в области собственно матрицы ячеек памяти, и в периферийной области энергонезависимого запоминающего устройства создана только одна канавка, в которой выполнен один канал. Следует понимать, что такой вариант является только одним, но не ограничивающим, примером настоящего изобретения, и что описываемые здесь технологии могут быть использованы для создания одной или нескольких канавок только в области собственно матрицы ячеек памяти, только в периферийной области матрицы ячеек памяти, и в области собственно матрицы ячеек памяти, и в периферийной области такой матрицы и/или в одной или нескольких периферийных областей и областей матриц ячеек памяти, равно как в каких-либо другой области матрицы ячеек памяти или энергонезависимого запоминающего устройства, содержащего такую матрицу ячеек памяти. Поэтому, в некоторых вариантах энергонезависимое запоминающее устройство, описываемое здесь, может содержать матрицу ячеек памяти, имеющую периферийную область и область собственно матрицы ячеек памяти, где одна или несколько (например, 2, 3, 4, 5, 6 и т.д.) канавок могут быть созданы по меньшей мере в одной из областей - периферийной области и/или области собственно матрицы ячеек памяти, и в качестве опции, в другой области матрицы или устройства, содержащего такую матрицу ячеек памяти. Более того, каждая канавка может быть в последующем обработана для создания одного или нескольких каналов, проходящих сквозь матрицу ячеек памяти.

На Фиг. 5B-5F показаны канавки 510, 510', имеющие конусообразную структуру, так что размер (например, ширина) в области дна канавки меньше соответствующего размера возле верхнего края канавки. В такой конфигурации можно понять, что канавки 510, 510' имеют наклонные боковые стенки. Величина наклона боковых стенок канавок 510, 510' может изменяться в широких пределах и может диктоваться конструкторскими и/или технологическими ограничениями. Без ограничений, наклон одной или обеих боковых стенок канавок 510, 510' может быть в пределах от примерно 85 до примерно 90 градусов относительно плоскости верхней поверхности структуры 509, таким как примерно 87-89 градусов или даже примерно 88-89 градусов. Как можно понимать, наклон боковых стенок канавок 510, 510' может быть выбран таким образом, чтобы обеспечить нужный уровень электрической изоляции между электропроводными материалами, которые могут быть помещены в канавки 510, 510' (например, барьерный слой 513, 513' и электропроводные материалы 514, 514', описываемые ниже). Однако слишком большой наклон может затруднить заполнение канавок 510, 510' без щелей и других дефектов. В некоторых вариантах канавки 510, 510' могут быть расположены таким образом, чтобы избежать или иным образом не повлиять на функции других компонентов матрицы ячеек памяти, таких как соединительные линии 506, 507, которые могут присутствовать в слое 508. Эта концепция представлена в периферийной части Фиг. 5B, где показано, что канавка 510' выполнена так, чтобы не задевать соединительных линий 506, 507, например, она создана между такими соединительными линиями.

Снова возвращаясь к Фиг. 4, способ может перейти к блоку 404, в котором канавки, созданные в соответствии с блоком 403, могут быть заполнены изоляционным материалом. Эту концепцию иллюстрирует Фиг. 5C, где показаны канавки 510, 510', заполненные изоляционным материалом 511, 511'. Изоляционный материал 511, 511' может быть создан путем осаждения и/или выращивания одного или сочетания изоляционных материалов в канавках 510, 510'. В качестве неограничивающих примеров подходящих изоляционных материалов, которые могут быть использованы в качестве или в составе изоляционного материала 511, 511', можно указать борфосфорсиликатное стекло, изоляционный оксид, такой как SiOx (например, SiO2), оксид кремния и/или силикаты, полученные из соответствующего кремнийсодержащего исходного материала, такого как тетраэтилортосиликат (tetraethylorthosilicate (TEOS)), наносимый на центрифуге полимерный диэлектрический материал, сочетания таких материалов и другие подобные материалы. В любом случае, канавки 510, 510' могут быть заполнены изоляционным материалом 511, 511' с использованием какого-либо подходящего процесса.

В некоторых вариантах канавки 510, 510' могут быть заполнены посредством многоступенчатого процесса, в котором объем канавок 510, 510' может быть первоначально заполнен борфосфорсиликатным стеклом (BPSG), например, посредством химического осаждения из паровой фазы (chemical vapor deposition (CVD)) или другим подходящим способом. Глубина первоначального заполнения стеклом BPSG может изменяться в значительных пределах примерно от 1000 Ангстрем до 50,000 Ангстрем или более в зависимости от глубины канавок 510, 510'. Без ограничений глубина первоначального заполнения стеклом BPSG может изменяться в пределах примерно от 10,000 до 30,000 Ангстрем, например, примерно от 18,000 до 25,000 Ангстрем. Хотя можно осадить стекло BPSG с высоким качеством (например, посредством осаждения CVD или другого процесса), во многих случаях в этом заполняющем канавки стекле BPSG могут присутствовать трещины или другие дефекты. Будучи оставлены «в одиночестве», такие дефекты могут отрицательно повлиять на характеристики сквозных каналов, описываемых здесь. Поэтому в некоторых вариантах трещины и/или другие дефекты в заполняющем стекле BPSG (если таковые есть) могут быть заполнены путем осаждения одного или нескольких дополнительных материалов в канавки 510, 510'.

В качестве примера, в некоторых вариантах дефекты в заполняющем стекле BPSG могут быть по меньшей мере частично заполнены путем осаждения тетраэтилортосиликата (TEOS) поверх этого заполняющего стекла BPSG, например, посредством химического осаждения из паровой фазы. Осажденный материал TEOS может быть затем преобразован в диоксид кремния путем воздействия тепла либо в единственном числе, либо в сочетании с другими технологическими этапами, которые известны в технике.

В некоторых вариантах осаждение стекла BPSG, указанное выше, может привести к образованию в канавках 510, 510' пленки стекла BPSG, в которой присутствуют механические напряжения растяжения. По мере заполнения канавок 510, 510' стеклом BPSG накопление механических напряжений растяжения может стать значительным. Для решения этой проблемы в некоторых вариантах осаждение материала TEOS может быть конфигурировано для релаксации части или всех механических напряжений, возникших в результате осаждения стекла BPSG. Это может быть достигнуто, например, путем осаждения материала TEOS таким образом, что полученный в результате оксид кремния образует пленку, содержащую механические напряжения растяжения, противоположные механическим напряжениям, имеющим место в заполняющем стекле BPSG. Это может ограничить и/или предотвратить выгибание пластины

Во время осаждения стекла BPSG и материала TEOS эти материалы могут быть нанесены поверх и/или на верхнюю поверхность чередующихся диэлектрических и электропроводных слоев 504, 505. Поэтому в некоторых вариантах может быть осуществлена, в качестве опции, первая операция полирования, такая как химико-механическое полирование, для удаления нежелательных участков стекла BPSG и оксида SiO2 и, в некоторых случаях, для планаризации поверхности чередующихся электропроводных и диэлектрических слоев 504, 505. После этой осуществляемой в качестве опции первой операции полирования (или если эта первая операция полирования исключена) могут остаться (или появиться другим способом) трещины или другие дефекты в заполняющем изоляционном материале 511, 511'. В таких случаях, материал TEOS может быть осажден снова для заполнения таких дефектов. В качестве альтернативы или в дополнение могут быть нанесены и другие материалы, такие как наносимый на центрифуге диэлектрик, для заполнения таких дефектов. После такого дополнительного осаждения материала TEOS и/или другого изоляционного материала можно, посредством выполняемой в качестве опции второй операции полирования, удалить нежелательный материал и/или планаризировать поверхность чередующихся электропроводных и диэлектрических слоев 504, 505.

После осаждения изоляционный материал 511, 511' может заполнить все или по существу все канавки 510, 510', так что верхняя поверхность изоляционного материала 511, 511' может быть по существу копланарной поверхности самого верхнего из диэлектрических и электропроводных слоев 504, 505. В варианте, показанном на Фиг. 5C, верхняя поверхность изоляционного материала 511, 511' копланарна поверхности самого верхнего из диэлектрических или электропроводных слоев 504, 505.

Возвращаясь снова к Фиг. 4, способ может перейти к блоку 405, согласно которому в изоляционном слое, созданном согласно блоку 404, могут быть выполнены один или несколько каналов. Как указано выше, настоящее изобретение сосредоточится на вариантах, в которых в изоляционном материале 511, 511' создан единственный канал 512, 512', однако следует понимать, что в изоляционном материале 511, 511' в каждой канавке 510, 510' могут быть созданы несколько каналов (например, 2, 3, 4, 5, 6 и т.п.) в зависимости от размеров канавки 510, 510' и характеристик изоляционного материала 511, 511'. В любом случае, концепция создания канала в изоляционном материале изображена на Фиг. 5D, который иллюстрирует создание одного канала 512, 512' в изоляционном материале 511, 511'.

Канал 512, 512' может быть создан с использованием какого-либо подходящего процесса, известного в технике, такого как процесс травления или размывания. Без ограничений, в некоторых вариантах канал 512, 512' предпочтительно формируют с использованием сухого травления, такого как, не ограничиваясь, контактное травление и травление канавок с большим коэффициентом формы (HART). Аналогично процессу HART, который может быть использован для создания канавки 510, 510', процесс сухого травления, применяемый для выполнения канала 512, 512', может быть конфигурирован для агрессивного травления материала, используемого в качестве изоляционного материала 511, 511' (например, стекла BPSG, оксида SiO2, наносимого на центрифуге диэлектрика и т.п.), но может не травить или может по существу не травить материал структуры 509 (например, электрический проводник, такой как вольфрам). Однако, поскольку размер верхней части канала 512, 512' много меньше размера канавки 510, 510', процесс сухого травления, используемый для образования канала 512, 512', может быть конфигурирован таким образом, чтобы травление позволяло получить значительно более высокий коэффициент формы, чем процесс HART, который может быть применен для создания канавки 510, 510'. В любом случае этот канал 512, 512' может создать доступ к структуре 509. Как будет рассмотрено позднее, каналы 512, 512' могут быть использованы для прокладки одной или нескольких линий доступа от области над пакетом диэлектрических и электропроводных слоев 504, 505 к области ниже этого пакета, например, к структуре 509 (например, к схеме, созданной по технологии CUA).

Хотя настоящее изобретение рассматривает варианты, в которых может быть создан канал 512, 512' каких-либо подходящих размеров, в некоторых вариантах может быть желательно управлять размерами канала 512, 512' и, в свою очередь, толщиной изоляционного слоя 511, 511', оставшегося между пакетом чередующихся диэлектрических и электропроводных слоев 504, 505 и каналом 512, 512'. Это особенно справедливо в случаях, когда канал 512, 512' должен быть заполнен или иначе содержать электропроводный материал. В таких случаях может быть желательно обеспечить, чтобы толщина изоляционного слоя 511, оставшегося после образования канала 512, 512', была достаточна для электрической изоляции электрического проводника, который может быть добавлен в канал 512, 512', от пакета чередующихся диэлектрических и электропроводных слоев 504, 505, например, для предотвращения электрического короткого замыкания. В этом смысле толщина изоляционного слоя 511, 511' оставшегося после образования канала 512, 512' может изменяться в широких пределах. В некоторых вариантах толщина изоляционного слоя 511, 511', оставшегося после образования канала 512, 512', может составлять примерно от 90 нм до 250 нм, например, примерно 100 нм. Без ограничений, толщина слоя изоляционного материала 511, 511', оставшегося после формирования канала 512, 512', не меньше 100 нм. На Фиг. 5D-F показаны каналы 512, 512', имеющие конусообразную структуру, так что размер (например, ширина) каждого канала возле его дна меньше соответствующего размера возле верхнего края этого канала. В такой конфигурации можно понять, что каналы 512, 512' имеют наклонные боковые стенки. Величина наклона боковых стенок каналов 512, 512' может изменяться в широких пределах и может диктоваться конструкторскими и/или технологическими ограничениями. Без ограничений, наклон одной или обеих боковых стенок каналов 512, 512' может быть в пределах от примерно 88 до примерно 89 градусов относительно плоскости верхней поверхности структуры 509. В некоторых вариантов наклон боковых стенок каналов 512, 512' может быть таким же или по существу таким же, как наклон боковых стенок канавок 510, 510'.

Возвращаясь снова к Фиг. 4, способ может перейти к блоку 406, в соответствии с которым канал, созданный согласно блоку 405, может быть металлизирован для создания электропроводной линии, проходящей через этот канал. В этом смысле настоящее изобретение рассматривает различные варианты, в которых каналы 512, 512' могут быть заполнены одним или несколькими материалами, включая по меньшей мере один электропроводный материал, такой как электропроводный металл. В некоторых вариантах металлизацию осуществляют посредством многоступенчатого процесса, в ходе которого сначала на стенки и/или дно каналов 512, 512' осаждают барьерный слой, после чего на этот барьерный слой осаждают один или несколько слоев электропроводного материала (например, металла). В других вариантах за осаждением барьерного слоя следует осаждение первого слоя металла и затем второго слоя металла/заполнения.

Изложенную выше концепцию иллюстрируют Фиг. 5E и 5F. В частности, на Фиг. 5E показан вариант, в котором на боковых стенках и дне каналов 512, 512' выполнены барьерные слои 513, 513'. Эти барьерные слои 513, 513' могут быть созданы любым подходящим способом, таким как, не ограничиваясь, химическое осаждение из паровой фазы, физическое осаждение из паровой фазы, электроннолучевое напыление, осаждение атомных слоев, импульсное лазерное напыление, какие-либо сочетания этих способов или другой подобный подходящий способ. Без ограничений, барьерные слои 513, 513' предпочтительно формируют посредством химического осаждения из паровой фазы.

Барьерные слои 513, 513' могут быть выполнены из какого-либо подходящего барьерного материала или сочетания барьерных материалов. Среди неограничивающих примеров подходящих материалов, которые могут быть использованы в качестве барьерных слоев 513, 513', можно указать барьерные металлы и нитриды металлов, такие как нитрид титана, нитрид тантала, нитрид вольфрама и вольфрам. Без ограничений, барьерные слои 513, 513' предпочтительно формируют из нитрида титана, наносимого способом химического осаждения из паровой фазы. Безусловно, могут быть использованы и другие барьерные материалы, что также предусмотрено настоящим изобретением.

Толщина барьерных слоев 513, 513' может варьироваться в широких пределах. В некоторых вариантах толщина барьерных слоев 513, 513' находится в пределах примерно от 1 до 5000 Ангстрем, например, от 1 до 500 Ангстрем или даже примерно от 1 до 100 Ангстрем. Без ограничений, барьерные слои 513, 513' предпочтительно имеют толщину примерно от 25 до 75 Ангстрем, а в некоторых вариантах эта толщина составляет около 60 Ангстрем. После осаждения барьерных слоев 513, 513' может быть, в качестве опции, произведено химико-механическое полирование, чтобы материал барьерных слоев 513, 513' остался только внутри каналов 512, 512'. В любом случае некоторая часть объема каналов 512, 512' может остаться свободной после осаждения барьерных слоев 513, 513', как показано на Фиг. 5E. Другими словами, барьерные слои 513, 513' предпочтительно заполняют только часть объема каналов 512, 512'.

Как показано на Фиг. 5F, процесс металлизации каналов 512, 512' может быть продолжен посредством осаждения электропроводного материала 514, 514' в оставшиеся участки каналов 512, 512'. Как отмечено ранее, электропроводный материал 514, 514' может содержать электропроводные материалы одного или нескольких типов, которые могут быть нанесены послойно или в смеси один с другим. В этом смысле, для создания электропроводного материала 514, 514' могут быть использованы самые различные электропроводные материалы, включая металлы, такие как алюминий, медь, титан, вольфрам, электропроводные нитриды и оксиды этих металлов, другие электропроводные материалы, такие как электропроводные полимеры, поликристаллический кремний и т.п., сочетания таких материалов и другие подобные материалы.

В некоторых вариантах электропроводный материал 514, 514' выполнен в форме единого заполнения, содержащего один или сочетание перечисленных выше материалов. В других вариантах электропроводный материал 514, 514' выполнен в виде многослойной структуры, в которой сначала созданы один или несколько слоев перечисленных выше электропроводных материалов, а затем или поочередно с этими слоями нанесены один или несколько дополнительных слоев перечисленных выше электропроводных материалов. В некоторых вариантах электропроводный материал 514, 514' формируют путем осаждения первого слоя металла (например, титана или другого электропроводного материала) и затем создания второго слоя металла (например, вольфрама или другого электропроводного материала) поверх первого слоя металла.

Электропроводный материал 514, 514' может быть создан и/или осажден в оставшиеся участки каналов 512, 512' каким-либо подходящим способом, таким как, не ограничиваясь, химическое осаждение из паровой фазы, физическое осаждение из паровой фазы, электроннолучевое напыление, осаждение атомных слоев, импульсное лазерное напыление, какие-либо сочетания этих способов или другой подобный подходящий способ. Без ограничений, электропроводный материал предпочтительно формируют путем химического осаждения из паровой фазы первого слоя металла (например, титана или другого электропроводного материала) и затем химического осаждения из паровой фазы второго слоя металла (например, вольфрама или другого электропроводного материала) поверх первого слоя металла.

После осаждения электропроводного материала 514, 514' может быть, в качестве опции, произведено химико-механическое полирование (chemical mechanical polishing (CMP)) для удаления электропроводного материала с верхней поверхности самого верхнего слоя из пакета диэлектрических и электропроводных слоев 504, 505, так что этот электропроводный материал 514, 514' может быть изолирован, оставаясь внутри канавок 510, 510', или более конкретно внутри каналов 512, 512', выполненных в этих канавках. В некоторых вариантах, поверхность электропроводного материала 514, 514' является копланарной верхней поверхности самого верхнего слоя из состава пакета диэлектрических и электропроводных слоев 504, 505, как показано на Фиг. 5F.

В этот момент формирование энергонезависимого запоминающего устройства может продолжиться, например, путем соединения одной или нескольких линий доступа с электропроводным материалом 514, 514', чтобы соединить такие линии со структурой 509, например, драйверной схемой, которая могла быть ранее создана под матрицей ячеек памяти и/или под периферийной областью матрицы. При таком подходе линии доступа могут быть проложены через каналы 512, 512'. Как отмечено выше, это может открыть широкий спектр альтернативных конфигураций соединений, где линии доступа могут быть проложены к расположенной ниже схеме через одно или несколько сквозных отверстий. В некоторых вариантах, такая конструкция может позволить проложить большое число линий доступа и/или добавить дополнительные линии доступа, не оказывая или по существу не оказывая нежелательного воздействия на высоту блока и на характеристики энергонезависимого запоминающего устройства. Поэтому предполагается, что описываемые здесь технологии будут особенно полезны в матрицах ячеек памяти с высокой плотностью размещения ячеек, где нужно проложить большое число линий доступа, а высота блока в матрице ячеек памяти ограничена конструктивными соображениями и/или требованиями стандарта.

На Фиг. 6 представлена функциональная блок-схема электронной системы, содержащей по меньшей мере одно запоминающее устройство согласно одному или нескольким вариантам настоящего изобретения. Запоминающее устройство 600, показанное на Фиг. 6, соединено с главным устройством, таким как процессор 610. Этот процессор 610 может представлять собой микропроцессор или схему управления какого-либо другого типа. Запоминающее устройство 600 и процессор 610 составляют часть электронной системы 620. Представленное запоминающее устройство 600 было упрощено, чтобы сосредоточиться на признаках запоминающего устройства, которые будут полезны для понимания различных вариантов настоящего изобретения.

Запоминающее устройство 600 содержит одну или несколько матриц 690 ячеек памяти, которые могут быть логически организованы в виде банков из строк и столбцов. Согласно одному или нескольким вариантам матрица 690 ячеек памяти может быть конфигурирована так, как это описано выше применительно к матрицам ячеек памяти, показанным на Фиг. 1-3 и 5А-F. Соответственно, матрица 690 ячеек памяти может быть выполнена в форме устройства флэш-памяти, которое содержит несколько банков и блоков ячеек памяти, размещенных в одном или нескольких кристаллах интегральных схем, как часть запоминающего устройства 600.

Устройство может содержать буфер 640 адресов для защелкивания адресных сигналов, поступающих по входным линиям AO-AX 642 адресов. Декодер 644 строк и декодер 648 столбцов принимают и декодируют эти адресные сигналы для доступа к матрице ячеек памяти. Декодер 644 строк может содержать драйверные схемы, конфигурированные для управления числовыми шинами, вентилями выбора цепочек и одним или несколькими плоскими затворами согласно различным вариантам настоящего изобретения, например. Специалистам в рассматриваемой области должно быть понятно, в соответствии с преимуществами настоящего изобретения, что число входных соединений 642 адресов может зависеть от плотности размещения ячеек памяти и архитектуры матрицы 690 ячеек памяти. Иными словами, число адресных разрядов увеличивается как при увеличении числа ячеек памяти, так и при увеличении числа банков и блоков, например.

Запоминающее устройство 600 может считывать данные из матрицы 690 ячеек памяти путем измерения изменений напряжения или тока в столбцах матрицы ячеек памяти с использованием измерительных устройств, таких как схема 650 измерений/кэша данных. В некоторых вариантах схема 650 измерений/кэша данных присоединена для считывания и защелкивания строки данных из матрицы 690 ячеек памяти. Система может содержать буферную схему 660 ввода/вывода (I/O) данных для обмена данными в двух направлениях по нескольким линиям 662 данных с процессором 610. Устройство может содержать схему 656 записи/стирания для записи данных в матрице 690 ячеек памяти и стирания данных из этой матрицы 690.

Схема управления 670 может быть конфигурирована по меньшей мере частично для осуществления различных вариантов настоящего изобретения, таких как способствование управлению различными вентилями и затворами, как обсуждается выше. По меньшей мере в одном из вариантов эта схема управления 670 может содержать конечный автомат. Сигналы управления и команды могут быть переданы процессором 610 запоминающему устройству 600 по командной шине 672. Командная шина 672 может передавать отдельные дискретные командные сигналы или группы из нескольких командных сигналов. Командные сигналы, передаваемые по командной шине 672, могут быть использованы для управления операциями в матрице 690 ячеек памяти, включая считывание данных, программирование данных (например, запись) и операции стирания. Командная шина 672, адресная шина 642 и шина 662 данных могут быть объединены все вместе или частично для образования нескольких стандартных интерфейсов 678. Например, интерфейс 678 между запоминающим устройством 600 и процессором 610 может представлять собой интерфейс универсальной последовательной шины (Universal Serial Bus (USB)). Интерфейс 678 может также представлять собой стандартный интерфейс, используемый в сочетаниях со многими накопителями на жестких дисках и материнскими платами, такими как, но без ограничений, интерфейс периферийных устройств (peripheral component interface (PCI)), интерфейс PCI express, интерфейс усовершенствованной технологии последовательного соединения (serial advanced technology attachment (SATA)) или интерфейс усовершенствованной технологии параллельного соединения (parallel advanced technology attachment (PATA)), сочетание таких интерфейсов или какой-либо другой подобный интерфейс, известный специалистам в рассматриваемой области.

Примеры

Приведенные ниже примеры относятся к другим вариантам. Эти дополнительные примеры настоящего изобретения могут содержать материал, являющийся предметом настоящего изобретения, такой как энергонезависимое запоминающее устройство и способы его изготовления, как указано ниже.

Пример 1: Одним из примеров технологии согласно настоящему изобретению является энергонезависимое запоминающее устройство, содержащее: матрицу ячеек памяти, имеющую в составе пакет чередующихся диэлектрических и электропроводных слоев, выполненный на изоляционном слое, эта матрица ячеек памяти содержит далее область собственно матрицы ячеек памяти и периферийную область; структуру, выполненную по меньшей мере под одной из областей - областью собственно матрицы ячеек памяти и/или периферийной областью, и электрически соединенную с другим компонентом энергонезависимого запоминающего устройства; и проходящее через матрицу сквозное отверстие, выполненное по меньшей мере в одной из областей - области собственно матрицы ячеек памяти и/или периферийной области; где по меньшей мере одна линия доступа матрицы ячеек памяти проложена через это сквозное отверстие.

Пример 2: Этот пример содержит какие-либо или все признаки примера 1, где указанное проходящее через матрицу сквозное отверстие выполнено по меньшей мере в периферийной области.

Пример 3: Этот пример содержит какие-либо или все признаки примера 1, где матрица ячеек памяти содержит вертикальный пакет ячеек памяти.

Пример 4: Этот пример содержит какие-либо или все признаки примера 1, где указанный другой компонент содержит драйверную схему для управления по меньшей мере одной цепочкой ячеек памяти в составе матрицы ячеек памяти.

Пример 5: Этот пример содержит какие-либо или все признаки примера 4, где:

матрица ячеек памяти составлена по меньшей мере из первой и второй матриц ячеек памяти, каждая из которых содержит несколько ячеек памяти;

и драйверная схема используется совместно первой и второй матрицами ячеек памяти, и эта драйверная схема конфигурирована для управления ячейками памяти в этих матрицах.

Пример 6: Этот пример содержит какие-либо или все признаки примера 1, где пакет чередующихся диэлектрических и электропроводных слоев имеет верхнюю поверхность и где сквозное отверстие проходит от верхней поверхности к структуре.

Пример 7: Этот пример содержит какие-либо или все признаки примера 1, где проходящее через матрицу сквозное отверстие содержит по меньшей мере одну канавку с большим коэффициентом формы.

Пример 8: Этот пример содержит какие-либо или все признаки примера 7, где указанная канавка заполнена по меньшей мере одним изоляционным материалом.

Пример 9: Этот пример содержит какие-либо или все признаки примера 8, где указанный по меньшей мере один изоляционный материал выбран из группы, содержащей борфосфорсиликатное стекло, неэлектропроводный оксид кремния, наносимый на центрифуге диэлектрик и сочетания этих материалов.

Пример 10: Этот пример содержит какие-либо или все признаки примера 9, где указанный по меньшей мере один изоляционный материал представляет собой сочетание борфосфорсиликатного стекла, SiO2 и наносимого на центрифуге диэлектрика.

Пример 11: Этот пример содержит какие-либо или все признаки примера 8, где в изоляционном материале создан по меньшей мере один канал.

Пример 12: Этот пример содержит какие-либо или все признаки примера 11, где в указанном по меньшей мере одном канале выполнен по меньшей мере один электропроводный материал.

Пример 13: Этот пример содержит какие-либо или все признаки примера 12, где указанный по меньшей мере один электропроводный материал выбран из группы, содержащей алюминий, медь, титан, вольфрам, электропроводный нитрид металла, электропроводный оксид металла, электропроводный полимер, поликристаллический кремний и сочетания этих материалов.

Пример 14: Этот пример содержит какие-либо или все признаки примера 12, где указанный по меньшей мере один электропроводный материал выполнен в форме по меньшей мере одного первого электропроводного слоя и по меньшей мере одного второго электропроводного слоя, осажденного на указанный по меньшей мере один первый электропроводный слой.

Пример 15: Этот пример содержит какие-либо или все признаки примера 14, где первый электропроводный слой выполнен из титана, а второй электропроводный слой выполнен из вольфрама.

Пример 16: Этот пример содержит какие-либо или все признаки какого-либо из примеров 12-15, где толщина промежутка между изоляционным материалом и каналом достаточна для электрической изоляции электропроводного материала от пакета из чередующихся диэлектрических и электропроводных слоев.

Пример 17: Этот пример содержит какие-либо или все признаки какого-либо из примеров 12-13, и дополнительно содержит по меньшей мере один барьерный слой, выполненный между по меньшей мере одним электропроводным материалом и пакетом из чередующихся диэлектрических и электропроводных слоев.

Пример 18: Этот пример содержит какие-либо или все признаки примера 17, где указанный по меньшей мере один барьерный слой выполнен из барьерного материала, выбранного из группы, содержащей нитрид титана, нитрид тантала, нитрид вольфрама, вольфрам и их сочетания.

Пример 19: Этот пример содержит какие-либо или все признаки какого-либо из примеров 14-15, и дополнительно содержит по меньшей мере один барьерный слой, выполненный между первым электропроводным слоем и пакетом из чередующихся диэлектрических и электропроводных слоев.

Пример 20: Этот пример содержит какие-либо или все признаки примера 19, где указанный по меньшей мере один барьерный слой выполнен из барьерного материала, выбранного из группы, содержащей нитрид титана, нитрид тантала, нитрид вольфрама, вольфрам и их сочетания.

Пример 21: Этот пример содержит какие-либо или все признаки примера 1, где по меньшей мере одна из линий доступа представляет собой по меньшей мере одно-истоковую шину, числовую шину, линию вентиля выбора истока и линию вентиля выбора стока.

Пример 22: Согласно этому примеру предложен способ изготовления энергонезависимого запоминающего устройства, содержащий создание матрицы ячеек памяти, имеющей в составе пакет чередующихся диэлектрических и электропроводных слоев, выполненный на изоляционном слое, матрица ячеек памяти далее содержит область собственно матрицы ячеек памяти и периферийную область; формирование по меньшей мере одного проходящего сквозь матрицу ячеек памяти сквозного отверстия по меньшей мере в области собственно матрицы ячеек памяти и/или периферийной области, это сквозное отверстие проходит от верхней поверхности пакет чередующихся диэлектрических и электропроводных слоев к структуре, расположенной под по меньшей мере одной из областей - областью собственно матрицы ячеек памяти и/или периферийной области, эта структура электрически соединена с другим компонентом энергонезависимого запоминающего устройства; где указанное сквозное отверстие конфигурировано таким образом, чтобы можно было электрически соединить по меньшей мере одну линию доступа из состава матрицы ячеек памяти с указанной структурой.

Пример 23: Этот пример содержит какие-либо или все признаки примера 22, где матрица ячеек памяти содержит вертикальный пакет ячеек памяти.

Пример 24: Этот пример содержит какие-либо или все признаки примера 22, где указанный другой компонент содержит драйверную схему для управления по меньшей мере одной цепочкой ячеек памяти в составе матрицы ячеек памяти.

Пример 25: Этот пример содержит какие-либо или все признаки примера 24, где: матрица ячеек памяти составлена по меньшей мере из первой и второй матриц ячеек памяти, каждая из которых содержит несколько ячеек памяти; и драйверная схема используется совместно первой и второй матрицами ячеек памяти, и эта драйверная схема конфигурирована для управления ячейками памяти в этих матрицах.

Пример 26: Этот пример содержит какие-либо или все признаки примера 23, где пакет чередующихся диэлектрических и электропроводных слоев имеет верхнюю поверхность и где сквозное отверстие проходит от верхней поверхности к структуре.

Пример 27: Этот пример содержит какие-либо или все признаки примера 22, где создание по меньшей мере одного проходящего через матрицу сквозного отверстия содержит формирование по меньшей мере одной канавки с большим коэффициентом формы, проходящей от верхней поверхности пакета чередующихся диэлектрических и электропроводных слоев к структуре.

Пример 28: Этот пример содержит какие-либо или все признаки примера 27, где создание по меньшей мере одной канавки с большим коэффициентом формы содержит травление чередующихся диэлектрических и электропроводных слоев способом сухого травления.

Пример 29: Этот пример содержит какие-либо или все признаки примера 27, где создание проходящего через матрицу ячеек памяти сквозного отверстия дополнительно содержит заполнение указанной по меньшей мере одной канавки с большим коэффициентом формы по меньшей мере одним изоляционным материалом.

Пример 30: Этот пример содержит какие-либо или все признаки примера 25, где указанный по меньшей мере один изоляционный материал выбран из группы, содержащей борфосфорсиликатное стекло, неэлектропроводный оксид кремния, наносимый на центрифуге диэлектрик и сочетания этих материалов.

Пример 31: Этот пример содержит какие-либо или все признаки примера 30, где указанный по меньшей мере один изоляционный материал представляет собой сочетание борфосфорсиликатного стекла, SiO2 и наносимого на центрифуге диэлектрического материала.

Пример 32: Этот пример содержит какие-либо или все признаки примера 31, где заполнение указанной по меньшей мере одной канавки с большим коэффициентом формы содержит: осаждение борфосфорсиликатного стекла по меньшей мере в одну канавку с большим коэффициентом формы; осаждение тетраэтилортосиликата на борфосфорсиликатное стекло способом химического осаждения из паровой фазы; и осаждение наносимого на центрифуге диэлектрического материала по меньшей мере на поверхность оксида кремния и/или борфосфорсиликатного стекла.

Пример 33: Этот пример содержит какие-либо или все признаки примера 29, где при создании по меньшей мере одного проходящего через матрицу сквозного отверстия дополнительно выполняют по меньшей мере один канал в указанном по меньшей мере одном изоляционном материале.

Пример 34: Этот пример содержит какие-либо или все признаки примера 33, где создание указанного по меньшей мере одного канала содержит травление по меньшей мере одного изоляционного материала, так что канал проходит от верхней поверхности по меньшей мере одного изоляционного материала к указанному компоненту.

Пример 35: Этот пример содержит какие-либо или все признаки примера 34, где травление указанного по меньшей мере одного изоляционного материала осуществляется способом сухого травления.

Пример 36: Этот пример содержит какие-либо или все признаки примера 33, где создание указанного по меньшей мере одного проходящего через матрицу сквозного отверстия содержит заполнение указанного по меньшей мере одного канала по меньшей мере одним электропроводным материалом.

Пример 37: Этот пример содержит какие-либо или все признаки примера 36, где указанный по меньшей мере один электропроводный материал выбран из группы, содержащей алюминий, медь, титан, вольфрам, электропроводный нитрид металла, электропроводный оксид металла, электропроводный полимер, поликристаллический кремний и сочетания этих материалов.

Пример 38: Этот пример содержит какие-либо или все признаки примера 36, где указанный по меньшей мере один электропроводный материал выполнен в форме по меньшей мере одного первого электропроводного слоя и по меньшей мере одного второго электропроводного слоя, осажденного на указанный по меньшей мере один первый электропроводный слой.

Пример 39: Этот пример содержит какие-либо или все признаки примера 38, где первый электропроводный слой выполнен из титана, а второй электропроводный слой выполнен из вольфрама.

Пример 40: Этот пример содержит какие-либо или все признаки какого-либо из примеров 36-39, где толщина промежутка между изоляционным материалом и каналом достаточна для электрической изоляции электропроводного материала от пакета из чередующихся диэлектрических и электропроводных слоев.

Пример 41: Этот пример содержит какие-либо или все признаки какого-либо из примеров 36-37, и дополнительно содержит по меньшей мере один барьерный слой, выполненный между по меньшей мере одним электропроводным материалом и пакетом из чередующихся диэлектрических и электропроводных слоев.

Пример 42: Этот пример содержит какие-либо или все признаки примера 41, где указанный по меньшей мере один барьерный слой выполнен из барьерного материала, выбранного из группы, содержащей нитрид титана, нитрид тантала, нитрид вольфрама, вольфрам и их сочетания.

Пример 43: Этот пример содержит какие-либо или все признаки примера 41, где создание указанного по меньшей мере одного барьерного слоя осуществляется с использованием по меньшей мере одного из способов - химического осаждения из паровой фазы, физического осаждения из паровой фазы, электроннолучевого напыления, осаждения атомных слоев или импульсного лазерного напыления.

Пример 44: Этот пример содержит какие-либо или все признаки какого-либо из примеров 38-39, и дополнительно содержит по меньшей мере один барьерный слой, выполненный между первым электропроводным слоем и пакетом из чередующихся диэлектрических и электропроводных слоев.

Пример 45: Этот пример содержит какие-либо или все признаки примера 44, где указанный по меньшей мере один барьерный слой выполнен из барьерного материала, выбранного из группы, содержащей нитрид титана, нитрид тантала, нитрид вольфрама, вольфрам и их сочетания.