Область техники

[1] Изобретение относится к микропроцессорной технике, в частности к многоядерным процессорам, снабженным иерархической кэш-памятью для хранения данных.

Предпосылки к созданию изобретения

[2] Современные процессоры характеризуются весьма высокой скоростью осуществления вычислительных команд, при этом самыми медленно исполняемыми командами, которые главным образом и ограничивают производительность процессора, являются команды, связанные с обращением к запоминающему устройству, а именно команды чтения и записи данных. Снабжение процессора собственным запоминающим устройством, выполненным заодно с иными компонентами процессора на полупроводниковом кристалле и далее именуемым как «кэш-память», позволяет снизить время исполнения команд чтения и записи данных и тем самым повысить производительность процессора.

[3] Однако в случае многоядерного процессора данное преимущество реализуется при том лишь условии, что данные, подлежащие чтению каким-либо из ядер, на момент исполнения команды чтения сохранены в доступном данному ядру разделе кэш-памяти, т.е. при так называемом попадании в кэш. Другими словами, для заметного повышения производительности многоядерного процессора его кэш-память должна быть способна сохранять значительный объем данных в доступных каждому из ядер разделах, при том, что емкость кэш-памяти имеет очевидные конструктивные ограничения. Следует отметить, что кэш-память многоядерного процессора в традиционном исполнении содержит индивидуальные разделы, каждый из которых доступен только своему ядру, и общий раздел, доступный всем ядрам.

[4] Один из известных подходов к увеличению объема сохраненных данных в кэш-памяти заданной емкости состоит в сжатии массива данных (далее также - кэшлайн), который в несжатом виде целиком занимает одну строку кэш-памяти. Сжатие кэшлайна при этом целесообразно выполнить так, чтобы сжатый кэшлайн мог занимать не больше половины строки кэш-памяти. В этом случае в одной строке кэш-памяти можно разместить два кэшлайна, что, очевидно, увеличит объем сохраненных в кэш-памяти данных, даже если сжатие с положительным результатом будет произведено только для некоторых кэшлайнов.

[5] Применительно к многоядерному процессору, сжатые данные традиционно сохраняются только в общем разделе кэш-памяти, в то время как индивидуальные разделы сохраняют данные в несжатом виде. Данная конфигурация обусловлена тем, что индивидуальные разделы должны выдавать ядрам данные незамедлительно, и восстановление данных перед выдачей в ядра существенно замедлит производительность многоядерного процессора.

[6] Описанный подход раскрыт, например, в статье «Base-Delta-Immediate Compression: Practical Data Compression for On-Chip Caches», G. Pekhimenko и др., представленной на конференции PACT’12 (International Conference on Parallel Architectures and Compilation Techniques), Minneapolis Minnesota USA September 19 - 23, 2012, (найдено в Интернете: https://users.ece.cmu.edu/~omutlu/pub/bdi-compression_pact12.pdf). Однако, как признается в указанной статье, при сохранении данных в сжатом виде производительность многоядерного процессора лишь незначительно увеличивается только в случае выполнения нескольких программ одновременно, а если же многоядерный процессор в определенный момент времени выполняет только одну программу, то каких-либо преимуществ от сохранения сжатых данных практически не наблюдается. Тем временем есть основания полагать, что отмеченный в анализируемой статье незначительный или нулевой прогресс в увеличении производительности многоядерного процессора даже при определенном увеличении объема данных, сохраняемых в общем разделе кэш-памяти, связан с отсутствием у ядер возможности для прямого доступа к данным, хранящимся в других индивидуальных разделах, что в конечном итоге замедляет выполнение взаимосвязанных потоков программы.

[7] Техническая проблема, на решение которой направлено изобретение, состоит в повышении производительности многоядерного процессора, кэш-память которого способна сохранять данные в сжатом виде.

Сущность изобретения

[8] Для решения указанной технической проблемы в качестве изобретения предложен многоядерный процессор, снабженный кэш-памятью, которая включает в себя общий раздел и индивидуальные разделы по количеству ядер. Общий раздел при этом доступен всем ядрам, а каждый индивидуальный раздел доступен только своему ядру. Каждый из общего раздела и индивидуальных разделов содержит указываемые ячейки, способные сохранять данные, и указывающие ячейки, способные сохранять идентификаторы данных, сохраненных в указываемых ячейках. Тем временем каждой указываемой ячейке любого раздела соответствует своя указывающая ячейка этого же раздела. Указываемые ячейки общего раздела при этом способны сохранять данные в несжатом или в сжатом виде, а указываемые ячейки индивидуальных разделов способны сохранять данные в несжатом виде. Каждая указывающая ячейка общего раздела, не имеющая своей указываемой ячейки, вместе с идентификатором данных способна сохранять адресный указатель, который указывает, в каком из разделов сохранены данные, идентифицируемые сохраненным в данной указывающей ячейке идентификатором. Кэш-память способна переносить данные из исходной указываемой ячейки индивидуального раздела в участок целевой указываемой ячейки общего раздела и способна сохранять перенесенные данные в участке целевой указываемой ячейки общего раздела в сжатом виде. Одновременно с этим указывающая ячейка общего раздела, сохраняющая идентификатор переносимых данных, способна вместе с ним сохранять адресный указатель, указывающий на сохранение данных в общем разделе.

[9] Технический результат, достигаемый при осуществлении изобретения относительно известных решений, состоит в сокращении времени, требуемого на передачу в ядра многоядерного процессора тех данных, которые сохранены в индивидуальных разделах кэш-памяти, принадлежащих другим ядрам.

[10] Причинно-следственная связь между признаками изобретения и техническим результатом заключается в следующем. Поскольку общий раздел кэш-памяти предложенного многоядерного процессора способен сохранять данные в несжатом и сжатом видах (далее также кратко - несжатые и сжатые данные), то при выполнении сжатия сохраняемых данных общий раздел получает свободное пространство, в которое могут быть скопированы предварительно сжатые данные из индивидуальных разделов. Соответственно, когда какое-либо ядро запрашивает в общем разделе данные, сохраняемые в индивидуальном разделе другого ядра, общий раздел уже располагает сохраненной у себя копией этих данных и незамедлительно выдает ее в ответ на запрос. Таким образом, время на ожидание запрашивающим ядром выдачи запрашиваемых данных уменьшается, а производительность предложенного многоядерного процессора возрастает.

[11] В первом частном случае изобретения при сохранении данных в сжатом виде участок указываемой ячейки общего раздела занимает не больше половины указываемой ячейки. Данное исполнение обеспечивает наиболее плотную «упаковку» сжатых данных в указываемые ячейки общего раздела кэш-памяти, что позволяет увеличить объем данных, сохраненных в кэш-памяти, а значит, способствует ускорению выдачи затребованных данных в ядра многоядерного процессора.

[12] Причинно-следственная связь между признаками первого частного случая изобретения и его техническим результатом состоит в следующем. Массив данных (кэшлайн), подлежащий сжатию и последующему сохранению в общем разделе, может представлять собой либо массив различных значений, либо массив одинаковых значений, например массив нулевых значений. Если сжатие массива данных было произведено успешно, то массив данных, прежде занимавший в индивидуальном разделе всю указываемую ячейку целиком, размещается на участке указываемой ячейки общего раздела. Для сжатого массива различных значений этот участок может быть больше или меньше половины указываемой ячейки, в то время как для сжатого массива одинаковых значений этот участок оказывается существенно меньше половины указываемой ячейки.

[13] Соответственно, если сжатый массив различных значений занимает в указываемой ячейке общего раздела участок, который больше половины указываемой ячейки, то оставшийся участок может при определенных условиях вместить в себя только сжатый массив одинаковых значений. Тем временем, если сжатый массив различных значений занимает в указываемой ячейке общего раздела участок, который меньше или равен половине указываемой ячейки, то оставшийся участок может вместить в себя такой же сжатый массив различных значений либо сжатый массив одинаковых значений. Таким образом, если каждый сжатый массив из множества сжатых массивов занимает в указываемой ячейке общего раздела участок, который не превышает половину указываемой ячейки, то одно и то же множество сжатых массивов может быть сохранено в меньше количестве указываемых ячеек, а значит, в общем разделе появляется дополнительное пространство для сохранения других данных.

[14] Во втором частном случае изобретения исходная указываемая ячейка индивидуального раздела сохраняет копию данных, перенесенных в участок целевой указываемой ячейки общего раздела для сохранения в сжатом виде, при этом эти перенесенные данные подлежат вытеснению из общего раздела в первоочередном порядке. Данное исполнение позволяет сохранить быстроту выдачи данных из индивидуального раздела в связанное с ним ядро, даже если эти данные были скопированы в общий раздел. Вместе с тем сохранение в общем разделе скопированных данных, дублирующих таковые в индивидуальном разделе, имеет меньший приоритет перед сохранением в общем разделе новых данных, отсутствующих в индивидуальных разделах, что ставит дублирующие данные в первую очередь на вытеснение из общего раздела.

Краткое описание чертежей

[15] Осуществление изобретения будет пояснено ссылками на фигуры:

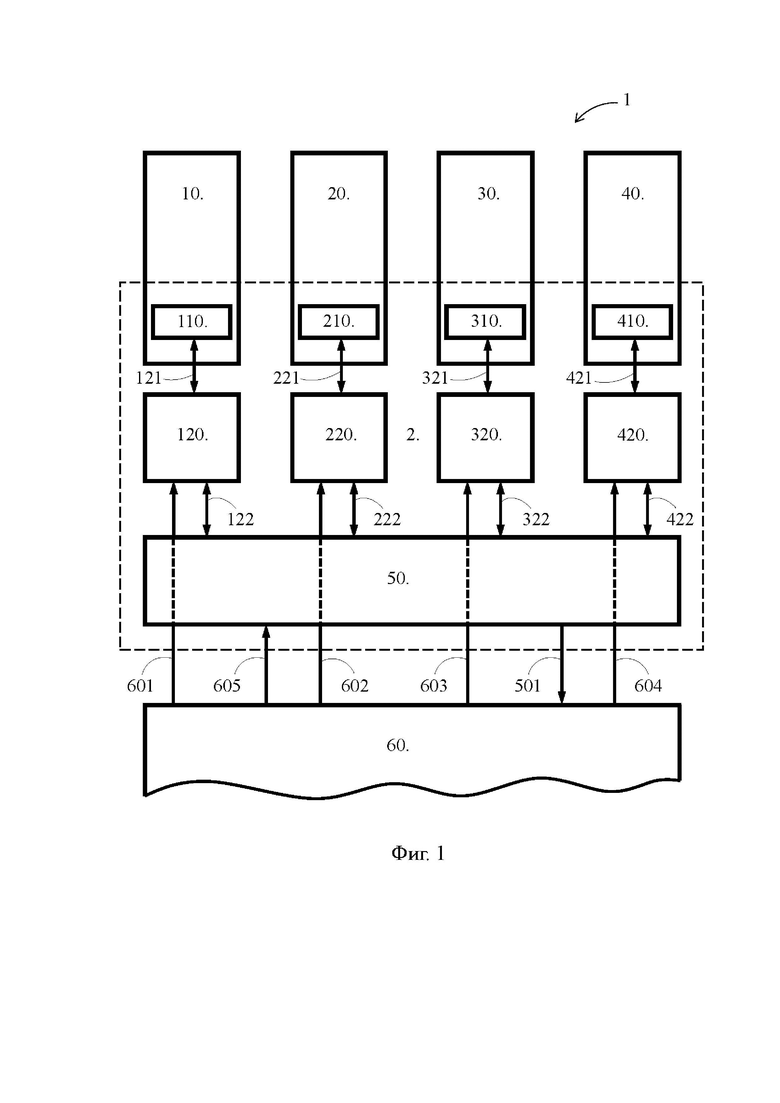

Фиг. 1 - блок-схема предложенного многоядерного процессора, иллюстрирующая структуру входящей в его состав кэш-памяти и ее взаимосвязь с ядрами предложенного многоядерного процессора;

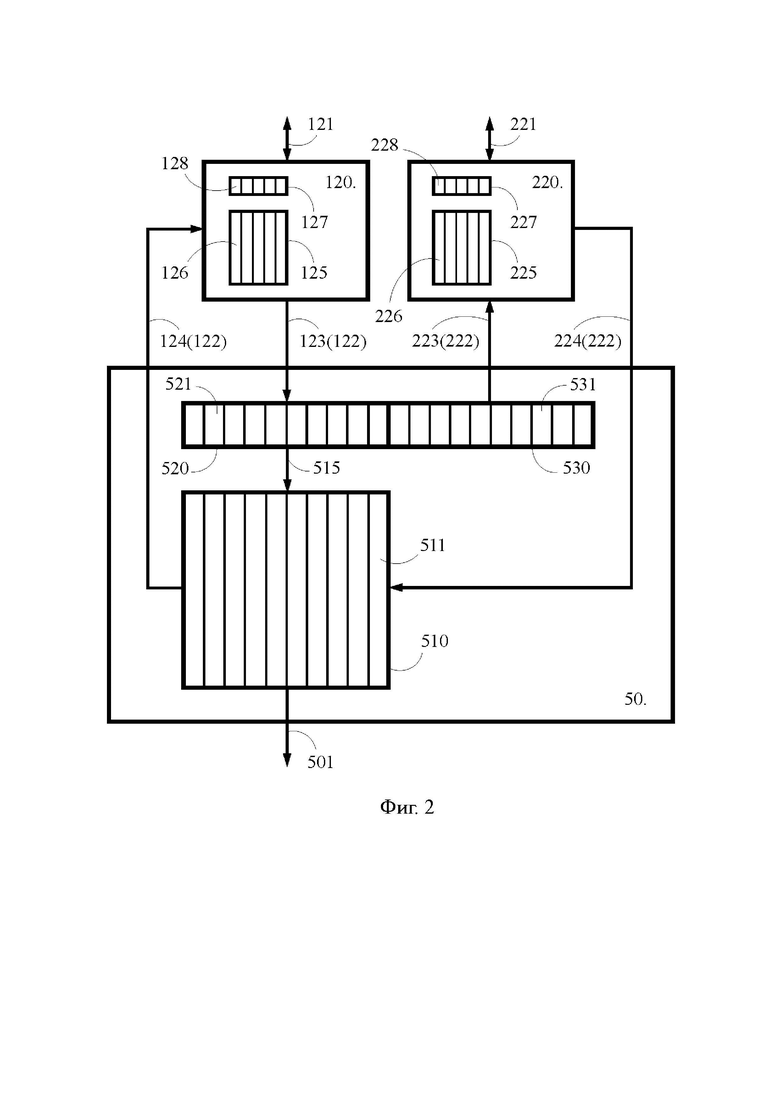

Фиг. 2 - блок-схема фрагмента кэш-памяти предложенного многоядерного процессора, иллюстрирующая работу кэш-памяти с несжатыми данными;

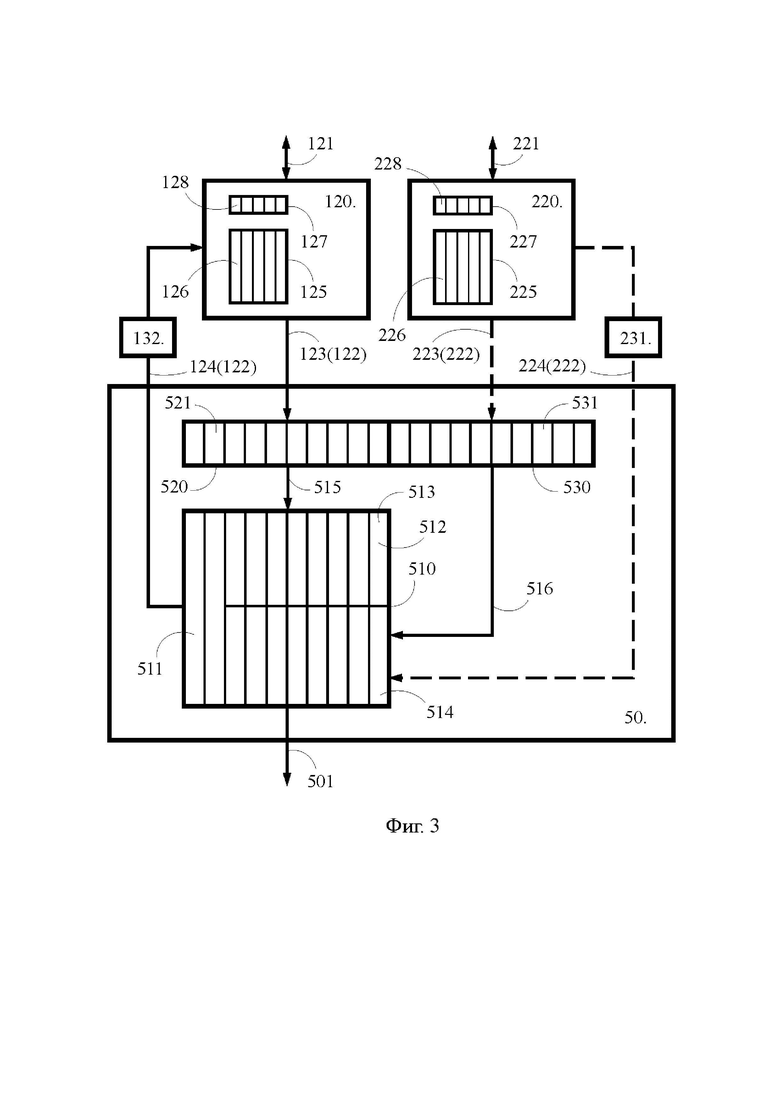

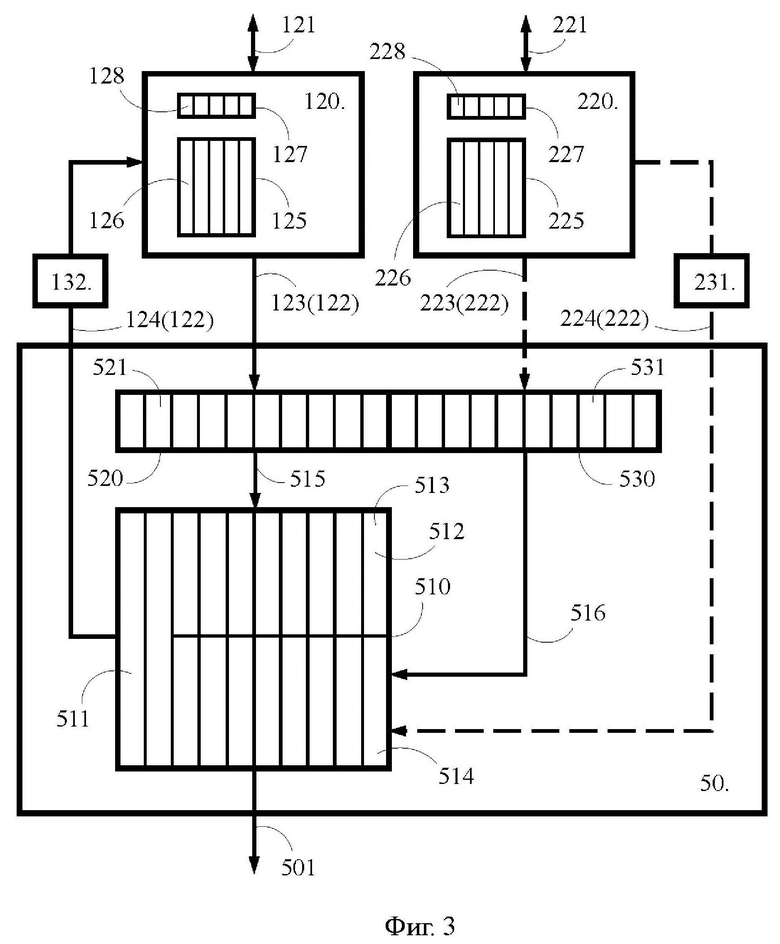

Фиг. 3 - блок-схема фрагмента кэш-памяти предложенного многоядерного процессора, иллюстрирующая работу кэш-памяти со сжатыми данными.

[16] Следует отметить, что форма и размеры отдельных элементов, отображенных на фигурах, являются условными и показаны так, чтобы наиболее наглядно проиллюстрировать взаимосвязи между элементами предложенного многоядерного процессора, а также причинно-следственную связь между этими элементами и техническим результатом. Кроме того, во избежание избыточного усложнения фигур некоторые взаимосвязи элементов, очевидные специалисту в данной области техники, могут быть не отображены.

Осуществление изобретения

[17] Осуществление изобретения будет показано на наилучших примерах его реализации, которые не являются ограничениями в отношении объема охраняемых прав.

[18] На Фиг. 1 показана блок-схема предложенного многоядерного процессора 1, иллюстрирующая структуру входящей в его состав кэш-памяти 2, а также взаимосвязь кэш-памяти 2 с ядрами 10, 20, 30 и 40 многоядерного процессора 1. Хотя на Фиг. 1 в иллюстративных целях показаны 4 ядра 10, 20, 30 и 40, многоядерный процессор 1 может содержать по существу любое количество ядер, например 8 ядер. Каждое из ядер 10, 20, 30 и 40 представляет собой по существу отдельный процессор, содержащий все необходимые компоненты для конвейерной обработки поступающего в него потока команд. Следует также отметить, что многоядерный процессор 1 может быть скалярным или суперскалярным процессором, может осуществлять выполнение команд в порядке загрузки (in-order execution) или в ином порядке (out-of-order execution), и может быть выполнен по существу в любой архитектуре, например в архитектуре VLIW (Very Long Instruction Word).

[19] Кэш-память 2 способна сохранять данные, используемые в качестве операндов команд и представляющие собой числовые значения, адреса собственных ячеек памяти и ячеек памяти в других устройствах и т.д. Обратим внимание, что наряду с кэш-памятью 2, по существу являющейся кэш-памятью данных, многоядерный процессор 1 может содержать кэш-память иного назначения, например кэш-память команд, при этом каждая из разновидностей кэш-памяти может быть выполнена как в виде одного или нескольких отдельных устройств, так и виде функционального раздела в одной интегрированной кэш-памяти.

[20] Далее, кэш-память 2 имеет общеизвестную трехуровневую иерархическую структуру, которая определяется степенью релевантности данных, сохраняемых на каждом иерархическом уровне, тому потоку команд, который поступает в каждое из ядер 10, 20, 30 и 40. Первый иерархический уровень кэш-памяти 2 представлен L1-кэшами 110, 210, 310 и 410, каждый из которых встроен в свое ядро 10, 20, 30 или 40. L1-кэши 110, 210, 310 и 410 предназначены для максимально быстрой выдачи необходимых данных в свои ядра 10, 20, 30 и 40, в связи с чем L1-кэши 110, 210, 310 и 410 имеют сравнительно небольшую емкость памяти (далее также - запоминающая емкость), например в многоядерном процессоре Эльбрус-8С каждый из L1-кэшей способен сохранять 64 Кбайт информации. Соответственно, L1-кэши 110, 210, 310 и 410 призваны сохранять только те данные, которые с очень большой вероятностью будут востребованы командами, подлежащими выполнению в ядрах 10, 20, 30 и 40 в ближайшее время, при этом данные, сохраняемые в L1-кэшах 110, 210, 310 и 410, доступны только своему ядру.

[21] Второй иерархический уровень кэш-памяти 2 представлен L2-кэшами 120, 220, 320 и 420, каждый из которых соединен со своим L1-кэшем 110, 210, 310 или 410 шиной 121, 221, 321 или 421 и способен выдавать данные только в свой L1-кэш 110, 210, 310 или 410, т.е. в свое ядро 10, 20, 30 или 40. Каждый из L2-кэшей 120, 220, 320 или 420 предназначен для максимально быстрого снабжения своего L1-кэша 110, 210, 310 или 410 необходимыми данными, и, исходя из этого, L2-кэши 120, 220, 320 и 420 имеют увеличенную относительно L1-кэшей 110, 210, 310 и 410 емкость памяти, например в многоядерном процессоре Эльбрус-8С каждый из L2-кэшей способен сохранять 512 Кбайт информации.

[22] Кроме того, L2-кэши 120, 220, 320 и 420 посредством шин 601, 602, 603 и 604 соединены с оперативной памятью 60. Ели запрашиваемые каким-либо из ядер 10, 20, 30 или 40 данные отсутствуют и в L1-кэше 110, 210, 310 или 410, и в L2-кэше 120, 220, 320 или 420, то именно соответствующий L2-кэш 120, 220, 320 или 420 напрямую получает требуемые данные из оперативной памяти 60 (пунктирные участки шин 601, 602, 603 и 604 на Фиг. 1 отображают тот факт, что шины 601, 602, 603 и 604 не имеют соединения с L3-кэшем 50). Следует отметить, что L2-кэши 120, 220, 320 и 420 по шинам 121, 221, 321 и 421 могут также получать данные, вытесняемые из L1-кэшей 110, 210, 310 и 410.

[23] Третий иерархический уровень кэш-памяти 2 представлен L3-кэшем 50, соединенным с каждым из L2-кэшей 120, 220, 320 или 420 шинами 122, 222, 322 или 422, по которым L3-кэш 50 способен выдавать данные в каждый из L2-кэшей 120, 220, 320 или 420, а также принимать данные, вытесняемые каждым из L2-кэшей 120, 220, 320 или 420. L3-кэш 50 предназначен для сравнительно быстрой выдачи в любой из L2-кэшей 120, 220, 320 или 420 широкого ряда потенциально необходимых данных, например тех данных, которые могут быть затребованы командами, принадлежащими различным альтернативным ветвям программы, переход на которые с определенной вероятностью будет осуществлен в будущем. В этих целях L3-кэш 50 выполнен с возможностью сохранения сравнительно большого объема данных, например в многоядерном процессоре Эльбрус-8С L3-кэш способен сохранять 16 Мбайт информации. Далее, L3-кэш 50 соединен с оперативной памятью 60 шиной 605, по которой данные, приобретающие релевантность загружаемому в ядра 10, 20, 30 и 40 фрагменту программы, заблаговременно поступают из оперативной памяти 60 в L3-кэш 50, и шиной 501, по которой данные, потерявшие релевантность указанному фрагменту программы, вытесняются из L3-кэша 50 в оперативную память 60.

[24] Поскольку L3-кэш 50 способен выдавать данные любому из L2-кэшей 120, 220, 320 или 420, т.е. любому ядру 10, 20, 30 и 40, то в контексте настоящего изложения он представляет собой общий раздел кэш-памяти 2 (далее также кратко - общий раздел). Обратим внимание, что в других исполнениях изобретения общий раздел может включать в себя дополнительные кэши, последовательно соединенные с L3-кэшем 50 со стороны оперативной памяти 60 и имеющие возрастающую запоминающую емкость в сторону оперативной памяти 60. Выполнение общего раздела из нескольких иерархически выстроенных кэшей вместо одного L3-кэша 50 той же запоминающей емкости позволяет увеличить среднюю скорость выдачи данных в L2-кэши 120, 220, 320 и 420, поскольку поиск затребованных данных в этом случае проводится по L3-кэшу 50 меньшего размера.

[25] Аналогичным образом, поскольку каждая цепочка из L1-кэша 110 и L2-кэша 120, L1-кэша 210 и L2-кэша 220, L1-кэша 310 и L2-кэша 320, L1-кэша 410 и L2-кэша 420 способна выдавать данные только своему ядру 10, 20, 30 или 40, то в контексте настоящего изложения она представляет собой индивидуальный раздел кэш-памяти 2 (далее также кратко - индивидуальный раздел). В других исполнениях изобретения индивидуальные разделы могут включать в себя дополнительные кэши, включенные в цепочку между каждым L1-кэшем 110, 210, 310 или 410 и каждым L2-кэшем 120, 220, 320 или 420 с теми же целями и по тем же принципам, что и упомянутые выше дополнительные кэши общего раздела. Вместе с тем возможно такое исполнение, когда каждый индивидуальный раздел состоит только лишь из одного L2-кэша 120, 220, 320 или 420.

[26] На Фиг. 2 показана блок-схема фрагмента кэш-памяти 2, иллюстрирующая работу кэш-памяти 2 с несжатыми данными. Этот режим работы кэш-памяти 2 (далее - режим несжатых данных) не является предметом изобретения и может быть задействован, когда потоки команд программы, загружаемые в ядра 10, 20, 30 и 40, имеют слабую связь друг с другом по используемым данным, а объем используемых данных невелик. При указанном условии, которое наблюдается сравнительно редко, режим несжатых данных получает некоторое преимущество перед описанным ниже режимом сжатых данных за счет экономии времени на восстановление выдаваемых кэш-памятью 2 данных, которые сохранялись в сжатом виде. По существу, режим несжатых данных и используемая для его реализации конфигурация кэш-памяти 2 являются опциональными для многоядерного процессора 1, при этом подробное их описание позволяет более наглядно представить особенности и технические результаты изобретения.

[27] Изображенный на Фиг. 2 фрагмент кэш-памяти 2 включает в себя два индивидуальных раздела и общий раздел, при этом индивидуальные разделы представлены L2-кэшами 120 и 220, и общий раздел представлен L3-кэшем 50. Следует отметить, что изображенные на Фиг. 2 L2-кэши 120 и 220 являются полностью идентичными, а любые различия между ними обусловлены целесообразностью упрощения Фиг. 2 для повышения ее наглядности. Другими словами, все элементы и взаимосвязи, показанные в отношении L2-кэша 120, являются характерными для L2-кэша 220 и наоборот. Данный принцип справедлив и для описанной ниже Фиг. 3.

[28] L2-кэш 120 содержит хранилище 125 указываемых ячеек 126, которые способны сохранять данные, и хранилище 127 указывающих ячеек 128, которые способны сохранять идентификаторы данных, сохраненных в указываемых ячейках 126, при этом каждой указываемой ячейке 126 соответствует своя указывающая ячейка 128. В свою очередь, L2-кэш 220 содержит хранилище 225 указываемых ячеек 226 и хранилище 227 указывающих ячеек 228, назначение, взаимосвязи и принцип работы которых идентичны таковым у L2-кэша 120. Обратим внимание, что каждый из L2-кэшей 120 и 220 связан шиной 121 или 221 только со своим L1-кэшем 110 или 120, и способен выдавать данные, т.е. является доступным, только своему ядру 10 или 20 соответственно.

[29] L3-кэш 50 содержит хранилище 510 указываемых ячеек 511, которые способны сохранять данные, и хранилище 520 указывающих ячеек 521, которые способны сохранять идентификаторы данных, сохраненных в указываемых ячейках 511, при этом каждой указываемой ячейке 511 соответствует своя указывающая ячейка 521. Следует отметить, что указываемые ячейки 511 сохраняют широкий ряд данных, который однако, не обязательно включает в себя данные, сохраненные в указываемых ячейках 126 и 226 L2-кэшей 120 и 220. Тем временем L3-кэш 50 содержит хранилище 530 указывающих ячеек 531, которые способны сохранять идентификаторы данных, сохраненных в указываемых ячейках 126 и 226 L2-кэшей 120 и 220, и для которых в хранилище 510 указываемых ячеек 511 отсутствуют свои указываемые ячейки. Каждая указывающая ячейка 531 вместе с идентификатором данных способна сохранять адресный указатель, который указывает, в каком из L2-кэшей 120 и 220 сохранены данные, идентифицируемые сохраненным в данной указывающей ячейке 531 идентификатором.

[30] В режиме несжатых данных кэш-память 2 работает следующим образом (Фиг. 2 и 1). Когда L1-кэшу 110 требуется получить от L2-кэша 120 необходимые данные, L1-кэш 110 по шине 121 передает в L2-кэш 120 идентификатор необходимых данных, после чего L2-кэш 120 осуществляет поиск этого идентификатора (далее - искомый идентификатор) в указывающих ячейках 128. В случае нахождения искомого идентификатора в какой-либо из указывающих ячеек 128, L2-кэш 120 по шине 121 передает из хранилища 125 в L1-кэш 110 те данные, которые сохранены в указываемой ячейке 126, связанной с содержащей искомый идентификатор указывающей ячейкой 128.

[31] Если же L2-кэш 120 не находит искомый идентификатор в указывающих ячейках 128, то L2-кэш 120 по шине 123, входящей в состав шины 122, передает искомый идентификатор в L3-кэш 50, который производит поиск искомого идентификатора в указывающих ячейках 521. В случае нахождения искомого идентификатора в какой-либо из указывающих ячеек 521, L3-кэш 50 по шине 124, входящей в состав шины 122, передает из хранилища 510 в L2-кэш 120 те данные, которые сохранены в указываемой ячейке 511, связанной с содержащей искомый идентификатор указывающей ячейкой 521 посредством шины 515. Возможно также исполнение, когда L3-кэш 50 осуществляет передачу данных, соответствующих искомому идентификатору, из хранилища 510 сразу в L1-кэш 110 по шине 121, минуя L2-кэш 120.

[32] Если L3-кэш 50 не находит искомого идентификатора в указывающих ячейках 521, то L3-кэш 50 производит поиск искомого идентификатора в указывающих ячейках 531. Если L3-кэш 50 не находит искомого идентификатора и в указывающих ячейках 531, то L3-кэш 50 по шине 501 передает искомый идентификатор в оперативную память 60 для поиска данных в оперативной памяти 60. В случае нахождения искомого идентификатора в какой-либо из указывающих ячеек 531, L3-кэш 50 передает искомый идентификатор в тот L2-кэш, который соответствует адресному указателю, сохраненному в указывающей ячейке 531 вместе с искомым идентификатором. На Фиг. 2 указывающая ячейка 531, сохраняющая искомый идентификатор, содержит вместе с ним адресный указатель, соответствующий L2-кэшу 120, и L3-кэш 50 передает искомый идентификатор в L2-кэш 220 по шине 223, входящей в состав шины 222.

[33] L2-кэш 220 находит искомый идентификатор в одной из указывающих ячеек 228, определяет связанную с ней указываемую ячейку 226 (далее - исходная указываемая ячейка 226) и передает данные, сохраненные в исходной указываемой ячейке 226 по шине 224, входящей в состав шины 222, в L3-кэш 50, а точнее - в хранилище 510. Далее хранилище 510 сохраняет полученные от L2-кэша 220 данные в одной из указываемых ячеек 511 (далее - целевая указываемая ячейка 511), а хранилище 520 сохраняет искомый идентификатор в той указывающей ячейке 521, которая связана с целевой указываемой ячейкой 511 шиной 515. Если на момент поступления данных от L2-кэша 220 хранилище 510 не имеет свободных указываемых ячеек 511, то оно освобождает одну из занятых указываемых ячеек 511 путем вытеснения из нее сохраненных данных в оперативную память 60 по шине 501. После этого L3-кэш 50 передает данные, которые сохранены в целевой указываемой ячейке 511, из хранилища 510 в L2-кэш 120 по шине 124 или сразу в L1-кэш 110 по шине 121.

[34] Как следует из приведенного выше описания, при предоставлении какому-либо ядру 10, 20, 30 или 40 тех данных, которые сохранены в индивидуальном разделе кэш-памяти 2, принадлежащем другому ядру, функционирование кэш-памяти 2 в режиме несжатых данных сопряжено с передачей идентификаторов и данных между ее общим и индивидуальным разделами, а также с многократными поисками идентификаторов по хранилищам указывающих ячеек в общем и индивидуальном разделах. Данные факторы существенно увеличивают время выдачи кэш-памятью 2 в ядро 10, 20, 30 или 40 запрошенных им данных, если эти данные сохранены в индивидуальном разделе, принадлежащем другому ядру, что может существенно снизить производительность многоядерного процессора 1.

[35] Указанная техническая проблема успешно решена в многоядерном процессоре 1, кэш-память 2 которого способна сохранять несжатые и сжатые данные, т.е. способна работать в режиме сжатых данных. Следует отметить, что в кэш-памяти 2 режим сжатых данных является приоритетным по отношению к режиму несжатых данных, имеющему описанную выше узкую сферу применения, и может представлять собой режим, используемый по умолчанию.

[36] Блок-схема фрагмента кэш-памяти 2, иллюстрирующая работу кэш-памяти 2 в режиме сжатых данных, показана на Фиг. 3. Поскольку кэш-память 2 в предпочтительном ее исполнении способна функционировать как в режиме несжатых данных, так и в режиме сжатых данных, то фрагмент кэш-памяти 2, показанный на Фиг. 3, в значительной степени повторяет фрагмент кэш-памяти 2, показанный на Фиг. 2. Идентичные элементы на обеих фигурах обозначены одними и теми же позициями, при этом если не указано иное, то назначение, конструкция и функционирование этих идентичных элементов полностью совпадают, а их описание, приведенное выше в отношении Фиг. 2, в полной мере справедливо для Фиг. 3. В дальнейшем изложении будут представлены только те особенности кэш-памяти 2 с Фиг. 3, которые отличают ее от таковой с Фиг. 2, и которые позволяют обеспечить достижение заявленных технических результатов.

[37] Как и в описанном выше исполнении кэш-памяти 2, указываемые ячейки 126 и 226 L2-кэшей 120 и 220 способны сохранять только несжатые данные, что позволяет минимизировать время, требуемое на осуществление выдачи данных из L2-кэшей 120 и 220 в L1-кэши 110 или 120. Тем временем указываемые ячейки 511 и 512 L3-кэша 50 способны сохранять как несжатые, так и сжатые данные, для чего кэш-память 2 снабжена сжимающими и восстанавливающими модулями, такими как сжимающий модуль 231 на шине 224, передающей данные из L2-кэша 220 в L3-кэш 50, и восстанавливающий модуль 132 на шине 124, передающей данные из L3-кэша 50 в L2-кэш 120. Естественным образом кэш-память 2 также содержит не показанные на Фиг. 3 сжимающий и восстанавливающий модули, установленные соответственно на шине, передающей данные из L2-кэша 120 в L3-кэш 50, и шине, передающей данные из L3-кэша 50 в L2-кэш 220. Кроме того, кэш-память 2 содержит не показанные на Фиг. 3 сжимающий и восстанавливающий модули, установленные соответственно на шине 605, передающей данные из оперативной памяти 60 в L3-кэш 50, и шине 501, передающей данные из L3-кэша 50 в оперативную память 60.

[38] Вместе с тем возможно такое исполнение кэш-памяти 2, когда она содержит единый сжимающий модуль и единый восстанавливающий модуль. В этом случае единый сжимающий модуль сжимает данные, передаваемые по упомянутым шине 224, шине 605 и не показанной на Фиг. 3 шине, передающей данные из L2-кэша 120 в L3-кэш 50. В свою очередь единый восстанавливающий модуль восстанавливает данные, передаваемые по упомянутым шине 124, шине 501 и не показанной на Фиг. 3 шине, передающей данные из L3-кэша 50 в L2-кэш 220. Здесь обратим внимание, что понятия «сжимающий модуль» и «восстанавливающий модуль» отражают прежде всего функциональное содержание обозначаемых ими объектов, при этом техническая реализация этих объектов, обусловленная их функциональным содержанием, является очевидной для специалиста в данной области техники и может иметь различную конфигурацию.

[39] Как было отмечено выше, минимальным фрагментом информации, обрабатываемым кэш-памятью 2, является кэшлайн, представляющий собой массив целевых значений, который без применения сжатия данных, как правило, полностью занимает одну указываемую ячейку 126, 226 или 511. Соответственно, под термином «данные» в контексте настоящего изложения понимается именно кэшлайн, содержащий массив данных. В процессорах архитектуры «Эльбрус» последних поколений кэшлайн занимает 68 байт, и в этом случае такую же запоминающую емкость имеют и указываемые ячейки 126, 226 или 511.

[40] Изобретение не ограничивает выбор алгоритмов сжатия и восстановления данных, реализуемых сжимающим модулем 231 и восстанавливающим модулем 132, и в качестве используемых указанными модулями алгоритмов могут выступать, например алгоритмы сжатия и восстановления данных, раскрытые в упомянутой выше статье «Base-Delta-Immediate Compression: Practical Data Compression for On-Chip Caches». В общем случае предпочтение отдается тем алгоритмам сжатия и восстановления данных, которые позволяют обеспечить сжатие наибольшего числа кэшлайнов до половины или меньше от их исходного размера. Вместе с тем следует отметить, что ни один алгоритм сжатия не способен обеспечить гарантированное сжатие всех кэшлайнов, в результате чего даже после прохождения через сжимающий модуль 231 часть кэшлайнов подлежат сохранению в несжатом виде.

[41] Как показано на Фиг. 3, хранилище 510 содержит указываемые ячейки 511, способные сохранять кэшлайны в несжатом виде, и указываемые ячейки 512, условно разделенные на условно верхний и нижний участки 513 и 514, каждый из которых способен сохранять один кэшлайн в сжатом виде. Соответственно те кэшлайны, которые в хранилище 510 на Фиг. 2 размещались в указываемых ячейках 511, теперь в хранилище 510 на Фиг. 3 размещаются в указываемых ячейках 511 и верхних участках 513 указываемых ячеек 512. В свою очередь, указывающие ячейки 521, сохраняющие идентификаторы этих кэшлайнов, известные также как «тэги», теперь связаны как с оставшимися указанными ячейками 511, так и с верхними участками 513 указываемых ячеек 512. Обратим внимание на отсутствие конструктивных различий между указываемыми ячейками 511 и 512, и в зависимости от ситуации каждая указываемая ячейка 511 может переходить в статус указываемой ячейки 512 и наоборот.

[42] Таким образом, нижние участки 514 указываемых ячеек 512 остаются свободными, при этом они не имеют связанных с ними указывающих ячеек 521. Для использования этой возможности по увеличению объема сохраняемых в хранилище 510 данных, L3-кэш 50 снабжен шиной 516, связывающей хранилище 510 с хранилищем 530. Более точно, если число указывающих ячеек 531 больше или равно числу указывающих ячеек 521, то шина 516 связывает с указывающими ячейками 531 все нижние участки 514 указываемых ячеек 512, а если число указывающих ячеек 531 меньше числа указывающих ячеек 521, то шина 516 связывает с указывающими ячейками 531 только взятую по числу указывающих ячеек 531 часть из общего числа нижних участков 514 указываемых ячеек 512. Ввиду отмеченной выше равноценности указываемых ячеек 511 и 512, если количество указывающих ячеек 531 больше или равно количеству указывающих ячеек 521, то нижние участки по существу всех указываемых ячеек хранилища 510 оказываются связанными с указывающими ячейками 531.

[43] Благодаря такой конфигурации, из указываемых ячеек 126 и 226 в нижние участки 514 указываемых ячеек 512 могут быть скопированы кэшлайны, подвергнутые предварительному сжатию. Указывающие ячейки 531 продолжают сохранять идентификаторы этих кэшлайнов, однако, заменяют сохраняемые вместе с идентификаторами прежние адресные указатели, которые указывали на сохранение этих кэшлайнов в L2-кэше 120 и L2-кэше 220, на адресный указатель, указывающий на сохранение этих кэшлайнов в L3-кэше 50.

[44] Хотя в одной и той же указываемой ячейке 512 верхний участок 513 оказывается связанным с указывающей ячейкой 521, а нижний участок 514 - с указывающей ячейкой 531, связь указываемой ячейки 512 с указывающей ячейкой 521 имеет приоритет. Если в разделенную на верхний и нижний участки 513 и 514 указываемую ячейку 512 потребуется сохранить кэшлайн в несжатом виде, то связь нижнего участка 514 с указывающей ячейкой 531 прерывается, и указываемая ячейка 512 переходит в статус указываемой ячейки 511. Таким образом, в контексте используемой в настоящем изложении терминологии «своими» указывающими ячейками для указываемых ячеек хранилища 510 являются постоянно соединенные с ними указывающие ячейки 521 и наоборот, при этом указывающие ячейки 531, как и в описанном выше режиме несжатых данных, не имеют «своей» указываемой ячейки в хранилище 510.

[45] Следует отметить, что указываемые ячейки 126 и 226 продолжают сохранять скопированные из них кэшлайны, а указывающие ячейки 128 и 228 продолжают сохранять идентификаторы скопированных кэшлайнов, в результате чего кэшлайны, дублированные в более отдаленном от ядер 10 и 20 хранилище 510, представляют собой менее ценные данные по сравнению с данными, не имеющими дублирования. Исходя из этого перенесенные из указываемых ячеек 126 и 226 в хранилище 510 кэшлайны подлежат вытеснению из хранилища 510 в первоочередном порядке.

[46] В режиме сжатых данных кэш-память 2 работает следующим образом (Фиг. 3 и 1). Кэшлайны, поступающие в L3-кэш 50 либо по шинам 122 и 222 из L2-кэшей 120 и 220 в результате вытеснения более релевантным кэшлайном, либо по шине 605 из оперативной памяти 60 (Фиг. 1) в результате заблаговременного планирования, проходят через сжимающих модуль, такой как сжимающий модуль 231. Если результат сжатия был отрицательным, то кэшлайн сохраняется в указываемой ячейке 511, а если результат сжатия был положительным, то кэшлайн сохраняется в верхнем участке 513 указываемой ячейки 512, при этом идентификатор этого кэшлайна сохранятся в указывающей ячейке 521.

[47] Тем временем, когда новый кэшлайн вытесняет прежний кэшлайн из L2-кэша 220, то новый кэшлайн и новый идентификатор сохраняются вместо прежнего кэшлайна и прежнего идентификатора в указываемой ячейке 226 и указывающей ячейки 228. Одновременно с этим новый кэшлайн передается из указываемой ячейки 226, являющейся исходной указываемой ячейкой, по шине 224 через сжимающий модуль 231 в хранилище 510, и при положительном результате сжатия сохраняется в нижнем участке 514 целевой указывающей ячейки 512. Кроме того, идентификатор нового кэшлайна передается по шине 223 в хранилище 530, где он сохраняется указывающей ячейке 531, связанной с нижним участком 514 целевой указываемой ячейки 512. Отображение шин 223 и 224 при помощи пунктира иллюстрирует тот факт, что передача кэшлайна и его идентификатора из хранилищ 225 и 227 в хранилища 510 и 530 по шинам 223 и 224 осуществляется предварительно по отношению к моменту поиска кэшлайна по запросу от L2-кэша 120.

[48] Возвращаясь к осуществлению кэш-памятью 2 выдачи данных в ядро 10, далее будут описаны те особенности работы кэш-памяти 2 в режиме сжатых данных, которые отличают режим сжатых данных от описанного выше режима несжатых данных, при этом описание совпадающих особенностей будет опущено.

[49] Если L2-кэш 120 не находит искомый идентификатор в указывающих ячейках 128, то L2-кэш 120 по шине 123 передает искомый идентификатор в L3-кэш 50, который производит поиск искомого идентификатора в указывающих ячейках 521. В случае нахождения искомого идентификатора в какой-либо из указывающих ячеек 521, дальнейшие действия зависят от того, связана ли указывающая ячейка 521 с указываемой ячейкой 511 или с верхним участком 513 указываемой ячейки 512. Если указывающая ячейка 521 связана с указываемой ячейкой 511, то соответствующий искомому идентификатору кэшлайн, сохраненный в указываемой ячейкой 511 в несжатом виде, т.е. в исходном виде, напрямую передается L3-кэшем 50 по шине 124 в L2-кэш 120 или сразу в L1-кэш 110. Если же указывающая ячейка 521 связана с верхним участком 513 указываемой ячейки 512, то соответствующий искомому идентификатору кэшлайн, сохраненный в верхнем участке 513 указываемой ячейки 512 в сжатом виде, передается L3-кэшем 50 по шине 124 в восстанавливающий модуль 132, откуда восстановленный до исходного состояния кэшлайн передается в L2-кэш 120 или сразу в L1-кэш 110.

[50] Если L3-кэш 50 не находит искомого идентификатора в указывающих ячейках 521, то L3-кэш 50 производит поиск искомого идентификатора в указывающих ячейках 531. В случае нахождения искомого идентификатора в какой-либо из указывающих ячеек 531, L3-кэш 50 определяет значение сохраненного вместе с ним адресного указателя, при этом поскольку все или почти все кэшлайны, сохраняемые в указываемых ячейках 126 и 226, скопированы в нижние участки 514 указываемых ячеек 512, то с очень большой вероятностью адресный указатель имеет значение, указывающее на L3-кэш 50. Данное обстоятельство является следствием того, что даже половина хранилища 510 имеет запоминающую емкость, значительно превышающую суммарную запоминающую емкость хранилищ 125 и 225. Далее соответствующий искомому идентификатору кэшлайн, сохраненный в сжатом виде в том нижнем участке 514 указываемой ячейки 512, который связан с сохраняющей искомый идентификатор указывающей ячейкой 531, передается L3-кэшем 50 по шине 124 в восстанавливающий модуль 132, откуда восстановленный до исходного состояния кэшлайн передается в L2-кэш 120 или сразу в L1-кэш 110.

[51] Одновременно с этим сохраняется весьма малая вероятность такой ситуации, когда при нахождении искомого идентификатора в какой-либо из указывающих ячеек 531, сохраненный вместе с ним адресный указатель имеет значение, указывающее на L2-кэш 220. В этом случае L2-кэш 220 передает кэшлайн, соответствующий искомому идентификатору, в хранилище 510, минуя при этом сжимающий модуль 231 и при необходимости замещая подлежащий вытеснению кэшлайн в указываемой ячейке 511, т.е. аналогично тому, как было описано выше. Далее L3-кэш 50 передает данный кэшлайн, находящийся в несжатом виде, напрямую в L2-кэш 120 или сразу в L1-кэш 110.

[52] Возможность практической реализации кэш-памяти 2, способной функционировать в режиме сжатых данных, может быть проиллюстрирована следующим примером. Многочисленные эксперименты показали, что в отношении большинства приложений эффективность сжатия данных составляет около 25%, т.е. данные, в несжатом виде занимающие 1 Мбайт, после сжатия потребуют примерно 0,75 Мбайт запоминающей емкости. В многоядерном процессоре Эльбрус-8С L3-кэш при его максимальном заполнении способен сохранять данные в объеме 16 Мбайт информации, и в результате сжатия этих данных для их сохранения потребуется 16*0,75=12 Мбайт запоминающей емкости. Тем временем максимальный совокупный объем данных, который могут вместить в себя L2-кэши многоядерного процессора Эльбрус-8С, составляет 8*0,512=4,096 Мбайт, и после сжатия этих данных для их сохранения потребуется 4,096*0,75=3,072 Мбайт запоминающей емкости. Поскольку сжатие изначально сохраняемых в L3-кэше данных высвобождает 16-12=4 Мбайт запоминающей емкости, то L3-кэш даже с некоторым запасом способен вместить в себя все содержащиеся в L2-кэшах данные при условии их предварительного сжатия.

[53] Как следует из вышеизложенного, кэш-память 2, выполненная с возможностью функционирования в режиме сжатых данных, способна заблаговременно копировать в L3-кэш данные, сохраненные в L2-кэшах других ядер, не сопровождая это вытеснением исходно сохраняемых в L3-кэше данных. Благодаря этому время, требуемое на передачу в ядра 10, 20, 30 и 40 многоядерного процессора 1 тех данных, которые сохранены в L2-кэшах других ядер, существенно сокращается, что естественным образом увеличивает производительность многоядерного процессора 1.

Изобретение относится к вычислительной технике. Технический результат заключается в сокращении времени, требуемого на передачу в ядра многоядерного процессора тех данных, которые сохранены в индивидуальных разделах кэш-памяти, принадлежащих другим ядрам. Многоядерный процессор, снабженный кэш-памятью, которая включает в себя общий раздел и индивидуальные разделы по количеству ядер, при этом каждый из общего раздела и индивидуальных разделов содержит указываемые ячейки и указывающие ячейки, при этом указываемые ячейки общего раздела способны сохранять данные в несжатом или в сжатом виде, а указываемые ячейки индивидуальных разделов способны сохранять данные в несжатом виде, при этом каждая указывающая ячейка общего раздела, не имеющая своей указываемой ячейки, вместе с идентификатором данных способна сохранять адресный указатель, причем кэш-память способна переносить данные из исходной указываемой ячейки индивидуального раздела в участок целевой указываемой ячейки общего раздела и способна сохранять перенесенные данные в участке целевой указываемой ячейки общего раздела в сжатом виде, а указывающая ячейка общего раздела способна вместе с ним сохранять адресный указатель, указывающий на сохранение данных в общем разделе. 2 з.п. ф-лы, 3 ил.

1. Многоядерный процессор, снабженный кэш-памятью, которая включает в себя общий раздел и индивидуальные разделы по количеству ядер, причем общий раздел доступен всем ядрам, а каждый индивидуальный раздел доступен только своему ядру, при этом

каждый из общего раздела и индивидуальных разделов содержит указываемые ячейки, способные сохранять данные, и указывающие ячейки, способные сохранять идентификаторы данных, сохраненных в указываемых ячейках, причем каждой указываемой ячейке любого раздела соответствует своя указывающая ячейка этого же раздела, при этом

указываемые ячейки общего раздела способны сохранять данные в несжатом или в сжатом виде, а указываемые ячейки индивидуальных разделов способны сохранять данные в несжатом виде, при этом

каждая указывающая ячейка общего раздела, не имеющая своей указываемой ячейки, вместе с идентификатором данных способна сохранять адресный указатель, который указывает, в каком из разделов сохранены данные, идентифицируемые сохраненным в данной указывающей ячейке идентификатором, причем

кэш-память способна переносить данные из исходной указываемой ячейки индивидуального раздела в участок целевой указываемой ячейки общего раздела и способна сохранять перенесенные данные в участке целевой указываемой ячейки общего раздела в сжатом виде, а

указывающая ячейка общего раздела, сохраняющая идентификатор переносимых данных, способна вместе с ним сохранять адресный указатель, указывающий на сохранение данных в общем разделе.

2. Процессор по п. 1, в котором при сохранении данных в сжатом виде участок указываемой ячейки общего раздела занимает не больше половины указываемой ячейки.

3. Процессор по п. 1, в котором исходная указываемая ячейка индивидуального раздела сохраняет копию данных, перенесенных в участок целевой указываемой ячейки общего раздела для сохранения в сжатом виде, при этом эти перенесенные данные подлежат вытеснению из общего раздела в первоочередном порядке.

| US 20070245097 A1, 18.10.2007 | |||

| US 20140189239 A1, 03.07.2014 | |||

| US 11151033 B1, 19.10.2021 | |||

| US 20120151146 A1, 14.06.2012 | |||

| US 20140033217 A1, 30.01.2014 | |||

| СПОСОБ ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ И УСТРОЙСТВО ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ | 2014 |

|

RU2592465C2 |

Авторы

Даты

2025-03-25—Публикация

2024-08-29—Подача