Область техники, к которой относится изобретение

Настоящее раскрытие относится к опорной и ограничивающей архитектуре в массиве памяти с узлами пересечения.

Уровень техники

Запоминающее устройство на фазовых переходах представляет собой устройство памяти, в котором обычно используется халькогенидный материал для элементов памяти. Элемент памяти представляет собой модуль, в котором фактически содержится информация. Во время работы память на фазовых переходах хранит информацию в элементе памяти путем изменения фазы элемента памяти между аморфной и кристаллической фазами. Халькогенидный материал может представлять либо кристаллическую, или аморфную фазу, проявляя низкую или высокую электропроводность. В общем, аморфная фаза имеет низкую электропроводность (высокий импеданс) и ассоциирована с состоянием сброса (логический ноль), и кристаллическая фаза имеет высокую электропроводность (низкий импеданс) и ассоциируется с установленным состоянием (логическая единица). Элемент памяти может быть включен в ячейку памяти, которая также включает в себя селектор, то есть, устройство выбора, соединенное с элементом памяти. Устройства выбора выполнены с возможностью способствовать комбинированию множества элементов памяти в массив.

Элементы памяти на фазовых переходах могут быть размещены в виде массива памяти с узлами пересечения, включающими в себя адресные линии ряда и адресные линии столбца, размещенные в виде сетки. Адресные линии ряда и адресные линии столбца, называемые линиями слова (WL) и линиями битов (BL), соответственно, пересекаются при формировании сетки, и каждая ячейка памяти соединена между WL и BL, где WL и BL пересекаются (то есть, в узлах пересечения). Следует отметить, что ряды и столбцы представляют собой термины, используемые для удобства, для обеспечения качественного описания размещения WL и BL в памяти с узлами пересечения.

Во время операции программирования фаза элемента памяти может изменяться при приложении первого напряжения смещения к WL и второго напряжения смещения к BL, в результате чего, возникает дифференциальное напряжение смещения на ячейке памяти, что может вызвать протекание тока в элементе памяти. Дифференциальное напряжение смещения может поддерживаться на ячейке памяти в течение первого периода времени, достаточного для того, чтобы элемент памяти быстро "выполнил скачкообразный переход", и затем поддерживается в течение второго периода времени для перехода элемента памяти из аморфного состояния в кристаллическое состояние или из кристаллического состояния в аморфное состояния. Скачкообразный переход представляет собой свойство композитного элемента памяти, который приводит к резкому изменению электропроводности и ассоциированному резкому изменению напряжения на элементе памяти.

При операции считывания целевую ячейку памяти выбирают путем приложения первого напряжения смещения к WL и второго напряжения смещения к BL, которые пересекаются в целевой ячейке памяти в течение определенного интервала времени. Получаемое в результате дифференциальное напряжение смещения на элементе памяти конфигурируют так, чтобы оно было выше, чем максимальное напряжение установки, и ниже, чем минимальное напряжение сброса для элемента памяти. В ответ на это целевой элемент памяти может выполнять скачкообразный переход или может не выполнять скачкообразный переход, в зависимости от того, находится ли элемент памяти в кристаллическом состоянии (установленном состоянии) или аморфном состоянии (состоянии сброса). Цепи опроса (включая в себя узел опроса), соединенный с элементом памяти, выполнены с возможностью детектирования присутствия или отсутствия скачкообразного перехода в течение интервала времени опроса. Наличие скачкообразного перехода может затем быть интерпретировано, как логическая единица и отсутствие скачкообразного перехода, как логический ноль.

Краткое описание чертежей

Свойства и преимущества заявленного предмета изобретения будут понятны из следующего подробного описания вариантов осуществления, последовательно изложенных здесь, и это описание следует рассматривать со ссылкой на приложенные чертежи, на которых:

на фиг. 1 показана блок-схема системы, в соответствии с несколькими вариантами осуществления настоящего раскрытия;

на фиг. 2А показана часть системы памяти с узлами пересечения, в соответствии с различными вариантами осуществления настоящего раскрытия;

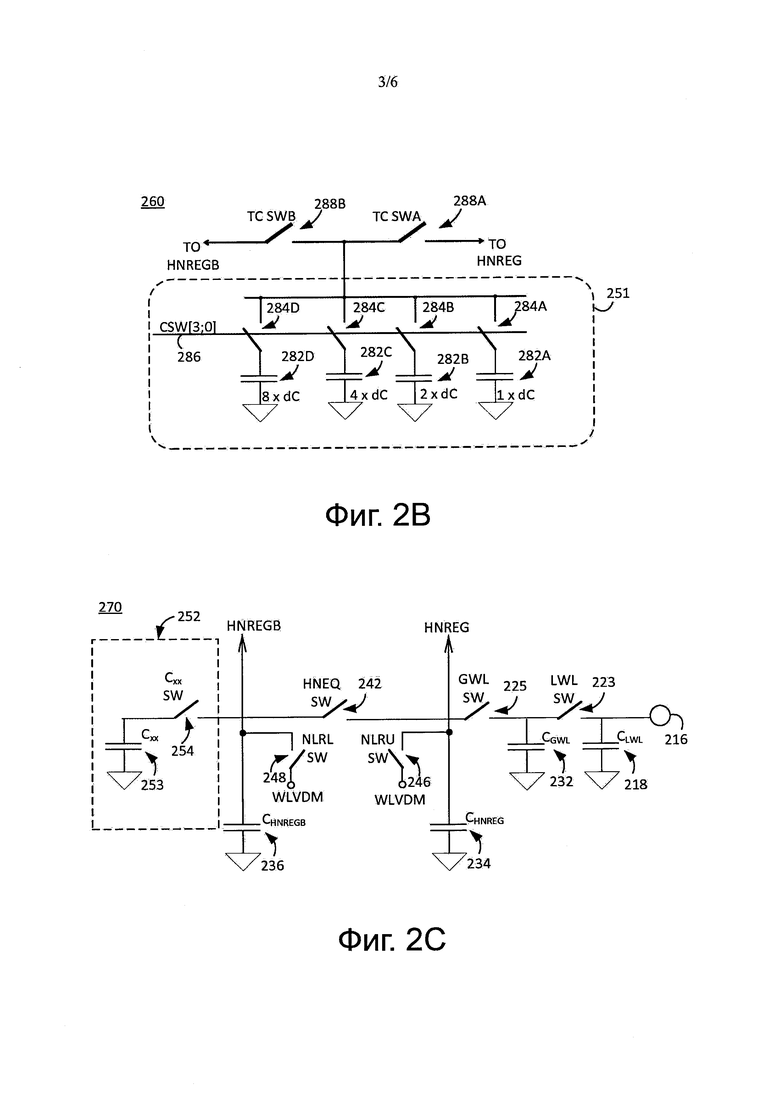

на фиг. 2В показана цепь двоично-взвешенного настроечного конденсатора в качестве примера, в соответствии с одним вариантом осуществления настоящего раскрытия;

на фиг. 2С показана упрощенная схема, поясняющая собственные емкости и емкость регулирования опорного напряжения, в соответствии с различными вариантами осуществления настоящего раскрытия;

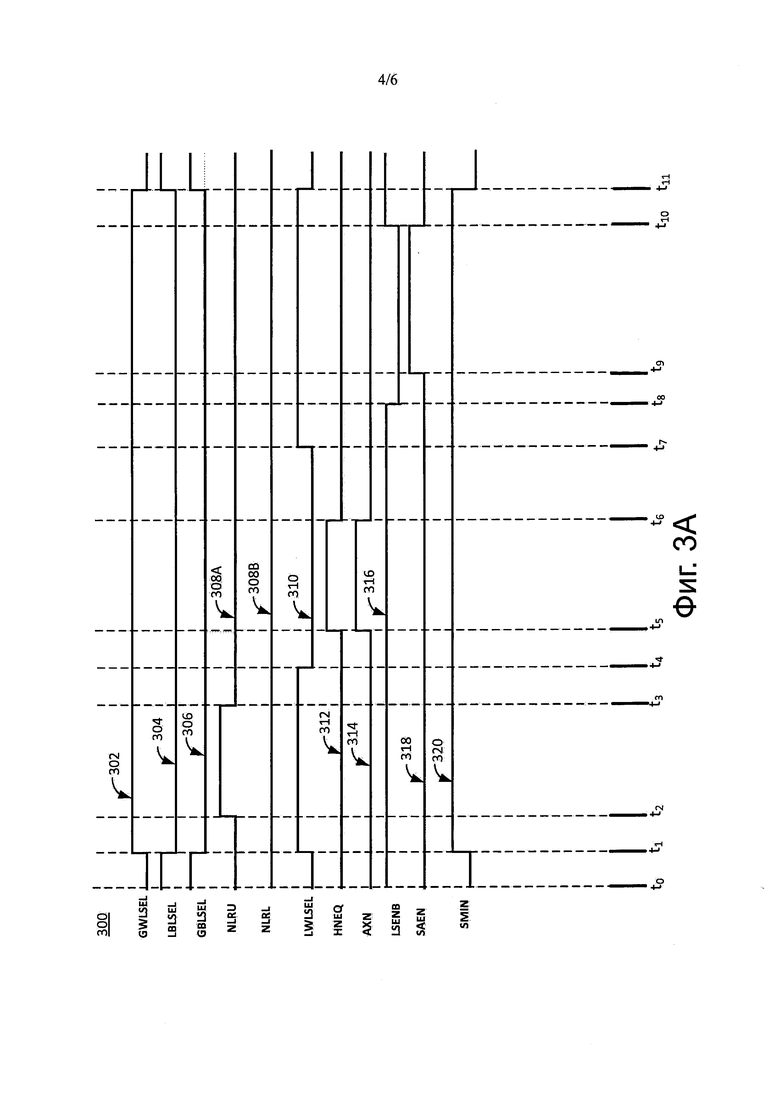

на фиг. 3А показана временная диаграмма, которая иллюстрирует пример операции считывания памяти системы памяти с узлами пересечения по фиг. 2А;

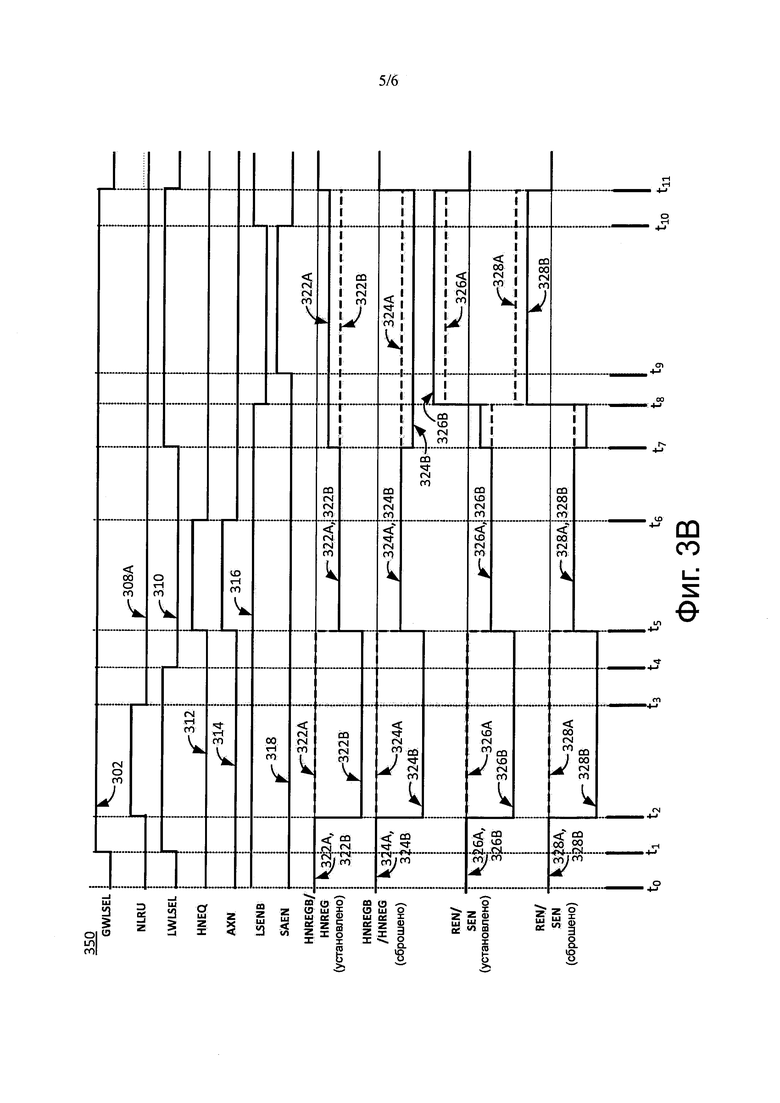

на фиг. 3В показана временная диаграмма, которая иллюстрирует пример напряжения опроса и опорного напряжения, и входные напряжения усилителя опроса для установки и сброса элементов памяти для операций считывания памяти в системе памяти с узлами пересечения по фиг. 2А; и

на фиг. 4 показана блок-схема последовательности операций для формирования опорного напряжения памяти с узлами пересечения в соответствии с различными вариантами осуществления настоящего раскрытия.

Хотя следующее подробное описание будет представлено со ссылкой на иллюстративные варианты осуществления, множество альтернатив, модификаций и их различий будут понятны для специалиста в данной области техники.

Осуществление изобретения

Во время операции считывания цепь опроса выполнена с возможностью детектирования, произошел или нет скачкообразный переход на основе, по меньшей мере, частично, протекает ли ток через элемент памяти. Ток может быть детектирован по изменению заряда, детектируемому, как изменение напряжения в локальной линии слова (FWF). Изменение напряжения может быть относительно малым, и его обычно определяют относительно опорного напряжения. Генерируемое снаружи опорное напряжение требует наличия электропроводных линий от опорного источника напряжения в цепь опроса для подачи опорного напряжения в цепь опроса. Электропроводные линии могут при этом увеличивать в размер всего массива памяти. Генерирование опорного напряжения дополнительно увеличивает потребление энергии массивом памяти.

В общем, в данном раскрытии описаны система и способ, выполненные с возможностью локального получения опорного напряжения для считывания элементов памяти. Система и способ, выполнены с возможностью использования собственных емкостей, взаимосвязанных с локальной WL и глобальной WL, емкости первой цепи опроса, например, емкости линий, соединяющих WL с цепью опроса, и напряжения смещения, прикладываемого, в части операции доступа к памяти. Напряжение смещения заряжает собственные емкости. Полученный в результате заряд собственных емкостей может затем использоваться для получения опорного напряжения. Значение опорного напряжения основано, по меньшей мере, частично, на относительных значениях собственных емкостей, включая, например, емкость второй цепи опроса, как описано здесь. В варианте осуществления не выбранная глобальная WL из невыбранной соседней части памяти может быть соединена с цепью опроса, при условии наличия регулирующей емкости, сконфигурированной для регулирования опорного напряжения, как описано здесь. В другом варианте осуществления настроечная цепь конденсатора может предоставлять дополнительную емкость (то есть, регулировочную емкость), выполненную с возможностью получения требуемого опорного напряжения. Например, настроечная цепь конденсатора может соответствовать двоично-взвешенному настроечному конденсатору, выполненному с возможностью предоставления избирательных емкостей, которые имеют значение, кратное номинальной емкости. Кратность определяется двоичным значением селектора, приложенным к двоично-взвешенному конденсатору. Опорное напряжение можно регулировать путем изменения значения двоичного селектора. Например, опорное напряжение можно регулировать для оптимизации зазора опроса между максимальным установленным напряжением и минимальным напряжением сброса для элемента памяти.

Система и способ могут дополнительно включать в себя усилитель опроса. Опорное напряжение прикладывается к первому входу, и напряжение опроса, взаимосвязанное с опорным напряжением, и вывод выбранного элемента памяти (то есть, детектируемое напряжение элемента памяти) прикладывают ко второму входу усилителя опроса. Первый вход и второй вход усилителя опроса могут быть соединены перед приложением напряжения опроса для получения опорного напряжения. Такое соединение может усилить обрезку шумов, благодаря формированию синфазных шумов на первом входе и на втором входе. Усилитель опроса может затем обеспечивать нечувствительность к шумам (то есть, подавление синфазных шумов), когда первый вход и второй вход отключают, и напряжение опроса прикладывают ко второму входу. Усилитель опроса выполнен с возможностью приема напряжения опроса и опорного напряжения и для предоставления выхода на логическом уровне, то есть, логической единицы или логического нуля, в соответствии с Vcc или Vss, на основе, по меньшей мере, частично, на относительных значениях опорного напряжения и напряжения зондирования. Например, Vcc может иметь значение 1,2 вольт, и Vss может соответствовать земле (то есть, ноль вольт).

В дальнейшем описаны технологии для формирования локального опорного напряжения и выхода опроса элемента памяти со ссылкой на линии слова. Аналогичные технологии могут использовать для формирования локальных опорных напряжений и опроса элемента в памяти в памяти с узлами пересечения для линий битов, в соответствии с настоящим раскрытием.

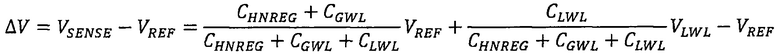

На фиг. 1 иллюстрируется блок-схема системы 100 в соответствии с несколькими вариантами осуществления настоящего раскрытия. Система 100 включает в себя процессор 102, контроллер 104 памяти и массив 106 памяти. Процессор 102 соединен с контроллером памяти 104 по шине 108. Процессор 102 может предоставлять запросы считывания и/или записи, включающие в себя адрес (адреса) памяти, и/или ассоциированные данные в контроллер 104 памяти и может принимать считанные данные из контроллера 104 памяти. Контроллер 104 памяти выполнен с возможностью выполнения операции доступа к памяти, например, считывания целевой ячейки памяти и/или записи в целевую ячейку памяти. Следует отметить, что система 100 представлена упрощенной для простоты иллюстрации и описания.

Массив 106 памяти соответствует, по меньшей мере, части памяти с узлами пересечения на фазовых переходах, и включает в себя множество линий 115 слова, множество линий 117 битов и множество ячеек памяти, например, ячеек памяти 107. Каждая ячейка памяти соединена между линией слова ("WL") и линией битов ("BL") в узле пересечения WL и BL. Каждая ячейка памяти включает в себя элемент памяти, выполненный с возможностью сохранения информации, и может включать в себя устройство выбора ячейки памяти (то есть, селектор), соединенный с элементом памяти. Устройства переключения могут включать в себя аморфно-полупроводниковые пороговые переключатели, диоды, транзисторы с биполярными переходами, полевые транзисторы и т.д. Массив 106 памяти выполнен с возможностью сохранения двоичных данных, и в нем можно выполнять запись (то есть, программировать) или считывать из него данные.

Контроллер 104 памяти включает в себя логику 110 контроллера памяти, схему 114 управления WL и логику 116 управления BL. Логика 110 контроллера памяти выполнена с возможностью выполнения операций, ассоциированных с контроллером 104 памяти. Например, логика 110 контроллера памяти может управлять связью с процессором 102. Логика 110 контроллера памяти может быть выполнена с возможностью идентификации одной или больше целевых WL, ассоциированных с каждым принятым адресом памяти. Логика 110 контроллера памяти может быть выполнена с возможностью управления работой логики 114 управления WL и логики 116 управления BL по меньшей мере частично на основе идентификаторов целевых WL.

Логика 114 управления WL включает в себя схему 120 переключения WL, и схему 122 опроса. Логика 114 управления WL выполнена с возможностью приема целевого адреса (адресов) WL из логики 110 контроллера памяти и выбора одной или больше WL для операций считывания и/или записи. Например, логика 114 управления WL может быть выполнена с возможностью выбора целевой WL путем подключения напряжения смещения выбора WL к целевой WL. Логика 114 управления WL может быть выполнена с возможностью отмены выбора WL путем отсоединения целевой WL от напряжения смещения выбора WL и/или путем подключения напряжения смещения отмены выбора WL к WL. Логика 114 управления WL может быть соединена с множеством WL 115, включенных в массив 106 памяти. Каждая WL может быть соединена с множеством ячеек памяти, соответствующих количеству BL 117. Схема 120 переключения WL может включать в себя множество переключателей, каждый переключатель выполнен с возможностью подключения (или отсоединения), соответствующей WL, например, WL 115а, к напряжению смещения выбора для выбора соответствующей WL 115а. Например, схема 120 переключения может включать в себя множество транзисторов.

Логика 116 управления BL включает в себя цепь 124 коммутатора BL. В некоторых вариантах осуществления логика 116 управления BL может включать в себя цепи опроса, например, цепь 122 опроса. Логика 116 управления BL выполнена с возможностью выбора одной или больше BL для операций считывания и/или записи. Логика 116 управления BL может быть выполнена с возможностью выбора целевой BL путем подключения напряжения смещения выбора BL (Vpp) к целевой BL. Например, Vpp может иметь значение 5,0 вольт. Логика 116 управления BL может быть выполнена с возможностью отмены выбора BL путем отсоединения целевой BL от напряжения смещения выбора BL и/или путем подключения напряжения смещения отмены выбора BL к BL. Цепь 124 коммутатора BL аналогична цепи 120 коммутатора WL, за исключением того, что цепь 124 коммутатора BL выполнена с возможностью подключения напряжения смещения выбора BL к целевой BL.

Цепи 122 опроса выполнены с возможностью детектирования наличия или отсутствия события скачкообразного перехода во время интервала опроса, например, во время операции считывания. Цепи 122 опроса выполнены с возможностью предоставления выхода на логическом уровне, связанного с результатом операции считывания, например, в контроллер 110 памяти. Например, логический уровень, соответствующий логической единице, может быть выведен, если будет детектирован скачкообразный переход, и логический уровень, соответствующий логическому нулю, может быть выведен, если скачкообразный переход не будет детектирован.

Например, в ответ на сигнал из логики 110 контроллера памяти, логика 114 управления WL и логика 116 управления BL могут быть выполнены с возможностью выбора целевого элемента памяти, например, элемента 107 памяти для операции считывания путем подключения WL 115а к напряжению смещения выбора WL и BL 117а к напряжению смещения выбора BL. Цепи 126 опроса могут затем быть выполнены с возможностью отслеживания WL 115а и/или BL 117а в течение интервала опроса для определения, произошло или нет событие скачкообразного перехода. Если схема 126 опроса детектирует событие скачкообразного перехода, тогда элемент 107 памяти может находиться в установленном состоянии. Если цепь 126 опроса не детектирует событие скачкообразного перехода в интервале опроса, то элемент 107 памяти может находиться в состоянии сброса.

Таким образом, логика 114 управления WL и/или логика 116 управления BL могут быть выполнены с возможностью выбора целевого элемента памяти для операции считывания, инициирования операции считывания, отслеживания, выбранного элемента памяти, не произошло в нем событие скачкообразного перехода в течение интервала опроса и предоставления результата опроса, например, в логику 110 контроллера памяти.

На фиг. 2А иллюстрируется часть 200 системы памяти с узлами пересечения, в соответствии с различными вариантами осуществления настоящего раскрытия. Часть 200 включает в себя BL и WL, которые пересекаются в элементе 216 памяти. Часть 200 дополнительно включает в себя цепь 210 смещения BL, схему 220 коммутатора BL, схему 222 коммутатора локальной WL (LWL), схему 224 коммутатора WL (GWL) и схему 230 опроса. В некоторых вариантах осуществления часть 200 может включать в себя коммутатор 225 GWLB, выполненный с возможностью представления соседней части массива памяти. Например, цепь 210 смещения BL и цепь 220 переключения BL могут быть включены в логику 116 управления BL, и цепь 222 переключения LWL, цепь 224 переключения GWL и переключатель 225 GWLB, могут быть включены в логику 114 управления WL. Цепь 230 опроса представляет собой пример цепи 122 опроса на фиг. 1.

Цепь 210 смещения BL соединена с источником Vpp напряжения и с цепью 220 переключения BL.

Цепь 220 переключения BL дополнительно соединена с элементом 216 памяти по локальной BL 214. Цепь 222 переключения LWL соединена с элементом 216 памяти по LWL 212 и с цепью 224 переключения GWL по GWL 213. Цепь 224 переключения GWL дополнительно соединена с цепью 230 опроса. Цепь 222 переключения LWL выполнена с возможностью выбора LWL, например, LWL 212, и соединения выбранной LWL 212 с цепью 224 GWL. Цепь 224 переключения GWL выполнена с возможностью подключения выбранной LWL, например, LWL 212, и GWL 213 к цепи 230 опроса в течение, например, операции считывания элемента памяти.

Часть 200 дополнительно включает в себя множество входов управления. Например, VDM действует, как сигнал управления, подаваемый в цепь 210 смещения BL. Например, VDM может иметь номинальное значение 4,0 вольта. Когда VDM увеличивается выше порогового значения, и выход AXN цепи 210 смещения BL может стать BLVDM, который относится к VDM, как BLVDM ~ VDM - VTn, где VTn представляет собой пороговое напряжение переключателя, управляемого VDM, и включенного в цепь 210 смещения BL. В другом примере GBLSEL представляет собой сигнал выбора GBL (глобальная BL). GBLSEL имеет активный низкий уровень, что означает, что GBL соединенную с цепью 220 переключения BL, выбирают, когда GBLSEL имеет низкое значение, и не выбирают, когда GBLSEL имеет высокое значение". Низкое" и "высокое" в данном контексте относится к логическим уровням и могут быть взаимосвязаны с напряжением, например, низкое может соответствовать земле (например, Vss) и высокое может соответствовать ненулевому положительному напряжению (например, Vcc=1,2 вольта). LBLSEL представляет собой сигнал выбора LBL (локальной BL) и имеет активное низкое значение. Когда, как GBLSEL, так и LBLSEL имеют низкое напряжение, LBL 214 соединена с AXN. LWLSEL (выбор локальной WL) выполнен с возможностью управлять соединением LWL 212 с GWL 213, и GWLSEL выполнен с возможностью управлять соединением GWL 213 с цепью 230 опроса. В некоторых вариантах осуществления цепь 224 переключения GWL и цепь 222 переключения LWL включает в себя цепи с отменой выбора, выполненные с возможностью соединения GWL 213 и/или LWL 212 с Vss, если они не выбраны. В этих вариантах осуществления GWLDES и LWLDES выполнены с возможностью управления соединением GWL 213 и LWL 212, соответственно, с Vss.

Часть 200 включает в себя собственную емкость LWL 218 со значением емкости CLWL, соединенную с LWL 212, и собственную емкость 232 GWL со значением емкости CGWL, соединенную с GWL 213. Собственные емкости 218, 232 соответствуют собственным емкостям, взаимосвязанным с LWL 212 и GWL 213, соответственно. Используемый здесь термин собственная емкость представляет собой емкость, которая существует в цепи (например, в проводящей дорожке и/или в переключателях), а не емкость, взаимосвязанную с конденсатором (то есть, дискретным элементом), который может быть добавлен к цепи. Таким образом, хотя емкости 218 и 232 показаны соединенными с LWL 212 и GWL 213, соответственно, емкости 218 и 232 не являются дискретными элементами. Емкость 218 соответствует собственной емкости LWL 212, и емкость 232 соответствует собственной емкости GWL213.

В вариантах осуществления, которые включают в себя переключатель 225 GWLB, часть 200 может также включать в себя собственную емкость 233 GWLB со значением емкости, CGWLB. Емкость 233 выполнена с возможностью представления емкости, взаимосвязанной с GWL, включенной в другую часть массива памяти, которая может совместно использовать (например, мультиплексировать) цепь 230 опроса. Емкость 233 может быть выбрана переключателем 225 GWLB. В данных вариантах осуществления емкость 233 может использоваться, как регулировочная емкость для регулирования опорного напряжения для цепи 230 опроса, которая основана, по меньшей мере, частично, на собственных емкостях 232, 234, 236, как описано здесь. Использование емкости 233, в качестве регулировочной емкости, может улучшить подавление шумов путем предоставления относительно лучше согласованного компонента шумов, который затем может быть подавлен, например, усилителем опроса.

Схема 230 опроса включает в себя усилитель 240 опроса, переключатель 242 HNEQ, блок переключателей 244А.., 244n, совместно называемый блоком 244 переключателей, переключатель 246 NLRU и переключатель 248 NLRL. Схема 230 опроса включает в себя первую емкость 234 схемы опроса с емкостью CHNREG и вторую емкость 236 схемы опроса с емкостью CHNREGB-234, емкости 234, 236 представляют собственную емкость схемы между цепью 224 переключателя GWL и переключателем 246 считывания верхней части без ограничений (NLRU) и между GWLB SW 225 и переключателем 248 считывания нижней части без ограничений (NLRL), соответственно. Здесь верхняя и нижняя относятся к частям массива памяти, например, массиву 106 памяти на фиг. 1.

В некоторых вариантах осуществления схема 230 опроса может включать в себя схему 250 настроечного конденсатора и переключателей ТС SWA 288А и ТС SWB 288В настроечного конденсатора. ТС SWA 288А выполнен с возможностью подключения цепи 250 настроечного конденсатора к узлу HNREG. ТС SWB 288В выполнен с возможностью подсоединения цепи 250 настроечного конденсатора к узлу HNREGB. Переключатели 288А, 288В выполнены с возможностью помогать использованию цепи 250 настроечного конденсатора с более, чем одной частью массива 106 памяти. Например, ТС, SWA 288А может быть разомкнут, и ТС SWB 288В может быть замкнут для подключения цепи 250 настроечного конденсатора к HNREGB, для регулирования емкости, подключенной к HNREGB, как описано здесь. В этом первом примере элемент 216 памяти может быть выбран для операции доступа к памяти. В другом примере ТС SWA 288А может быть замкнут и ТС SWB 288В может быть разомкнут для соединения цепи 250 настроечного конденсатора с HNREG, для регулирования емкости, соединенной с HNREG. В этом втором примере элемент памяти на соседнем участке памяти может быть выбран для операции доступа к памяти. Другими словами, цепь 250 настроечного конденсатора может быть соединена с узлом HNREGB или узлом HNREG, но не с обоими ими. Цепь 250 настроечного конденсатора может затем использоваться для регулирования VREF, как описано здесь. Совместное использование цепи 250 настроечного конденсатора позволяет освободить область кристалла.

Усилитель 240 опроса включает в себя два входа, при этой первый вход SA1, соединен с узлом HNREGB и второй вход SA2 соединили к узлу HNREG. Переключатель 242HNEQ, подключен между узлами HNREGB и HNREG. Блок 244 переключателей включает в себя множество переключателей 244А…, 244n, выполненных с возможностью индивидуального подключения и отсоединения узла HNREG и/или HNREGB к или от Vss. Переключатели 244А.. 244n управляются сигналом SMIN управления. SMIN является активным низким сигналом, таким образом, переключатели 244А.. 244n замкнуты, когда SMIN имеет низкое значение, и разомкнуты, когда SMIN имеет высокое значение. Переключатель 246 NLRU подключен между напряжением WLVDM питания и узлом HNREG, и переключатель 248 NLRL подключен между напряжением WLVDM источника питания и узлом HNREGB. Например, WLVDM может иметь номинальное значение -3,6 вольта. Первая емкость 234 цепи опроса соединена с узлом HNREG, и вторая емкость 236 цепи опроса соединена с узлом HNREGB. Цепь 224 переключателя GWL соединена с узлом HNREG, и GWLB SW 225 может быть соединен с узлом HNREGB. Цепь 250 настроечного конденсатора может быть соединена с узлом HNREG по ТС SWA 288А или с узлом HNREGB по ТС SWB 288В, как описано здесь.

Переключатель 242 HNEQ, имеет вход HNEQ управления и выполнен с возможностью соединения или отсоединения узла HNREG с/от узла HNREGB. Переключатель 246 NLRU переключают и переключатель 248 NLRL каждый имеет соответствующий вход управления: NLRU и NLRL. Переключатель 246 NLRU выполнен с возможностью соединения узла HNREG с WLVDM и переключатель 248 NLRL выполнен с возможностью соединения узла HNREGB с WLVDM.

Усилитель 240 опроса может включать в себя два переключателя 247, 249, Каскад 1 первого каскада SA и Каскад 2 второго каскада SA. Усилитель 240 опроса соединен, по меньшей мере, с одним напряжением питания, Vcc (питание на логическом уровне), и может быть соединен с Vss, то есть, заземлен. Усилитель 240 опроса дополнительно включает в себя два входа управления и SAEN. Переключатель 247 выполнен с возможностью соединения узла SA2 и, таким образом, узла HNREG с SEN, входом в SA Каскада 1. Переключатель 249 выполнен с возможностью соединения узла SA1 и, таким образом, узла HNREGB с REN, другим входом в SA Каскада 1. В некоторых вариантах осуществления узлы REN и SEN также могут быть соединены со входами SA Каскада 2. Переключатели 247, 249 являются переключателями с активным высоким уровнем, управляемые LSENB, таким образом, когда LSENB имеет высокий уровень, HNREGB соединен с REN, и HNREG соединен с SEN. LSENB дополнительно соединен с SA Каскада 1 и представляет собой активный низкий сигнал, выполненный с возможностью включения SA Каскада 1. Таким образом, SA Каскада 1 включается, когда LSENB имеет низкий уровень, и отключается, когда LSENB имеет высокий уровень, как описано здесь. SAEN выполнен с возможностью включения SA Каскада 2. Во время работы, когда SA Каскада 2 включен, выход считывания памяти устройства может быть предоставлен в узел опроса.

Усилитель 240 опроса может включать в себя любой тип усилителя опроса, выполненный с возможностью приема отрицательных входных напряжений (например, опорного напряжения и напряжения опроса) и генерирования напряжения логического уровня, выводимого в то время, как исключается ток короткого замыкания между источниками питания логического уровня (например, Vcc и Vss) во время переходов. Такой усилитель опроса может быть выполнен с возможностью сдвига уровня отрицательных входных напряжений до промежуточных напряжений, упомянутых, как положительные. Соответствующие значения промежуточных напряжений могут быть основаны, по меньшей мере, частично, на относительных значениях отрицательных входных напряжений. Такой усилитель опроса может быть дополнительно выполнен с возможностью преобразования промежуточных напряжений в напряжения логического уровня, выводимых на основе, по меньшей мере, частично, относительных значений промежуточных напряжений. Такой усилитель опроса может иметь относительно малое входное напряжение смещения, и может быть выполнен с возможностью предоставления относительно низкой энергии относительно высокоскоростного сдвига уровня для получения выхода логического уровня из относительно низкого входа уровня.

На фиг. 2В иллюстрируется пример части 260 цепи, включающей в себя двоично-взвешенный настроечный конденсатор 251 в соответствии с одним вариантом осуществления настоящего раскрытия. Двоично-взвешенный настроечный конденсатор 251 представляет собой пример цепи 250 настроечного конденсатора по фиг. 2А. Двоично-взвешенный настроечный конденсатор 251 включает в себя множество (например, четыре) настроечных конденсаторов 282А…, 282D. Каждый настроечный конденсатор 282А…, 282D имеет значение емкости, которое представляет собой степень двух, умноженную на номинальное значение емкости, dC. В неограничительном примере значение емкости dC может составлять порядка 10 фемтофарад (fF). Например, первый настроечный конденсатор 282А имеет значение емкости, равное однократному значению (то есть, 2°) dC, второй настроечный конденсатор 282В имеет двойное значение емкости (то есть, 21) dC, третий настроечный конденсатор 282С имеет значение емкости четыре (то есть, 22) dC, и четвертый настроечный конденсатор 282D имеет значение емкости восемь (то есть, 23) dC. Двоично-взвешенный настроечный конденсатор 251 дополнительно включает в себя множество переключателей 284А…, 284D. Количество переключателей соответствует количеству настроечных конденсаторов 282А…, 282D. Состояние каждого переключателя 284А, 284D выполнено так, чтобы ими мог управлять селектор 286. Когда соответствующий переключатель 284А…, 284D замкнут, взаимосвязанный настроечный конденсатор 282А…, 282D соединяется с переключателем 288А, 288В и, таким образом, с HNREG или HNREGB. Таким образом, на основе значение селектора (например, четырехбитного) может быть замкнут ни один, один или больше из переключателей 284А…, 284D. Двоично-взвешенный настроечный конденсатор 251 может затем предоставлять избирательное значение настроечной емкости в диапазоне от нуля (то есть, все переключатели 284А…, 284D разомкнуты) до 15*dC (то есть, все переключатели 284А…, 284D замкнуты) с шагом dC. Таким образом, на основе, по меньшей мере, частично, значений емкости собственных емкостей 218, 232, 234 и 236 и выбранного значения емкости двоично-взвешенного настроечного конденсатора 251, выбранное опорное напряжение может быть получено на одном или больше из узлов HNREG и HNREGB, как описано здесь.

На фиг. 2С показан упрощенный чертеж 270, иллюстрирующий собственные емкости и цепь 252 конденсатора регулирования опорного напряжения, ассоциированную с формированием локального опорного напряжения, как описано здесь. Цепь 252 конденсатора регулирования опорного напряжения включает в себя регулировочный конденсатор 253 и переключатель 254 регулировочного конденсатора. В варианте осуществления цепь 252 может соответствовать цепи 250 настроечного конденсатора. В этом примере, Схх SW 254 соответствует ТС SWB 288В, ТС SWA 288А разомкнут для отсоединения цепи 250 настроечного конденсатора от узла HNREG, и Сxx 253 соответствуют емкости цепи 250 настроечного конденсатора. Цепь 252 другого варианта осуществления может соответствовать GWLB SW225 и собственной емкости 233. В этом варианте осуществления переключатель 254 Схх соответствует GWLB SW 225, и емкость 253 соответствует емкости 233. Таким образом, Схх соответствует CGWLB в данном варианте осуществления.

Собственные емкости 218, 232, 234, 236 и регулировочная емкость 253 могут быть выполнены с возможностью, в общем, параллельного включения. Соединением емкостей 218, 232, 234, 236, 253 можно затем управлять с помощью переключателя 242 HNEQ, цепи 223 LWL, переключателя 225 GWL и переключателя 254 Сxx. Переключатель 223 LWL и переключатель 225 GWL могут быть включены в цепь 222 переключателя LWL и в цепь переключения 224 GWL, соответственно. Обычно, во время работы, емкости 218, 232, 234, 236, 253 могут использоваться для сохранения заряда, относящегося к опорному напряжению, для усилителя 240 опроса. Переключатель 242 HNEQ выполнен с возможностью соединения и отсоединения узлов HNREG и HNREGB, как описано здесь. Параллельное соединение емкости 253 регулирования собственной емкости 236 выполнено с возможностью обеспечения требуемого опорного напряжения, относящегося к WLVDM.

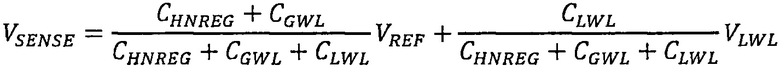

Обычно заряд Q на емкостном элементе с емкостью С равен произведению емкости и разности потенциалов (то есть, напряжению) на емкостном элементе (Q=C*V). Используемый здесь термин "емкостный элемент" включает в себя, например, конденсатор, собственную емкость и/или параллельную комбинацию одного или больше из них. Если множество емкостных элементов, один или больше из которых, с исходным зарядом и соответствующим исходным напряжением, затем будут соединены параллельно, то исходные напряжения будут выровнены до конечного напряжения. На основе сохранения заряда, общий заряд перед выравниванием равен общему заряду после выравнивания. Например, рассмотрим два емкостных элемента с емкостями С1 и С2, и соответствующими исходными напряжениями V1 и V2. Исходный заряд равен

Qi=Q1+Q2=C1*V1+C2*V2.

Если конденсаторы затем соединить параллельно, конечный заряд будет равен

Qf=Vf*(C1+C2)

где Vr представляет собой конечное напряжение на емкостных элементах, включенных параллельно. Поскольку Qi=Qf,

C1*V1+C2*V2=Vf*(C1+C2).

Таким образом,

На основе сохранения заряда и используя собственные емкости, заряженные напряжениями смещения, опорное напряжение может быть локально сформировано, как описано здесь.

На фиг. 3А показана временная диаграмма 300, которая иллюстрирует пример операции считывания памяти в системе 200 памяти с узлами пересечения. На фиг. 3В показана временная диаграмма 350, которая иллюстрирует пример напряжений на узлах HNREG и HNREGB, включая в себя напряжения опроса и опорные напряжения, и входные напряжения (REN, SEN) усилителя опроса для установки и сброса элементов памяти для операций считывания памяти в системе 200 памяти с узлами пересечения. Временные диаграммы 300, 350 лучше всего можно понять при чтении также со ссылкой на участок 200 памяти с узлами пересечения, представленный на фиг. 2А, и упрощенный участок 270, представленный на фиг. 2С.

Временная диаграмма 300 включает в себя форму 302 колебаний, которая соответствует входу управления GWFSEF, форму колебаний 304, которая соответствует входу управления FBFSEF, форму 306 колебаний, которая соответствует входу управления GBFSEF, форму 308А колебаний, которая соответствует входу управления NFRU, входу управления для переключателя 246 NFRU и форму колебаний 308В, которая соответствует входу управления NFRF, входу управления для переключателя 248 NFRF. Временная диаграмма 300 дополнительно включает в себя форму 310 колебаний, которая соответствует входу управления FWFSEF, форму колебаний 312, которая соответствует входу управления HNEQ, форму 314 колебаний, которая соответствует выходу AXN цепи 210 напряжения смещения BE, форму 316 колебаний, которая соответствует входу управления FSENB, выполненному с возможностью включения первого каскада усилителя 240 опроса, форму 318 колебаний, которая соответствует входу управления SAEN, выполненному с возможностью включения выхода усилителя 240 опроса, и форму 320 колебаний, которая соответствует входу управления SMIN, как описано здесь.

Временная диаграмма 350 включает в себя форму 322А колебаний, которая соответствует напряжению, детектируемому на узле HNREGB (и может соответствовать опорному напряжению VREF), и форму 322В колебаний, которая соответствует напряжению, детектируемому на узле HNREG (и может соответствовать напряжению пороса VSENSE). Формы 322А и 322В колебаний соответствуют напряжениям в HNREGB и HNREG для элемента памяти, например, элемента 216 памяти, в установленном состоянии. Временная диаграмма 350 дополнительно включает в себя форму 324А колебаний, которая аналогична форме 322А колебаний и форме 324В колебаний, которая аналогична форме 322В колебаний, за исключением форм 324А и 324В колебаний, которые соответствуют элементу памяти, например, элементу 216 памяти, в состоянии сброса.

Временная диаграмма 350 дополнительно включает в себя форму 326А колебаний, которая соответствует первому входному напряжению REN первого каскада усилителя 240 опроса, и форму 326В колебаний, которая соответствует второму входному напряжению SEN, первого каскада усилителя 240 опроса, как описано здесь. Формы 326А и 326В колебаний соответствуют REN и SEN для элементов памяти, например, элемента 216 памяти, в установленном состоянии. Временная диаграмма 350 дополнительно включает в себя форму 328А колебаний, которая соответствует первому входному напряжению REN первого каскада усилителя 240 опроса, и форму 328В колебаний, которая соответствует второму входному напряжению SEN первого каскада усилителя 240 опроса, как описано здесь. Формы 328А и 328В колебаний соответствуют REN и SEN для элемента памяти, например, элемента 216 памяти, в состоянии сброса.

Первоначально, во время, когда GWLSEL и LWLSEL имеют низкое значение, и LBLSEL, и GBLSEL имеют высокое значение, это обозначает, что ассоциированные GWL, LWL, GBL, LBL не выбраны. NLRU имеет низкое значение, что обозначает, что узел HNREG не соединен с WLVDM. Аналогично, NLRL имеет низкое значение, обозначающее, что HNREGB не соединен с WLVDM. NLRL остается в низком состоянии в течение периода времени от t0 до, по меньшей мере, t11. NLRL может использоваться для операций считывания памяти для соседнего участка массива памяти, аналогично NRLU, таким образом, форма 308В колебаний может соответствовать форме 308А колебаний для операций считывания памяти соседнего участка памяти. HNEQ имеет низкое значение, что обозначает, что узел HNREG не соединен с узлом HNREGB. AXN имеет низкое значение, что обозначает, что VDM также имеет низкое значение, LSENB имеет высокое значение, что обозначает, что HNREGB соединен с REN, HNREG соединен с SEN, и SA Каскада 1 не включен. SAEN имеет низкое значение, что обозначает, что выходы усилителя 240 опроса (то есть, SA Каскада 2) не включены. SMIN имеет низкое значение, что обозначает, что HNREG и HNREGB соединены с Vss с помощью переключателей 244А…, 244n. Таким образом, во время, когда заряды собственных емкостей 218, 232, 234 и 236 и регулировочные емкости 253 равны нулю, как и напряжение на HNREGB, напряжение в узле HNREG, REN и SEN также равно нулю (то есть, Vss).

Во время t1 GWLSEL, LBLSEL, GBLSEL и LWLSEL изменяют состояния, выбирая GWL 213, LWL 212, LBL 214 и взаимосвязанную GBL и, таким образом, соединяя элемент 216 памяти с цепью смещения 210 BL и схемой 230 опроса. SMIN переключает переключатели 244А и 244n, открывающие высокий уровень, и отсоединяющие узлы HNREG и HNREGB от  . Таким образом, во время t1, переключатель 223 LWL и переключатель 225 GWL замыкаются, соединяя собственные емкости 218 и 232 с узлом HNREG. Напряжения на узлах HNREGB и HNREG, REN и SEN остаются равными нулю.

. Таким образом, во время t1, переключатель 223 LWL и переключатель 225 GWL замыкаются, соединяя собственные емкости 218 и 232 с узлом HNREG. Напряжения на узлах HNREGB и HNREG, REN и SEN остаются равными нулю.

Во время t2, переключатель 246 NLRU замыкается, соединяя HNREG с WLVDM. Таким образом, во время t2, когда переключатель 246 NLRU замыкается, собственные емкости 218, 232 и 234 становятся соединенными с WLVDM и начинают заряжаться до WLVDM. Узел HNREG начинает переход на WLVDM, и узел HNREGB, остается на уровне Vss.

Во время t3, переключатель 246 NLRU размыкается, отсоединяя собственные емкости 218, 232 и 234 от WLVDM. Период времени от t2 до t3 представляет период времени предварительного заряда. Собственные емкости 218, 232 и 234 заряжаются до WLVDM во время периода времени предварительного заряда. Во время t3, HNREGB остается на уровне Vss, и HNREG (то есть, CHNREG), GWL 213 (то есть, CGWL) и LWL 212 (то есть, CLWL) остаются на уровне WLVDM. Во время t4, в ответ на состояние заряда LWLSEL, схема 222 переключателя LWL отсоединяет LWL 212 от GWL 213, переводя, таким образом, LWL 212 в плавающее состояние. LWL 212 остается заряженным до WLVDM.

Во время t5, переключатель 242 HNEQ замыкает соединительный узел HNREGB на HNREG и SA1 на SA2. Также, во время t5, VDM применяется для цепи 210 смещения BL, повышая AXN от уровня Vss до BLVDM. Время t5 соответствует началу интервала опроса состояния элемента 216 памяти и также формированию опорного напряжения VREF для усилителя 240 опроса. Предпочтительно, опорное напряжение VREF может быть сформировано локально из напряжений смещения GWL и LWL, и в период времени, который соответствует интервалу опроса. Другими словами, VREF можно понимать как случайный побочный продукт заряда LWL 212. Таким образом, генерирование опорного напряжения удаленно с передачей удаленно генерируемого опорного напряжения в усилитель 240 опроса может быть исключено и без увеличения длительности интервала опроса. Дополнительное преимущество соединения HNREGB и HNREG состоит в том, что шумы, присутствующие, например, на GWL, HNREG, HNREG и/или GWLB (если используются в качестве регулирующей емкости), могут стать синфазными шумами. Таким образом, усилитель 240 опроса может уменьшить или устранить шумы путем подавления синфазных шумов, что приводит к относительному улучшению помехозащищенности и надежности.

Непосредственно перед замыканием переключателя 242 HNEQ, то есть, непосредственно перед временем t5, собственную емкость 236 (CHNREGB) и регулировочную емкость 253 (Сxx), конфигурируют так, чтобы они имели нулевой заряд, и собственные емкости 232 и 234 конфигурируют так, чтобы они имели накопленный заряд:

QGWL=CGWL*WLVDM

и

QHNREG=CHNREG*WLVDM,

соответственно.

Таким образом, непосредственно перед замыканием переключателя 242 HNEQ, исходный заряд Qi составляет:

Qi=Qxx+QHNREGB+QGWL+QHNREG

Если емкости 236 и 253 имеют нулевой заряд, тогда Qi составляет:

Qi=(Сxx*0)+(CHNREGB*0)+(CGWL*WLVDM)+(CHNREG*WLVDM)=(CGWL+CHNREG)*WLVDM.

После замыкания переключателя 242 HNEQ, заряд может перетечь из емкостей 232 и 234 в емкости 236 и 253. В установившемся состоянии, поскольку емкости 232, 234, 236 и 253 соединены параллельно,

Qf=(CGWL+CHNREG+СHNREGB+Схх) Vf

где Qf представляет собой общий конечный заряд, и Vf представляет собой конечное напряжение на емкостях 232, 234, 236, 253. Следует отметить, что емкость 218 LWL не включена в этот расчет, поскольку переключатель 223 LWL разомкнут таким образом, что LWL 212 отсоединена от, по меньшей мере, GWL 213 и схемы 230 опроса. На основе сохранения заряда (то есть, Qi=Qf),

(CGWL+CHNREG)*WLVDM=(CGWL+CHNREG+CHNREGB+Cxx)*Vf

что может быть записано, как:

где Vf соответствует опорному напряжению VREF, как описано здесь. Предпочтительно, в соответствии с настоящим раскрытием, VREF может быть сформировано, используя локальное напряжение смещения WLVDM и заряд, сохраненный в собственных емкостях (то есть, емкости GWL CGWL и емкости первой схемы опроса CHNREG), когда напряжение смещения WLVDM приложено к GWL 213 через узел HNREG.

BLVDM приблизительно равно VDM, которое меньше на пороговое напряжение (например, VTn) переключателя, взаимосвязанного с цепью 210 смещения BL. Таким образом, LWL 212, которая была заряжена до WLVDM, и LBL 214, которая не была заряжена до BLVDM, обеспечивают дифференциальное напряжение на элементе 216 памяти, соответствующее BLVDM+IWLVDMI. Другими словами, поскольку WLVDM обычно является отрицательным и BLVDM обычно положительным, суммарная разность потенциалов на элементе 216 памяти составляет сумму абсолютных значений BLVDM и WLVDM. Таким образом, элемент 216 памяти может выполнять скачкообразный переход (может устанавливаться), или может выполнять обратный скачкообразный переход (выполнять сброс) в течение временного интервала от t5 до t6 в зависимости от того, содержит ли элемент памяти ноль (сброшен) или единицу (установлен). Заряд в LWL 212 может затем отражать состояние памяти. Например, если пороговое напряжение элемента 216 памяти больше, чем BLVDM+IWLVDMI, обратный скачкообразный переход не может происходить в соответствии с сохраненным логическим нулем. Если скачкообразный переход не происходит, VLWL в LWL 212 может оставаться на уровне, близком к WLVDM. В другом примере, если пороговое значение напряжения элемента 216 памяти меньше, чем или равно BLVDM+IWLVDMI, обратный скачкообразный переход может происходить, в соответствии с сохраненной логической единицей. Если происходит обратный скачкообразный переход, напряжение (VLWL) в LWL 212 может увеличиваться до уровня больше, чем WLVDM, то есть, |VLWL|<|WLVDM|, по мере протекания тока через элемент памяти. Другими словами, VLWL может соответствовать WLVDM, если не происходит обратный скачкообразный переход, и VLWL может увеличиваться до уровня, близкого к нулю, если происходит обратный скачкообразный переход.

Одновременно с опросом, когда переключатель 242 HNEQ замкнут, узел HNREG соединен с узлом HNREGB. Непосредственно перед замыканием переключателя HNEQ (то есть, t5minus), узел HNREGB находится на уровне Vss, и узел HNREG находится на уровне WLVDM. Таким образом, собственные емкости 234 и 232 заряжаются до WLVDM, и собственная емкость 236 и собственная емкость 253 находятся на уровне Vss. После замыкания переключателя 242 HNEQ, HNREGB и HNREG могут выравниваться до значения Vss и WLVDM.

Таким образом, непосредственно перед моментом времени t6, напряжения на HNREGB, HNREG и GWL 213 могут находиться на уровне или близко к VREF, и LWL 212 может иметь заряд, соответствующий напряжению VLWL (т.е., детектированное напряжение элемента памяти). Во время t6 переключатель 242 HNEQ может быть разомкнут, отсоединяя HNREGB и HNREG. Также в момент времени t6, цепь 210 смещения BL может быть отсоединена от Vpp, таким образом, AXN может возвращаться к Vss. Как HNREG, так и HNREG, может оставаться на уровне VREF, и GWL 213 аналогично может оставаться на уровне VREF.

Во время t7, LWL 212 может снова быть выбрана, и схема 222 переключателя LWL может соединять LWL 212 с GWL 213 (то есть, CGWL) и, таким образом, с узлом HNREG. VLWL из LWL 212 может быть затем скомбинировано с VREF в узле HNREG, для получения напряжения VSENSE в HNREG, выполненном с возможностью обозначения состояния элемента 216 памяти.

Перед временем t7, переключатель HNEQ разомкнут, таким образом, узел HNREGB отсоединен от узла HNREG. Из выравнивания, которое произошло между временем t5 и t6 оба узла HNREGB и HNREG находятся на уровне VREF. Таким образом, непосредственно перед временем t7, исходный заряд собственных емкостей 232 и 234, соединенных с узлом HNREG, составляет:

Qi=(CHNREG+CGWL)*VREF.

Аналогично, исходный заряд, взаимосвязанный с LWL 212, составляет CLWL * VLWL, где VLWL соответствует обнаруживаемому напряжению элемента памяти, которое может находиться на уровне или рядом с уровнем WLVDM, или напряжению, соответствующему WLVDM и BLVDM, например, ноль вольт. Снова, на основе сохранения заряда:

(CHNREG+CGWL)*VREF+CLWLVLWL=(CHNREG+CGWL+CLWL)*VSENSE

где VSENSE соответствует напряжению в узле HNREG, что получается в результате повторного соединения LWL 212 с GWL 213 и узлом HNREG после интервала опроса. Таким образом,

Во время временного интервала от t7 до t8, HNREGB может находиться на уровне VREF, и узел HNREG может находиться на уровне VSENSE. Таким образом, форма 322А колебаний соответствует VSENSE, и форма 322В колебаний соответствует VREF для элемента памяти в установленном состоянии, и форма 324А колебаний соответствует VSENSE, и форма 324В колебаний соответствует VREF для элемента памяти в состоянии сброса в течение интервала времени, начинающегося с момента времени t7. VREF прикладывают ко входу SA1, и VSENSE прикладывают ко входу SA2 усилителя 240 опроса. Поскольку LSENB остается высоким во временном интервале от t7 до t8, SA1 соединен с REN, и SA2 соединен с SEN, таким образом, REN находится на уровне VREF, и SEN находится на уровне VSENSE. Является ли разность между VSENSE и VREF положительной или отрицательной (то есть, VSENSE > VREF или VSENSE < VREF), может затем обозначать, произошел или нет обратный скачкообразный переход, и, таким образом, содержит ли элемент 216 памяти ноль или единицу. Если VSENSE больше, чем VREF, усилитель 240 опроса выполнен с возможностью вывода логической единицы в узел опроса. Если VSENSE меньше, чем VREF, усилитель 240 опроса выполнен с возможностью вывода логического нуля в узел опроса.

Разность между VSENSE и VREF может быть определена следующим образом

которое, после некоторых алгебраических манипуляций упрощается до

Поскольку VLWL может соответствовать WLVDM при отсутствии обратного скачкообразного перехода и может находиться на уровне ноль или близком к нулю, если присутствует обратный скачкообразный переход, может быть желательным, чтобы VREF было равно или было близким к WLVDM/2. VREF может находиться на уровне или близко к WLVDM/2, если

CGWL+CHNREG=CHNREGE+Cxx

Таким образом, выбор Cxx может быть основан, по меньшей мере, частично, на значениях CGWL, CHNREG и CHNREGB.

В некоторых вариантах осуществления Схх может быть выбрана таким образом, чтобы VREF не было равно WLVDM/2. Например, если регулировать VREF так, чтобы оно было больше или меньше, чем WLVDM/2 можно его сконфигурировать так, чтобы оно подгоняло вариации порогового напряжения элемента памяти, обеспечивая, таким образом, более надежный опрос состояния элемента памяти. Другими словами, регулирование VREF может быть выполнено с возможностью оптимизации определения состояния элемента памяти.

В момент времени t8, LSENB переключают на низкий уровень, отсоединяя SA1 от REN и SA2 от SEN и включая SA Каскада 1 для генерирования промежуточных положительных опорных напряжений на основе, по меньшей мере, частично, REN (то есть, VREF и SEN (то есть, VSENSE)- Напряжения на узлах SEN и REN (которые находились на уровне или ниже нуля перед временем t8, конфигурируют так, чтобы они повысились до промежуточных напряжений, Vcc или Vcc - |VTP|. Находится ли узел SEN на уровне Vcc или Vcc - |VTP|, зависит от того, было ли VSENSE больше чем или меньше чем VREF. Например, если VSENSE больше, чем VREF (то есть, VSENSE менее отрицательно, чем VREF), узел SEN может достигать Vcc (форма 326В колебаний), и узел REN может затем перейти на уровень Vcc - |VTP| (форма 326А колебаний), где VTP соответствует пороговому напряжению транзистора, включенного в SА Каскада 1. В другом примере, если VSENSE меньше, чем VREF (то есть, VSENSE в большей степени отрицательно, чем VREF), узел REN может достигать Vcc (форма 328А колебаний) и узел SEN может затем установиться на Vcc - |VTP| (форма 328В колебаний). SA Каскада 1 может быть выполнен с возможностью генерирования промежуточных выходных напряжений на узлах SEN и REN, которые соответствуют Vcc и Vcc - |VTP|, когда узлы REN и SEN отсоединены от SA1 и SA2, соответственно. Уровень отрицательных входных напряжений может быть сдвинут до Vcc (например, положительного напряжения логического уровня), которые называются промежуточными напряжениями, например, в SA Каскада 1. SA Каскада 1 может быть выполнен с возможностью обеспечения сдвига уровня с относительно малым входным напряжением смещения, нулевым статическим током между подачами и относительно низким потреблением энергии.

Во время t9, SAEN переключают на высокий уровень, для включения SA Каскада 2. Период времени от t8 по t9 сконфигурирован для обеспечения установившегося состояния промежуточных напряжений. Например, во время временного интервала от t8 по t9, соответствующие Vcc и Vcc - |VTP| могут достигать установившегося состояния по SEN и REN. В момент времени t9, SA Каскада 2 выполнен с возможностью преобразования промежуточных напряжений в напряжения логического уровня, выводимые на основе, по меньшей мере, частично, относительных значений промежуточных напряжений и предоставления логического уровня, выводимого в узел опроса. Например, SA Каскада 2 может быть соединен с SEN и REN. Таким образом, в момент времени t9, SAEN переключается на высокий уровень, предоставляя, таким образом, выход усилителя опроса в узел опроса. Если VSENSE больше, чем VREF, тогда выход может соответствовать Vcc. Если VSENSE меньше, чем VREF, тогда выход может соответствовать Vss. В момент времени t10, данные, соответствующие состоянию элемента 216 памяти, например, напряжение (напряжения), соответствующее логическому нулю и/или логической единице, выводят из усилителя 240 опроса в узел опроса. В момент времени t10, усилитель 240 опроса может быть отключен. Операция считывания может заканчиваться в момент времени t11.

Таким образом, усилитель 240 опроса выполнен с возможностью приема VSENSE и VREF и предоставления логического выходного уровня на основе, по меньшей мере, частично, является ли VSENSE большим, чем или меньшим чем Vref. SA Каскада 1 выполнен с возможностью сдвига уровня VSENSE и VREF до соответствующих промежуточных напряжений, называемых Vcc. SA Каскада 2 выполнен с возможностью преобразования промежуточных напряжений на логический уровень (например, Vss или Vcc), по меньшей мере частично, по относительным значениям промежуточных напряжений, и предоставлять вывод в узел опроса.

Таким образом, временные диаграммы 300, 350 и участок 200 массива памяти сконфигурированы для иллюстрации операции системы для получения опорного напряжения, локально используя, например, смещение WL и собственные емкости. Опорное напряжение можно регулировать с помощью регулирующей емкости, например, регулирующих конденсаторов, включенных в цепь 250 настроечного конденсатора или собственных емкостей 233, ассоциированных с соседним GWLB.

Таким образом, на фиг. 2А, 2В и 2С иллюстрируется формирование опорного напряжения с помощью схем опроса, используя собственные емкости. В варианте осуществления соседний участок памяти может использоваться (например, GWLB) для предоставления дополнительной собственной емкости, для получения опорного напряжения, которое находится на уровне или рядом с WLVDM/2. В другом варианте осуществления цепь настроечного конденсатора может предоставлять регулировочную емкость. Регулировочная емкость может использоваться для регулирования VREF. VREF может быть отрегулировано так, чтобы размещать характеристики ассоциированного участка памяти с узлами пересечения. Например, VREF можно отрегулировать так, чтобы оно было больше чем или меньше чем WLVDM/2 для того, чтобы, например, оптимизировать запас опроса между максимальным установленным напряжением и минимальным напряжением сброса для элемента памяти.

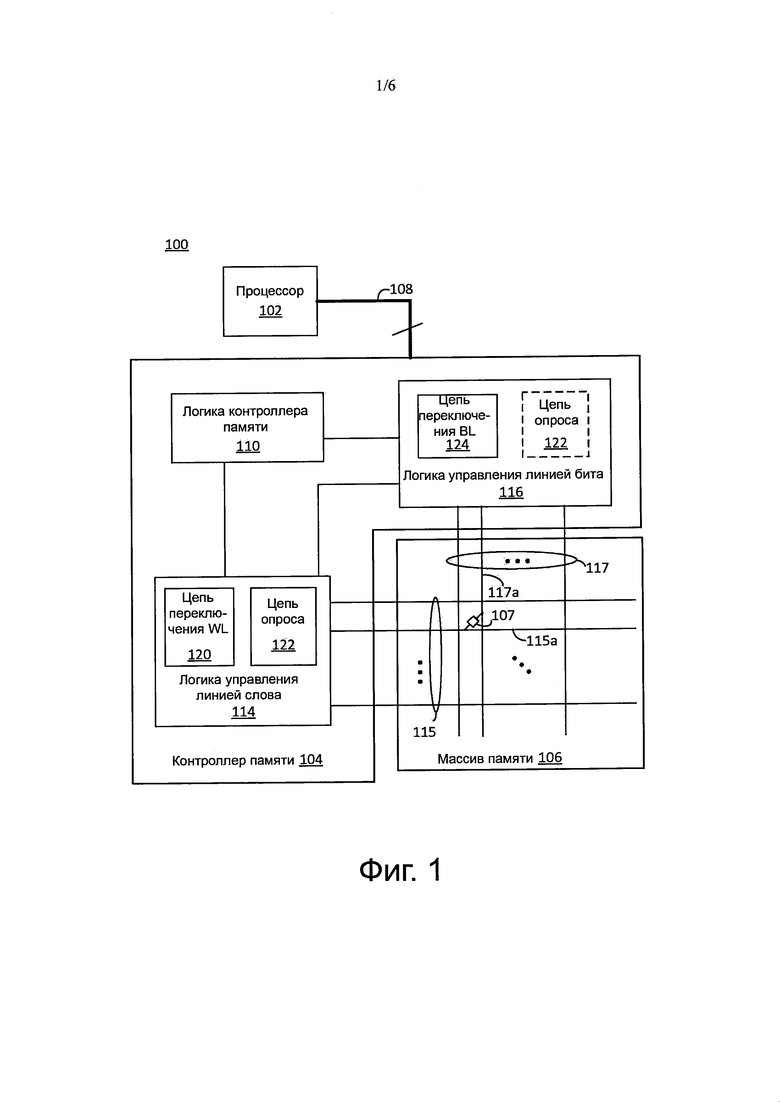

На фиг. 4 иллюстрируется блок-схема 400 последовательности операций для операций доступа к памяти, включающих в себя: формируют опорное напряжение в памяти с узлами пересечения, в соответствии с различными вариантами осуществления настоящего раскрытия. Операции могут выполняться, например, контроллером памяти, например, контроллером 104 памяти, включающим в себя логику 114 управления WL и логику 116 управления BL. Блок-схема 400 последовательности операций представляет примерные операции, предназначенные для выполнения операции доступа к памяти, например, операции считывания. В частности, блок-схема 400 последовательности операций представляет примерные операции, сконфигурированные для считывания элемента памяти, включая в себя формирование опорного напряжения, используя собственные емкости и напряжение смещения, как описано здесь.

Операции блок-схемы 400 последовательности операций могут начинаться с декодирования адреса памяти во время операции 402. GWL, LWL, GBL и LBL, ассоциированные с целевым элементом памяти, могут быть выбраны на основе, по меньшей мере, частично декодированного адреса памяти во время операции 404. Операция 406 может включать в себя подключение выбранных GBL и LBL к цепи смещения, и GWL, и LWL к схеме опроса, например, к схеме 230 опроса на фиг. 2А. Операция 408 включает в себя предварительный заряд выбранной GWL, LWL и емкости первой цепи опроса. Например, выбранные GWL, LWL и емкость первой цепи опроса могут быть предварительно заряжены до напряжения WLVDM.

LWL может быть отсоединена от схемы опроса, и напряжение смещения BL может быть приложено к LBL во время операции 410. Приложенное напряжение к выбранному элементу памяти может затем соответствовать BLVDM - WLVDM, и выполнено так, чтобы оно было больше, чем максимальное установленное напряжение, и меньше, чем минимальное напряжение сброса элемента памяти. Обратный скачкообразный переход может увеличивать напряжение на LWL от WLVDM до напряжения на уровне или рядом с нулем, и отсутствие скачкообразного обратного перехода может не влиять на напряжение на LWL, то есть, напряжение LWL может оставаться WLVDM. Операция 412 включает в себя: формируют опорное напряжение, VREF, используя заряды емкостей, ассоциированных с GWL и емкость первой цепи опроса. Опорное напряжение может быть основано, по меньшей мере, частично, на собственной емкости, взаимосвязанной с GWL, емкости первой цепи опроса и емкости второй цепи опроса, и регулирующей емкости, как описано здесь. Например, узлы HNREG и HNREGB цепи 230 опроса могут быть подключены для выравнивания напряжения на емкостях.

После интервала опроса LWL может, быть соединено со схемой опроса во время операции 414. Как результат операции 414, узел HNREG можно быть заряжен до VSENSE. VSENSE основано, по меньшей мере, частично, на состоянии считываемого элемента памяти. Операция 416 может включать в себя: определяют состояния элемента памяти на основе, по меньшей мере, частично VREF, и напряжения элемента памяти VLWL. Операция 418 может включать в себя: предоставляют логический уровень выхода, который соответствует состоянию элемента памяти. Например, усилитель опроса, например, усилитель 240 опроса, может быть выполнен с возможностью приема VSENSE и VREF и предоставления выходного логического уровня на основе, по меньшей мере, частично того, больше ли VSENSE чем или меньше, чем VREF. Поток обработки программы может затем заканчиваться на операции 420.

Таким образом, операции блок-схемы 400 последовательности операций, выполнены с возможностью получения опорного напряжения VREF, используя собственные емкости и напряжение смещения WL, WLVDM. Операции блок-схемы 400 последовательности операций, дополнительно выполнены с возможностью приложения напряжения смещения к элементу памяти и детектирования выбранного напряжения элемента памяти. Произошел или нет скачкообразный обратный переход, может затем быть определено на основе, по меньшей мере, частично, относительных значений напряжения опроса VSENSE, которое относится к детектируемому напряжению VLWL и VREF элемента памяти.

В то время, как на фиг. 4 иллюстрируются различные операции, в соответствии с одним вариантом осуществления, следует понимать, что не все из операций, представленных на фиг. 4, являются необходимыми для других вариантов осуществления. Действительно, здесь совершенно понятно, что в других вариантах осуществления настоящего раскрытия, операции, представленные на фиг. 4, и/или другие операции, описанные здесь, могут быть скомбинированы таким образом, как, в частности, не представлено на любом из чертежей, но все еще в полном соответствии с настоящим раскрытием. Таким образом, пункты формулы изобретения, направленные на свойства и/или операции, которые точно не показаны на одном чертеже, рассматриваются как находящиеся в пределах объема и содержания настоящего раскрытия.

Используемый в любом варианте осуществления, представленном здесь, термин "логика" может относиться к программному приложению, программному обеспечению, встроенному программному обеспечению и/или схеме, сконфигурированной для выполнения любой из упомянутых выше операций. Программное обеспечение может быть воплощено, как программный пакет, код, инструкции, набор инструкций и/или данные, записанные на непереходном считываемом компьютером носителе информации. Встроенное программное обеспечение может быть воплощено, как код, инструкции или наборы инструкций и/или данные, которые жестко закодированы (например, энергонезависимо) в запоминающих устройствах.

"Цепь", как используется в любом из представленных здесь вариантов осуществления, может содержать, например, одну или любую комбинацию аппаратных цепей, программируемых цепей, таких как процессоры компьютера, содержащие одно или больше отдельных ядер обработки инструкций, схему конечного автомата и/или встроенное программное обеспечение, которое содержит инструкции, выполняемые программируемой цепью. Логика может совместно или по-отдельности быть воплощена, как цепь, которая формирует часть более крупной системы, например, интегральную схему (IС), специализированную интегральную схему (ASIC), систему на кристалле (SoC), настольные компьютеры, переносные компьютеры, планшетные компьютеры, серверы, смартфоны и т.д.

В некоторых вариантах осуществления формулировки для описания аппаратных средств могут использоваться для установления воплощения цепи и/или логики варианта (вариантов) выполнения логики для различной логики и/или цепей, описанных здесь. Например, в одном варианте осуществления формулировки для описания аппаратных средств могут соответствовать или могут быть совместимыми с языком описания аппаратных средств (VHDL) интегральных схем с сверхвысокой скоростью (VHSIC), которые могут обеспечивать возможность изготовления полупроводников одной или больше цепей и/или логики, описанной здесь. VHDL может соответствовать или может быть совместим со Стандартом IEEE 1076-1987, Стандартом IEEE 1076.2, IEEE 1076.1, IEEE Draft 3.0 VHDL-2006, IEEE Draft 4.0 VHDL-2008 и/или других версий стандартов IEEE VHDL и/или других стандартов для описания аппаратных средств.

Таким образом, в данном раскрытии описаны система и способ, выполненные с возможностью локального формирования опорного напряжения для считывания элементов памяти. Система и способ, выполнены с возможностью использования собственных емкостей, взаимосвязанных с локальной WL и глобальной WL, а также, первой емкости цепи опроса. Напряжение смещения, приложенное, как часть операции доступа к памяти, заряжает собственные емкости. Полученный в результате заряд собственных емкостей может затем использоваться для формирования опорного напряжения. Значение опорного напряжения основано, по меньшей мере, частично, на относительных значениях собственных емкостей. В варианте осуществления глобальная WL из невыбранной части соседней памяти может предоставлять регулировочную емкость, выполненную с возможностью регулирования опорного напряжения, как описано здесь. В другом варианте осуществления цепь настроечного конденсатора может предоставлять дополнительную (то есть, регулировочную) емкость, выполненную с возможностью получения требуемого опорного напряжения.

Система и способ могут дополнительно включать в себя двухкаскадный усилитель опроса. Опорное напряжение поступает от зарядов собственных емкостей путем подключения входов усилителя опроса, таким образом, также обеспечивая воздействие шумов, присутствующих в схеме опроса, в режиме синфазных шумов. Опорное напряжение прикладывается к первому входу, и напряжение опроса, относящееся к опорному напряжению и выходу выбранного элемента памяти, прикладывают ко второму входу усилителя опроса. Первый каскад выполнен с возможностью сдвига уровня отрицательных входных напряжений для промежуточных напряжений, называемых напряжением Vcc источника питания. Промежуточные напряжения выводят из первого каскада и вводят во второй каскад. Второй каскад преобразует промежуточные напряжения до сигнала логического уровня, то есть, логической единицы или логического нуля, в соответствии с Vcc или Vss. Усилитель опроса выполнен с возможностью предоставления относительно высокоскоростного переключения уровня с относительно низкой энергией, выполненного с возможностью получения выхода логической единицы из относительно низкого входного уровня с относительно надежной защитой от шумов.

Примеры

Примеры настоящего раскрытия включают в себя материал предмета изобретения, такой как способ, средство для выполнения действия способа, устройства или устройства, или системы, относящихся к опорной архитектуре в памяти с узлами пересечения, как описано ниже.

Пример 1

В соответствии с этим примером, обеспечивается устройство, включающее в себя контроллер памяти, выполненный с возможностью выбора целевого элемента памяти для операции доступа к памяти. Контроллер памяти включает в себя схему переключения линии слова (WL), выполненную с возможностью выбора глобальной WL (GWL), и локальной WL (LWL), ассоциированных с целевым элементом памяти. Контроллер памяти дополнительно включает в себя схему переключения линии битов (BL), выполненную с возможностью выбора глобальной BL (GBL), и локальной BL (LBL), ассоциированных с целевым элементом памяти; и схемы опроса. Схемы опроса включают в себя первую емкость схемы опроса и вторую емкость схемы опроса. Схемы опроса выполнены с возможностью предварительного заряда выбранной GWL, LWL и первой емкости схемы опроса до напряжения WL смещения WLVDM. Схемы опроса дополнительно выполнены с возможностью получения опорного напряжения (VREF), используя заряд по выбранной GWL и заряд первой емкости схемы опроса. Схемы опроса дополнительно выполнены с возможностью определения состояния целевого элемента памяти на основе, по меньшей мере, частично, VREF и обнаруженного напряжения VLWL элемента памяти.

Пример 2

Этот пример включает в себя элементы примера 1, в котором цепь переключения BL выполнена с возможностью приложения напряжение смещения BL (BLVDM) к выбранной LBL.

Пример 3

Этот пример включает в себя элементы примера 1, дополнительно включающие регулировочную емкость, в которой VREF основано, по меньшей мере, частично, на регулировочной емкости.

Пример 4

Этот пример включает в себя элементы примера 3, в котором регулировочная емкость содержит, по меньшей мере, одну из цепи настроечного конденсатора и не выбранной GWL.

Пример 5

Этот пример включает в себя элементы по примеру 3 или 4, в котором сумма емкости GWL и первой емкости цепи опроса равна сумме второй емкости цепи опроса и регулировочной емкости.

Пример 6

Этот пример включает в себя элементы по примеру 4, в котором цепь настроечного конденсатора представляет собой двоично-взвешенный настроечный конденсатор.

Пример 7

Этот пример включает в себя элементы по любому одному из примеров 1-3, в котором VREF равно половине WLVDM.

Пример 8

Этот пример включает в себя элемент по примеру 3 или 4, в котором регулировочная емкость выполнена с возможностью регулирования VREF таким образом, что VREF больше чем или меньше чем половина WLVDM.

Пример 9

Этот пример включает в себя элементы по примеру 4, в котором цепь настроечного конденсатора выполнена с возможностью ее совместного использования с соседним участком памяти.

Пример 10

Этот пример включает в себя элементы по любому одному из примеров 1-3, дополнительно включая в себя усилитель опроса, включающий в себя первый вход, соединенный со второй емкостью цепи опроса, и второй вход, соединенный с первой емкостью цепи опроса, цепь опроса, выполненную с возможностью соединения первого входа со вторым входом, для получения VREF.

Пример 11

Этот пример включает в себя элементы по примеру 10, в котором усилитель опроса выполнен с возможностью приема определяемого напряжения (VSENSE), относящегося к VREF и VLWL, для сдвига уровня VSENSE и VREF, для промежуточных положительных опорных напряжений и преобразования промежуточных напряжений в выход логического уровня, который соответствует состоянию целевого элемента памяти.

Пример 12

В соответствии с этим примером, обеспечивается способ, включающий в себя этапы, на которых: выбирают, с помощью контроллера памяти, целевой элемент памяти для операции доступа к памяти; выбирают, с помощью цепи переключения линии слова (WL), глобальную WL (GWL) и локальную WL (LWL), ассоциированные с целевым элементом памяти; выбирают, с помощью цепей переключения линии битов (BL), глобальную BL (GBL) и локальную BL (LBL), ассоциированную с целевым элементом памяти; предварительно заряжают, с помощью схемы опроса, выбранную GWL, LWL и первую емкость цепи опроса до напряжения смещения WLVDM WL; формируют, с помощью цепей опроса, опорное напряжение (VREF), используя заряд выбранного GWL и заряд первой емкости цепи опроса; и определяют, с помощью цепей опроса, состояние целевого элемента памяти на основе, по меньшей мере, частично, VREF, и обнаруживают напряжение элемента памяти VLWF.

Пример 13

Этот пример включает в себя элементы по примеру 12, и дополнительно включает в себя этапы, на которых: прикладывают, с помощью цепи переключения BL, напряжение смещения BL (BLVDM) к выбранной LBL.

Пример 14

Этот пример включает в себя элементы по примеру 12, в котором VREF основано, по меньшей мере, частично, на регулировочной емкости.

Пример 15

Этот пример включает в себя элементы по примеру 14, в котором регулировочная емкость содержит по меньшей мере одну цепь настроечного конденсатора и невыбранную GWL.

Пример 16

Этот пример включает в себя элементы по примеру 14, в котором сумма емкости GWL и первой емкости цепи опроса равна сумме второй емкости цепи опроса и регулировочной емкости.

Пример 17

Этот пример включает в себя элементы по примеру 15, в котором цепь настроечного конденсатора представляет собой двоично-взвешенный настроечный конденсатор.

Пример 18

Этот пример включает в себя элементы по примеру, в котором VREF равно половине WLVDM.

Пример 19

Этот пример включает в себя элементы по примеру 14, в котором регулировочную емкость конфигурируют для регулировки VREF таким образом, чтобы VREF было больше чем или меньше чем половина WLVDM.

Пример 20

Этот пример включает в себя элементы по примеру 15, в котором цепь настроечного конденсатора выполнена с возможностью ее совместного использования с соседним участком памяти.

Пример 21

Этот пример включает в себя элементы по примеру 12, и дополнительно включает в себя соединение, с помощью цепи опроса, первого входа усилителя опроса со вторым входом усилителя опроса, для получения VREF, первый вход соединен со второй емкостью цепи опроса и второй вход соединен с первой емкостью цепи опроса.

Пример 22

Этот пример включает в себя элементы по примеру 21, и дополнительно включает в себя этапы, на которых: принимают, с помощью усилителя опроса, определяемое напряжение (VSENSE), относящееся к VREF и VLWL; выполняют сдвиг уровня, с помощью усилителя опроса, VSENSE и VREF, для промежуточных положительных опорных напряжений; и преобразуют, с помощью усилителя опроса, промежуточные напряжения до логического уровня, выводимого так, чтобы он соответствовал состоянию целевого элемента памяти.

Пример 23

В соответствии с этим примером, предусмотрена система, включающая в себя процессор; массив памяти с узлами пересечения, включающий в себя целевой элемент памяти, целевую линию слова (WL) и целевую линию бита (BL). Целевой элемент памяти соединен между целевой WL и целевой BL. Система дополнительно включает в себя контроллер памяти, соединенный с процессором и массивом памяти с узлами пересечения. Контроллер памяти выполнен с возможностью выбора целевого элемента памяти для операции доступа к памяти. Контроллер памяти включает в себя цепь переключения линии слова (WL), выполненную с возможностью выбора глобальной WL (GWL) и локальной WL (LWL), ассоциированных с целевыми элементом памяти; цепь переключения линии битов (BL), выполненную с возможностью выбора глобальной BL (GBL) и локальной BL (LBL), ассоциированных с целевым элементом памяти; и цепь опроса. Цепь опроса включает в себя первую емкость цепи опроса и вторую емкость цепи опроса, цепь опроса выполнена с возможностью предварительного заряда выбранной GWL, LWL и первой емкости цепи опроса до напряжения смещения WL WLVDM. Цепь опроса дополнительно выполнена с возможностью получения опорного напряжения (VREF), используя заряд выбранной GWL и заряд первой емкости цепи опроса, и определения состояния целевого элемента памяти, на основе, по меньшей мере, частично, VREF и обнаруженного напряжения VLWL-элемента памяти

Пример 24

Этот пример включает в себя элементы по примеру 23, в котором цепь переключения BL выполнена с возможностью приложения напряжения смещения BL (BLVDM) к выбранной LBL.

Пример 25

Этот пример включает в себя элементы по примеру 23, дополнительно содержащий регулировочную емкость, в котором VREF основано, по меньшей мере, частично, на регулировочной емкости.

Пример 26

Этот пример включает в себя элементы по примеру, в котором регулировочная емкость содержит по меньшей мере одну из цепи настроечного конденсатора и невыбранной GWL.

Пример 27

Этот пример включает в себя элементы по примеру пункта 25 или 26, в котором сумма емкости GWL и первой емкости цепи опроса равна сумме второй емкости цепи опроса и регулировочной емкости.

Пример 28

Этот пример включает в себя элементы по примеру 26, в котором цепь настроечного конденсатора представляет собой двоично-взвешенный настроечный конденсатор.

Пример 29

Этот пример включает в себя элементы по примерам 23-25, в котором VREF равна половине WLVDM.

Пример 30

Этот пример включает в себя элементы по примерам 25 или 26, в котором регулировочная емкость выполнена с возможностью регулировки VREF таким образом, что VREF было больше чем или меньше чем половина WLVDM.

Пример 31

Этот пример включает в себя элементы по примеру 26, в котором цепь настроечного конденсатора выполнена с возможностью ее совместного использования соседним участком памяти.

Пример 32

Этот пример включает в себя элементы по любому одному из примеров 23-25, дополнительно включающие в себя усилитель опроса, включающий в себя первый вход, соединенный со второй емкостью цепи опроса, и второй вход, соединенный с первой емкостью цепи опроса, цепь опроса выполнена с возможностью соединения первого входа со вторым входом, для получения VREF.

Пример 33

Этот пример включает в себя элементы по примеру 32, в котором усилитель опроса выполнен с возможностью приема определяемого напряжения (VSENSE), относящегося к VREF и VLWL, до VSENSE и VREF сдвига уровня, для промежуточных положительных опорных напряжений и преобразования промежуточных напряжений в выход логического уровня, который соответствует состоянию целевого элемента памяти.

Пример 34

Другой пример настоящего раскрытия направлен на систему, включающую в себя, по меньшей мере, одно устройство, выполненное с возможностью выполнения способа по любому одному из пунктов 12-22.

Пример 35

Другой пример настоящего раскрытия направлен на устройство, содержащее средство для выполнения способа по любому одному из пунктов 12-22.

Различные особенности, аспекты, и варианты осуществления были описаны здесь. В отношении этих свойств, аспектов и вариантов осуществления могут быть выполнены комбинации друг с другом, а также с вариантами и модификациями, как будет понятно для специалиста в данной области техники. Настоящее раскрытие, поэтому, следует рассматривать, как охватывающее такие комбинации, варианты и модификации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УМЕНЬШЕНИЕ РАЗРУШЕНИЯ ТОКОМ СЧИТЫВАНИЯ В ПАМЯТИ С УЗЛАМИ ПЕРЕСЕЧЕНИЯ | 2015 |

|

RU2653320C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ОСНОВЕ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ | 2014 |

|

RU2620502C2 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ЗАРЯДА (ВАРИАНТЫ) И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С МАТРИЧНОЙ АДРЕСАЦИЕЙ, СНАБЖЕННОЕ ТАКИМ УСТРОЙСТВОМ | 2004 |

|

RU2311695C2 |

| МАГНИТНАЯ ПАМЯТЬ И СПОСОБ УПРАВЛЕНИЯ ЕЮ | 2014 |

|

RU2628221C1 |

| СХЕМА СМЕЩЕНИЯ ПАМЯТИ С УЗЛАМИ ПЕРЕСЕЧЕНИЯ | 2015 |

|

RU2651191C2 |

| УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ЭНЕРГИИ И ГЕНЕРАТОР ЭНЕРГИИ, СОДЕРЖАЩИЙ ТАКОЕ УСТРОЙСТВО | 2019 |

|

RU2780813C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЕМКОСТНОГО ОБНАРУЖЕНИЯ ОБЪЕКТОВ | 2008 |

|

RU2486530C2 |

| КОНТУР ДИСКРЕТНОГО СЧИТЫВАНИЯ (ВАРИАНТЫ) | 2005 |

|

RU2297052C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2681344C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении возможности локального получения опорного напряжения для считывания элементов памяти. Устройство доступа к памяти содержит контроллер памяти, выполненный с возможностью выбора целевого элемента памяти для операции доступа к памяти, при этом контроллер содержит: схему переключения линии слова (WL), выполненную с возможностью выбора глобальной WL (GWL) и локальной WL (LWL), ассоциированных с целевым элементом памяти; схему переключения линии битов (BL), выполненную с возможностью выбора глобальной BL (GBL) и локальной BL (LBL), ассоциированных с целевым элементом памяти; и схему опроса, содержащую первую емкость схемы опроса и вторую емкость схемы опроса, при этом схема опроса выполнена с возможностью предварительного заряда выбранной GWL, LWL и первой емкости схемы опроса до напряжения WL смещения WLVDM, получения опорного напряжения (VREF), с использованием заряда по выбранной GWL и заряда первой емкости схемы опроса, определения состояния целевого элемента памяти по меньшей мере частично на основе VREF и обнаруженного напряжения VLWL элемента памяти. 5 н. и 18 з.п. ф-лы, 7 ил.

1. Устройство доступа к памяти, содержащее:

контроллер памяти, выполненный с возможностью выбора целевого элемента памяти для операции доступа к памяти, при этом контроллер содержит:

схему переключения линии слова (WL), выполненную с возможностью выбора глобальной WL (GWL) и локальной WL (LWL), ассоциированных с целевым элементом памяти;

схему переключения линии битов (BL), выполненную с возможностью выбора глобальной BL (GBL) и локальной BL (LBL), ассоциированных с целевым элементом памяти; и

схему опроса, содержащую первую емкость схемы опроса и вторую емкость схемы опроса, при этом схема опроса выполнена с возможностью предварительного заряда выбранной GWL, LWL и первой емкости схемы опроса до напряжения WL смещения WLVDM, получения опорного напряжения (Vref), с использованием заряда по выбранной GWL и заряда первой емкости схемы опроса, определения состояния целевого элемента памяти по меньшей мере частично на основе Vref и обнаруженного напряжения Vlwl элемента памяти.

2. Устройство по п. 1, в котором цепь переключения BL выполнена с возможностью приложения напряжения смещения BL (BLVDM) к выбранной LBL.

3. Устройство по п. 1, дополнительно содержащее регулировочную емкость, причем Vref по меньшей мере частично основано на регулировочной емкости.

4. Устройство по п. 3, в котором регулировочная емкость содержит по меньшей мере одну из цепи настроечного конденсатора и не выбранной GWL.

5. Устройство по п. 3 или 4, в котором сумма емкости GWL и первой емкости цепи опроса равна сумме второй емкости цепи опроса и регулировочной емкости.

6. Устройство по любому из пп. 1-3, дополнительно содержащее усилитель опроса, включающий в себя первый вход, соединенный со второй емкостью цепи опроса, и второй вход, соединенный с первой емкостью цепи опроса, при этом цепь опроса выполнена с возможностью соединения первого входа со вторым входом, для получения Vref.

7. Устройство по п. 6, в котором усилитель опроса выполнен с возможностью приема определяемого напряжения (Vsense), относящегося к Vref и Vlwl, сдвига уровня Vsense и Vref, для промежуточных положительных опорных напряжений и преобразования промежуточных напряжений в выход логического уровня, соответствующий состоянию целевого элемента памяти.

8. Способ доступа к памяти, содержащий этапы, на которых:

выбирают, с помощью контроллера памяти, целевой элемент памяти для операции доступа к памяти;

выбирают, с помощью цепи переключения линии слова (WL), глобальную WL (GWL) и локальную WL (LWL), ассоциированные с целевым элементом памяти;

выбирают, с помощью цепи переключения линии битов (BL), глобальную BL (GBL) и локальную BL (LBL), ассоциированную с целевым элементом памяти;