Перекрестная ссылка на родственные заявки

Данная заявка основана и испрашивает приоритет по предварительной заявке на патент США № 61/804,557, поданной 22 марта 2013 года; и заявке на патент США № 14/018,242, поданной 4 сентября 2013 года, содержимое всех из которых полностью содержится в данном документе по ссылке.

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, в общем, относятся к запоминающему устройству на основе изменения сопротивления.

Уровень техники

В последнее время привлекают внимание полупроводниковые запоминающие устройства, которые включают в себя энергонезависимое запоминающее устройство, к примеру, запоминающее устройство на основе изменения сопротивления (например, магниторезистивное оперативное запоминающее устройство (MRAM), оперативное запоминающее устройство на основе фазового перехода (PRAM), резистивное оперативное запоминающее устройство (ReRAM) и т.д.) в качестве запоминающего устройства.

Типичное запоминающее устройство на основе изменения сопротивления выполнено с возможностью делать различение между данными в "1" и данными в "0" посредством изменения своего сопротивления посредством подачи тока (или приложения напряжения). Помимо этого, запоминающее устройство на основе изменения сопротивления оснащено считывающим усилителем, который считывает небольшое варьирование тока считывания из каждой ячейки запоминающего устройства.

Краткое описание чертежей

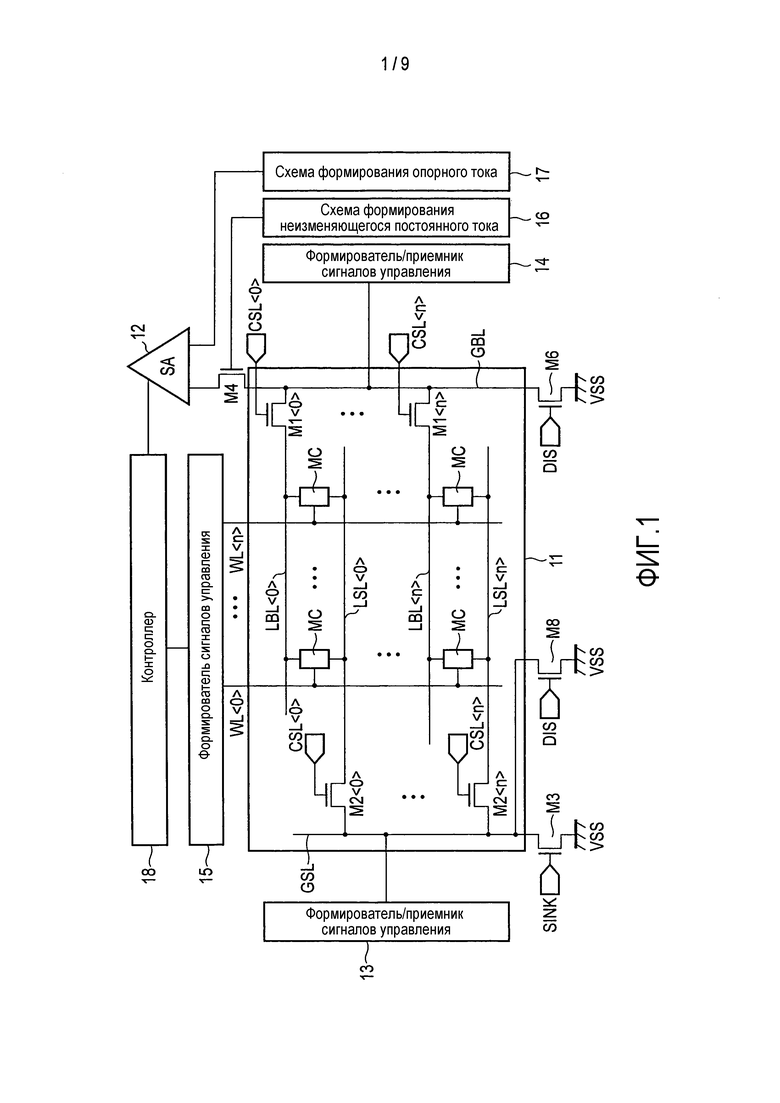

Фиг. 1 является видом, иллюстрирующим конфигурацию запоминающего устройства на основе изменения сопротивления согласно первому варианту осуществления;

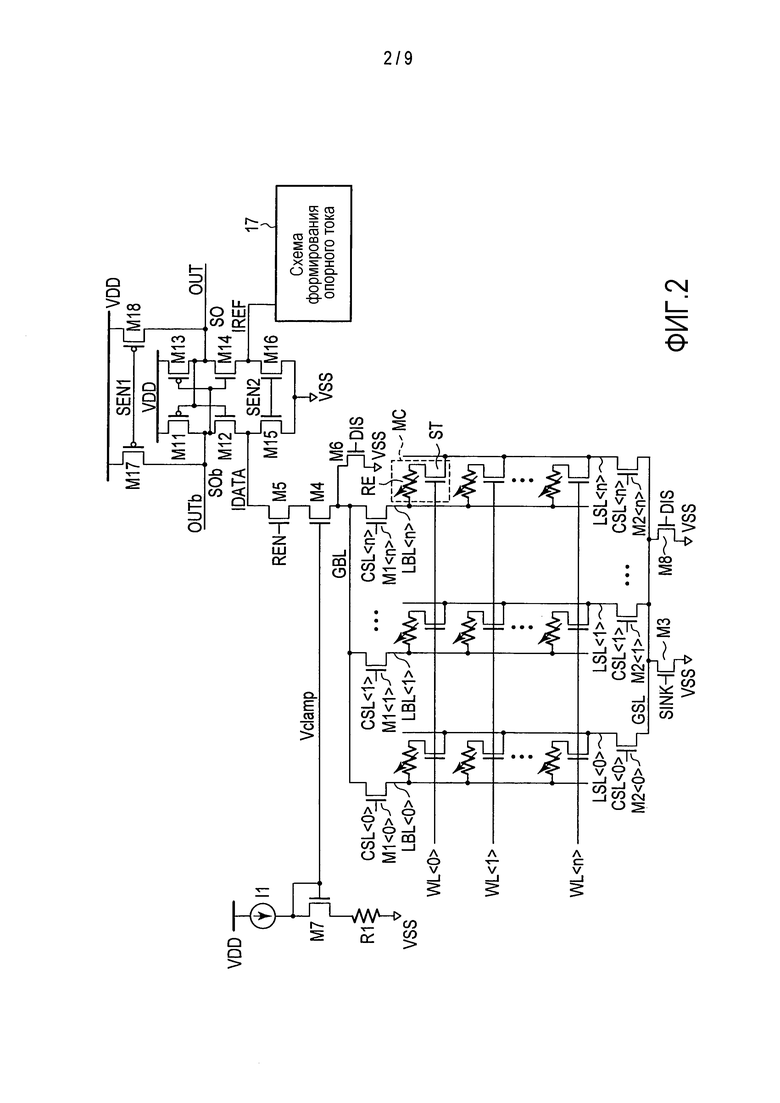

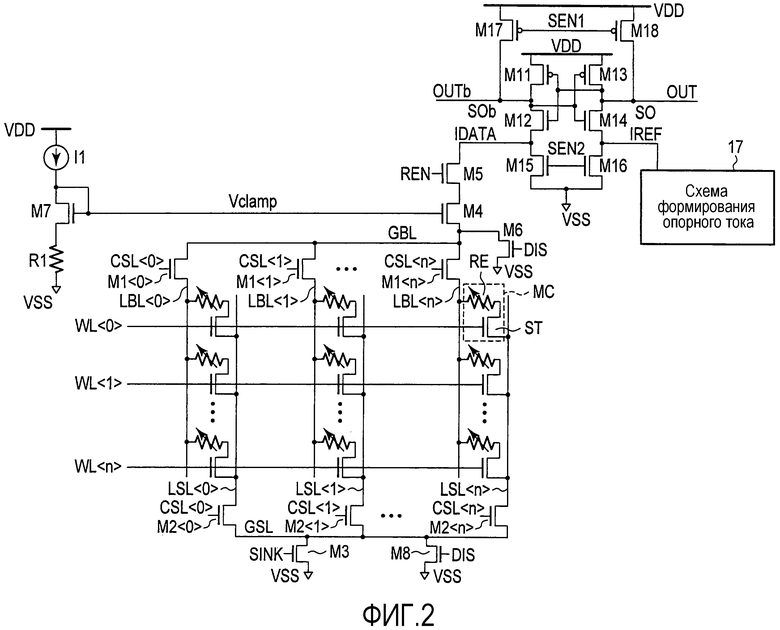

Фиг. 2 является принципиальной схемой основной составной части запоминающего устройства на основе изменения сопротивления;

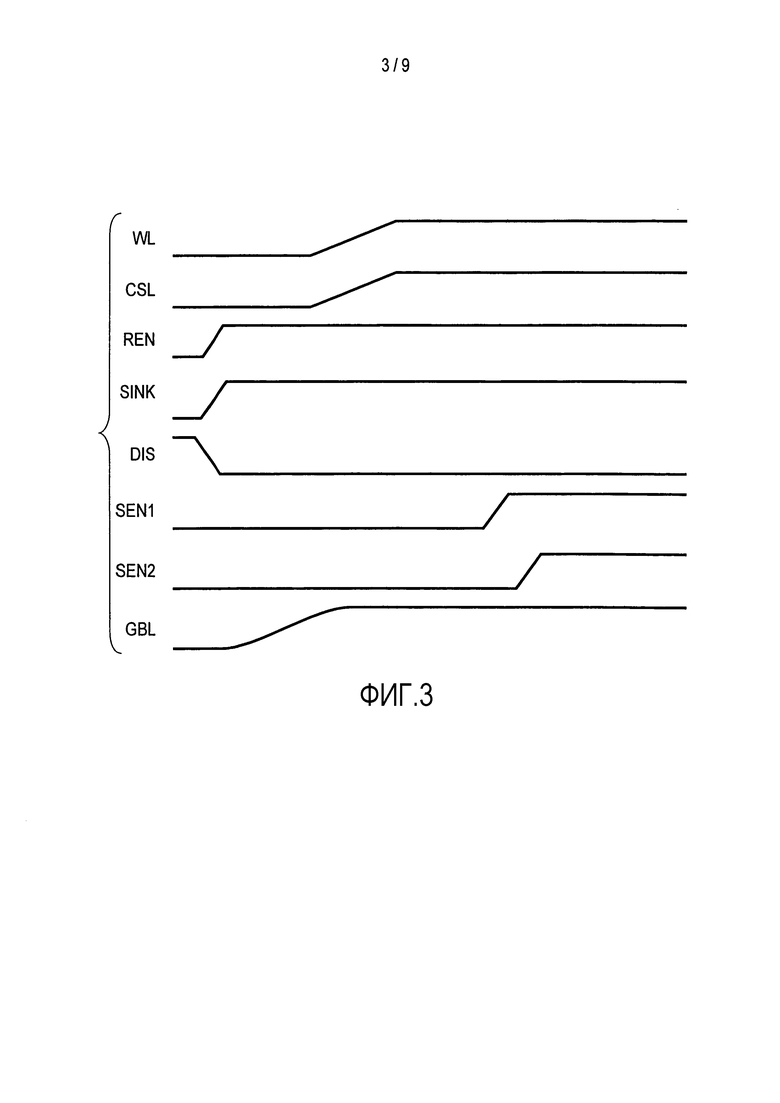

Фиг. 3 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления;

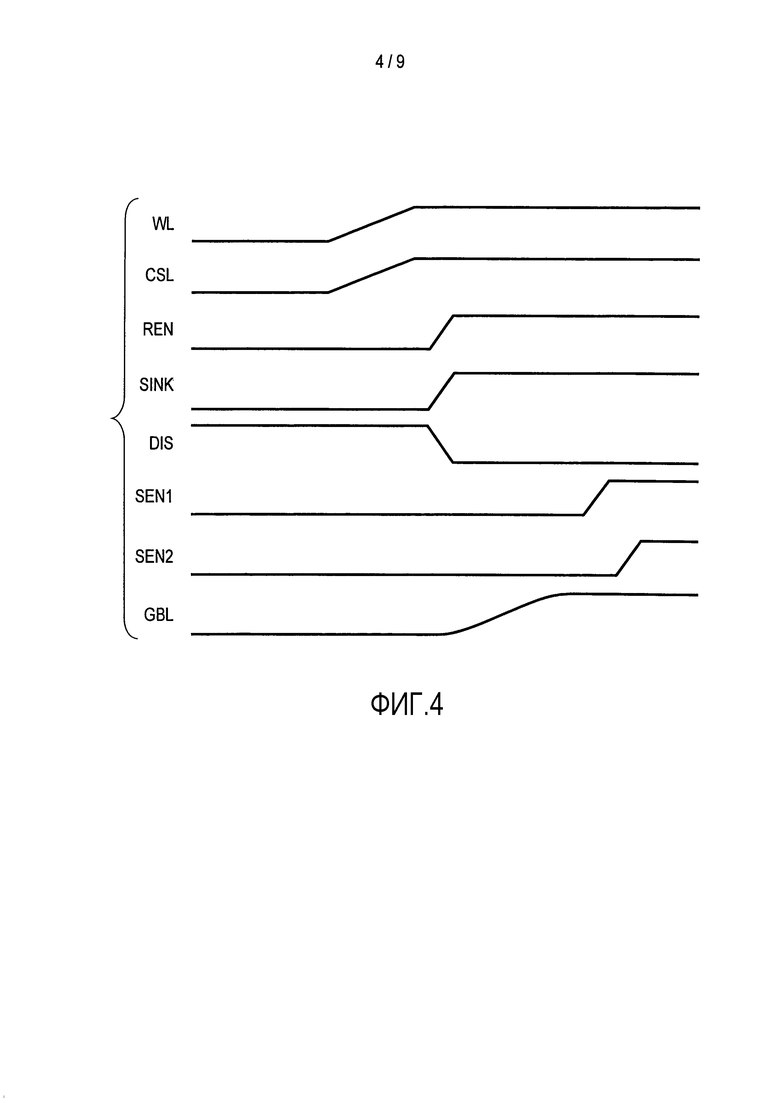

Фиг. 4 является примерной временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления в качестве сравнительного примера;

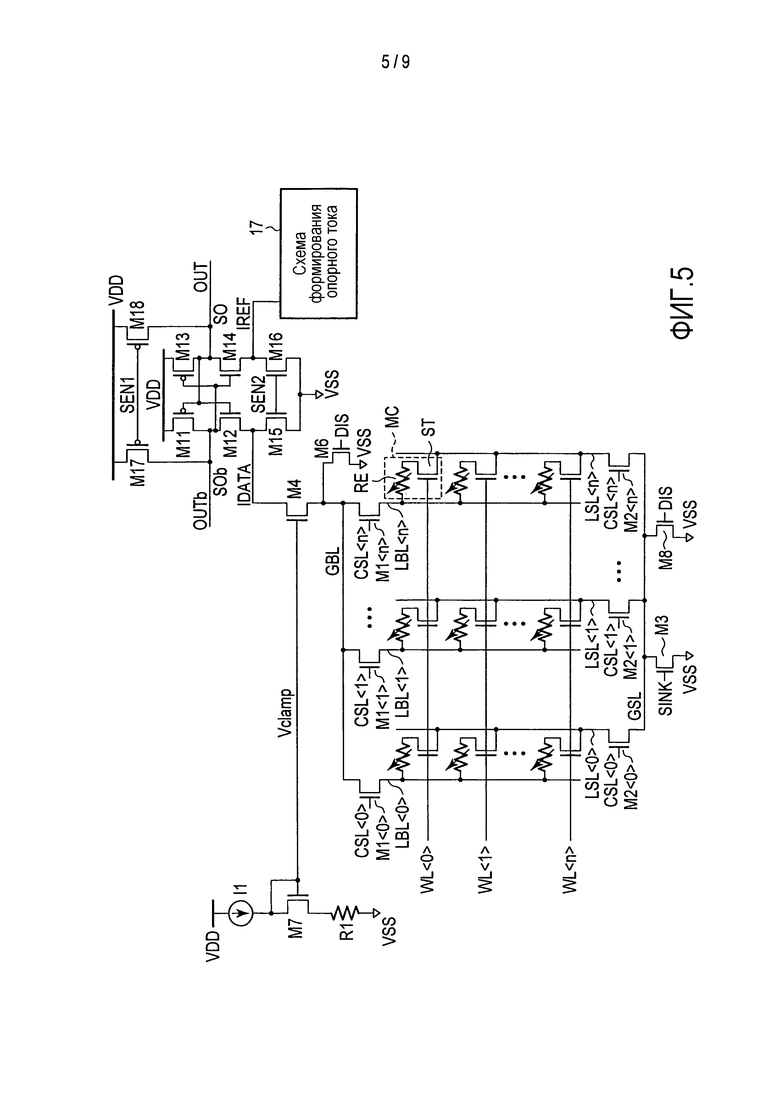

Фиг. 5 является принципиальной схемой основной составной части запоминающего устройства на основе изменения сопротивления согласно второму варианту осуществления;

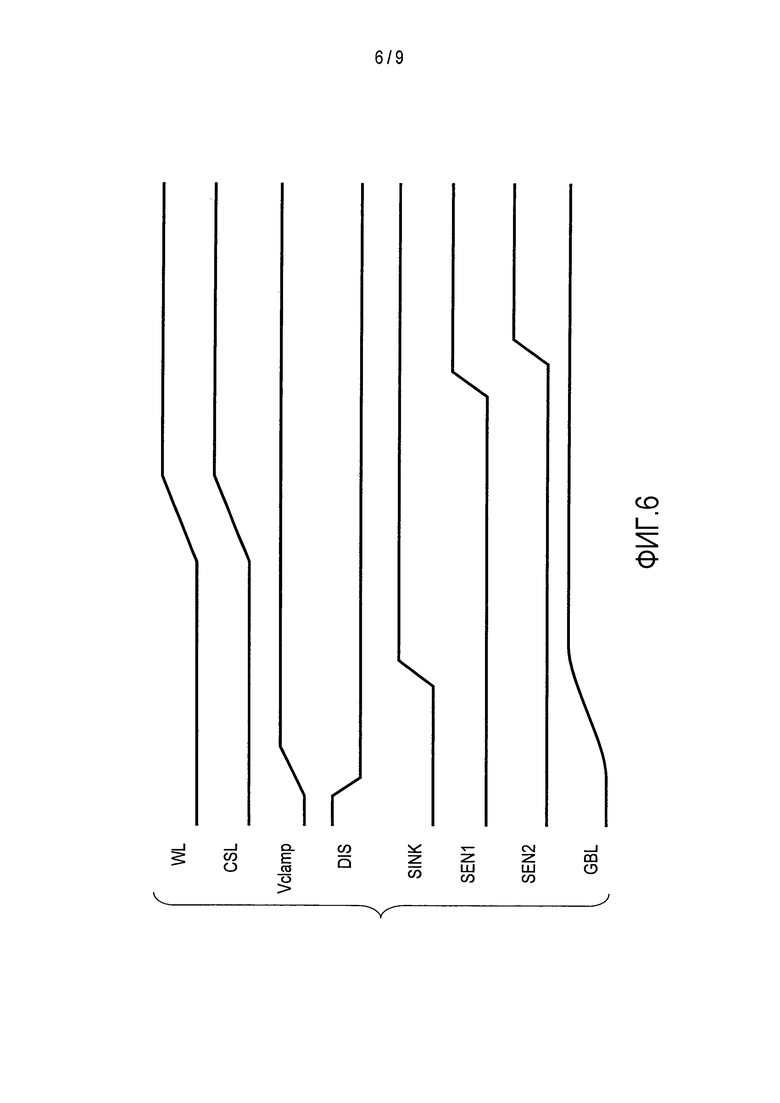

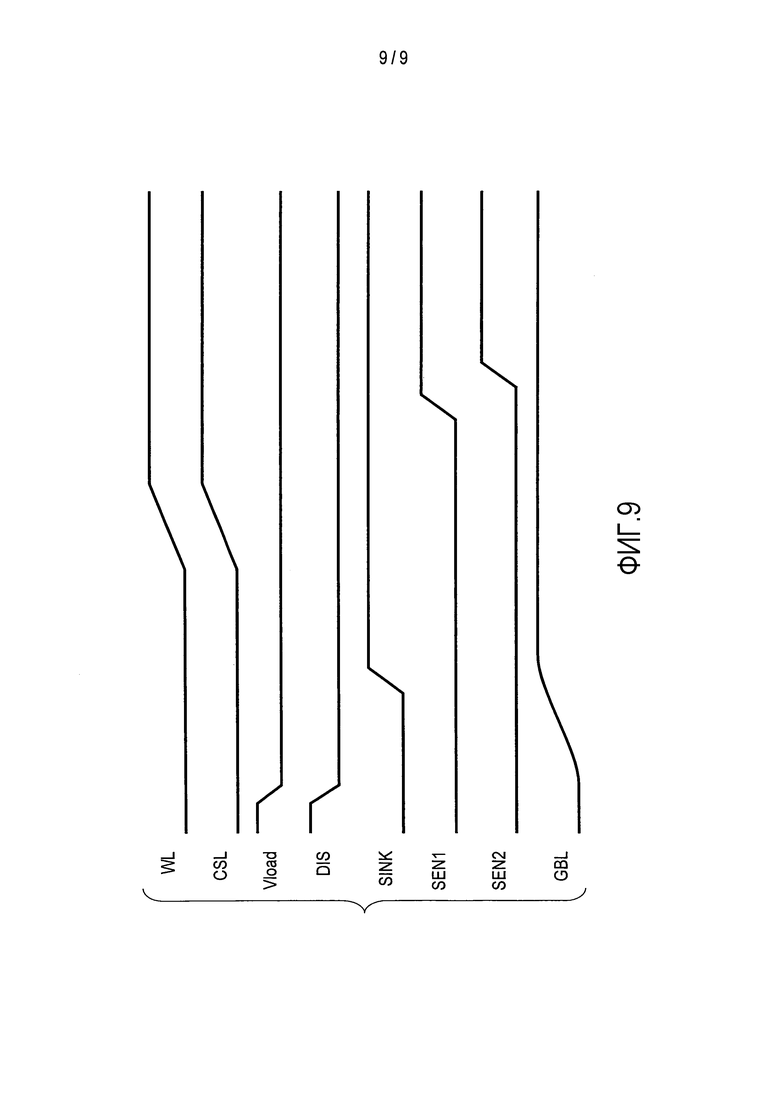

Фиг. 6 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления;

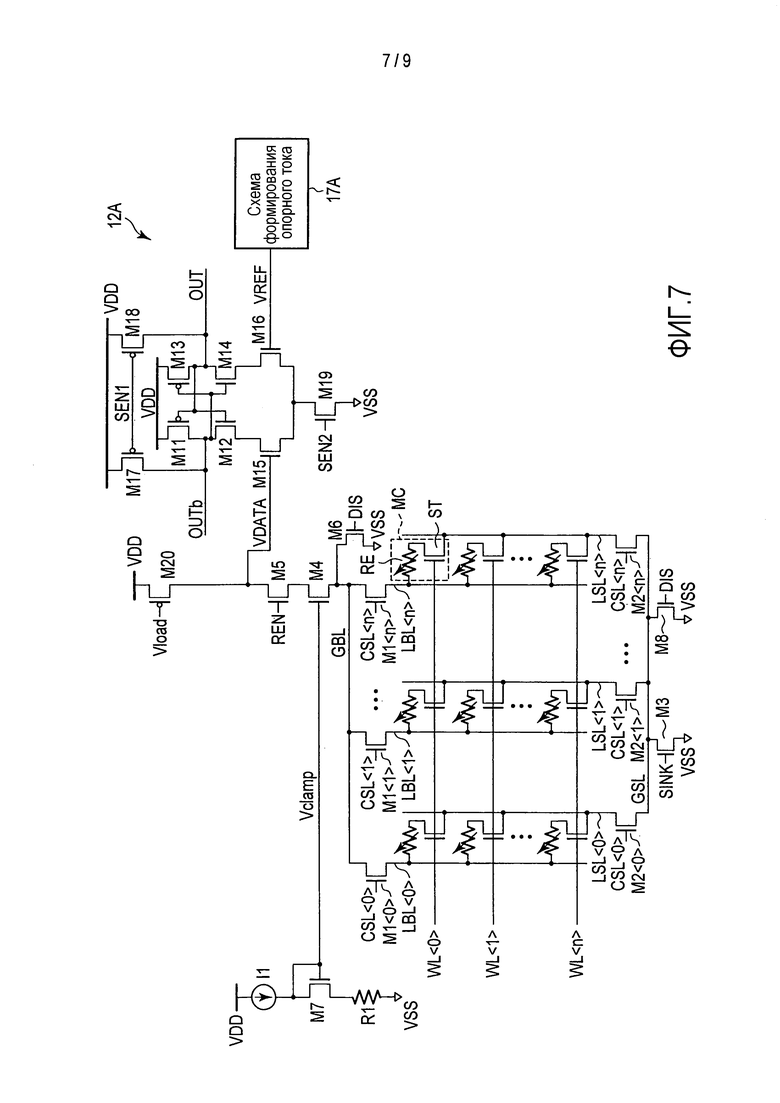

Фиг. 7 является принципиальной схемой основной составной части запоминающего устройства на основе изменения сопротивления согласно третьему варианту осуществления;

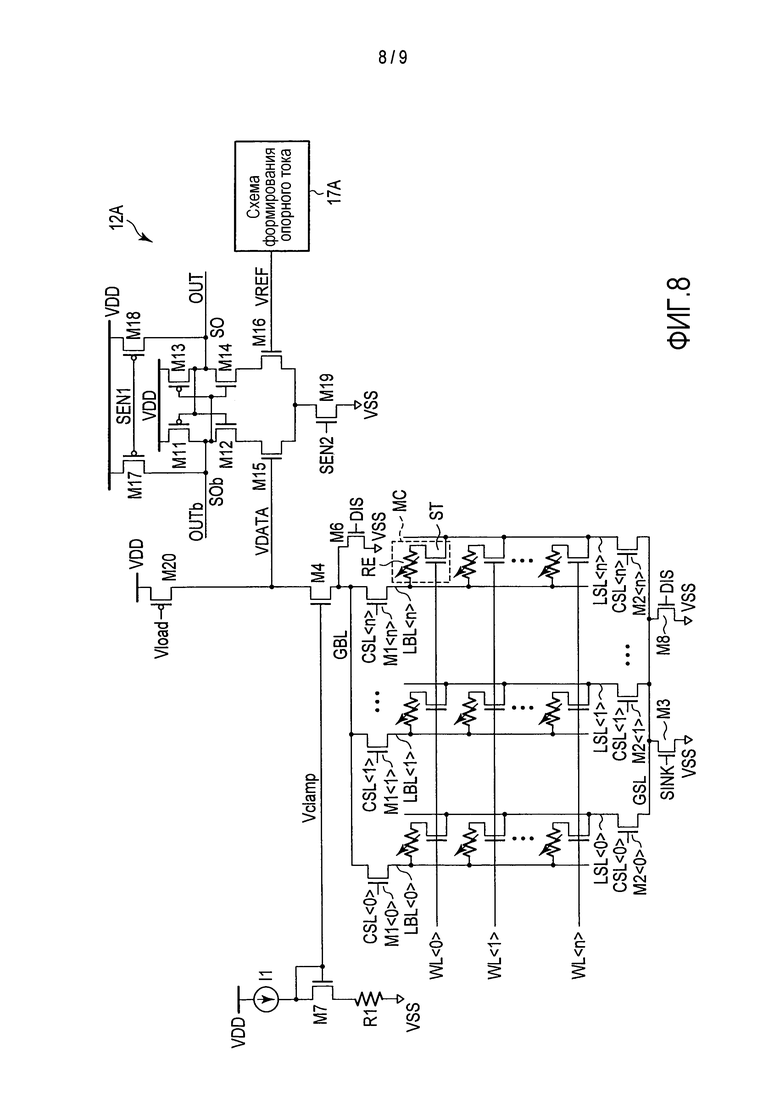

Фиг. 8 является принципиальной схемой основной составной части запоминающего устройства на основе изменения сопротивления согласно четвертому варианту осуществления; и

Фиг. 9 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно пятому варианту осуществления.

Подробное описание изобретения

В дальнейшем в этом документе описывается запоминающее устройство на основе изменения сопротивления согласно вариантам осуществления, со ссылкой на прилагаемые чертежи. В нижеприведенном описании, идентичные ссылки с номерами предоставляются для компонентов, имеющих идентичную функцию и конфигурацию, и перекрывающееся описание приводится только при необходимости.

В общем, согласно одному варианту осуществления, запоминающее устройство на основе изменения сопротивления включает в себя первую ячейку запоминающего устройства, линию слова, первую битовую линию, первый и второй инверторы и первый, второй, третий, четвертый, пятый и шестой МОП-транзисторы. Первая ячейка запоминающего устройства имеет элемент с изменяемым сопротивлением. Линия слова подключается к первой ячейке запоминающего устройства и возбуждается на основе сигнала адреса. Первая битовая линия подключается к первой ячейке запоминающего устройства при пересечении линии слова и выбирается на основе сигнала адреса. Первый инвертор имеет первый входной контактный вывод, первый выходной контактный вывод и первый и второй контактные выводы напряжения. Второй инвертор имеет второй входной контактный вывод, второй выходной контактный вывод и третий и четвертый контактные выводы напряжения. Второй входной контактный вывод подключается к первому выходному контактному выводу, и второй выходной контактный вывод подключается к первому входному контактному выводу. Первый МОП-транзистор подключается к первому выходному контактному выводу. Второй МОП-транзистор подключается ко второму выходному контактному выводу. Третий МОП-транзистор подключается к первому контактному выводу напряжения. Четвертый МОП-транзистор подключается к третьему контактному выводу напряжения. Один конец пути тока пятого МОП-транзистора подключается к первому контактному выводу напряжения. Первый сигнал подается в затвор пятого МОП-транзистора. Вторая битовая линия подключается к другому концу пути тока пятого МОП-транзистора. Шестой МОП-транзистор подключается между первой и второй битовыми линиями. Второй сигнал подается в затвор шестого МОП-транзистора. До того, как шестой МОП-транзистор включается посредством второго сигнала, пятый транзистор включается посредством первого сигнала.

Первый вариант осуществления

Фиг. 1 является видом, иллюстрирующим конфигурацию запоминающего устройства на основе изменения сопротивления согласно первому варианту осуществления.

Запоминающее устройство на основе изменения сопротивления включает в себя матрицу 11 ячеек запоминающего устройства, считывающий усилитель 12, формирователи/приемники 13 и 14 сигналов управления, формирователь 15 сигналов управления, схему 16 формирования неизменяющегося постоянного тока, схему 17 формирования опорного тока и контроллер 18.

Матрица 11 ячеек запоминающего устройства имеет множество ячеек MC запоминающего устройства, выстраиваемых матричным способом. Ячейки MC запоминающего устройства подключаются между локальной битовой линией LBL<0> и локальной линией LSL<0> истока, между локальной битовой линией LBL<1> и локальной линией LSL<1>, … истока и между локальной битовой линией LBL<n> и локальной линией LSL<n> истока, соответственно. Кроме того, ячейки запоминающего устройства подключаются к линиям слова WL<0>-WL<n>, соответственно. Другими словами, ячейки MC запоминающего устройства размещаются в местоположениях, в которых линии слова WL<0>-WL<n> пересекают как локальные битовые линии LBL<0>-LBL<n>, так и локальные линии LSL<0>-LSL<n> истока, соответственно. Следует отметить, что n представляет 0, 1, 2, …, или n.

Одни из локальных битовых линий LBL<0>-LBL<n> подключаются к глобальной битовой линии GBL через полевые МОП-транзисторы M1<0>-M1<n> с каналом n-типа (в дальнейшем в этом документе, называемые "n-МОП-транзисторами"), соответственно. Сигналы CSL<0>-CSL<n> выбора столбца подаются в затворы n-МОП-транзисторов M1<0>-M1<n>, соответственно. Другой конец каждой из локальных битовых линий LBL<0>-LBL<n> подключается к множеству ячеек MC запоминающего устройства.

Глобальная битовая линия GBL подключается к формирователю/приемнику 14 сигналов управления. Кроме того, глобальная битовая линия GBL подключается к считывающему усилителю 12 через n-МОП-транзистор M4. Затвор n-МОП-транзистора M4 подключается к схеме 16 формирования неизменяющегося постоянного тока для формирования неизменяющегося постоянного тока. Глобальная битовая линия GBL подключается к контактному выводу опорного напряжения, такому как контактный вывод Vss потенциала земли, через n-МОП-транзистор M6. Сигнал DIS разряда подается в затвор n-МОП-транзистора M6.

Одни концы локальных линий LSL<0>-LSL<n> истока подключаются к глобальной линии GSL истока через n-МОП-транзисторы M2<0>-M2<n>, соответственно. Сигналы CSL<0>-CSL<n> выбора столбца подаются в затворы n-МОП-транзисторов M2<0>-M2<n>, соответственно. Другой конец каждой из локальных линий LSL<0>-LSL<n> истока подключается к множеству ячеек MC запоминающего устройства.

Глобальная линия GSL истока подключается к формирователю/приемнику 13 сигналов управления. Кроме того, глобальная линия GSL истока подключается к концу опорного напряжения, такому как контактный вывод Vss потенциала земли, через n-МОП-транзистор M3. Сигнал SINK подается в затвор n-МОП-транзистора M3. Кроме того, глобальная линия GSL истока подключается к контактному выводу опорного напряжения, такому как контактный вывод Vss потенциала земли, через n-МОП-транзистор M8. Сигнал DIS разряда подается в затвор n-МОП-транзистора M8.

Формирователи/приемники 13 и 14 сигналов управления подают ток записи в каждую ячейку MC запоминающего устройства в направлении согласно данным, которые должны быть записаны в ходе операции записи. Таким образом, формирователи/приемники 13 и 14 сигналов управления записывают данные в каждую ячейку MC запоминающего устройства.

Линии слова WL<0>-WL<n> подключаются к формирователю 15 сигналов управления для возбуждения линий слова WL<0>-WL<n>.

Затвор n-МОП-транзистора M4 подключается к схеме 16 формирования неизменяющегося постоянного тока для формирования неизменяющегося постоянного тока. Считывающий усилитель 12 подключается к схеме 17 формирования опорного тока для подачи опорного тока в считывающий усилитель 12. Кроме того, контроллер 18 подключается как к формирователю 15 сигналов управления, так и к считывающему усилителю 12. Контроллер 18 управляет операциями, выполняемыми посредством отдельных частей вышеуказанного запоминающего устройства на основе изменения сопротивления. Например, контроллер 18 формирует управляющий сигнал, который должен подаваться в считывающий усилитель 12, и управляет операцией считывания, выполняемой посредством считывающего усилителя 12.

Фиг. 2 является принципиальной схемой конфигурации матрицы 11 ячеек запоминающего устройства, считывающего усилителя 12 и схемы 16 формирования неизменяющегося постоянного тока на фиг. 1.

В дальнейшем в этом документе описывается конфигурация матрицы 11 ячеек запоминающего устройства.

Матрица 11 ячеек запоминающего устройства имеет множество ячеек MC запоминающего устройства, размещаемых матричным способом в местоположениях, в которых линии слова WL<0>-WL<n> пересекают как локальные битовые линии LBL<0>-LBL<n>, так и локальные линии LSL<0>-LSL<n> истока, соответственно, как описано выше. Следует отметить, что n представляет 0, 1, 2, …, или n.

Каждая ячейка MC запоминающего устройства включает в себя, например, элемент RE с изменяемым сопротивлением и транзистор ST выбора. Элемент RE с изменяемым сопротивлением представляет собой элемент, который выполнен с возможностью изменять свое сопротивление посредством подачи тока или приложения напряжения. Примеры элемента RE с изменяемым сопротивлением включают в себя, но не только, элемент с магнитным туннельным переходом (MTJ), переменный резистивный элемент, элемент с фазовым переходом и ферроэлектрический элемент. Затвор транзистора ST выбора подключается к линии слова WL. Транзистор ST выбора включается посредством линии слова WL, в силу чего выбирается ячейка MC запоминающего устройства.

Одни из локальных битовых линий LBL<0>-LBL<n> подключаются к глобальной битовой линии GBL через транзисторы M1<0>-M1<n> выбора столбца, соответственно. Сигналы CSL<0>-CSL<n> выбора столбца подаются в затворы транзисторов M1<0>-M1<n> выбора столбца, соответственно.

Глобальная битовая линия GBL подключается к соединительному узлу между n-МОП-транзисторами M12 и M15 в считывающем усилителе 12 через фиксирующий транзистор M4 и транзистор M5 переноса, пути тока которых подключены последовательно между собой. Кроме того, глобальная битовая линия GBL подключается к контактному выводу опорного напряжения, такому как контактный вывод Vss потенциала земли, через разрядный транзистор M6. Сигнал DIS разряда подается в затвор разрядного транзистора M6.

Одни концы локальных линий LSL<0>-LSL<n> истока подключаются к глобальной линии GSL истока через транзисторы M2<0>-M2<n> выбора столбца, соответственно. Сигналы CSL<0>-CSL<n> выбора столбца подаются в затворы транзисторов M2<0>-M2<n> выбора столбца, соответственно.

Глобальная линия GSL истока подключается к контактному выводу опорного напряжения, такому как контактный вывод Vss потенциала земли, через транзистор M3 переноса. Сигнал SINK подается в затвор транзистора M3 переноса. Кроме того, глобальная линия GSL истока подключается к опорному напряжению, такому как контактный вывод Vss потенциала земли, через разрядный транзистор M8. Сигнал DIS разряда подается в затвор разрядного транзистора M8.

В дальнейшем в этом документе описывается конфигурация считывающего усилителя 12.

Считывающий усилитель 12 представляет собой тип на основе считывания током считывающего усилителя. Считывающий усилитель 12 содержит: первый инвертор, включающий в себя полевой транзистор M11 (в дальнейшем в этом документе называемый "p-МОП-транзистором") с каналом p-типа и n-МОП-транзистор M12; второй инвертор, включающий в себя p-МОП-транзистор M13 и n-МОП-транзистор M14; n-МОП-транзисторы M15 и M16; и p-МОП-транзисторы M17 и M18.

Первый инвертор (транзисторы M11 и M12) включает в себя первый входной контактный вывод, первый выходной контактный вывод и первый и второй контактные выводы напряжения. Второй инвертор (транзисторы M13 и M14) включает в себя второй входной контактный вывод, второй выходной контактный вывод и третий и четвертый контактные выводы напряжения. Второй входной контактный вывод подключается к первому выходному контактному выводу, и второй выходной контактный вывод подключается к первому входному контактному выводу.

Первый выходной контактный вывод первого инвертора подключается к стоку p-МОП-транзистора M17, и исток p-МОП-транзистора M17 подключается к контактному выводу VDD напряжения питания. Второй выходной контактный вывод второго инвертора подключается к стоку p-МОП-транзистора M18, и исток p-МОП-транзистора M18 подключается к контактному выводу VDD напряжения питания. Первый сигнал SEN1 разрешения считывания из контроллера 18 подается в оба затвора n-МОП-транзисторов M17 и M18.

Первый контактный вывод напряжения первого инвертора (или исток транзистора M12) подключается к стоку n-МОП-транзистора M15, и исток n-МОП-транзистора M15 подключается к контактному выводу Vss потенциала земли. Третий контактный вывод напряжения второго инвертора (или исток транзистора M14) подключается к стоку n-МОП-транзистора M16, и исток n-МОП-транзистора M16 подключается к контактному выводу Vss потенциала земли. Второй сигнал SEN2 разрешения считывания из контроллера 18 подается в оба затвора n-МОП-транзисторов M15 и M16.

Первый контактный вывод напряжения первого инвертора (или исток транзистора M12) подключается к стоку n-МОП-транзистора M5. Сигнал REN разрешения считывания из контроллера 18 подается в затвор n-МОП-транзистора M5. Исток n-МОП-транзистора M5 подключается к глобальной битовой линии GBL через n-МОП-транзистор M4. Затвор n-МОП-транзистора M4 подключается к схеме 16 формирования неизменяющегося постоянного тока.

Третий контактный вывод напряжения второго инвертора (или исток транзистора M14) подключается к схеме 17 формирования опорного тока. Схема 17 формирования опорного тока выполнена с возможностью подавать опорный ток IREF в считывающий усилитель 12. Здесь, опорный ток IREF задается равным промежуточному значению между токами соответствующих ячеек, которые инструктируют ячейке запоминающего устройства сохранять "0" и "1". Этот опорный ток IREF формируется, например, посредством опорной ячейки.

В дальнейшем в этом документе описывается конфигурация схемы 16 формирования неизменяющегося постоянного тока.

Затвор n-МОП-транзистора M4 подключается к схеме 16 формирования неизменяющегося постоянного тока. Схема 16 формирования неизменяющегося постоянного тока прикладывает фиксирующее напряжение Vclamp (например, 0,1-0,6 В), которое представляет собой предварительно установленное аналоговое напряжение, к затвору n-МОП-транзистора M4 в ходе операции считывания. В ответ, напряжение в стоке n-МОП-транзистора M4 фиксируется неизменяющимся постоянным. Это неизменяющееся постоянное напряжение служит цели ограничения тока, протекающего через каждую ячейку MC запоминающего устройства, таким образом, что он не превышает верхний предел, за счет этого предотвращая повреждение данных, сохраненных в выбранной одной из ячеек MC запоминающего устройства.

Схема 16 формирования неизменяющегося постоянного тока включает в себя источник I1 неизменяющегося постоянного тока, n-МОП-транзистор M7 и резистор R1. Сток n-МОП-транзистора M7 подключается к контактному выводу VDD напряжения питания через источник I1 неизменяющегося постоянного тока и подключается к затвору самого n-МОП-транзистора M7. Исток n-МОП-транзистора M7 подключается к контактному выводу Vss потенциала земли через резистор R1.

Далее приводится описание операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно первому варианту осуществления, со ссылкой на фиг. 3.

Фиг. 3 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления.

Состояние ожидания, которое предполагается до того, как инициируется операция считывания, заключается в следующем.

В считывающем усилителе 12, первый сигнал SEN1 разрешения считывания имеет низкий уровень, который инструктирует p-МОП-транзисторам M17 и M18 находиться во включенном состоянии, и второй сигнал SEN2 разрешения считывания имеет низкий уровень, который инструктирует обоим p-МОП-транзисторам M15 и M16 находиться в отключенном состоянии. Кроме того, сигнал REN разрешения считывания имеет низкий уровень, который инструктирует n-МОП-транзистору M5 находиться в отключенном состоянии. Как результат, оба потенциала напряжения в узлах SO и SOb предварительно заряжаются при потенциале напряжения VDD питания, и считывающий усилитель 12 допускает состояние ожидания.

Фиксирующее напряжение Vclamp, которое представляет собой постоянное аналоговое напряжение, прикладывается к n-МОП-транзистору M4, и n-МОП-транзистор M4 находится во включенном состоянии в течение состояния ожидания.

В матрице 11 ячеек запоминающего устройства, линия слова WL<n> находится в неактивном состоянии (или в состоянии низкого уровня), и сигнал CSL<n> выбора столбца находится в состоянии низкого уровня, который инструктирует n-МОП-транзистору M1<n> находиться в отключенном состоянии.

После того, как оба потенциала напряжения на глобальной битовой линии GBL и глобальной линии GSL истока разряжаются при потенциале Vss напряжения земли, в то время как оба разрядных транзистора M6 и M8 находятся во включенном состоянии, оба разрядных транзистора M6 и M8 выключаются посредством сигнала DIS разряда. Необязательно могут предоставляться разрядные транзисторы M6 и M8. Дополнительно, транзистор M3 приемника в выключенном состоянии включается. Предпочтительно, чтобы время, когда транзистор M3 приемника включается, задавалось до того, как ток считывания протекает через ячейку MC запоминающего устройства.

В вышеуказанном состоянии, внешний источник вводит команду активации и сигнал адреса в контроллер 18 запоминающего устройства на основе изменения сопротивления. В ответ, контроллер 18 формирует сигнал активации банка для активации банка на основе сигнала адреса и активирует банк, который должен использоваться, посредством использования сигнала активации банка.

В это время, контроллер 18 задает уровень сигнала REN разрешения считывания как высокий уровень через сигнал адреса или сигнал активации банка, за счет этого включая n-МОП-транзистор M5. Как результат, электрический ток вытекает из считывающего усилителя 12 в глобальную битовую линию GBL через n-МОП-транзисторы M4 и M5, так что заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL. Следует отметить, что сигнал активации банка используется в вышеприведенном описании, но другой внутренний сигнал, сформированный из сигнала адреса, может использоваться вместо сигнала активации банка.

В свою очередь, в матрице 11 ячеек запоминающего устройства, локальная битовая линия LBL<n> и локальная линия LSL<n> истока выбираются через сигнал CSL<n> выбора столбца. Помимо этого, линия слова WL<n> возбуждается, так что выбирается ячейка MC запоминающего устройства, которая должна считываться. В частности, посредством задания уровня сигнала CSL<n> выбора столбца как высокого уровня, n-МОП-транзисторы M1<n> и M2<n> включаются. Как результат, локальная битовая линия LBL<n> подключается к глобальной битовой линии GBL, и локальная линия LSL<n> истока подключается к глобальной линии GSL истока.

Кроме того, посредством задания уровня линии слова WL<n> как высокого уровня, транзистор ST выбора включается. Как результат, выбирается ячейка MC запоминающего устройства, которая должна считываться. В этом случае, n-МОП-транзистор M3 находится во включенном состоянии через сигнал SINK в ходе операции считывания. Посредством вышеуказанной обработки, ток считывания подается из считывающего усилителя 12 в выбранную ячейку MC запоминающего устройства.

Затем, посредством задания уровня первого сигнала SEN1 разрешения считывания как высокого уровня, оба p-МОП-транзистора M17 и M18 выключаются. Как результат, предварительный заряд обоих узлов SO и SOb прекращается. Затем ток считывания становится током, поданным только из контактного вывода VDD напряжения питания, к которому подключены оба стока n-МОП-транзисторов M11 и M13. В этом случае, ток считывания изменяется в зависимости от данных ("0" или "1"), сохраненных в выбранной ячейке MC запоминающего устройства. Другими словами, ток считывания изменяется в зависимости от того, какое из состояний с низким и высоким сопротивлением допускает выбранная ячейка MC запоминающего устройства. Ток считывания, измененный таким образом, а именно, в зависимости от данных выбранной ячейки MC запоминающего устройства, означает ток IDATA ячейки.

После этого, посредством задания уровня второго сигнала SEN2 разрешения считывания как высокого уровня, оба n-МОП-транзистора M15 и M16 включаются. В ответ, опорный ток IREF, возбужденный посредством схемы 17 формирования опорного тока, сравнивается с током IDATA ячейки. Как результат, уровень защелкивающей схемы, включающий в себя p-МОП-транзисторы M11 и M13 и n-МОП-транзисторы M12 и M14, сохраняется на высоком или низком уровне, в соответствии с результатом сравнения. В завершение, (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме, выводятся из узлов SO и SOb в качестве выходных сигналов OUT и OUTb, соответственно.

Здесь, опорный ток IREF задается равным промежуточному значению между токами соответствующих ячеек, которые инструктируют ячейке запоминающего устройства сохранять "0" и "1". Опорный ток IREF может формироваться, например, посредством опорной ячейки запоминающего устройства.

Как описано выше, n-МОП-транзистор M5 включается посредством сигнала REN разрешения считывания, тем самым заряжая глобальную битовую линию GBL заранее. Затем ячейка MC запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца и линии слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Другими словами, глобальная битовая линия GBL предварительно заряжается до того, как ячейка MC запоминающего устройства выбирается через сигнал CSL<n> выбора столбца и затем линию слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Следовательно, можно сокращать время считывания на время, требуемое для заряда глобальной битовой линии GBL.

В первом варианте осуществления, после того, как предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, операция считывания выполняется посредством выбора ячейки запоминающего устройства через сигнал CSL<n> выбора столбца и подачи тока считывания в выбранную ячейку запоминающего устройства. Этот вариант осуществления обеспечивает возможность исключения времени заряда битовой линии, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания.

Кроме того, посредством использования сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса, формируется сигнал для инициирования заряда маршрута считывания (сигнал REN разрешения считывания). Другими словами, сигнал адреса или внутренний сигнал, сформированный из сигнала адреса, инициирует заряд маршрута считывания. Соответственно, можно эффективно задавать время инициирования заряда маршрута считывания.

Кроме того, в этом варианте осуществления, битовые линии предварительно заряжаются с помощью тока, поданного из считывающего усилителя, как описано выше. Следовательно, этот вариант осуществления исключает необходимость установки дополнительной схемы предварительного заряда, а также не допускает увеличения площади.

Фиг. 4 является примерной временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления в качестве сравнительного примера.

Во-первых, в соответствии с входной информацией адреса, активируется линия слова WL<n>, и уровень сигналов CSL<n> выбора столбца задается как высокий уровень, который включает n-МОП-транзисторы M1<n> и M2<n>, как проиллюстрировано на фиг. 4. Затем уровень сигнала REN разрешения считывания задается как высокий уровень, который включает n-МОП-транзистор M5. В этом случае, n-МОП-транзистор M3 находится во включенном состоянии через сигнал SINK в ходе операции считывания.

Как результат, ток подается из считывающего усилителя 12 в глобальную битовую линию GBL через n-МОП-транзисторы M4 и M5, так что разряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, и ток считывания протекает через выбранную ячейку MC запоминающего устройства.

В свою очередь, оба уровня первого и второго сигналов SEN1 и SEN2 разрешения считывания задаются как высокий уровень. Как результат, уровень защелкивающей схемы сохраняется на высоком или низком уровне, в соответствии с данными, сохраненными в выбранной ячейке MC запоминающего устройства. В завершение, выводятся (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме.

В ходе операции считывания так, как показано на фиг. 4, активируется сигнал REN разрешения считывания, и затем емкость маршрута считывания (в основном, глобальной битовой линии GBL) заряжается в соответствии со своей постоянной времени RC. Как результат, сигнал появляется на маршруте считывания. Тем не менее, время заряда для маршрута считывания, как описано выше, непосредственно не способствует операции считывания ячейки запоминающего устройства. Если это время заряда значительно продлевается, это может влиять на время считывания. Другими словами, время заряда может излишне продлевать время считывания.

Напротив, в первом варианте осуществления, маршрут считывания заряжается посредством активации сигнала начала считывания (или сигнала REN разрешения считывания) заранее через сигнал адреса или внутренний сигнал, сформированный из сигнала адреса. После этого активируются линия слова WL и сигнал CSL выбора столбца, затем деактивируется инициализирующий сигнал (или первый сигнал SEN1 разрешения считывания) для считывающего усилителя, и активируется сигнал начала защелкивания (или второй сигнал SEN2 разрешения считывания). В завершение, ток считывания подается в выбранную ячейку MC запоминающего устройства, и считываются данные, сохраненные в выбранной ячейке MC запоминающего устройства.

В этом варианте осуществления, как описано выше, предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию, и затем ток считывания подается в выбранную ячейку запоминающего устройства, так что инициируется операция считывания. Этот вариант осуществления позволяет сокращать время заряда для маршрута считывания, за счет этого сокращая время считывания. Кроме того, в этом варианте осуществления, маршрут считывания, включающий в себя глобальную битовую линию, предварительно заряжается с помощью тока, поданного из считывающего усилителя, как описано выше. Следовательно, этот вариант осуществления исключает необходимость установки дополнительной схемы предварительного заряда, а также не допускает увеличения площади.

Второй вариант осуществления

Что касается второго варианта осуществления, приводится описание примера предварительного заряда глобальной битовой линии посредством переключения фиксирующего транзистора M4.

Фиг. 5 является принципиальной схемой конфигурации матрицы 11 ячеек запоминающего устройства, считывающего усилителя 12 и схемы 16 формирования неизменяющегося постоянного тока во втором варианте осуществления.

Запоминающее устройство на основе изменения сопротивления согласно второму варианту осуществления имеет схему, эквивалентную схеме по фиг. 2, из которой исключается транзистор M5 переноса, расположенный между фиксирующим транзистором M4 и считывающим усилителем 12, как проиллюстрировано на фиг. 5. Оставшаяся конфигурация запоминающего устройства на основе изменения сопротивления согласно второму варианту осуществления, а именно, другие конфигурации матрицы ячеек запоминающего устройства, считывающего усилителя и схемы формирования неизменяющегося постоянного тока являются идентичным конфигурациям первого варианта осуществления, приведенным на фиг. 1 и 2. Следовательно, их описания опускаются.

Во-первых, приводится описание операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно второму варианту осуществления, со ссылкой на фиг. 6.

Фиг. 6 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления.

Состояние ожидания, которое предполагается до того, как инициируется операция считывания, является идентичным состоянию, как проиллюстрировано на фиг. 3.

В вышеуказанном состоянии, внешний источник вводит команду активации и сигнал адреса в контроллер 18 запоминающего устройства на основе изменения сопротивления. В ответ, контроллер 18 формирует сигнал активации банка для активации банка на основе сигнала адреса и активирует банк, который должен использоваться, через сигнал активации банка.

В вышеописанном случае, сигнал адреса или сигнал активации банка инициирует приложение фиксирующего напряжения Vclamp к затвору n-МОП-транзистора M4. Когда фиксирующее напряжение Vclamp достигает предварительно определенного уровня, n-МОП-транзистор M4 включается. Как результат, электрический ток вытекает из считывающего усилителя 12 в глобальную битовую линию GBL через n-МОП-транзистор M4, так что заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL. Следует отметить, что сигнал активации банка используется в вышеприведенном описании, но другой внутренний сигнал, сформированный из сигнала адреса, может использоваться вместо сигнала активации банка.

В свою очередь, в матрице 11 ячеек запоминающего устройства, локальная битовая линия LBL<n> и локальная линия LSL<n> истока выбираются через сигнал CSL<n> выбора столбца. Помимо этого, линия слова WL<n> возбуждается, так что выбирается ячейка MC запоминающего устройства, которая должна считываться. В частности, посредством задания уровня сигнала CSL<n> выбора столбца как высокого уровня, оба n-МОП-транзистора M1<n> и M2<n> включаются. Как результат, локальная битовая линия LBL<n> подключается к глобальной битовой линии GBL, и локальная линия LSL<n> истока подключается к глобальной линии GSL истока. Кроме того, посредством задания уровня линии слова WL<n> как высокого уровня, транзистор ST выбора включается. Как результат, выбирается ячейка MC запоминающего устройства, которая должна считываться. В этом случае, n-МОП-транзистор M3 находится во включенном состоянии через сигнал SINK в ходе операции считывания. Посредством вышеуказанной обработки, ток считывания подается из считывающего усилителя 12 в выбранную ячейку MC запоминающего устройства.

Затем, посредством задания уровня первого сигнала SEN1 разрешения считывания как высокого уровня, оба p-МОП-транзистора M17 и M18 выключаются. Как результат, предварительный заряд обоих узлов SO и SOb прекращается. Затем ток считывания становится током, поданным только из контактного вывода VDD напряжения питания, к которому подключены оба стока n-МОП-транзисторов M11 и M13. В этом случае, ток считывания изменяется в зависимости от данных, сохраненных в выбранной ячейке MC запоминающего устройства.

После этого, посредством задания уровня второго сигнала SEN2 разрешения считывания как высокого уровня, оба n-МОП-транзистора M15 и M16 включаются. В ответ, опорный ток IREF, возбужденный посредством схемы 17 формирования опорного тока, сравнивается с током IDATA ячейки. Как результат, уровень защелкивающей схемы, включающей в себя p-МОП-транзисторы M11 и M13 и n-МОП-транзисторы M12 и M14, сохраняется на высоком или низком уровне, в соответствии с результатом сравнения. В завершение, (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме, выводятся из узлов SO и SOb в качестве выходных сигналов OUT и OUTb, соответственно.

Как описано выше, n-МОП-транзистор M4 включается посредством фиксирующего напряжения Vclamp, и глобальная битовая линия GBL заряжается заранее. Затем ячейка MC запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца и линии слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Другими словами, глобальная битовая линия GBL предварительно заряжается до того, как ячейка MC запоминающего устройства выбирается через сигнал CSL<n> выбора столбца и линию слова WL<n>, и затем ток считывания подается в выбранную ячейку MC запоминающего устройства. Следовательно, можно сокращать время считывания на время, требуемое для заряда глобальной битовой линии GBL.

Во втором варианте осуществления, как описано выше, после того, как предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, ячейка запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца, и ток считывания подается в выбранную ячейку запоминающего устройства, так что инициируется операция считывания. Этот вариант осуществления обеспечивает возможность исключения времени заряда битовой линии, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания.

Кроме того, посредством использования сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса, инициируется подача сигнала для указания верхнего предела тока, протекающего через выбранную ячейку MC запоминающего устройства (или приложение фиксирующего напряжения Vclamp). Другими словами, сигнал адреса или внутренний сигнал, сформированный из сигнала адреса, инициирует заряд маршрута считывания. Соответственно, можно эффективно задавать время инициирования заряда маршрута считывания.

Кроме того, в этом варианте осуществления, битовые линии предварительно заряжаются с помощью тока, поданного из считывающего усилителя, как описано выше. Следовательно, этот вариант осуществления исключает необходимость установки дополнительной схемы предварительного заряда, а также не допускает увеличения площади.

Третий вариант осуществления

В вышеуказанных первом и втором вариантах осуществления, предоставлено запоминающее устройство на основе изменения сопротивления, оснащенное типом на основе считывания током считывающего усилителя. Между тем, что касается третьего варианта осуществления, приводится описание запоминающего устройства на основе изменения сопротивления, оснащенного типом на основе считывания напряжением считывающего усилителя.

Фиг. 7 является принципиальной схемой конфигурации матрицы 11 ячеек запоминающего устройства, типа на основе считывания напряжением считывающего усилителя 12A, схемы 16 формирования неизменяющегося постоянного тока и схемы 17A формирования опорного напряжения в третьем варианте осуществления.

В дальнейшем в этом документе описывается конфигурация матрицы 11 ячеек запоминающего устройства.

Глобальная битовая линия GBL подключается к затвору n-МОП-транзистора M15 в считывающем усилителе 12A через n-МОП-транзистор M4 (фиксирующий транзистор) и n-МОП-транзистор M5 (транзистор переноса), пути тока которых подключены последовательно между собой. Ее оставшаяся конфигурация является идентичной оставшейся конфигурации матрицы ячеек запоминающего устройства так, как показано на фиг. 2.

В дальнейшем в этом документе описывается конфигурация считывающего усилителя 12A.

Считывающий усилитель 12A представляет собой тип на основе считывания напряжением считывающего усилителя. Считывающий усилитель 12A содержит: первый инвертор, включающий в себя p-МОП-транзистор M11 и n-МОП-транзистор M12; второй инвертор, включающий в себя p-МОП-транзистор M13 и n-МОП-транзистор M14; n-МОП-транзисторы M15, M16 и M19; и p-МОП-транзисторы M17, M18 и M20.

Первый инвертор (транзисторы M11 и M12) включает в себя первый входной контактный вывод, первый выходной контактный вывод и первый и второй контактные выводы напряжения. Второй инвертор (транзисторы M13 и M14) включает в себя второй входной контактный вывод, второй выходной контактный вывод и третий и четвертый контактные выводы напряжения. Второй входной контактный вывод подключается к первому выходному контактному выводу, и второй выходной контактный вывод подключается к первому входному контактному выводу.

Первый выходной контактный вывод первого инвертора подключается к стоку p-МОП-транзистора M17, и исток p-МОП-транзистора M17 подключается к контактному выводу VDD напряжения питания. Второй выходной контактный вывод второго инвертора подключается к стоку p-МОП-транзистора M18, и исток p-МОП-транзистора M18 подключается к контактному выводу VDD напряжения питания. Первый сигнал SEN1 разрешения считывания из контроллера 18 подается в оба затвора n-МОП-транзисторов M17 и M18.

Первый контактный вывод напряжения первого инвертора (или исток транзистора M12) подключается к стоку n-МОП-транзистора M15. Третий контактный вывод напряжения второго инвертора (или исток транзистора M14) подключается к стоку n-МОП-транзистора M16. Оба истока n-МОП-транзисторов M15 и M16 подключаются к контактному выводу Vss потенциала земли через n-МОП-транзистор M19. Второй сигнал SEN2 разрешения считывания из контроллера 18 подается в затвор n-МОП-транзистора M19.

Затвор n-МОП-транзистора M15 подключается к стоку n-МОП-транзистора M5. Сигнал REN разрешения считывания из контроллера 18 подается в затвор n-МОП-транзистора M5.

Затвор n-МОП-транзистора M16 подключается к схеме 17A формирования опорного напряжения. Схема 17A формирования опорного напряжения прикладывает опорное напряжение VREF к считывающему усилителю 12A. Здесь, опорное напряжение VREF задается равным промежуточному значению между напряжениями соответствующих ячеек, которые инструктируют ячейке запоминающего устройства сохранять "0" и "1". Это опорное напряжение VREF формируется, например, посредством опорной ячейки.

Сток n-МОП-транзистора M5 подключается к контактному выводу VDD напряжения питания через p-МОП-транзистор M20 (нагрузочный транзистор). Напряжение Vload нагрузки прикладывается к затвору p-МОП-транзистора M20.

В дальнейшем в этом документе описывается конфигурация схемы 16 формирования неизменяющегося постоянного тока.

Затвор n-МОП-транзистора M4 подключается к схеме 16 формирования неизменяющегося постоянного тока. Конфигурация схемы 16 формирования неизменяющегося постоянного тока является идентичной конфигурации схемы формирования неизменяющегося постоянного тока так, как показано на фиг. 2.

Далее приводится описание операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно третьему варианту осуществления.

Временная диаграмма операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно третьему варианту осуществления, является идентичной временной диаграмме по фиг. 3.

В типе на основе считывания напряжением считывающего усилителя 12A, ток считывания изменяется в зависимости от данных, сохраненных в выбранной ячейке MC запоминающего устройства, так что изменяется напряжение в соединительном узле между n-МОП-транзистором M5 и p-МОП-транзистором M20. Напряжение в соединительном узле, которое изменяется таким образом, а именно, в зависимости от данных выбранной ячейки MC запоминающего устройства, означает напряжение VDATA ячейки.

В ответ, опорное напряжение VREF, прикладываемое посредством схемы 17A формирования опорного напряжения, сравнивается с напряжением VDATA ячейки. Как результат, уровень защелкивающей схемы, включающей в себя p-МОП-транзисторы M11 и M13 и n-МОП-транзисторы M12 и M14, сохраняется на высоком или низком уровне, в соответствии с результатом сравнения. В завершение, (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме, выводятся из узлов SO и SOb в качестве выходных сигналов OUT и OUTb, соответственно.

В третьем варианте осуществления, аналогично первому варианту осуществления, сигнал REN разрешения считывания формируется посредством сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса, и n-МОП-транзистор M5 включается посредством этого сигнала REN разрешения считывания. Как результат, глобальная битовая линия GBL заряжается заранее. Затем ячейка MC запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца и линии слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Другими словами, глобальная битовая линия GBL предварительно заряжается до того, как ячейка MC запоминающего устройства выбирается через сигнал CSL<n> выбора столбца и линию слова WL<n>, и затем ток считывания подается в выбранную ячейку MC запоминающего устройства. Следовательно, можно сокращать время считывания на время, требуемое для заряда глобальной битовой линии GBL.

В третьем варианте осуществления, как описано выше, после того, как предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, ячейка запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца, и ток считывания подается в выбранную ячейку запоминающего устройства, так что инициируется операция считывания. Соответственно, этот вариант осуществления обеспечивает возможность исключения времени заряда битовой линии, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания. Его оставшаяся конфигурация является идентичной оставшейся конфигурации первого варианта осуществления, как описано выше.

Четвертый вариант осуществления

В четвертом варианте осуществления, запоминающее устройство на основе изменения сопротивления оснащено типом на основе считывания напряжением считывающего усилителя, аналогично третьему варианту осуществления. В четвертом варианте осуществления, приводится описание примера предварительного заряда глобальной битовой линии посредством переключения фиксирующего транзистора M4.

Фиг. 8 является принципиальной схемой конфигурации матрицы 11 ячеек запоминающего устройства, типа на основе считывания напряжением считывающего усилителя 12A, схемы 16 формирования неизменяющегося постоянного тока и схемы 17A формирования опорного напряжения в четвертом варианте осуществления.

Запоминающее устройство на основе изменения сопротивления согласно четвертому варианту осуществления имеет схему, эквивалентную схеме по фиг. 7, из которой исключается транзистор M5 переноса, расположенный между фиксирующим транзистором M4 и нагрузочным транзистором M20, как проиллюстрировано на фиг. 8. Оставшаяся конфигурация запоминающего устройства на основе изменения сопротивления согласно четвертому варианту осуществления, а именно, другие конфигурации матрицы ячеек запоминающего устройства, считывающего усилителя и схемы формирования неизменяющегося постоянного тока являются идентичными конфигурациям третьего варианта осуществления, как проиллюстрировано на фиг. 1 и 7. Следовательно, их описания опускаются.

Далее приводится описание операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно четвертому варианту осуществления.

Временная диаграмма операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно четвертому варианту осуществления, является идентичной временной диаграмме по фиг. 6.

В типе на основе считывания напряжением считывающего усилителя 12A, ток считывания изменяется в зависимости от данных, сохраненных в выбранной ячейке MC запоминающего устройства, так что изменяется напряжение в соединительном узле между n-МОП-транзистором M4 и p-МОП-транзистором M20.

В ответ, опорное напряжение VREF, прикладываемое посредством схемы 17A формирования опорного напряжения, сравнивается с напряжением VDATA ячейки. Как результат, уровень защелкивающей схемы, включающей в себя p-МОП-транзисторы M11 и M13 и n-МОП-транзисторы M12 и M14, сохраняется на высоком или низком уровне, в соответствии с результатом сравнения. В завершение, (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме, выводятся из узлов SO и SOb в качестве выходных сигналов OUT и OUTb, соответственно.

В четвертом варианте осуществления, аналогично второму варианту осуществления, приложение фиксирующего напряжения Vclamp инициируется посредством сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса, и n-МОП-транзистор M4 включается посредством этого фиксирующего напряжения Vclamp. Как результат, глобальная битовая линия GBL заряжается заранее. Затем ячейка MC запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца и линии слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Другими словами, глобальная битовая линия GBL предварительно заряжается до того, как ячейка MC запоминающего устройства выбирается через сигнал CSL<n> выбора столбца и линию слова WL<n>, и затем ток считывания подается в выбранную ячейку MC запоминающего устройства. Следовательно, можно сокращать время считывания на время, требуемое для заряда глобальной битовой линии GBL.

В четвертом варианте осуществления, как описано выше, после того, как предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, ячейка запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца, и ток считывания подается в выбранную ячейку запоминающего устройства, так что инициируется операция считывания. Этот вариант осуществления обеспечивает возможность исключения времени заряда битовой линии, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания. Его оставшаяся конфигурация является идентичной оставшейся конфигурации первого варианта осуществления, как описано выше.

Пятый вариант осуществления

Пятый вариант осуществления предоставляет схемную конфигурацию, идентичную схемной конфигурации четвертого варианта осуществления так, как показано на фиг. 8. В этом варианте осуществления, приводится описание примера предварительного заряда глобальной битовой линии посредством переключения нагрузочного транзистора M20.

Конфигурация запоминающего устройства на основе изменения сопротивления согласно пятому варианту осуществления, а именно, конфигурации матрицы ячеек запоминающего устройства, считывающего усилителя и схемы формирования неизменяющегося постоянного тока являются идентичными конфигурациям четвертого варианта осуществления, как проиллюстрировано на фиг. 1 и 8. Следовательно, их описания опускаются.

Далее приводится описание операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления согласно пятому варианту осуществления, со ссылкой на фиг. 9.

Фиг. 9 является временной диаграммой операции считывания, выполняемой посредством запоминающего устройства на основе изменения сопротивления.

Состояние ожидания, которое предполагается до того, как инициирована операция считывания, является идентичным состоянию, как проиллюстрировано на фиг. 3.

В вышеуказанном состоянии, внешний источник вводит команду активации и сигнал адреса в контроллер 18 запоминающего устройства на основе изменения сопротивления. В ответ, контроллер 18 формирует сигнал активации банка для активации банка на основе сигнала адреса и активирует банк, который должен использоваться, посредством использования сигнала активации банка.

В этом случае, сигнал адреса или сигнал активации банка инициирует низкий уровень напряжения Vload нагрузки, за счет этого включая p-МОП-транзистор M20. Как результат, электрический ток вытекает из контактного вывода VDD напряжения питания в глобальную битовую линию GBL через p-МОП-транзистор M20 и n-МОП-транзистор M4, так что заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL. Следует отметить, что сигнал активации банка используется в вышеприведенном описании, но другой внутренний сигнал, сформированный из сигнала адреса, может использоваться вместо сигнала активации банка.

В свою очередь, в матрице 11 ячеек запоминающего устройства, локальная битовая линия LBL<n> и локальная линия LSL<n> истока выбираются через сигнал CSL<n> выбора столбца. Помимо этого, линия слова WL<n> возбуждается, так что выбирается ячейка MC запоминающего устройства, которая должна считываться. В частности, посредством задания уровня сигнала CSL<n> выбора столбца как высокого уровня, оба n-МОП-транзистора M1<n> и M2<n> включаются. Как результат, локальная битовая линия LBL<n> подключается к глобальной битовой линии GBL, и локальная линия LSL<n> истока подключается к глобальной линии GSL истока. Кроме того, посредством задания уровня линии слова WL<n> как высокого уровня, транзистор ST выбора включается. Как результат, выбирается ячейка MC запоминающего устройства, которая должна считываться. В этом случае, n-МОП-транзистор M3 находится во включенном состоянии через сигнал SINK в ходе операции считывания. Посредством вышеуказанной обработки, ток считывания подается из считывающего усилителя 12A в выбранную ячейку MC запоминающего устройства.

В типе на основе считывания напряжением считывающего усилителя 12A, ток считывания изменяется в зависимости от данных, сохраненных в выбранной ячейке MC запоминающего устройства, так что изменяется напряжение в соединительном узле между n-МОП-транзистором M4 и p-МОП-транзистором M20.

В ответ, опорное напряжение VREF, прикладываемое посредством схемы 17A формирования опорного напряжения, сравнивается с напряжением VDATA ячейки. Как результат, уровень защелкивающей схемы, включающей в себя p-МОП-транзисторы M11 и M13 и n-МОП-транзисторы M12 и M14, сохраняется на высоком или низком уровне, в соответствии с результатом сравнения. В завершение, (данные) с высоким уровнем или низким уровнем, которые сохраняются в защелкивающей схеме, выводятся из узлов SO и SOb в качестве выходных сигналов OUT и OUTb, соответственно.

В пятом варианте осуществления, напряжение Vload нагрузки формируется посредством сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса, и p-МОП-транзистор M20 включается посредством этого напряжения Vload нагрузки. Как результат, глобальная битовая линия GBL заряжается заранее. Затем ячейка MC запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца и линии слова WL<n>, и ток считывания подается в выбранную ячейку MC запоминающего устройства. Другими словами, глобальная битовая линия GBL предварительно заряжается до того, как ячейка MC запоминающего устройства выбирается через сигнал CSL<n> выбора столбца и линию слова WL<n>, и затем ток считывания подается в выбранную ячейку MC запоминающего устройства. Следовательно, можно сокращать время считывания на время, требуемое для заряда глобальной битовой линии GBL.

В пятом варианте осуществления, как описано выше, после того, как предварительно заряжается маршрут считывания, включающий в себя глобальную битовую линию GBL, ячейка запоминающего устройства выбирается посредством сигнала CSL<n> выбора столбца, и ток считывания подается в выбранную ячейку запоминающего устройства, так что инициируется операция считывания. Соответственно, этот вариант осуществления обеспечивает возможность исключения времени заряда битовой линии, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания. Его оставшаяся конфигурация является идентичной оставшейся конфигурации первого варианта осуществления, как описано выше.

Преимущество

Вышеописанные варианты осуществления являются применимыми к полупроводниковым запоминающим устройствам, в которые данные записываются с помощью тока, включающим в себя MRAM, имеющие элементы на магниторезистивном эффекте, ReRAM, имеющие переменные резистивные элементы, и PRAM, имеющие элементы с фазовым переходом.

Например, MRAM включает в себя магнитный резистивный элемент, называемый элементом с магнитным туннельным переходом (MTJ), в качестве запоминающего элемента. Такой MTJ-элемент включает в себя фиксированный слой (или опорный слой), слой для записи (или свободный слой) и изолирующий слой, который размещается посередине между ними. В фиксированном слое, направление намагничивания является фиксированным посредством антиферромагнитного слоя, а в слое для записи, направление намагничивания может инвертироваться свободно. MTJ-элемент использует изменение сопротивления в слое для записи в направлении намагничивания относительно сопротивления фиксированного слоя, что называется магниторезистивным эффектом. Таким образом, MTJ-элемент различает между данными в "1" и данными в "0" посредством использования относительной разницы между соответствующими сопротивлениями в направлении намагничивания.

Механизм для записи данных в MRAM, таком как тип на основе спинового введения MRAM, работает следующим образом. Когда данные "1" записываются в MRAM, ток подается в него в направлении от фиксированного слоя к слою для записи MTJ-элемента. Между тем, когда данные "0" записываются в MRAM, ток подается в него в направлении от слоя для записи к фиксированному слою MTJ-элемента.

В вариантах осуществления, как описано выше, маршрут считывания (в основном, глобальная битовая линия) предварительно заряжается посредством сигнала адреса или внутреннего сигнала, сформированного из сигнала адреса до того, как активируется сигнал выбора столбца или линия слова. После этого выполняется инициирование операции считывания. Соответственно, эти варианты осуществления обеспечивают возможность исключения времени заряда маршрута считывания, которое по существу рассматривается в качестве необязательного времени и влияет на время считывания, из фактического времени считывания. Следовательно, можно сокращать время считывания, в течение которого активируется матрица ячеек запоминающего устройства, и данные считываются из нее.

Кроме того, в соответствии с сигналом адреса или внутренним сигналом, сформированным из сигнала адреса, формируется сигнал для инициирования заряда маршрута считывания. Другими словами, сигнал адреса или внутренний сигнал, сформированный из сигнала адреса, инициирует заряд маршрута считывания. Соответственно, можно эффективно задавать время инициирования заряда маршрута считывания.

Кроме того, в вышеописанных вариантах осуществления, битовые линии предварительно заряжаются с помощью тока, поданного из считывающего усилителя, как описано выше. Следовательно, эти варианты осуществления исключают необходимость установки дополнительной схемы предварительного заряда, а также не допускают увеличения площади.

Общая конфигурация запоминающего устройства на основе изменения сопротивления согласно каждому варианту осуществления, а именно, конфигурации матрицы ячеек запоминающего устройства, ячеек запоминающего устройства, считывающего усилителя, формирователей/приемников сигналов управления, схемы формирования неизменяющегося постоянного тока, схема формирования опорного тока и т.п., не ограничены конфигурациями вышеприведенных примеров. Например, может использоваться структура, раскрытая посредством US 7,649,792 или US 2012/0286339. Содержимое этих подробных описаний полностью содержится в данном документе по ссылке.

Хотя описаны конкретные варианты осуществления, эти варианты осуществления представлены только в качестве примера и не предназначены для того, чтобы ограничивать объем изобретения. Фактически, новые способы и системы, описанные в данном документе, могут быть осуществлены во множестве других форм. Помимо этого, различные пропуски, замены и изменения в форме способов и систем, описанных в данном документе, могут быть осуществлены без отступления от сущности изобретения. Прилагаемая формула изобретения и ее эквиваленты предназначены для того, чтобы охватывать такие формы и модификации как попадающие в пределы объема и сущности изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2681344C1 |

| МАГНИТНАЯ ПАМЯТЬ И СПОСОБ УПРАВЛЕНИЯ ЕЮ | 2014 |

|

RU2628221C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИЗМЕНЕНИЕМ СОПРОТИВЛЕНИЯ | 2016 |

|

RU2702271C2 |

| УСТРОЙСТВО ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ ДЛЯ ДОСТИЖЕНИЯ ВЫСОКОЙ ПРОИЗВОДИТЕЛЬНОСТИ И СПОСОБ РАСПОЛОЖЕНИЯ В НЕМ СИГНАЛЬНЫХ ШИН | 1995 |

|

RU2170955C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2016 |

|

RU2669872C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ЕГО УПРАВЛЕНИЯ | 1996 |

|

RU2190885C2 |

| МАГНИТОРЕЗИСТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2653131C2 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

Группа изобретений относится к запоминающим устройствам. Технический результат – сокращение времени записи/считывания. Для этого согласно одному варианту осуществления запоминающее устройство на основе изменения сопротивления включает в себя ячейку запоминающего устройства, считывающий усилитель и глобальную битовую линию. Ячейка запоминающего устройства располагается в местоположении, в котором локальная битовая линия и линия слова пересекают друг друга. Ячейка запоминающего устройства подключается как к локальной битовой линии, так и к линии слова. Считывающий усилитель считывает данные, сохраненные в ячейке запоминающего устройства, посредством подачи тока считывания в ячейку запоминающего устройства. Глобальная битовая линия подключается между локальной битовой линией и считывающим усилителем. Глобальная битовая линия подает ток считывания, поданный посредством считывающего усилителя, в локальную битовую линию. Считывающий усилитель заряжает глобальную битовую линию до того, как локальная битовая линия и глобальная битовая линия подключаются между собой. 3 н. и 17 з.п. ф-лы, 9 ил.

1. Запоминающее устройство на основе изменения сопротивления, содержащее:

- первую ячейку запоминающего устройства, включающую в себя элемент с изменяемым сопротивлением;

- линию слова, подключенную к первой ячейке запоминающего устройства, причем линия слова возбуждается на основе сигнала адреса;

- первую битовую линию, подключенную к первой ячейке запоминающего устройства и пересекающую линию слова, причем первая битовая линия выбирается на основе сигнала адреса;

- первый инвертор, включающий в себя первый входной контактный вывод, первый выходной контактный вывод и первый и второй контактные выводы напряжения;

- второй инвертор, включающий в себя второй входной контактный вывод, второй выходной контактный вывод и третий и четвертый контактные выводы напряжения, причем второй входной контактный вывод подключается к первому выходному контактному выводу, второй выходной контактный вывод подключается к первому входному контактному выводу;

- первый МОП-транзистор, подключенный к первому выходному контактному выводу;

- второй МОП-транзистор, подключенный ко второму выходному контактному выводу;

- третий МОП-транзистор, подключенный к первому контактному выводу напряжения;

- четвертый МОП-транзистор, подключенный к третьему контактному выводу напряжения;

- пятый МОП-транзистор, имеющий путь тока, один конец которого подключается к первому контактному выводу напряжения, причем пятый МОП-транзистор имеет затвор, на который подается первый сигнал;

- вторую битовую линию, подключенную к другому концу упомянутого пути тока; и

- шестой МОП-транзистор, подключенный между второй битовой линией и первой битовой линией, причем шестой МОП-транзистор имеет затвор, на который подается второй сигнал,

- при этом, до того, как шестой МОП-транзистор включается посредством второго сигнала, пятый МОП-транзистор включается посредством первого сигнала.

2. Запоминающее устройство на основе изменения сопротивления по п. 1,

- в котором первый контактный вывод напряжения подает ток во вторую битовую линию, тем самым заряжая вторую битовую линию.

3. Запоминающее устройство на основе изменения сопротивления по п. 1,

- в котором первый сигнал включает в себя сигнал разрешения считывания, который разрешает операцию считывания, и второй сигнал включает в себя сигнал выбора столбца, который выбирает первую битовую линию.

4. Запоминающее устройство на основе изменения сопротивления по п. 1,

- в котором пятый МОП-транзистор включает в себя транзистор, который ограничивает ток считывания, протекающий через первую ячейку запоминающего устройства, и шестой МОП-транзистор включает в себя транзистор выбора столбца, который выбирает первую битовую линию.

5. Запоминающее устройство на основе изменения сопротивления по п. 1,

- в котором пятый МОП-транзистор включается через формирование первого сигнала посредством использования одного из сигнала адреса и сигнала, сформированного из сигнала адреса.

6. Запоминающее устройство на основе изменения сопротивления по п. 1, дополнительно содержащее седьмой МОП-транзистор, подключенный между второй битовой линией и другим концом упомянутого пути тока пятого МОП-транзистора, причем к затвору седьмого МОП-транзистора прикладывается неизменяющееся постоянное напряжение.

7. Запоминающее устройство на основе изменения сопротивления по п. 1, дополнительно содержащее схему, которая подает опорный ток во второй выходной контактный вывод,

- при этом данные, сохраненные в первой ячейке запоминающего устройства, сохраняются в первом и втором инверторах на основе разности между опорным током и током считывания, протекающим через первый выходной контактный вывод в ходе операции считывания.

8. Запоминающее устройство на основе изменения сопротивления по п. 1, дополнительно содержащее матрицу ячеек запоминающего устройства, которая включает в себя множество ячеек запоминающего устройства, размещаемых в матричной форме, причем каждая из ячеек запоминающего устройства имеет элемент с изменяемым сопротивлением, причем ячейки запоминающего устройства в матрице ячеек запоминающего устройства включают в себя первую ячейку запоминающего устройства.

9. Запоминающее устройство на основе изменения сопротивления по п. 1,

- в котором элемент с изменяемым сопротивлением включает в себя элемент с магнитным туннельным переходом (MTJ), сопротивление которого изменяется посредством по меньшей мере одного из подачи тока в него и приложения напряжения к нему.

10. Запоминающее устройство на основе изменения сопротивления, содержащее:

- первую ячейку запоминающего устройства, включающую в себя элемент с изменяемым сопротивлением;

- линию слова, подключенную к первой ячейке запоминающего устройства, причем линия слова возбуждается на основе сигнала адреса;

- первую битовую линию, подключенную к первой ячейке запоминающего устройства и пересекающую линию слова, причем первая битовая линия выбирается на основе сигнала адреса;

- первый инвертор, имеющий первый входной контактный вывод, первый выходной контактный вывод и первый и второй контактные выводы напряжения;

- второй инвертор, имеющий второй входной контактный вывод, второй выходной контактный вывод и третий и четвертый контактные выводы напряжения, причем второй входной контактный вывод подключается к первому выходному контактному выводу, второй выходной контактный вывод подключается к первому входному контактному выводу;

- первый МОП-транзистор, подключенный к первому выходному контактному выводу;

- второй МОП-транзистор, подключенный ко второму выходному контактному выводу;

- третий МОП-транзистор, подключенный к первому контактному выводу напряжения;

- четвертый МОП-транзистор, подключенный к третьему контактному выводу напряжения;

- пятый МОП-транзистор, имеющий путь тока, один конец которого подключается к затвору третьего МОП-транзистора, причем пятый МОП-транзистор имеет затвор, на который подается первый сигнал;

- вторую битовую линию, подключенную к другому концу упомянутого пути тока пятого МОП-транзистора; и

- шестой МОП-транзистор, подключенный между второй битовой линией и первой битовой линией, причем шестой МОП-транзистор имеет затвор, на который подается второй сигнал,

- при этом до того, как шестой МОП-транзистор включается посредством второго сигнала, пятый МОП-транзистор включается посредством первого сигнала.

11. Запоминающее устройство на основе изменения сопротивления по п. 10,

- в котором ток подается с упомянутого одного конца пути тока пятого МОП-транзистора во вторую битовую линию, тем самым заряжая вторую битовую линию.

12. Запоминающее устройство на основе изменения сопротивления по п. 10,

- в котором первый сигнал включает в себя сигнал разрешения считывания, который разрешает операцию считывания, и второй сигнал включает в себя сигнал выбора столбца, который выбирает первую битовую линию.

13. Запоминающее устройство на основе изменения сопротивления по п. 10,

- в котором пятый МОП-транзистор включает в себя транзистор, который ограничивает ток считывания, протекающий через первую ячейку запоминающего устройства, и шестой МОП-транзистор включает в себя транзистор выбора столбца, который выбирает первую битовую линию.

14. Запоминающее устройство на основе изменения сопротивления по п. 10,

- в котором пятый МОП-транзистор включается через формирование первого сигнала посредством использования одного из сигнала адреса и сигнала, сформированного из сигнала адреса.

15. Запоминающее устройство на основе изменения сопротивления по п. 10, дополнительно содержащее седьмой МОП-транзистор, подключенный к упомянутому одному концу пути тока пятого МОП-транзистора,

- при этом, до того, как шестой МОП-транзистор включается, включается седьмой МОП-транзистор.

16. Запоминающее устройство на основе изменения сопротивления по п. 10, дополнительно содержащее седьмой МОП-транзистор, подключенный между второй битовой линией и другим концом упомянутого пути тока пятого МОП-транзистора, причем к затвору седьмого МОП-транзистора прикладывается неизменяющееся постоянное напряжение.

17. Запоминающее устройство на основе изменения сопротивления по п. 10, дополнительно содержащее схему, которая прикладывает опорное напряжение к затвору четвертого МОП-транзистора,

- при этом данные, сохраненные в первой ячейке запоминающего устройства, сохраняются в первом и втором инверторах на основе разности между соответствующими токами, протекающими через первый выходной контактный вывод и второй выходной контактный вывод в ходе операции считывания.

18. Запоминающее устройство на основе изменения сопротивления по п. 10, дополнительно содержащее матрицу ячеек запоминающего устройства, которая включает в себя множество ячеек запоминающего устройства, размещаемых в матричной форме, причем каждая из ячеек запоминающего устройства имеет элемент с изменяемым сопротивлением, причем ячейки запоминающего устройства в матрице ячеек запоминающего устройства включают в себя первую ячейку запоминающего устройства.

19. Запоминающее устройство на основе изменения сопротивления, содержащее:

- ячейку запоминающего устройства, расположенную в местоположении, в котором локальная битовая линия и линия слова пересекают друг друга, причем ячейка запоминающего устройства имеет элемент с изменяемым сопротивлением, при этом ячейка запоминающего устройства подключается как к локальной битовой линии, так и к линии слова;

- считывающий усилитель, который считывает данные, сохраненные в ячейке запоминающего устройства, посредством подачи тока считывания в ячейку запоминающего устройства; и

- глобальную битовую линию, подключенную между локальной битовой линией и считывающим усилителем, причем глобальная битовая линия подает ток считывания, подаваемый посредством считывающего усилителя, в локальную битовую линию,

- при этом считывающий усилитель заряжает глобальную битовую линию до того, как локальная битовая линия и глобальная битовая линия подключаются между собой.

20. Запоминающее устройство на основе изменения сопротивления по п. 19,

- в котором считывающий усилитель инициирует заряд глобальной битовой линии в ответ на одну из команды активации, сигнала адреса, который обозначает локальную битовую линию и линию слова, либо область, содержащую локальную битовую линию и линию слова, и сигнала, сформированного из сигнала адреса.

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ЕГО УПРАВЛЕНИЯ | 1996 |

|

RU2190885C2 |

Авторы

Даты

2017-05-26—Публикация

2014-03-11—Подача