Область техники, к которой относится изобретение

Настоящее раскрытие относится к схеме смещения памяти с узлами пересечения.

Уровень техники

Запоминающее устройство на фазовых переходах представляет собой устройство памяти, в котором обычно используется халькогенидный материал для элементов памяти. Элемент памяти представляет собой модуль, в котором фактически содержится информация. Во время работы память на фазовых переходах хранит информацию в элементе памяти путем изменения фазы элемента памяти между аморфной и кристаллической фазами. Халькогенидный материал может представлять либо кристаллическую, или аморфную фазу, проявляя низкую или высокую электропроводность. В общем, аморфная фаза имеет низкую электропроводность (высокий импеданс) и ассоциирована с состоянием сброса (логический ноль), и кристаллическая фаза имеет высокую электропроводность (низкий импеданс) и ассоциируется с установленным состоянием (логическая единица). Элемент памяти может быть включен в ячейку памяти, которая также включает в себя селектор, то есть устройство выбора, соединенное с элементом памяти. Устройства выбора выполнены с возможностью способствовать комбинированию множества элементов памяти в массив.

Элементы памяти на фазовых переходах могут быть размещены в виде массива памяти с узлами пересечения, включающими в себя адресные линии ряда и адресные линии столбца, размещенные в виде сетки. Адресные линии ряда и адресные линии столбца, называемые линиями слова (WL) и линиями битов (BL), соответственно, пересекаются при формировании сетки, и каждая ячейка памяти соединена между WL и BL, где WL и BL пересекаются (то есть в узлах пересечения). Следует отметить, что ряды и столбцы представляют собой термины, используемые для удобства, для обеспечения качественного описания размещения WL и BL в памяти с узлами пересечения.

Ячейка памяти (например, целевая ячейка памяти) может быть выбрана путем приложения напряжений смещения к WL и BL, которые пересекаются в целевой ячейке памяти, то есть напряжения выбора WL, Vselwl, и напряжения выбора BL, Vselbl, соответственно. Получаемое в результате дифференциальное напряжение смещения целевой ячейки (Vt_sel = Vselbl - Vselwl) на элементе памяти конфигурируют так, чтобы оно было больше, чем пороговое напряжение выбора (Vt) для элемента памяти. Желательно, чтобы VT_SEL было достаточно велико, чтобы надежно выбирать целевую ячейку, но не таким большим, чтобы непреднамеренно были выбраны другие ячейки, в частности нецелевые ячейки, включенные в выбранную WL или выбранную BL.

Одна технология, выполненная так, чтобы VT_SEL было достаточно большим, при исключении выбора нецелевых ячеек, состоит в приложении напряжения компенсации смещения (“смещения C-ячейки”) к невыбранным WL и/или невыбранным BL. Смещение C-ячейки конфигурируют так, чтобы оно уменьшало или поддерживало напряжение смещения на нецелевых ячейках ниже Vt, когда повышенное VT_SEL прикладывают к целевой ячейке. Повышенное VT_SEL подбирают так, чтобы увеличить вероятность того, что будет выбрана целевая ячейка. Постоянное поддержание смещения C-ячейки (то есть независимо от того, был ли инициирован доступ к памяти), увеличивает ток утечки в массиве с узлами пересечения и увеличивает ток к режиме ожидания и потребление энергии в режиме ожидания.

Другая технология, которая используется для обеспечения достаточно высокого VT_SEL при исключении выбора нецелевых ячеек, состоит в подаче смещения к C-ячейке при каждой операции выбора ячейки памяти. Эта технология выполнена так, чтобы исключить увеличение тока утечки и/или тока в режиме ожидания, но приводит к относительно высоким затратам энергии из-за заряда и разряда, ассоциированных с установлением и отключением смещения C-ячейки при каждой операции с ячейкой памяти. Относительно большие структуры шин могут потребоваться для обеспечения быстрого заряда для смещения C-ячейки, и/или относительно длительное время задержки может возникать для обеспечения достаточного времени, чтобы все ячейки памяти достигли смещения C-ячейки перед выбором целевой ячейки.

Краткое описание чертежей

Свойства и преимущества заявленного предмета изобретения будут понятны из следующего подробного описания вариантов осуществления, последовательно изложенных здесь, и это описание следует рассматривать со ссылкой на приложенные чертежи, на которых:

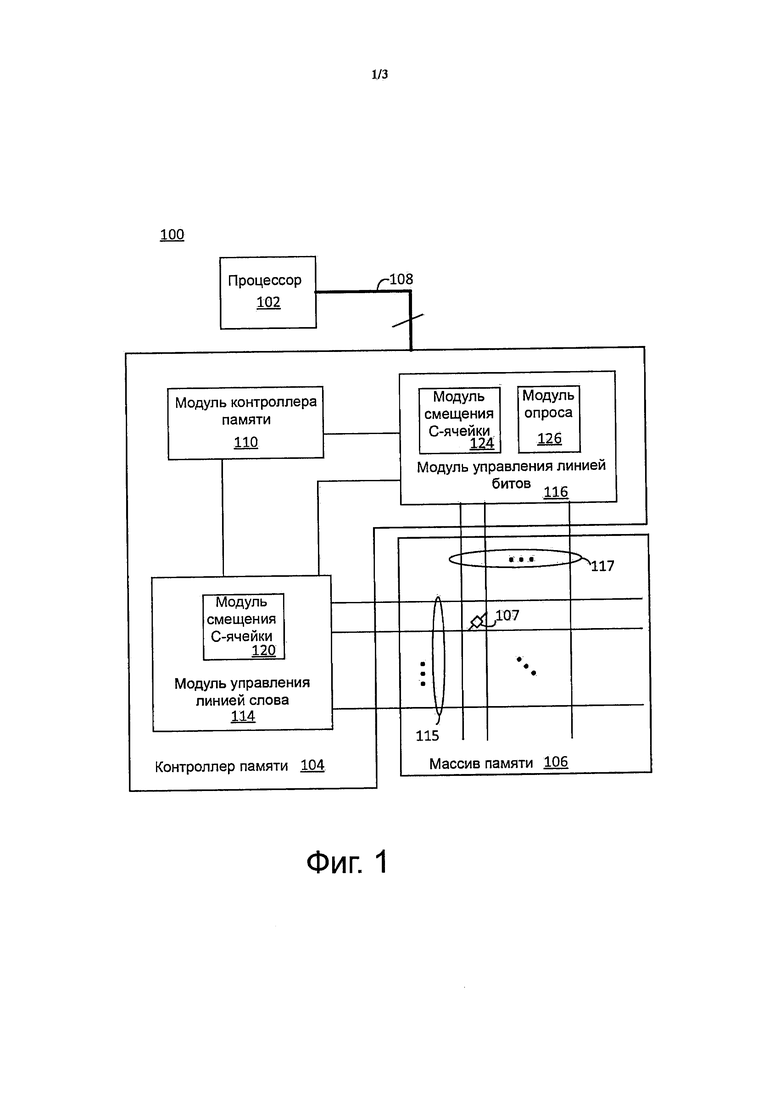

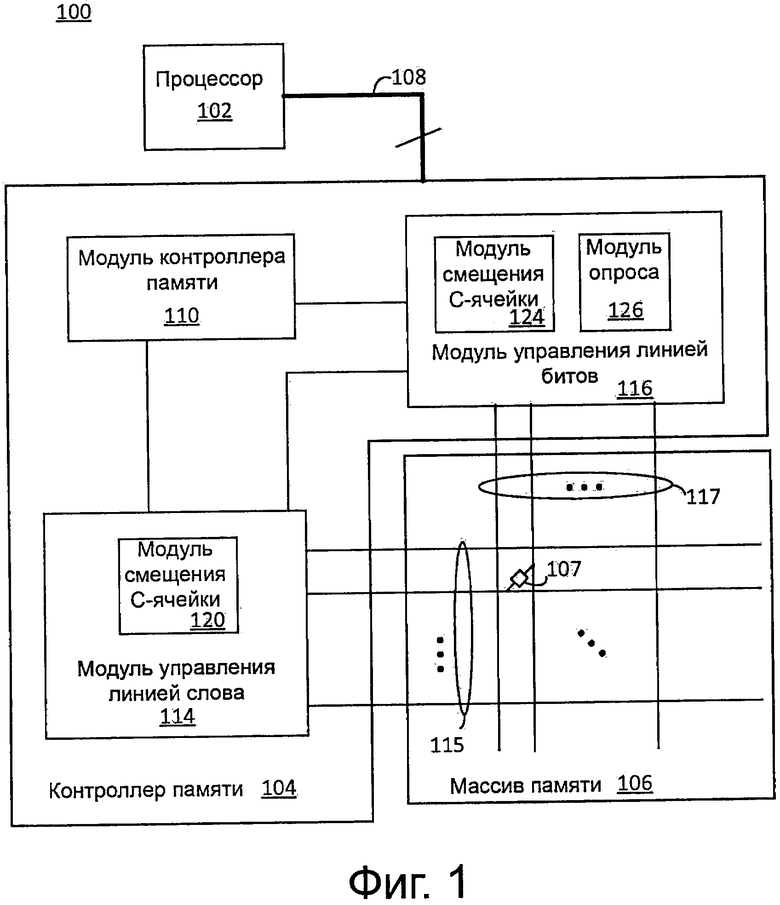

на фиг. 1 показана блок-схема системы, в соответствии с несколькими вариантами осуществления настоящего раскрытия;

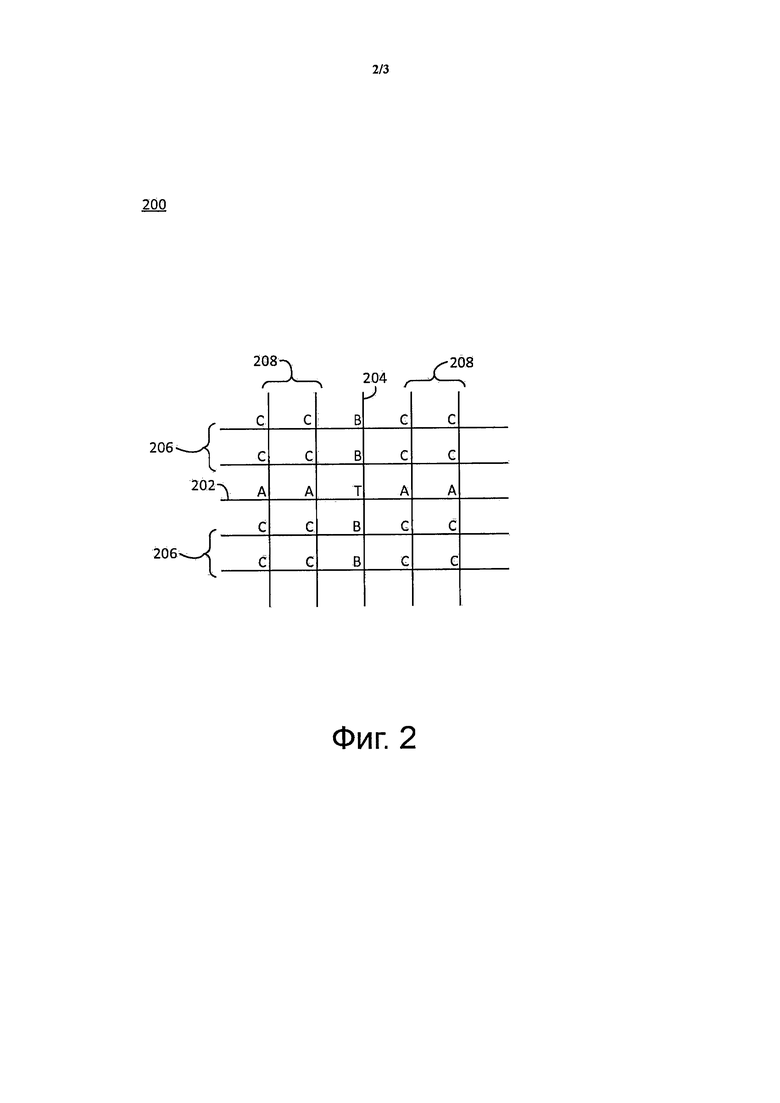

на фиг. 2, в качестве примера, показана часть системы памяти с узлами пересечения, включающей в себя целевую ячейку, ячейки А, ячейки B и ячейки C, в соответствии с одним вариантом осуществления настоящего раскрытия;

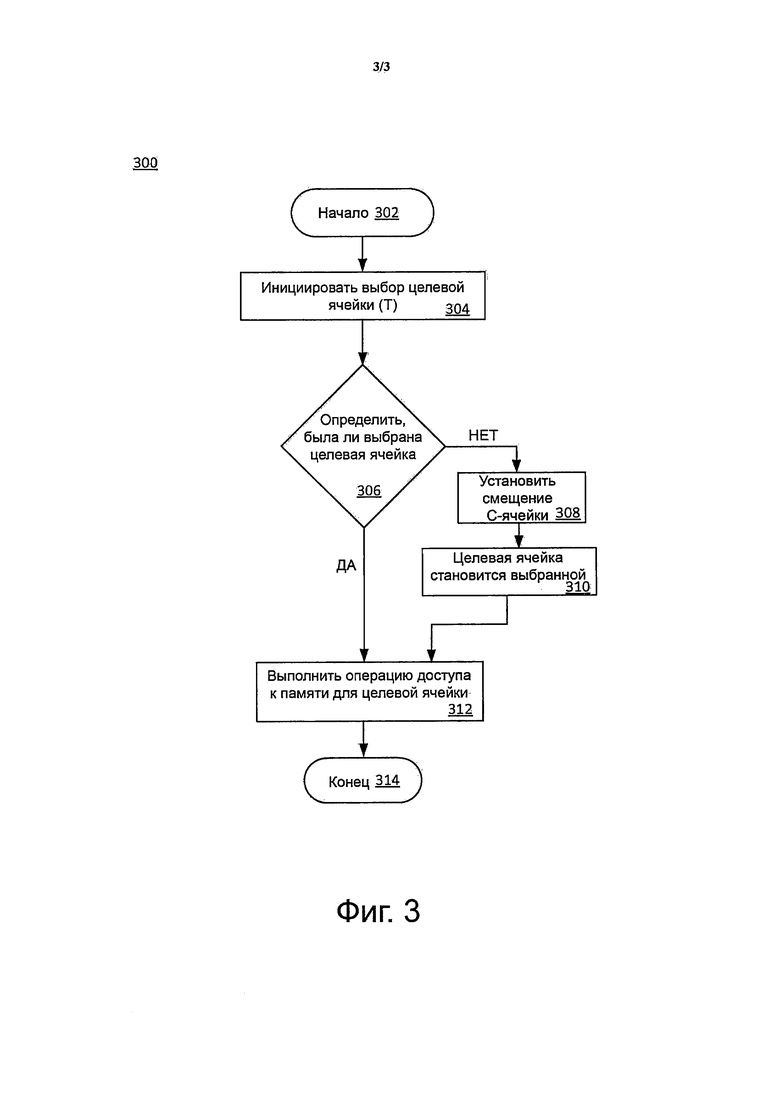

на фиг. 3 иллюстрируется блок-схема последовательности операций для избирательного смещения C-ячейки в соответствии с различными вариантами осуществления настоящего раскрытия.

Хотя следующее подробное описание изобретения будет представлено со ссылкой на иллюстративные варианты осуществления, множество альтернатив, модификаций и их вариантов будут понятными для специалиста в данной области техники.

Подробное описание изобретения

В общем, в данном раскрытии описаны система и способ, выполненные так, чтобы расширить окно операций массива памяти с узлами пересечения, при минимизации влияния на мощность, энергию, размеры кристалла и/или задержку. Система и способ выполнены с попыткой выбора целевой ячейки путем приложения номинального напряжения VT_SEL_nominal смещения к целевой ячейке, без приложения смещения к C-ячейке, для детектирования, была ли выбрана целевая ячейка. Если целевая ячейка не была при этом выбрана, может быть приложено смещение C-ячейки, и напряжение смещения, приложенное к целевой ячейке, может быть увеличено на величину, соответствующую смещению C-ячейки. Смещение C-ячейки устанавливают так, чтобы увеличить окно операций для целевой ячейки, когда пороговое напряжение выбора Vt больше, чем VT_SEL_nominal. Таким образом, смещение C-ячейки можно применять "по требованию", исключая, таким образом, увеличение потребления энергии в режиме ожидания, ассоциированное с непрерывно приложенным смещением C-ячейки, и исключая относительно высокие затраты энергии, ассоциированные с приложением смещения C-ячейки для каждой операции выбора ячейки памяти.

Пороговое значение выбора для ячейки памяти в состоянии сброса выше, чем пороговое напряжение выбора для ячейки памяти в установленном состоянии. Смещение C-ячейки может обычно применяться при операциях записи, поскольку операции считывания выполняют для выбора ячеек памяти в установленном состоянии и для исключения выбора ячеек в состоянии сброса. Другими словами, в общем, можно использовать более низкое значение VT_SEL для операций считывания, чем используется для операций записи.

На фиг. 1 иллюстрируется блок-схема системы 100 в соответствии с несколькими вариантами осуществления настоящего раскрытия. Система 100 включает в себя процессор 102, контроллер 104 памяти и массив 106 памяти. Процессор 102 соединен с контроллером памяти 104 по шине 108. Процессор 102 может предоставлять запросы считывания и/или записи, включая в себя адрес (адреса) памяти, и/или ассоциированные данные в контроллер 104 памяти и может принимать считанные данные из контроллера 104 памяти. Следует отметить, что система 100 представлена в упрощенном виде для простоты иллюстрации и описания.

Массив 106 памяти соответствует по меньшей мере части памяти с узлами пересечения на фазовых переходах и включает в себя множество линий 115 слова, множество линий 117 битов и множество ячеек памяти, например ячеек памяти 107. Каждая ячейка памяти соединена между линией слова (“WL”) и линией битов (“BL”) в узле пересечения WL и BL. Каждая ячейка памяти включает в себя элемент памяти, выполненный с возможностью сохранения информации, и может включать в себя устройство выбора ячейки памяти (то есть селектор), соединенный с элементом памяти. Устройства могут включать в себя аморфно-полупроводниковые пороговые переключатели, диоды, транзисторы с биполярными переходами, полевые транзисторы и т.д. Массив 106 памяти выполнен с возможностью сохранения двоичных данных, и в нем можно выполнять запись (то есть программировать) или считывать из него данные.

Контроллер 104 памяти включает в себя модуль 110 контроллера памяти, модуль WL управления 114 и модуль 116 управления BL. Модуль 110 контроллера памяти выполнен с возможностью выполнения операций, ассоциированных с контроллером 104 памяти. Например, модуль 110 контроллера памяти может администрировать обменом данными с процессором 102. Модуль 110 контроллера памяти может быть выполнен с возможностью идентификации одной или больше целевых WL, ассоциированных с каждым принятым адресом памяти. Модуль 110 контроллера памяти может быть выполнен с возможностью администрирования работой модуля 114 управления WL и модуля 116 управления BL на основе по меньшей мере частично идентифицированных целевых WL.

Модуль 114 управления WL может включать в себя модуль 120 смещения С-ячейки. Модуль 114 управления WL выполнен с возможностью приема целевого адреса (адресов) WL из модуля 110 контроллера памяти и выбора одной или больше WL для операций считывания и/или записи. Модуль 114 управления WL может быть выполнен с возможностью выбора целевой WL путем подключения Vselwl (то есть напряжения смещения выбора WL) к целевой WL и может быть выполнен с возможностью отмены выбора WL путем соединения напряжения смещения не выбора WL Vdeswl к WL. Модуль 114 управления WL может быть соединен с множеством WL 115, включенных в массив 106 памяти. Каждая WL может быть соединена с множеством ячеек памяти, соответствующих количеству BL 117.

Модуль 116 управления BL может включать в себя модуль 124 смещения C-ячейки и/или модуль 126 опроса. Модуль 116 управления BL выполнен с возможностью выбора одной или больше BL для операций считывания и/или записи. Модуль 116 управления BL может быть выполнен с возможностью выбора целевой BL путем подключения Vselbl (то есть напряжения смещения выбора BL) к целевой BL и может быть выполнен с возможностью отмены выбора BL путем подключения напряжения смещения не выбора BL Vdesbl к BL. WL и BL, которые не были выбраны, могут быть соединены с напряжениями смещения не выбора, то есть Vdeswl и Vdesbl, соответственно. Номинально, Vdeswl и Vdesbl равны нулю.

На фиг. 2 иллюстрируется примерный участок массива 200 памяти с узлами пересечения, включающими в себя целевую ячейку (то есть ячейку T), ячейки A, ячейки B и ячейки C, в соответствии с одним вариантом осуществления настоящего раскрытия. Например, часть массива 200 памяти с узлами пересечения может соответствовать массиву 106 памяти, и ячейка T может соответствовать ячейке 107 на фиг. 1. Пример 200 включает в себя выбранную WF 202, выбранную BF 204, множество невыбранных WF 206 и множество невыбранных BF 208. Пример 200 включает в себя одну целевую ячейку T памяти с узлами пересечения, множество A ячеек, которые включены в выбранную WF 202 и множество B-ячеек, которые включены в выбранную BF 204. Пример 200 дополнительно включает в себя множество C-ячеек (узлов пересечения невыбранных WF 206 и невыбранных BF 208).

Напряжение смещения на каждой из A-ячеек составляет Va = Vdesbl - Vselwl. Напряжение смещения на каждой из B-ячеек составляет Vb = Vselbl - Vdeswl. Напряжение смещения на каждой из C-ячеек c = Vdeswl - Vdesbl. Номинально, Vdeswl и Vdesbl равны нулю и Vselwl, и Vselbl установлены так, чтобы выбрать целевую ячейку и при этом не выбрать A-ячейку и/или B-ячейку. Смещение C-ячейки соответствует регулировке Vdeswl и/или Vdesbl, так, чтобы обеспечивалась возможность увеличения VT_SEL (VT_SEL = Vselbl - Vselwl), при поддержании Va и/или Vb на уровне их номинальных значений (которые меньше, чем Vt). Vt представляет собой пороговое напряжение выбора целевой ячейки. Другими словами, VT_SEL может быть увеличено при увеличении Vselbl и/или уменьшении Vselwl, но увеличение Vselbl, без изменения Vdeswl может привести к увеличению Vb, и уменьшение Vselwl, без изменения Vdesbl, может привести к увеличению Va. Смещение C-ячейки используется для регулировки Vdeswl и/или Vdesbl, для поддержания значений Va и/или Vb ниже Vt, когда увеличивается VT_SEL.

Разность между VT_SEL и максимальными значениями Va, Vb и Vc соответствует окну операции. Смещение C-ячейки может, таким образом, использоваться для увеличения окна операции, обеспечивая возможность увеличения VT_SEL, при поддержании Va и Vb на уровне или рядом с их номинальными значениями. Другими словами, поскольку Va, Vb и Vc установлены так, чтобы они были меньше Vt для правильной операции (то есть выбора только целевой ячейки (ячеек)), обеспечение возможности увеличения VT_SEL при поддержании Va, и Vb на уровне или рядом с их номинальными значениями увеличивает окно операции.

Модуль 114 управления WL и модуль 116 управления BL, выполнены с возможностью идентификации целевой ячейки, например, ячейки T, для операции доступа к памяти, например, в ответ на команду из процессора 102 и/или модуля 110 контроллера памяти. Модуль 114 управления WL и модуль 116 управления BL, выполненные с возможностью выбора целевой ячейки T путем приложения Vselwl и Vselbl к выбранной WL, например, WL 202, и выбранной BL, например, BL 204, соответственно, прикладывая, таким образом, VT_SEL к ячейке T. Если VT_SEL больше, чем или равно напряжению порога выбора целевой ячейки Vt, тогда может быть выбрана ячейка T.

Модуль 126 опроса выполнен с возможностью определения, выбрана или нет целевая ячейка, например, ячейка T. Когда ячейка памяти выбрана, ячейка памяти переходит из состояния ВЫКЛЮЧЕНО в состояние ВКЛЮЧЕНО, и состояние импеданса ячейки переходит из состояния относительно высокого импеданса (например, больше чем приблизительно 10 мегаом (МΩ) в состояние относительно низкого импеданса (например, меньше чем приблизительно 10 килоом (kΩ). Когда состояние импеданса ячейки памяти относительно низкое, ячейка памяти "выбрана". Таким образом, модуль 226 опроса может быть выполнен с возможностью определения, была ли выбрана целевая ячейка, например ячейка T на основе по меньшей мере частично состояния импеданса ячейки памяти. Например, модуль 226 опроса может быть выполнен с возможностью определения тока, протекающего через ячейку T (например, непосредственно тока или падения напряжения на резисторе опроса). Таким образом, модуль 226 опроса может определять, что ячейка выбрана, если определяемый ток и/или напряжение увеличиваются, это обозначает, что импеданс уменьшился (при фиксированном напряжении питания).

Если модуль 126 опроса определяет, что ячейка T была выбрана, операция (операции) доступа к памяти (например, считывания и/или записи) ячейки T может продолжиться. Если после приложения VT_SEL модуль 126 опроса определяет, что ячейка T не была выбрана, модуль 120 смещения C-ячейки выполнен с возможностью приложения смещения к C-ячейке на уровень невыбранной WL (например, невыбранной WL 206), и/или модуль 124 смещения C-ячейки выполнен с возможностью приложения смещения С-ячейки к невыбранной BL (например, невыбранной BL 208). Смещение C-ячейки может быть достигнуто путем увеличения Vdeswl и/или уменьшения Vdesbl относительно их номинального значения (например, нуля) таким образом, что соответственно увеличивается Vc. Модуль 114 управления WL и/или модуль 116 управления BL могут затем быть выполнены с возможностью увеличения, VT_SEL, путем увеличения Vselbl и/или уменьшения Vselwl на величину, соответствующую напряжению смещения C-ячейки Vc. Повышенное VT_SEL установлено так, чтобы выбрать ячейку T (то есть установлено выше чем или равным Vt), и при этом может выполняться операция доступа к памяти.

Следует понимать, что пороговое напряжение Vt выбора для каждой ячейки памяти в массиве с узлами пересечения может изменяться, в зависимости от по меньшей мере частичных изменений свойств материала и/или других характеристик ячеек памяти с узлами пересечения. Например, вариации Vt ячейки могут происходить из-за геометрической вариации формы ячейки (например, толщины, ширины, длины). Вариации формы ячейки могут привести к вариациям Vt в диапазоне +/-10% от номинального значения Vt. В другом примере, для некоторых типов ячеек памяти, с течением времени, Vt может увеличиваться из-за дрейфа и/или уменьшаться из-за тепловой кристаллизации ячейки.

Например, Vt для конкретной ячейки памяти может иметь значение между минимальным пороговым значением напряжения Vt min и максимальным пороговым значением напряжения Vt max. Например, путем выборки множества ячеек памяти можно получить распределение значений Vt между Vt min и Vt max. Прежде всего, VT_SEL может быть установлено, как номинальное значение (например, VT_SEL_nominal) на основе по меньшей мере частично распределения значений Vt. Например, VT_SEL_nominal может быть установлено, как значение Vt, которое больше чем, например, приблизительно 50% значений Vt распределения значений Vt. В другом примере VT_SEL_nominal может быть установлено, как значение Vt, которое больше, чем, например, приблизительно 80% значений Vt распределения значений Vt. В этом примере смещение C-ячейки может быть инициировано на уровне приблизительно 20% попыток выбора целевой ячейки памяти (для операций записи). Конкретные установки для VT_SEL_nominal могут быть выбраны на основе по меньшей мере частично характеристик распределения значений Vt. При выполнении операции смещение C-ячейки может инициироваться с частотой, относящейся к распределению. Например, возможны относительно низкие частоты переключения, например, меньше чем 1%.

Если во время операции VT_SEL, установленное, как VT_SEL_nominal, не приводит к выбору целевой ячейки, VT_SEL может быть установлено на большее значение, чем или равное Vt max, для выбора целевой ячейки. Напряжение Vc смещения C-ячейки затем может быть сопоставлено с разностью между Vt max и VT_SEL_nominal. Например, Vc может быть равно Vt max - VT_SEL_nominal.

Как описано здесь, Vc = Vdeswl - Vdesbl, таким образом, смещение C-ячейки может быть достигнуто путем увеличения Vdeswl и/или уменьшения Vdesbl. Например, для получения Vc 2 вольта, смещение C-ячейки может быть приложено к одной стороне невыбранных ячеек, например, Vdeswl может быть увеличено до +2 вольта, и Vdesbl может поддерживаться на уровне ноль вольт. Конечно, одностороннее смещение C-ячейки может быть аналогично получено путем уменьшения Vdesbl до -2 вольта и поддержания Vdeswl на уровне ноль вольт. В другом примере смещение C-ячейки может быть воплощено, используя двусторонний сбалансированный подход, например, Vdeswl может быть увеличено до +1 вольт, и Vdesbl может быть уменьшено до -1 вольт для получения Vc 2 вольта.

Односторонний подход состоит в переключении напряжения на и/или выборе половины WL и BL по сравнению с двусторонним подходом и, таким образом, может привести к относительно меньшим затратам на энергию переключения, ассоциированного с установлением смещения C-ячейки. Один источник напряжения смещения может использоваться для установления одностороннего смещения C-ячейки по сравнению с двусторонним подходом, который может быть основан на двух источниках напряжения смещения. Один источник напряжения смещения может быть воплощен, используя существующий источник напряжения, в зависимости от значения напряжения смещения. Используя существующий источник напряжения, можно уменьшить затраты на смещение C-ячейки (например, размер кристалла, потребление энергии, сложность).

Приложение смещения C-ячейки, когда не происходит выбор целевой ячейки при подаче VT_SEL, установленным на значение VT_SEL_nominal, (то есть, когда может потребоваться увеличенное окно операции), конфигурируют так, чтобы получить относительно низкое среднее потребление энергии по сравнению с подходами, при которых требуется либо постоянно подавать напряжение смещения C-ячейки ко всем ячейкам или прикладывать напряжение смещения C-ячейки во время операции с каждой из ячеек памяти. Например, в соответствии с настоящим раскрытием, смещение C-ячейки может прикладываться во время операции приблизительно к 20% ячеек памяти. Таким образом, потребление энергии в режиме ожидания, из-за смещения C-ячейки может быть исключено, и "затраты" на энергию, ассоциированные со смещением C-ячейки, могут быть ограничены только теми ячейками, которые не были выбраны при напряжении VT_SEL_nominal. Максимальный ток, отбираемый в соответствии с установкой C-ячейки, может быть ограничен, и может использоваться установка C-ячейки с малой задержкой, поскольку только для нескольких ячеек памяти может использоваться смещение C-ячейки при определенной операции доступа к памяти. Таким образом, можно исключить расширение шины для быстрого установления смещения C-ячейки.

В таблице 1 в качестве примера иллюстрируются некоторые схемы смещения C-ячейки. В таблице В обозначает вольты, и VT_SEL обозначает напряжение смещения, приложенное к целевой ячейке.

Таблица 1

Схема с нулевым смещением C-ячейки представляет пример напряжения WL и BL и приводит к напряжению смещения ячейки для смещения C-ячейки, равному нулю, то есть без смещения C-ячейки. Таким образом, целевая ячейка может быть выбрана, когда Vt sel ≥ 8 вольт и Vt равно 8 вольт. Смещение C-ячейки со сбалансированными WL и BL соответствует увеличенному Vdeswl и уменьшенному Vdesbl в равной степени (то есть сбалансировано), для получения смещения C-ячейки. Смещение C-ячейки только по WL сконфигурировано для увеличения только Vdeswl, для достижения смещения C-ячейки и увеличения напряжения смещения целевой ячейки VT_SEL.

Ряды в представленной выше таблице "Окно, расширенное по требованию" иллюстрируют пример, который соответствует варианту осуществления, соответствующему настоящему раскрытию. В этом примере, когда Vt меньше чем или равно 8 вольт и VT_SEL равно 8 вольт без смещения C-ячейки (то есть целевую ячейку выбирают без приложения смещения C-ячейки), смещение C-ячейки не прикладывается. Продолжая этот пример, когда Vt больше чем 8 вольт и меньше чем или равно 10 вольт, смещение C-ячейки 2В может быть получено путем увеличения Vdeswl до +2В, и Vselbl может быть затем увеличено до +6В для получения VT_SEL 10В. Конечно, смещение C-ячейки 2В может быть аналогично получено путем уменьшения Vdesbl до -2В, и Vselwl может быть уменьшено до -6В, для получения Vt 10В, для выбора целевой ячейки. Таким образом, в соответствии с настоящим раскрытием, смещение C-ячейки может прикладываться "по требованию", и окно операции может быть увеличено для этой ячейки (ячеек) памяти, которая не была выбрана, в ответ на установку напряжения смещения VT_SEL, как VT_SEL _nominal.

На фиг. 3 иллюстрируется блок-схема 300 последовательности операций для избирательного приложения смещения C-ячейки, в соответствии с различными вариантами осуществления настоящего раскрытия. Операции могут быть выполнены, например, с помощью контроллера памяти, например, контроллера 104 памяти, включающего в себя модуль 114 управления WL и модуль 116 управления BL. На блок-схеме 300 последовательности операций представлены примерные операции, выполненные для избирательного установления смещения C-ячейки. В частности, в блок-схеме 300 последовательности операций представлены примерные операции, выполняемые для инициирования выбора целевой ячейки без смещения C-ячейки и установления смещением C-ячейки, если не выбрана целевая ячейка, как описано здесь.

Операции блок-схемы 300 последовательности операций могут начинаться во время операции 302. Выбор целевой ячейки (T) может быть инициирован во время операции 304. Была ли выбрана целевая ячейка, может быть определено во время операции 306. Если целевая ячейка не была выбрана, смещение C-ячейки может быть установлено во время операции 308. Целевая ячейка может затем стать выбранной во время операции 310. Ход выполнения программы может затем перейти к операции 312. Если целевая ячейка была выбрана, операция доступа к памяти может быть выполнена во время операции 312. Например, операция доступа к памяти может включать в себя операцию считывания и/или записи (то есть программирование). Ход выполнения программы может затем закончиться во время операции 314.

Таким образом, операции в соответствии с блок-схемой 300 последовательности операций выполняются с попыткой выбора целевой ячейки без смещения C-ячейки и для установления смещения C-ячейки, если попытка выбора целевой ячейки не будет успешной. Смещение C-ячейки, таким образом, может быть установлено "по требованию".

В то время, как на фиг. 3 иллюстрируются различные операции, в соответствии с одним вариантом осуществления, следует понимать, что не все из операций, представленных на фиг. 3, являются необходимыми для других вариантов осуществления. Действительно, здесь совершенно понятно, что в других вариантах осуществления настоящего раскрытия, операции, представленные на фиг. 3, и/или другие операции, описанные здесь, могут быть скомбинированы таким образом, как, в частности, не представлено на любом из чертежей, но все еще в полном соответствии с настоящим раскрытием. Таким образом, пункты формулы изобретения, направленные на свойства и/или операции, которые точно не показаны на одном чертеже, рассматриваются как находящиеся в пределах объема и содержания настоящего раскрытия.

Используемый в любом варианте осуществления, представленном здесь, термин "модуль" может относиться к программному приложению, программному обеспечению, встроенному программному обеспечению и/или схеме, сконфигурированной для выполнения любой из упомянутых выше операций. Программное обеспечение может быть воплощено, как программный пакет, код, инструкции, наборы инструкций и/или данные, записанные на непереходном считываемого компьютером носителе информации. Встроенное программное обеспечение может быть воплощено как код, инструкции или набор инструкций, и/или данные, которые жестко закодированы (например, являются энергонезависимыми) в запоминающих устройствах.

"Схема", используемая в любом из представленных здесь вариантов осуществления, может содержать, например, одну или любую комбинацию из соединенных проводами схем, программируемые схем, таких как компьютерные процессоры, содержащие один или больше индивидуальных ядер для обработки инструкций, схема конечного автомата, и/или встроенное программное обеспечение, которое содержит инструкции, выполняемые программируемой схемой. Модули могут быть совместно или индивидуально внедрены, как схема, которая формирует часть более крупной системы, например, интегральная схема (IC), система на кристалле (SoC), настольные компьютеры, переносные компьютеры, планшетные компьютеры, серверы, смартфоны и т.д.

В некоторых вариантах осуществления язык описания аппаратных средств может использоваться для установления схемного и/или логического варианта (вариантов) осуществления для различных модулей и/или схем, описанных здесь. Например, в одном варианте осуществления язык описания аппаратных средств может соответствовать или может быть совместим с языком (VHDL) описания аппаратных средств с высокоскоростными интегральными схемами (VHSIC), которые могут обеспечивать изготовление полупроводников в виде одной или больше схем и/или модулей, описанных здесь. VHDL может соответствовать или может быть совместим со стандартом IEEE 1076-1987, стандартом IEEE 1076.2, IEEE1076.1, проектом 3.0 IEEE для VHDL 2006, проектом 4.0 IEEE для VHDL 2008 и/или другими версиями стандартов VHDL IEEE и/или другими стандартами описания аппаратных средств.

Таким образом, система и способ, выполненные с возможностью инициирования выбора целевой ячейки без смещения C-ячейки и для установления смещения C-ячейки, если целевая ячейка не выбрана, были описаны выше. Система и способ выполняются при попытке выбора целевой ячейки с номинальным напряжением смещения и для определения, была или нет выбрана целевая ячейка. Если выбор целевой ячейки не произошел, система и способ выполнены с возможностью установления смещения C-ячейки с последующим увеличением напряжения смещения целевой ячейки на величину, соответствующую напряжению смещения C-ячейки, для увеличения окна операции. Таким образом, смещение C-ячейки может быть воплощено для увеличения окна операций, в соответствии с необходимостью.

В соответствии с одним аспектом, предусмотрено устройство. Устройство включает в себя контроллер памяти, который включает в себя модуль управления линией слова (WL) и модуль управления линией битов (BL).

Контроллер памяти выполнен с возможностью инициирования выбора целевой ячейки памяти. Устройство дополнительно включает в себя модуль опроса, выполненный с возможностью определения, была ли выбрана целевая ячейка памяти, и модуль смещения C-ячейки выполнен с возможностью установления смещения C-ячейки, если целевая ячейка не была выбрана.

В соответствии с другим аспектом, предусмотрен способ. Способ включает в себя инициируют, с помощью контроллера памяти, выбор целевой ячейки памяти, определяют с помощью модуля опроса, была ли выбрана целевая ячейка памяти, и устанавливают, с помощью модуля смещения С-ячейки, смещение C-ячейки, если целевая ячейка не была выбрана.

В соответствии с другим аспектом, предусмотрена система. Система включает в себя процессор, массив памяти с узлами пересечения, который включает в себя целевую ячейку памяти, целевую линию слова (WL) и целевую линию битов (BL). Целевая ячейка памяти включена между целевой линией слова и целевой линией битов. Система дополнительно включает в себя контроллер памяти, выполненный с возможностью инициирования выбора целевой ячейки памяти. Контроллер памяти включает в себя модуль управления WL и модуль управления BL, модуль опроса, выполненный с возможностью определения, была ли выбрана целевая ячейка памяти, и модуль смещения C-ячейки, выполненный с возможностью установления смещения C-ячейки, если целевая ячейка не была выбрана.

Различные свойства, аспекты и варианты осуществления были описаны здесь. В отношении свойств, аспектов и вариантов осуществления могут быть выполнены комбинации друг с другом, а также их вариации и модификации, как будет понятно для специалиста в данной области техники. Настоящее раскрытие следует, поэтому, рассматривать, как охватывающее такие комбинации, вариации и модификации.

Группа изобретений относится к запоминающим устройствам и может быть использована для установления смещения ячейки памяти. Техническим результатом является уменьшение мощности, затрат энергии, размеров кристалла, времени задержки. Устройство содержит контроллер памяти, включающий в себя модуль управления линией слова (WL), и модуль управления линией битов (BL), при этом контроллер памяти выполнен с возможностью инициирования выбора целевой ячейки памяти; модуль опроса, выполненный с возможностью определения, была ли выбрана целевая ячейка памяти; и модуль смещения С-ячейки, выполненный с возможностью установления смещения С-ячейки, если целевая ячейка не выбрана. 3 н. и 16 з.п. ф-лы, 3 ил., 1 табл.

1. Устройство для установления смещения ячейки памяти, содержащее:

контроллер памяти, содержащий модуль управления линией слова (WL) и модуль управления линией битов (BL), при этом контроллер памяти выполнен с возможностью инициирования выбора целевой ячейки памяти;

модуль опроса, выполненный с возможностью определения, была ли выбрана целевая ячейка памяти; и

модуль смещения C-ячейки, выполненный с возможностью установления смещения C-ячейки, если целевая ячейка не выбрана.

2. Устройство по п. 1, в котором модуль смещения C-ячейки выполнен с возможностью регулирования напряжения смещения отказа от выбора WL и/или напряжения смещения отказа от выбора BL для установления смещения C-ячейки.

3. Устройство по п. 1, в котором контроллер памяти выполнен с возможностью увеличения напряжения смещения целевой ячейки памяти на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

4. Устройство по п. 1, в котором модуль управления WL выполнен с возможностью приложения напряжения смещения выбора WL к целевой WL, а модуль управления BL выполнен с возможностью приложения напряжения смещения выбора BL к целевой BL для инициирования выбора целевой ячейки памяти, причем разность между напряжением смещения выбора BL и напряжением смещения выбора WL соответствует напряжению смещения целевой ячейки, при этом напряжение смещения целевой ячейки имеет номинальное значение.

5. Устройство по п. 4, в котором модуль управления WL выполнен с возможностью регулирования напряжения смещения выбора WL для увеличения напряжения смещения целевой ячейки на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

6. Устройство по п. 4, в котором модуль управления BL выполнен с возможностью регулирования напряжения смещения выбора BL для увеличения напряжения смещения целевой ячейки на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

7. Способ установления смещения ячейки памяти, содержащий этапы, на которых:

инициируют, с помощью контроллера памяти, выбор целевой ячейки памяти;

определяют, с помощью модуля опроса, была ли выбрана целевая ячейка памяти; и

устанавливают, с помощью модуля смещения C-ячейки, смещение C-ячейки, если целевая ячейка не выбрана.

8. Способ по п. 7, дополнительно содержащий этап, на котором:

регулируют, с помощью модуля смещения C-ячейки, напряжение смещения отказа от выбора WL и/или напряжение смещения отказа от выбора BL для установления смещения C-ячейки.

9. Способ по п. 7, дополнительно содержащий этап, на котором:

увеличивают, с помощью контроллера памяти, напряжение смещения целевой ячейки памяти на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

10. Способ по п. 7, в котором на этапе инициирования выбора целевой ячейки памяти:

прикладывают, с помощью модуля управления WL, напряжение смещения выбора WL к целевой WL и

прикладывают, с помощью модуля управления BL, напряжение смещения выбора BL к целевой BL,

причем разность между напряжением смещения выбора BL и напряжением смещения выбора WL соответствует напряжению смещения целевой ячейки, при этом напряжение смещения целевой ячейки имеет номинальное значение.

11. Способ по п. 10, дополнительно содержащий этап, на котором регулируют, с помощью модуля управления WL, напряжение смещения выбора WL для увеличения напряжения смещения целевой ячейки на величину, соответствующую смещению С-ячейки, если целевая ячейка не выбрана.

12. Способ по п. 10, дополнительно содержащий этап, на котором регулируют, с помощью модуля управления BL, напряжение смещения выбора BL для увеличения напряжения смещения целевой ячейки на величину, соответствующую смещению C-ячейки, если целевая ячейка не выбрана.

13. Способ по п. 7, дополнительно содержащий этап, на котором выполняют, с помощью контроллера памяти, операцию считывания и/или операцию записи на целевой ячейке памяти.

14. Система для установления смещения ячейки памяти, содержащая:

процессор;

массив памяти с узлами пересечения, содержащий целевую ячейку памяти, целевую линию слова (WL) и целевую линию битов (BL), причем целевая ячейка памяти подключена между целевой линией слова и целевой линией битов; и

контроллер памяти, выполненный с возможностью инициировать выбор целевой ячейки памяти, при этом контроллер памяти содержит:

модуль управления WL и модуль управления BL,

модуль опроса, выполненный с возможностью определения, была ли выбрана целевая ячейка памяти, и

модуль смещения C-ячейки, выполненный с возможностью установления смещения C-ячейки, если целевая ячейка не выбрана.

15. Система по п. 14, в которой модуль смещения C-ячейки выполнен с возможностью регулирования напряжения смещения отказа от выбора WL и/или напряжения смещения отказа от выбора BL для установления смещения C-ячейки.

16. Система по п. 14, в которой контроллер памяти выполнен с возможностью повышения напряжения смещения целевой ячейки памяти на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

17. Система по п. 14, в которой модуль управления WL выполнен с возможностью приложения напряжения смещения выбора WL к целевой WL, а модуль управления BL выполнен с возможностью приложения напряжения смещения выбора BL к целевой BL для инициирования выбора целевой ячейки памяти, причем разность между напряжением смещения выбора BL и напряжением смещения выбора WL соответствует напряжению смещения целевой ячейки, при этом напряжение смещения целевой ячейки имеет номинальное значение.

18. Система по п. 17, в которой модуль управления WL выполнен с возможностью регулирования напряжения смещения выбора WL для увеличения напряжения смещения целевой ячейки на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

19. Система по п. 17, в которой модуль управления BL выполнен с возможностью регулирования напряжения смещения выбора BL для увеличения напряжения смещения целевой ячейки на величину, относящуюся к смещению C-ячейки, если целевая ячейка не выбрана.

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| АДРЕСАЦИЯ МАТРИЧНОЙ ПАМЯТИ | 2001 |

|

RU2239889C1 |

Авторы

Даты

2018-04-18—Публикация

2015-03-09—Подача