Изобретение относится к вычислительной технике и может быть использовано при создании электрически программируемых постоянных запоминающих устройство на лавинно-инжекционных транзисторах с плавающими затворами и ультрафиолетовым стиранием информации типа СППЗУ.

Целью изобретения является повышение надежности усилителя записи-считывания в режиме записи при программи- ровании матричного накопителя.

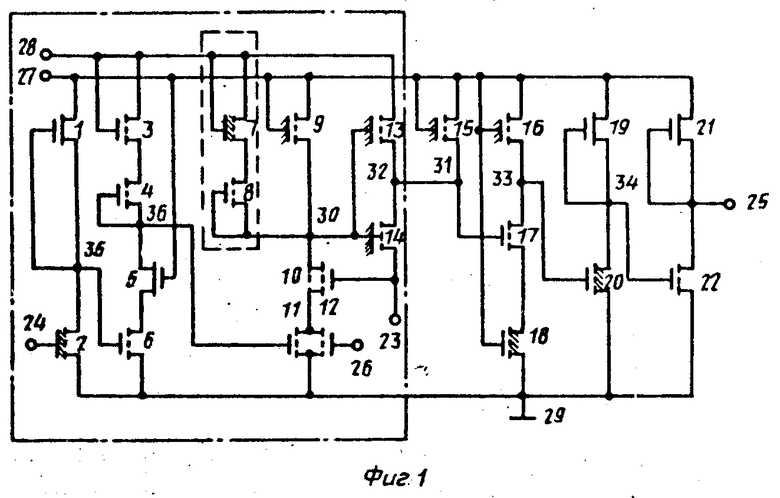

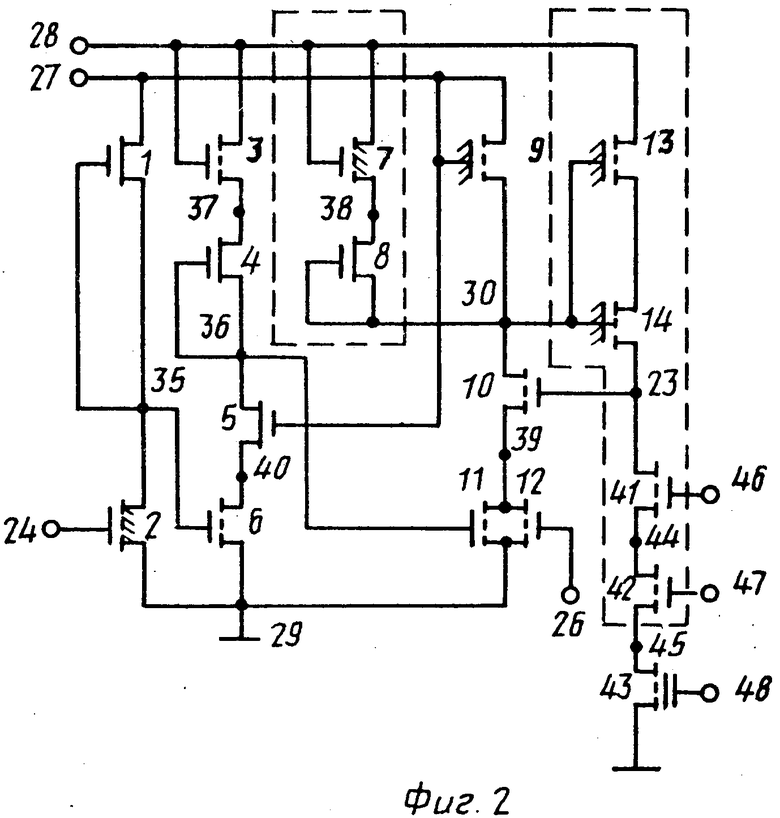

На фиг.1 изображена принципиальная электрическая схема усилителя записи-считывания (штрихпунктирной линией выделен функциональный узел, который является усилителем записи); на фиг.2 - электрическая схема усилителя записи со столбцовыми ключами и ячейкой памяти.

Усилитель (см. фиг.1 и 2) содержит МДП-транзисторы 1-22, из которых пять нагрузочных транзисторов обедненного типа: первый 1, второй 4, третий 8, девятый 19, десятый 21, три нагрузочных транзистора с нулевым пороговым напряжением: четвертый 9, пятый 15, шестой 16, два нагрузочных транзистора обогащенного типа: девятый 3, десятый 7, двенадцать ключевых транзисторов, из которых девять ключевых транзисторов обогащенного типа: первый 2, второй 6, четвертый 10, третий 11, пятый 12, восьмой 17, девятый 18, десятый 20, одиннадцатый 22, два ключевых транзистора с нулевым пороговым напряжением: седьмой 13, шестой 14, двенадцатый ключевой разделительный транзистор 5 обедненного типа, вход-выход 22 записи-считывания усилителя, шину 24 записи данных, информационный выход 25 усилителя, шину 26 управления режимом, первую шину 27 питания, вторую шину 28 питания, шину 29 нулевого потенциала.

На фиг.1 и 2 позициями 30-40 обозначены узлы принципиальной электрической схемы усилителя.

Работа усилителя определяется сигналом на шине 26, а также сигналами, поступающими на вход-выход 23 и шину 24 записи данных. Усилитель переходит в режим усилителя считывания, когда на шину 26 приходит высокий уровень (логической "1"), равный напряжению на шине 27. Когда на шину 26 приходит сигнал низкого уровня (логического "0"), то усилитель переходит в режим работы усилителя записи (в этом случае вход 23 является одновременно и выходом усилителя записи). В связи с этим в описании использовано два термина: усилитель считывания, когда речь идет о режиме считывания, и усилитель записи, когда речь идет о программировании ячейки памяти в матричном накопителе.

Схема усилителя записи-считывания включает в себя четыре вида МДП-транзисторов, отличающихся значениями пороговых напряжений:

U01 = 0 ± 0,2 В - транзисторы 9, 13, 14, 15 и 16 с нулевым порогом;

U02 = 0,6 ± 0,2 В - транзисторы 3, 6, 10, 11, 12, 17 и 22 обогащенного типа первого вида;

U03 = 1,0 ± 0,2 В - транзисторы 2, 7, 18 и 20 обогащенного типа второго вида;

U04 = -3,25 ± 0,75 В - транзисторы 1, 4, 5, 8, 19 и 21 с обеднением.

Формирование первого вида транзисторов с обогащением U02 = 0,6 ± 0,2 В производится одновременно с легированием каналов ячеек памяти матричного накопителя с целью получения более высокой крутизны, формирование второго вида транзистора обогащенного типа с U03 = 1,0± 0,2 В обусловлено обеспечением более высокой надежности схемы усилителя записи в режиме программирования входной информации с входными нормированными уровнями Uвх0 = 0,8 В, Uвх1 = 2 В.

Для более полного понимания работы схемы усилителя записи-считывания в режиме записи на фиг.2 представлена электрическая схема только усилителя записи с дополнительными ключевыми МДП-транзисторами 41 и 42 обогащенного типа, а также элементом 43 памяти, узлами 44 и 45. Затворы 46 и 47 ключевых транзисторов 41 и 42 подключаются к дешифратору столбцов, а затвор 48 элемента 43 памяти - к строчному дешифратору.

На шину 26 усилителя записи-считывания в режиме записи приходит сигнал логического "0", и ключевой транзистор 12 не блокирует работу усилителя записи, так как переходит в закрытое состояние. В момент программирования (записи) на первую шину 27 питания подается напряжение 5 В±5%, на вторую шину 28 питания подается, например, напряжение 25 В + 1 В.

Если на шину 24 усилителя записи (шину записи данных) приходит уровень логической "1", то ключевой транзистор 2, открываясь, понижает высокий уровень напряжения в узле 35 до уровня логического "0", достаточного для запирания ключевого транзистора 6. Запирание транзистора 6 вызывает нарастание напряжения в узле 36. Высокий потенциал узла 36 отпирает ключевой транзистор 11, который вызывает шунтирование узла 30 до низкого уровня, примерно равного 2 - 3 В, что приводит к резкому снижению проводимости ключевых транзисторов 13 и 14 и установлению режима, подобного режиму усилителя считывания, т.е. на выходе 23 усилителя записи устанавливается потенциал 1,5 - 2,5 В. Этот потенциал через открытые ключевые транзисторы 41 и 42 передается на сток элемента 43 памяти (узел 45). В режиме программирования на затворах 46, 47 и 48 устанавливается потенциал, равный потенциалу на шине 28.

В режиме считывания (см. фиг.1) на шину 24 усилителя приходит сигнал высокого уровня (логической "1"), который отпирает двенадцатый ключевой транзистор, шунтируя исток транзистора 11 на шину 29 нулевого потенциала.

Пусть работа усилителя рассматривается с момента, когда к входу-выходу 23 подключена разрядная шина (столбца) с проводящей ячейкой памяти Iя.п=25 мкА. В этот момент происходит падение потенциала на входе-выходе 23 за счет разряженной паразитной емкости столбца, которая достаточно быстро заряжается токами, протекающими через ширококанальные ключевые транзисторы 13 и 14 и нагрузочный транзистор 15, выполненные на материале подложки. Снижение потенциала на входе-выходе 23 вызывает подзапирание транзистора 10 и увеличение потенциала узла 30, вызывая быстрое подзапирание транзистора 10 усилительного каскада на транзисторах 7, 8, 9, 10, 12, 13, 14 и 15. Быстрое переключение узла 30 происходит через нагрузочные транзисторы 7, 8 и 9, причем транзисторы 7 и 8 в усилителе считывания играют второстепенную роль, основной нагрузкой усилительного каскада является транзистор 9. Резкое повышение потенциала в узле 30 и быстрое понижение потенциала на входе-выходе 23 приводит к отпиранию ширококанальных транзисторов 13 и 14, выполненных на материале подложки, и быстрому разряду узловой емкости 31 несколько выше потенциала, установившегося на входе-выходе 23.

Для предупреждения генерации усилителя считывания необходимо выполнять следующее условие: ток нагрузочного транзистора 15 должен быть меньше тока ячейки памяти в проводящем состоянии.

Инверторный каскад на транзисторах 16, 17 и 18 является ответственным звеном в усилителе считывания и выполняет функции преобразователя уровня, обеспечивая нормальный логический перепад в узле 33 (U330 = 0,66 В, U331 = 1,83 В). Для последующего инвертора на транзистоpах 19 и 20 ключевой транзистор 18 служит для подсмещения потенциала истока ключевого транзистора 11, когда последний открыт и через него протекает ток, чтобы уровень логического "0" узла 33 отслеживал изменение порогового напряжения транзистора 20. Транзисторы 18 и 20 выполнены с одинаковыми порогами (U03 = 1 В).

Уровень логической "1" в узле 33 невысок (U33 = 1,83), поэтому инвертор на транзисторах 19 и 20 должен иметь соотношение между ключевым транзистором 20 и нагрузочным транзистором 19, по крайней мере, не менее m = 43, которое определяется из соотношения W/L ключевого транзистора 20 к нагрузочному транзистору 19. Повышение потенциала узла 33 приводит к возрастанию проводимости транзистора 20 и разряду узла 34, что значительно ниже порогового напряжения транзистора 22. Это незамедлительно сказывается на повышении потенциала на выходе 25 усилителя считывания с 0,2 до 4,3 В.

В следующий момент времени к первому входу-выходу 23 подключается разрядная шина (столбец) с запрограммированной ячейкой памяти (Iя.п = 5 мкА), при этом берется наихудший случай, когда паразитная емкость столбца разряжена до нулевого потенциала. При этом в момент переходного процесса потенциал на входе-выходе 23 усилителя понижается. Этот провал потенциала вызывает отпирание ключевых ширококанальных транзисторов 13 и 14, которые достаточно быстро подзаряжают узловые емкости на входе-выходе 23 и столбца. Ключевой транзистор 10 приоткрывается, и потенциал узла 30 начинает понижаться. Понижение потенциала узла 30 и повышение потенциала на входе-выходе 23 вызывает запирание ключевых транзисторов 13 и 14, и нагрузочный транзистор 15 заряжает емкость узла 31. Изменение потенциала узла 31 вызывает переключение инвертора-преобразователя на транзисторах 16, 17 и 18. Понижение уровня напряжения в узле 33 до значения порогового напряжения транзистора 20 вызывает резкое возрастание потенциала узла 34, которое переключает последующий инвертор на транзисторах 21 и 22 из состояния логической "1" в состояние логического "0" (выход 25).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании электрически программируемых постоянных запоминающих устройств на лавинноинжекционных транзисторах с плавающими затворами и ультрафиолетовым стиранием информации. Целью изобретения является повышение надежности усилителя записи-считывания в режиме записи при программировании матричного накопителя. Схема усилителя записи-считывания включает в себя четыре вида МДП-транзисторов, отличающихся значениями пороговых напряжений: U01= 0 ± 0,2B - транзисторы с нулевым порогом; U02= 0,6 ± 0,2B - транзисторы обогащенного типа первого вида; U03= 1,0 ± 0,2B - транзисторы обогащенного типа второго вида; U04= -3,25 ± 0,75B - транзисторы с обеднением. Формирование первого вида транзисторов с обогащением производится одновременно с легированием каналов ячеек памяти матричного накопителя с целью получения более высокой крутизны. Формирование второго вида транзисторов обогащенного типа обусловлено обеспечением более высокой надежности схемы усилителя записи в режиме программирования входной информации с входными нормированными уровнями U

УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ содержащий ключевые транзисторы с первого по двенадцатый и нагрузочные транзисторы с первого по восьмой, причем затвор и исток первого нагрузочного транзистора подключены к стоку первого и затвору второго ключевых транзисторов, стоки первого, четвертого, пятого, шестого, седьмого и восьмого нагрузочных транзисторов подключены к первой шине питания, исток первого ключевого транзистора подключен к шине нулевого потенциала, затвор и исток второго нагрузочного транзистора подключены к затвору третьего ключевого транзистора, затвор и исток третьего нагрузочного транзистора подключены к стоку четвертого ключевого транзистора, исток четвертого ключевого транзистора подключен к стокам третьего и пятого ключевых транзисторов, исток четвертого нагрузочного транзистора и затвор шестого ключевого транзистора подключены к стоку четвертого ключевого транзистора, затвор четвертого ключевого транзистора и исток шестого ключевого транзистора объединены и являются входом - выходом усилителя считывания, затвор пятого ключевого транзистора является входом задания режима усилителя записи - считывания, а затвор первого ключевого транзистора - входом данных усилителя записи - считывания, затворы, четвертого, пятого, шестого нагрузочных транзисторов подключены к первой шине питания, сток седьмого ключевого транзистора подключен к второй шине питания, а его затвор - к стоку четвертого ключевого транзистора, сток шестого и исток седьмого ключевых транзисторов подключены к истоку пятого нагрузочного транзистора и затвору восьмого ключевого транзистора, сток девятого ключевого транзистора подключен к истоку восьмого ключевого транзистора, затвор девятого ключевого транзистора подключен к первой шине питания, сток восьмого ключевого транзистора подключен к истоку шестого нагрузочного транзистора и затвору десятого ключевого транзистора, затвор и исток седьмого нагрузочного транзистора подключены к стоку десятого и затвору одиннадцатого ключевых транзисторов, истоки второго, третьего, пятого, девятого, десятого и одиннадцатого ключевых транзисторов подключены к шине нулевого потенциала, затвор и исток восьмого нагрузочного транзистора и сток одиннадцатого ключевого транзистора объединены и являются информационным выходом усилителя записи - считывания, отличающийся тем, что, с целью повышения надежности усилителя записи - считывания при программировании матричного накопителя, в него введены девятый и десятый нагрузочные транзисторы, причем затворы и стоки девятого и десятого нагрузочных транзисторов подключены к второй шине питания, исток девятого нагрузочного транзистора подключен к стоку второго нагрузочного транзистора, исток десятого нагрузочного транзистра подключен к стоку третьего нагрузочного транзистора, сток двенадцатого ключевого транзистра подключен к затвору третьего ключевого транзистора, исток и затвор двенадцатого ключевого транзистора подключены соответственно к стоку второго ключевого транзистора и первой шине питания.

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-12-30—Публикация

1987-06-01—Подача