Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к коммуникационным технологиям и, в частности, к способу и устройству для согласования скорости передачи для кодирования.

Уровень техники

В настоящее время основным принципом полярного кода является определение вектора строки (или вектора столбца) матрицы кодирования в соответствии с конкретным условием с использованием Bhattacharyya параметра или емкости (симметричной емкости) или определение вектора строки (или вектора столбца) соответствующей матрицы кодирования с использованием частоты ошибок в битах. Таким образом, полярный код может иметь лучшую производительность, например: уменьшенную величину частоты ошибок в битах или повышенную скорость передачи данных, используя выбранный вектор строки (или вектор столбца) матрицы кодирования согласно вышеизложенному способу.

Дополнительно, полярный код может дополнительно поддерживать функцию гибридного автоматического запроса на повторную передачу (гибридный автоматический запрос на повторную передачу, HARQ, для краткости) с использованием алгоритма двухступенчатого согласования скоростей передачи данных. В частности, конкретный способ реализации процесса согласования скорости передачи данных по полярному коду состоит в следующем: делят кодированные биты, вырабатываемые кодером полярного кода, на три группы, и выполняют независимую и равномерную операцию выкалывания или операцию повторения для каждой группы, так что длина кодированного бита может быть сопоставлена с размером виртуального инкрементного избыточного буфера (инкрементальный избыточный буфер, коротко IR-буфер) и размером ресурса передачи.

Однако когда используется алгоритм двухступенчатого согласования скоростей передачи данных, кодированные биты, выводимые кодером полярного кода, необходимо разделить на три группы, что, следовательно, противоречит выбору вектора строки (или вектора столбца) матрицы кодирования полярного кода. То есть, в случае, когда не учитывается приоритетный порядок расположения и порядок вывода битов, вектор строки (или вектор столбца) матрицы кодирования не может быть выбран по вышеизложенному способу и, следовательно, производительность снижается во время декодирования, вызывая существенное повышение уровня ошибок при передаче данных при декодировании, и дополнительно являясь причиной снижения производительности полярного кода.

Раскрытие сущности изобретения

Варианты осуществления настоящего изобретения обеспечивают способ и устройство для согласования скорости передачи для кодирования для решения технической задачи предшествующего уровня техники, согласно которому использование алгоритма двухступенчатого согласования скоростей передачи может противоречить выбору вектора строки (или вектора столбца) матрицы кодирования полярного кода, что приводит к снижению производительности во время декодирования, вызывая существенное повышение уровня ошибок при передаче данных декодирования, и дополнительно являясь причиной снижения производительности полярного кода.

Первый аспект вариантов осуществления настоящего изобретения обеспечивает способ согласования скорости для кодирования, включающий в себя:

деление кодированных битов, выводимых кодером полярного кода, на

выполнение процесса битового уменьшения кодированных бит во множестве групп

сравнение количества доступных битов канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполнение, в соответствии с результатом сравнения, процесса повторения или уменьшения кодированных бит во множестве групп, хранящиеся в виртуальном модуле IR буфера; и

выполнение тандемной обработки закодированных бит, на которых выполняют процесс повторения или уменьшения, для генерирования одного битового потока и отправки битового потока по каналу передачи.

В первом возможном способе реализации первого аспекта, когда

начиная с 1-й группы, последовательный вывод кодированных бит, на которых выполняют процесс перемежения, в каждой группе в виртуальный модуль IR буфера, до тех пор, пока не будут выведены

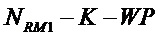

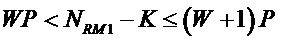

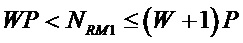

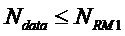

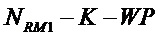

Ссылаясь на первый возможный вариант реализации первого аспекта, во втором возможном варианте реализации первого аспекта, сравнение количества доступных битов канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполнение, в соответствии с результатом сравнения, процесса повторения или уменьшения закодированных бит во множестве групп, хранящихся в виртуальном модуле IR буфера включает в себя:

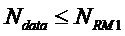

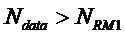

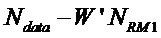

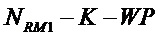

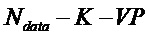

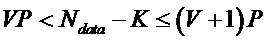

когда,

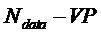

когда,

Со ссылкой на возможный вариант реализации первого аспекта, в третьем возможном варианте реализации первого аспекта, когда

последовательный вывод закодированных битов, на которых выполняют процесс перемежения, в первой группе до W-й группы в виртуальный модуль IR буфера и вывод 1-й по

Ссылаясь на третий возможный вариант реализации первого аспекта, в четвертом возможном варианте реализации первого аспекта, сравнение количества доступных битов канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполнение, в соответствии с результатом сравнения, процесса повторения или уменьшения закодированных бит во множестве групп, хранящихся в виртуальном модуле IR буфера, включает в себя:

когда

когда

Со ссылкой на возможный вариант реализации первого аспекта в пятом возможном варианте реализации первого аспекта, когда 1-я группа включает в себя системные биты, 2-я группа по

вывод системных битов, на которых выполняют процесс перемежения, в 1-й группе в виртуальный модуль IR буфера; последовательный вывод битов четности, на которых выполняют процесс перемежения, во 2-й группе по W-ю группу в виртуальный модуль IR буфера; и затем вывод 1-го по

Ссылаясь на пятый возможный вариант реализации первого аспекта, в шестом возможном варианте реализации первого аспекта, сравнение количества доступных битов канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполнение, в соответствии с результатом сравнения, процесса повторения или уменьшения закодированных бит во множестве групп, хранящихся в виртуальном модуле IR буфера, включает в себя:

когда,

когда

Второй аспект вариантов осуществления настоящего изобретения обеспечивает устройство для согласования скорости для кодирования, включающее в себя:

модуль деления, выполненный с возможностью разделять кодированные биты, выводимые кодером полярного кода, на

модуль перемежения, выполненный с возможностью выполнять процесс перемежения кодированных бит в 1-й группе по

первый модуль согласования скорости, выполненный с возможностью выполнять процесс битового уменьшения кодированных бит во множестве групп

модуль IR буфера, выполненный с возможностью хранить закодированные биты во множестве групп, выводимые первым модулем согласования скорости;

второй модуль согласования скорости, выполненный с возможностью сравнивать количество доступных битов канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполнять в соответствии с результатом сравнения процесс повторения или уменьшения кодированных бит во множестве групп, хранящихся в виртуальном модуле IR буфера; и

модуль сбора кодированных битов, выполненный с возможностью выполнять тандемную обработку закодированных бит, на которых выполняют процесс повторения или уменьшения, для генерирования одного битового потока и отправки битового потока посредством канала передачи.

В первом возможном варианте реализации второго аспекта, когда

Со ссылкой на первый возможный вариант реализации второго аспекта, во втором возможном варианте реализации второго аспекта второй модуль согласования скорости включает в себя:

блок обработки битового уменьшения, выполненный с возможностью: когда

блок обработки повторения бит, выполненный с возможностью: когда

Со ссылкой на возможный вариант реализации второго аспекта, в третьем возможном варианте реализации второго аспекта, когда

Со ссылкой на третий возможный вариант реализации второго аспекта, в четвертом возможном варианте реализации второго аспекта второй модуль согласования скорости включает в себя:

блок обработки битового уменьшения, выполненный с возможностью: когда

блок обработки повторения бит, выполненный с возможностью: когда

Со ссылкой на возможный вариант реализации второго аспекта, в пятом возможном варианте реализации второго аспекта, когда 1-я группа включает в себя системные биты, со 2-й группы по

Со ссылкой на пятый возможный вариант реализации второго аспекта в шестом возможном варианте реализации второго аспекта второй модуль согласования скорости включает в себя:

блок обработки битового уменьшения, выполненный с возможностью: когда

блок обработки повторения бит, выполненный с возможностью: когда

По способу и устройству для согласования скорости для кодирования в вариантах осуществления настоящего изобретения, кодированные биты, выводимые кодером полярного кода, делятся на М-группы, и выполняют процесс перемежения кодированных бит в 1-й группе до M-й группы отдельно; выполняют процесс битового уменьшения кодированных бит во множестве групп

Краткое описание чертежей

С целью более подробного описания технических решений в вариантах осуществления настоящего изобретения или предшествующего уровня техники, ниже кратко представлены прилагаемые чертежи, необходимые для описания вариантов осуществления или предшествующего уровня техники. Очевидно, что прилагаемые чертежи в следующем описании показывают некоторые варианты осуществления настоящего изобретения, и специалисты в данной области техники могут все еще получать другие чертежи из этих сопроводительных чертежей без творческих усилий.

Фиг. 1 является блок-схемой алгоритма варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением;

Фиг. 2 является блок-схемой алгоритма другого варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением;

Фиг. 3 является блок-схемой алгоритма еще одного варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением;

Фиг. 4 является блок-схемой алгоритма еще одного варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением;

Фиг. 5 является схемой варианта осуществления устройства для согласования скорости для кодирования в соответствии с настоящим изобретением; и

Фиг. 6 является схемой другого варианта осуществления устройства для согласования скорости для кодирования в соответствии с настоящим изобретением.

Осуществление изобретения

С целью более четкого описания целей, технических решений и преимуществ вариантов осуществления настоящего изобретения, ниже приведено четкое и полное описание технических решений в вариантах осуществления настоящего изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления настоящего изобретения изобретение. Очевидно, что описанные варианты осуществления представляют собой некоторые из них, но не все варианты осуществления настоящего изобретения. Все другие варианты осуществления, полученные специалистами в данной области техники на основании вариантов осуществления настоящего изобретения без творческих усилий, находятся в пределах защиты настоящего изобретения.

Фиг. 1 является блок-схемой алгоритма варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением. Как показано на фиг. 1, способ в этом варианте осуществления может включать в себя:

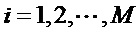

Этап 101: разделяют кодированные биты, выведенные кодером полярного кода, на M группы, и выполняют процесс перемежения закодированных бит в 1-й группе по M-ю группу отдельно.

В этом варианте осуществления кодированные биты, выводимые кодером полярного кода, могут быть систематическими битами с полярным кодированием или несистематическими битами с полярным кодированием.

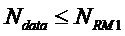

Этап 102: выполняют процесс битового уменьшения кодированных бит во множестве групп

Этап 103: сравнивают количество доступных бит канала передачи с количеством кодированных битов во множестве групп, сохраненных в виртуальном модуле IR буфера, и выполняют, согласно результату сравнения, процесс повторения или уменьшения кодированных битов во множестве групп, хранящихся в виртуальном модуле IR буфера.

В этом варианте осуществления количество доступных бит канала передачи представляет собой количество доступных ресурсов физического уровня радио интерфейса.

В этом варианте осуществления, если количество кодированных битов во множестве групп, сохраненные в виртуальном модуле IR буфера, больше или равно количеству доступных битов канала передачи, то выполняют процесс уменьшения битов, т.е., первые кодированные биты группы, соответствующие выбранной начальной позиции, предпочтительно выводят, и оставшиеся кодированные биты отбрасывают. Дополнительно, если количество кодированных битов во множестве групп, хранящихся в виртуальном модуле IR буфера, меньше количества доступных битов канала передачи, то выполняют процесс повторения битов и, начиная с группы, соответствующей выбранной начальной позиции, кодированные биты групп выводят циклически и многократно, выводят преимущественно первые кодированные биты групп и последние закодированные биты отбрасывают.

Выбранная начальная позиция может быть предварительно определена или представляет собой индикацию гибридного запроса автоматического повторения (HARQ) версии избыточности (RV), посланной системой беспроводной связи.

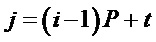

Этап 104: выполняют процесс тандемной обработки закодированных бит, на которых выполняют процесс повторения или уменьшения, для генерирования одного битового потока и отправки битового потока посредством канала передачи.

В этом варианте осуществления кодированные биты, выводимые кодером полярного кода, делятся на М-группы, и выполняют процесс перемежения кодированных бит в 1-й группе по M-ю группу отдельно; выполняют процесс битового уменьшения кодированных бит во множестве групп

Техническое решение в варианте осуществления способа, показанном на фиг. 1, подробно описана ниже, используя несколько конкретных вариантов осуществления.

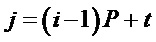

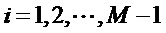

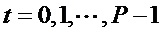

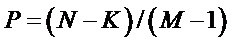

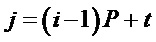

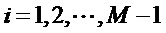

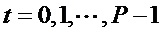

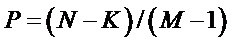

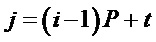

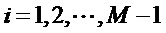

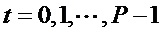

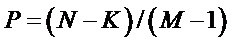

Фиг. 2 представляет собой блок-схему алгоритма другого варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением. На основании вышеизложенного варианта осуществления, показанного на фиг. 1, как показано на фиг. 2, в этом варианте осуществления используется пример, в котором кодированные биты, выводимые кодером полярного кода, могут быть несистематическими битами с полярным кодированием, то есть, эта

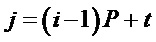

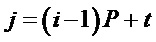

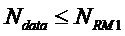

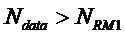

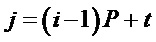

Этап 201: начиная с 1-й группы, последовательно выводят кодированные биты, на которых выполняют процесс перемежения в каждой группе, в виртуальный модуль IR буфера до тех пор, пока не будут выведены

Возможно, конкретный вариант реализации на этапе 103 является:

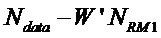

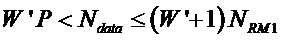

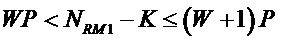

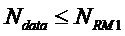

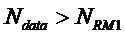

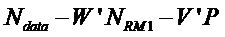

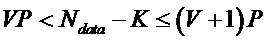

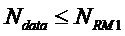

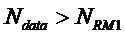

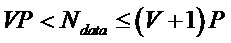

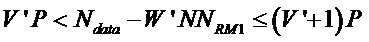

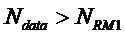

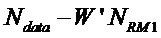

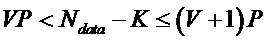

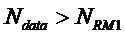

Этап 202: сравнивают

Этап 203: начиная с S1-й группы, соответствующей предварительно сконфигурированной первой начальной позиции, в виртуальном модуле IR буфера последовательно выводят из каждой группы кодированные биты, на которых выполняют процесс перемежения, до тех пор, пока не будут выведены

Этап 204: начиная с S1-й группы, последовательно и циклически начинают выводить из каждой группы кодированные биты, на которых выполняют процесс перемежения, до тех пор, пока не будут выведены

Фиг. 3 является блок-схемой алгоритма еще одного варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением. На основании вышеизложенного варианта осуществления, показанного на фиг. 1, как показано на фиг. 3, в этом варианте осуществления, пример, в котором кодированные биты, выводимые кодером полярного кода, могут быть несистематическими битами с полярным кодированием, то есть,

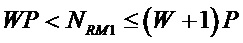

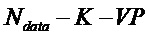

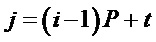

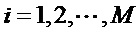

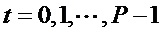

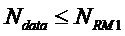

Этап 301: последовательно выводят кодированные биты, на которых выполняют процесс перемежения, в 1-й группе по W группы в виртуальный модуль IR буфера и выводят с 1-го по

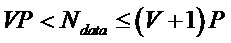

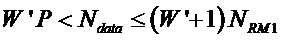

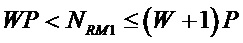

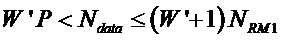

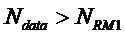

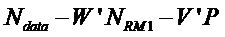

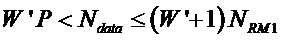

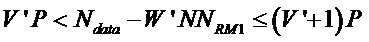

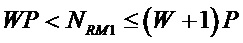

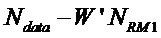

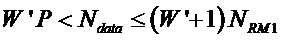

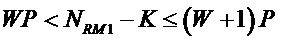

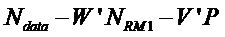

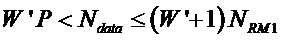

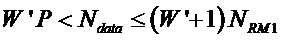

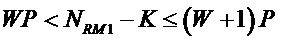

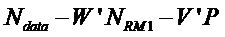

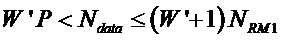

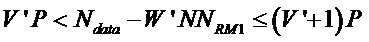

W удовлетворяет условию

Возможен другой конкретный способ реализации на этапе 103:

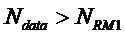

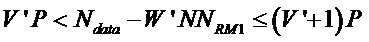

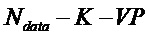

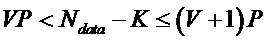

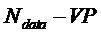

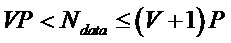

Этап 302: сравнивают

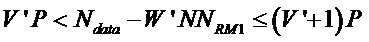

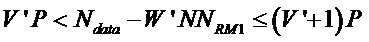

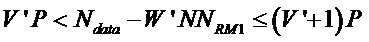

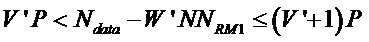

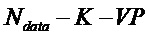

Этап 303: начиная с S2-й группы, соответствующей предварительно сконфигурированной второй начальной позиции, в виртуальном модуле IR буфере, последовательно выводят кодированные биты, на которых выполняют процесс перемежения, в V группах и выводят 1-й по

V удовлетворяет условию

Этап 304: начиная с S2-й группы, последовательно и циклически выводят кодированные биты, на которых выполняют процесс перемежения, в группах W + 1, где количество циклов равно

Фиг. 4 блок-схема алгоритма еще одного варианта осуществления способа согласования скорости для кодирования в соответствии с настоящим изобретением. На основании вышеизложенного варианта осуществления, показанного на фиг. 1, как показано на фиг. 4, в этом варианте осуществления пример, в котором кодированные биты, выводимые кодером полярного кода, могут быть систематическими битами с полярным кодированием, то есть, 1-я группа включает в себя системные биты, вторая группа по M группе включает в себя биты четности,

Этап 401: выводят системные биты, на которых выполняют процесс перемежения, в 1-й группе в виртуальный модуль IR буфера; последовательно выводят биты четности, на которых выполняют процесс перемежения, во 2-й группе по W группе в виртуальный модуль IR буфера; и затем выводят 1-го по

Возможен еще один конкретный вариант реализации на этапе 103:

Этап 402: сравнивают

Этап 403: выводят из виртуального модуля IR буфера системные биты, на которых выполняют процесс перемежения, в первой группе; и, начиная с S3-й группы, соответствующей предварительно сконфигурированной третьей начальной позиции, в виртуальном модуле IR буфера, последовательно выводят биты четности, на которых выполняют процесс перемежения, в V группах, и выводят 1-й по

Этап 404: циклически выводят из виртуального модуля IR буфера

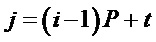

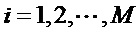

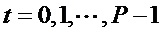

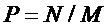

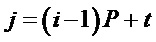

Фиг. 5 представляет собой схему варианта осуществления устройства для согласования скорости для кодирования в соответствии с настоящим изобретением. Как показано на фиг. 5, устройство этого варианта осуществления может включать в себя: модуль 11 деления, модуль 12 перемежения, первый модуль 13 согласования скорости, модуль 14 IR буфера, второй модуль 15 согласования скорости и модуль 16 сбора кодированных битов, где модуль 11 деления выполнен с возможностью разделять кодированные биты, выводимые кодером полярного кода, на M-группы, где

Устройство в этом варианте осуществления может быть выполнено с возможностью реализовать техническое решение в варианте осуществления способа, показанном на фиг. 1. Принципы реализации и технические эффекты этого варианта осуществления и вариант осуществления способа аналогичны, и подробности не описаны здесь снова.

Фиг. 6 является схемой другого варианта осуществления устройства для согласования скорости для кодирования в соответствии с настоящим изобретением. Как показано на фиг. 6, на основании структуры устройства, показанной на фиг. 5, в устройстве в этом варианте осуществления, когда

Возможно, второй модуль 15 согласования скорости включает в себя: блок 151 обработки с битовым уменьшением и блок 152 обработки повторения битов, где блок 151 обработки с битовым уменьшением выполнен с возможностью: когда

Устройство в этом варианте осуществления может быть выполнено с возможностью реализовать техническое решение в варианте осуществления способа, показанном на фиг. 2. Принципы реализации и технические эффекты этого варианта осуществления и вариант осуществления способа аналогичны, и подробности не описаны здесь еще раз.

Дополнительно, в еще одном варианте осуществления настоящего изобретения на основании вышеизложенного варианта осуществления, показанного на фиг. 5, когда

Возможно, второй модуль 15 согласования скорости включает в себя: блок обработки с битовым уменьшением и блок обработки повторения бит, где блок обработки с битовым уменьшением выполнен с возможностью: когда

Устройство в этом варианте осуществления может быть выполнено с возможностью реализовать техническое решение в варианте осуществления способа, показанном на фиг. 3. Принципы реализации и технические эффекты этого варианта осуществления и варианта осуществления способа аналогичны, и подробности не описаны здесь снова.

Дополнительно, в еще одном варианте осуществления настоящего изобретения на основании вышеизложенного варианта осуществления, показанного на фиг. 5, когда 1-я группа включает в себя системные биты, 2-я группа по M-й группу включают в себя биты четности,

Возможно, второй модуль 15 согласования скорости включает в себя: блок обработки с битовым уменьшением и блок обработки повторения бит, где блок обработки с битовым уменьшением выполнен с возможностью: когда

Устройство в этом варианте осуществления может быть выполнено с возможностью реализации технического решения в варианте осуществления способа, показанном на фиг. 4. Принципы реализации и технические эффекты этого варианта осуществления и варианта осуществления способа аналогичны, и подробности не описаны здесь снова.

Специалисты в данной области техники могут понять, что все или некоторые из этапов вариантов осуществления способа могут быть реализованы программой, инструктирующей соответствующее оборудование. Программа может храниться на машиночитаемом носителе данных. Когда программа запускается, выполняются этапы вариантов осуществления способа. Вышеупомянутый носитель данных включает в себя: любой носитель информации, который может хранить программный код, такой как ROM, RAM, магнитный диск или оптический диск.

В заключении, следует отметить, что приведенные выше варианты осуществления предназначены только для описания технических решений в настоящем изобретении, но не для ограничения настоящего изобретения. Хотя настоящее изобретение подробно описано со ссылкой на вышеизложенные варианты осуществления, специалисты в данной области техники должны понимать, что они могут все еще вносить изменения в технические решения, описанные в вышеприведенных вариантах осуществления, или сделать эквивалентную замену некоторым или всем техническим характеристикам, не отступая от объема технических решений в вариантах осуществления настоящего изобретения.

Группа изобретений относится к области кодирования и может быть использована для согласования скорости для кодирования. Техническим результатом является обеспечение эффективного и гибкого согласования скорости, а также повышение эффективности передачи. Способ содержит этапы, на которых: делят кодированные биты, выводимые кодером полярного кода, на M групп, и выполняют процесс перемежения кодированных битов отдельно для групп с 1-ой по M-ую, где M – положительное целое число; выполняют процесс битового уменьшения кодированных битов во множестве групп из

| Способ получения эхограмм внутренних органов человека и устройства для его осуществления | 1986 |

|

SU1482669A1 |

| EP 1538757 A2, 08.06.2005 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| УСТРОЙСТВО И СПОСОБ ДЛЯ ВЫПОЛНЕНИЯ КОДИРОВАНИЯ И СОГЛАСОВАНИЯ СКОРОСТИ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ МДКР | 2002 |

|

RU2233544C2 |

Авторы

Даты

2019-02-12—Публикация

2014-02-20—Подача