Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к области связи и, в частности, к способу и устройству для обработки информации, устройству связи и системе связи.

Уровень техники

В системе беспроводной связи технология гибридного автоматического запроса на повторную передачу (Hybrid Automatic Repeat Request, HARQ) является важной технологией, которая может значительно повысить надежность канала передачи данных.

Код с низкой плотностью проверок на четность (Hybrid Automatic Repeat Request, LDPC) является типом линейного блочного кода, имеющего разреженную проверочную матрицу, и характеризуется гибкой структурой и низкой сложностью декодирования. Поскольку LDPC код использует частично-параллельный итерационный алгоритм декодирования, LDPC код имеет более высокую пропускную способность, чем обычный турбокод. LDPC код может быть использован в качестве кода с исправлением ошибок следующего поколения для систем связи и может быть использован для повышения надежности передачи канала и использования мощности; и могут широко применяться для космической связи, оптоволоконной связи, систем персональной связи, ADSLs, магнитных записывающих устройств и тому подобного. В настоящее время в мобильной связи 5-го поколения схему LDPC кода рассматривают в качестве одной из схем канального кодирования.

Для поддержки различных длин кода и скоростей кодирования, устройство связи выполняет согласование скорости после канального кодирования с целью корректировки скорости кодирования кодированного блока, и получает последовательность битов, которая должна быть отправлена, чтобы соответствовать скорости декодирования кода. Во время согласования скорости устройство связи может дополнительно выполнять выкалывание битов в LDPC кодированных блоках, сгенерированных после кодирования, чтобы увеличить кодовую скорость; или выполнить повторение битов в LDPC кодированных блоках, сгенерированных после кодирования, для снижения скорости кода.

В процессе согласования скорости устройство связи на стороне передачи выбирает последовательность битов, которая должна быть отправлена, выполняет обработку, такую как перемежение и отображение в последовательности битов, и отправляет обработанную последовательность битов в устройство связи на стороне приема. Устройство связи на стороне приема выполняет объединение и декодирование мягких значений последовательности битов и сохраненных мягких канальных битов (мягкий канальный бит) при декодировании для получения кодированного блока.

В предшествующем уровне техники, когда устройство связи на стороне передачи использует существующий способ согласования скорости, производительность HARQ является относительно низкой.

Сущность изобретения

Варианты осуществления настоящего изобретения предоставляют способ и устройство для обработки информации, устройство связи и систему связи для повышения HARQ производительности.

Согласно первому аспекту предоставлен способ обработки информации в системе связи. Способ включает в себя:

получение начальной позиции k0 (i) выходной последовательности битов в кодированном блоке; и

определение выходной последовательности битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i), где кодированный блок хранят в кольцевом буфере, и i является целым числом, большим или равно 0.

Согласно второму аспекту предоставлен способ обработки информации в системе связи. Способ включает в себя:

получение начальной позиции k0 (i) последовательности мягких битов, имеющей длину E (i), сохраненную в мягком буфере; и

объединение и сохранение последовательности мягких битов в мягком буфере, начиная с начальной позиции k0 (i).

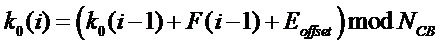

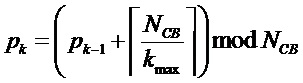

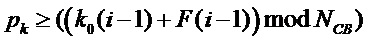

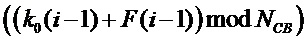

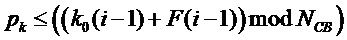

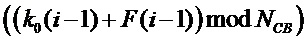

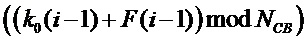

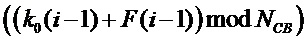

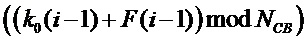

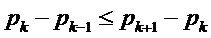

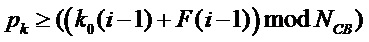

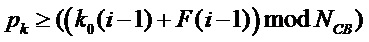

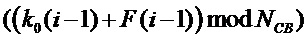

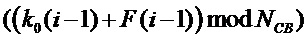

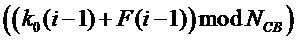

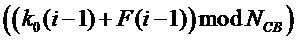

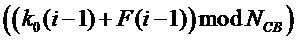

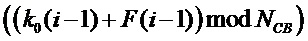

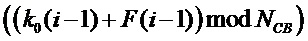

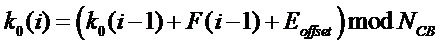

В возможной реализации первого аспекта или второго аспекта, для конкретной повторной передачи, для i> 0, k0 (i) определяют на основании начальной позиции k0 (i-1) предшествующей выходной последовательности битов передачи и длины E (i-1) предшествующей выходной последовательности битов передачи. k0 (i) = (k0 (i - 1) + F (i - 1)) mod NCB. NCB является размером кодированного блока, и F (i - 1) является количеством битов, необходимым для последовательного получения E (i - 1) выходных битов из кодированного блока, начиная с k0 (i - 1).

В этой реализации выходные последовательности битов двух смежных передач являются последовательными, и между двумя выходными последовательностями битов отсутствуют повторные биты, так что, когда такие выходные последовательности битов отправляют устройству связи на стороне приема, может быть достигнута относительно хорошая производительность декодирования.

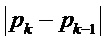

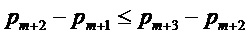

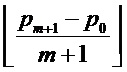

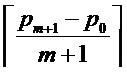

В возможной реализации, основанной на предшествующей реализации, если бит передают на конечной позиции в кодированном блоке,

В этой реализации после того, как все биты переданы, количество повторяющихся битов уменьшается тем самым уменьшая потерю производительности декодирования.

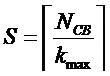

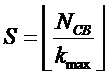

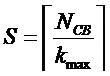

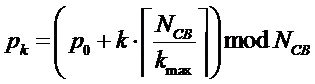

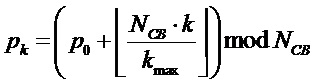

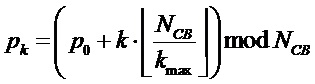

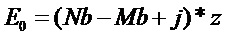

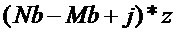

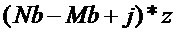

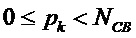

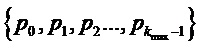

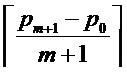

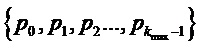

В другой возможной реализации первого аспекта или второго аспекта значение k0 (i) является

Например,

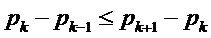

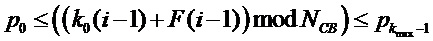

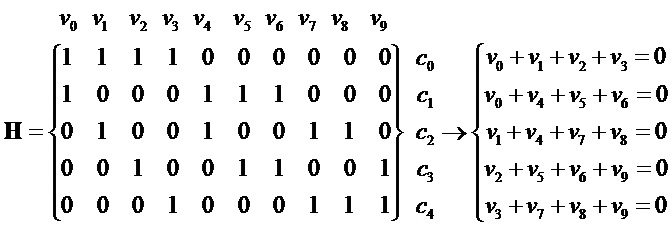

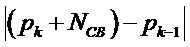

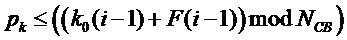

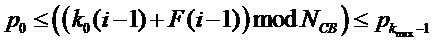

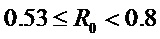

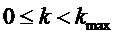

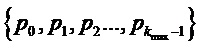

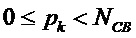

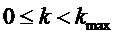

В другой возможной реализации, основанной на первом аспекте или втором аспекте или вышеизложенной реализации, если

Используя

В примере, в котором S = z и z является размером поднятия кодированного блока,

Вышеизложенный способ может быть адаптирован к различным начальным скоростям кодов передачи, так что интервал между передачами версии с избыточностью не сильно изменяется или не включает в себя большое количество повторных битов, тем самым, достигая относительно стабильной производительности.

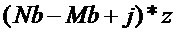

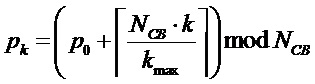

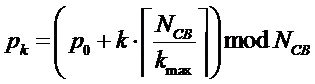

В другой возможной реализации первого аспекта или второго аспекта значение k0 (i) является

Например,

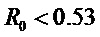

Если

Если

Согласно способу, начальные позиции более плотно распределены на позициях, более близких к информационным битам, и начальные позиции более разреженно распределены на позициях, более близких к последнему биту кодированного блока.

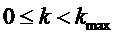

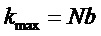

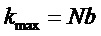

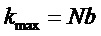

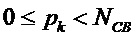

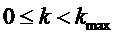

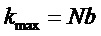

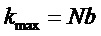

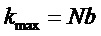

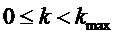

В вышеприведенных реализациях kmax может быть целым числом больше 4. Например, kmax = 5; или

В другой возможной реализации, основанной на любой из вышеприведенных реализаций, для повторной конкретной передачи для i> 0, начальную позицию k0 (i) определяют на основании начальной позиции k0(i-1) предшествующей выходной последовательности битов передачи и длины E (i-1) предшествующей выходной последовательности битов передачи.

В возможной реализации, с целью уменьшения количества повторяющихся избыточных битов,

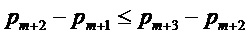

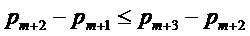

В другой возможной реализации, для удовлетворения требования последовательного декодирования,

В другой возможной реализации, чтобы компенсировать потери производительности декодирования, вызванные повторяющимися битами и пропуском избыточных битов, если

В другой возможной реализации для компенсации потерь производительности декодирования, вызванных повторяющимися битами и пропуском избыточных битов, начальную позицию k0 (i) определяют на основании начальной позиции k0(i-1) предшествующей выходной последовательности битов передачи, длины E(i-1) предшествующей выходной последовательности битов передачи и количества i передач.

В вышеприведенных реализациях F(i-1) является количеством битов, требуемым для последовательного получения E(i-1) выходных битов из кодированного блока, начиная с k0(i-1).

В другой возможной реализации, основанной на любой из вышеупомянутых реализаций, начальную позицию k0 (i) определяют на основании номера rvidx (i) начальной позиции версии с избыточностью.

Например, для адаптивной повторной передачи номер rvidx (i) версии с избыточностью может быть получен посредством сигнализации.

В другом примере, для адаптивной повторной передачи или неадаптивной повторной передачи номер rvidx (i) начальной позиции версии с избыточностью может быть получен на основании последовательности номеров начальной позиции версии с избыточностью и количества i передач.

Последовательность номеров начальных позиций версии с избыточностью извлекают из памяти, или последовательность нумерации начальных позиций версии с избыточностью определяют на основании начальной кодовой скорости передачи, или определяют последовательность номеров начальных позиций версии с избыточностью на основании длины выходной последовательности битов и размера z поднятия.

Согласно третьему аспекту предоставляют устройство для обработки информации в системе связи. Устройство включает в себя:

блок получения, выполненный с возможностью получать начальную позицию k0 (i) выходной последовательности битов в кодированном блоке; и

блок обработки, выполненный с возможностью определять выходную последовательность битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i), где кодированный блок хранят в кольцевом буфере, и i является целым числом больше или равно 0.

Устройство может быть выполнено с возможностью выполнять способ в соответствии с первым аспектом или любой возможной реализацией первого аспекта. Подробное описание приведено в вышеизложенном аспекте.

В возможной реализации устройство для обработки информации в соответствии с настоящим изобретением может включать в себя модуль, соответственно выполненный с возможностью выполнять первый аспект или любую возможную реализацию первого аспекта в вышеупомянутой структуре способа. Модуль может быть программным и/или аппаратным.

Согласно четвертому аспекту предоставлено устройство для обработки информации в системе связи. Устройство включает в себя:

блок получения, выполненный с возможностью получать начальную позицию k0 (i) последовательности мягких битов, имеющей длину E (i), сохраненной в мягком буфере; и

блок обработки, выполненный с возможностью объединять и сохранять полученную последовательность мягких битов в мягком буфере, начиная с начальной позиции k0 (i).

Устройство может быть выполнено с возможностью выполнять способ согласно второму аспекту или любой возможной реализации второго аспекта. Подробное описание приведено в вышеизложенном аспекте.

В возможной реализации устройство для обработки информации в соответствии с настоящим изобретением может включать в себя модуль, соответственно выполненный с возможностью выполнять второй аспект или любую возможную реализацию второго аспекта в вышеупомянутой структуре способа. Модуль может быть программным и/или аппаратным.

В соответствии с пятым аспектом предоставлено устройство связи. Устройство связи включает в себя кодер, устройство согласования скорости и приемопередатчик.

Кодер выполнен с возможностью кодировать информационные данные.

Устройство согласования скорости включает в себя устройство для обработки информации в соответствии с третьим аспектом и выполнено с возможностью определять выходную последовательность битов в вышеизложенных вариантах осуществления.

Приемопередатчик выполнен с возможностью отправлять сигнал, соответствующий выходной последовательности битов из устройства согласования скорости.

Согласно шестому аспекту предоставлено устройство связи. Устройство связи включает в себя декодер, устройство де-согласования скорости и приемопередатчик.

Приемопередатчик выполнен с возможностью принимать сигнал, соответствующий последовательности мягких битов выходной последовательности битов в вышеприведенном аспекте.

Декодер выполнен с возможностью декодировать мягкие канальные биты в мягком буфере.

Устройство де-согласования скорости включает в себя устройство для обработки информации в соответствии с четвертым аспектом и выполнено с возможностью объединять и сохранять мягкие канальные биты выходной последовательности битов в вышеупомянутом аспекте в мягком буфере.

В соответствии с седьмым аспектом вариант осуществления настоящего изобретения предоставляет систему связи. Система включает в себя устройство связи согласно пятому аспекту и устройство связи согласно шестому аспекту.

Согласно другому аспекту, вариант осуществления настоящего изобретения предоставляет компьютерный носитель данных, включающий в себя программу, предназначенную для выполнения вышеупомянутых аспектов.

Согласно еще одному аспекту настоящего изобретения предоставляют компьютерный программный продукт, включающий в себя инструкции. При выполнении компьютерного программного продукта на компьютере, побуждают компьютер выполнять способы в соответствии с вышеизложенными аспектами.

Согласно способу и устройству для обработки информации, устройству связи и системе связи в вариантах осуществления настоящего изобретения надлежащим образом определяют выходную последовательность битов для начальной передачи или повторной передачи, таким образом повышают производительность декодирования устройства связи на приемной стороне после приема последовательности мягких битов выходной последовательности битов, повышают интенсивность успешных попыток декодирования и дополнительно сокращают количество повторных передач.

Краткое описание чертежей

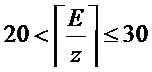

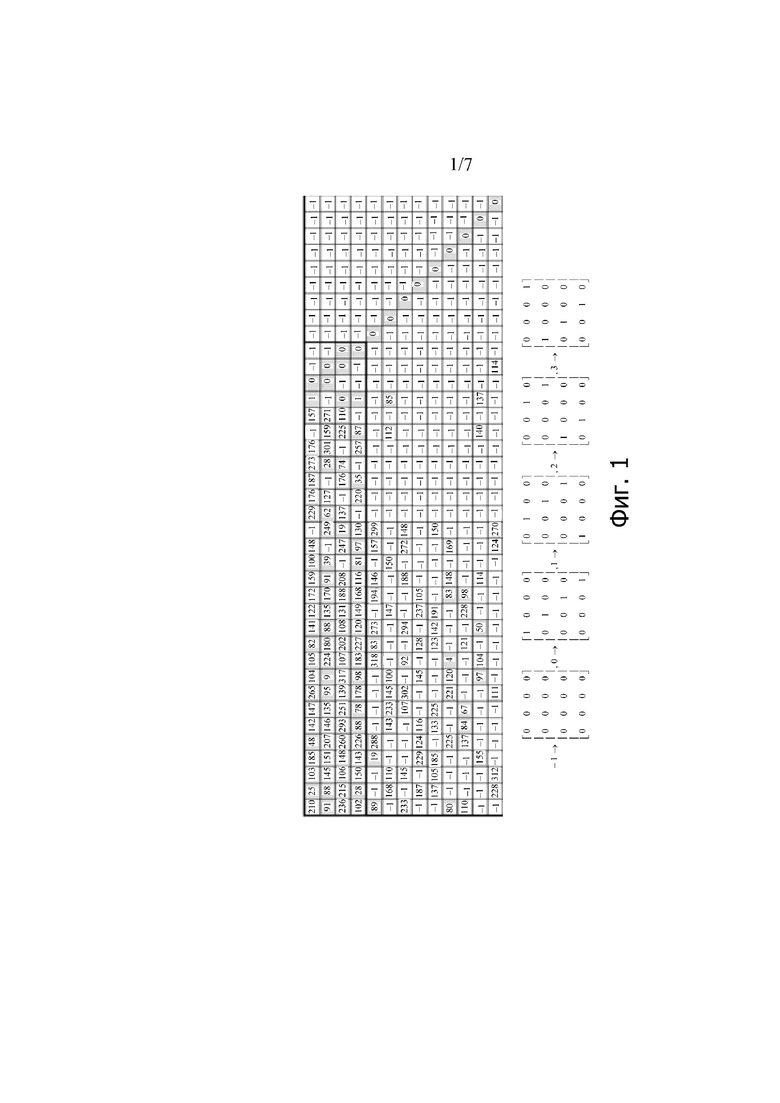

Фиг. 1 является принципиальной схемой базовой матрицы LDPC кода и матриц перестановок;

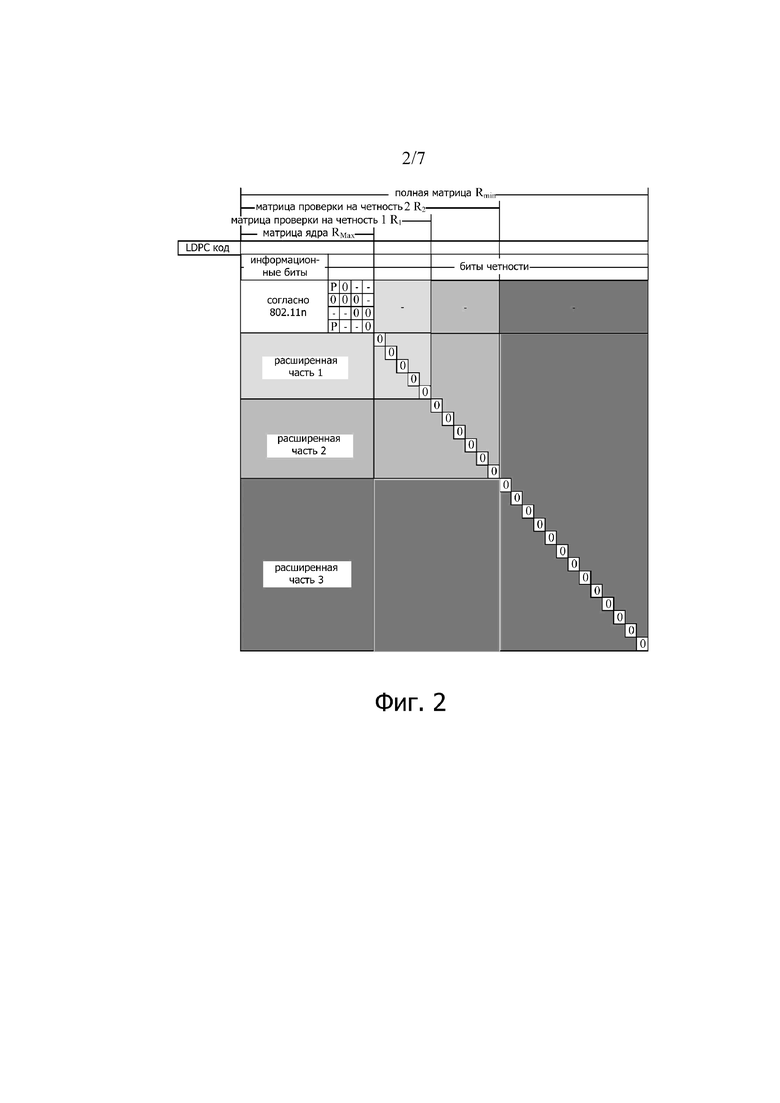

Фиг. 2 является схемой матрицы проверки на четность LDPC кода;

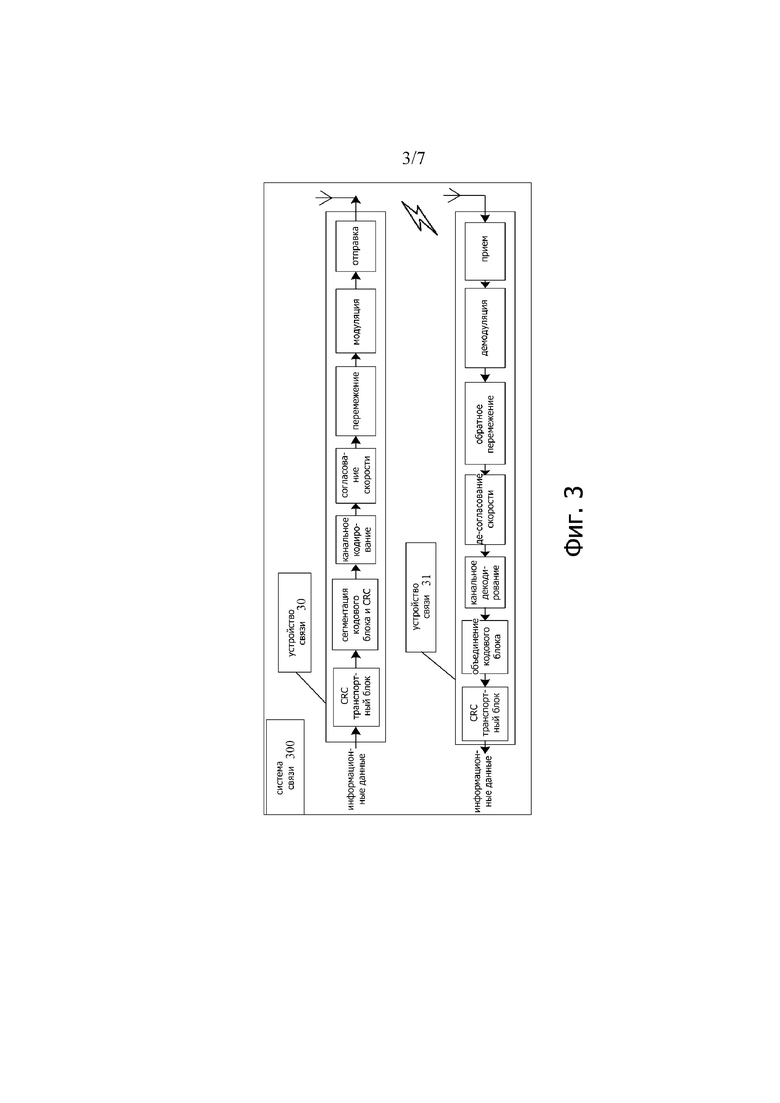

Фиг. 3 является схемой системы связи в соответствии с вариантом осуществления настоящего изобретения;

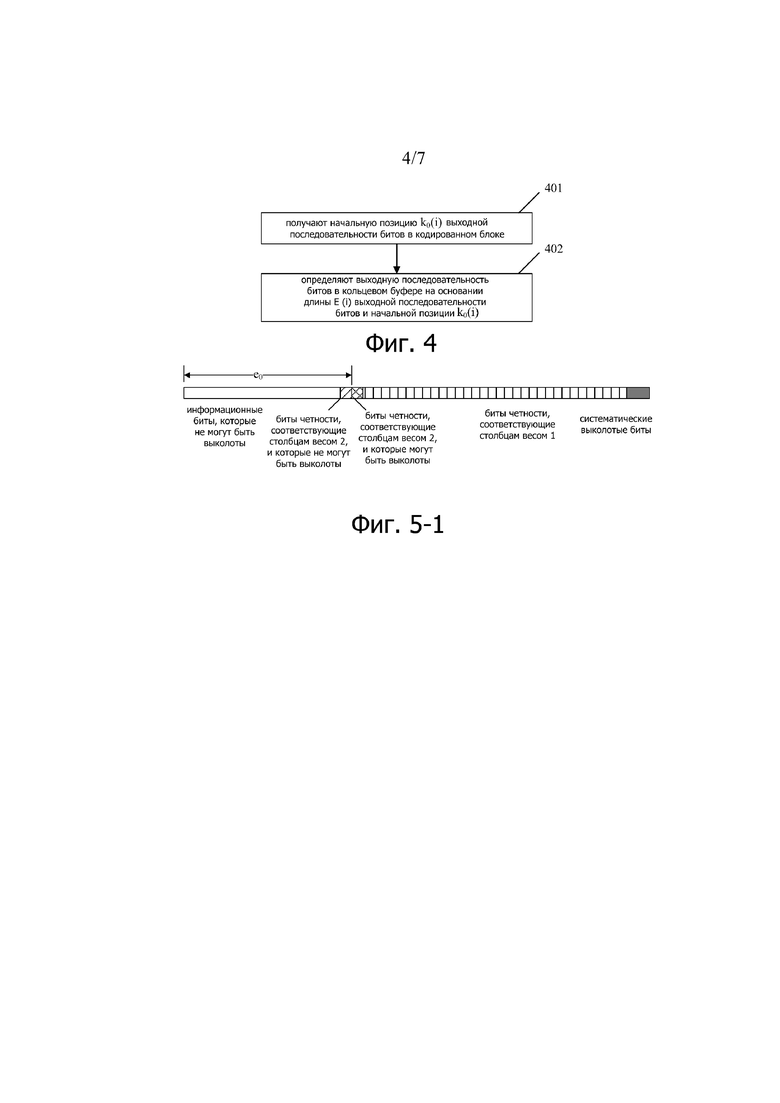

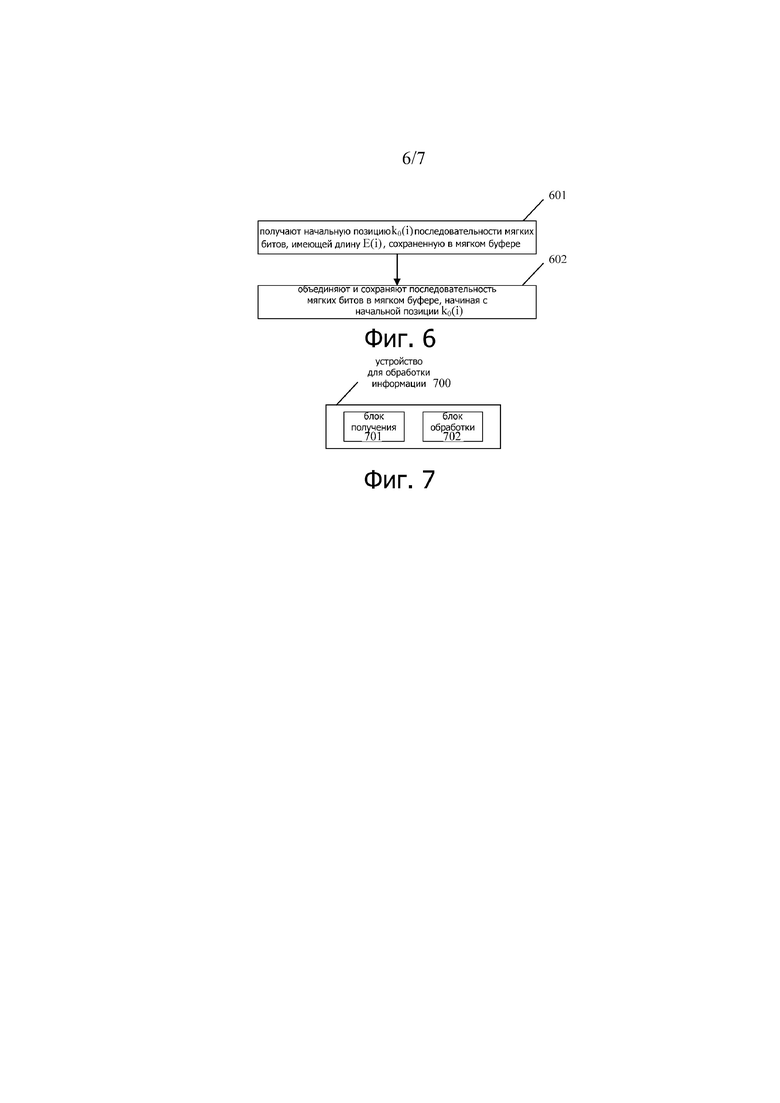

Фиг.4 является блок-схемой последовательности операций способа обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

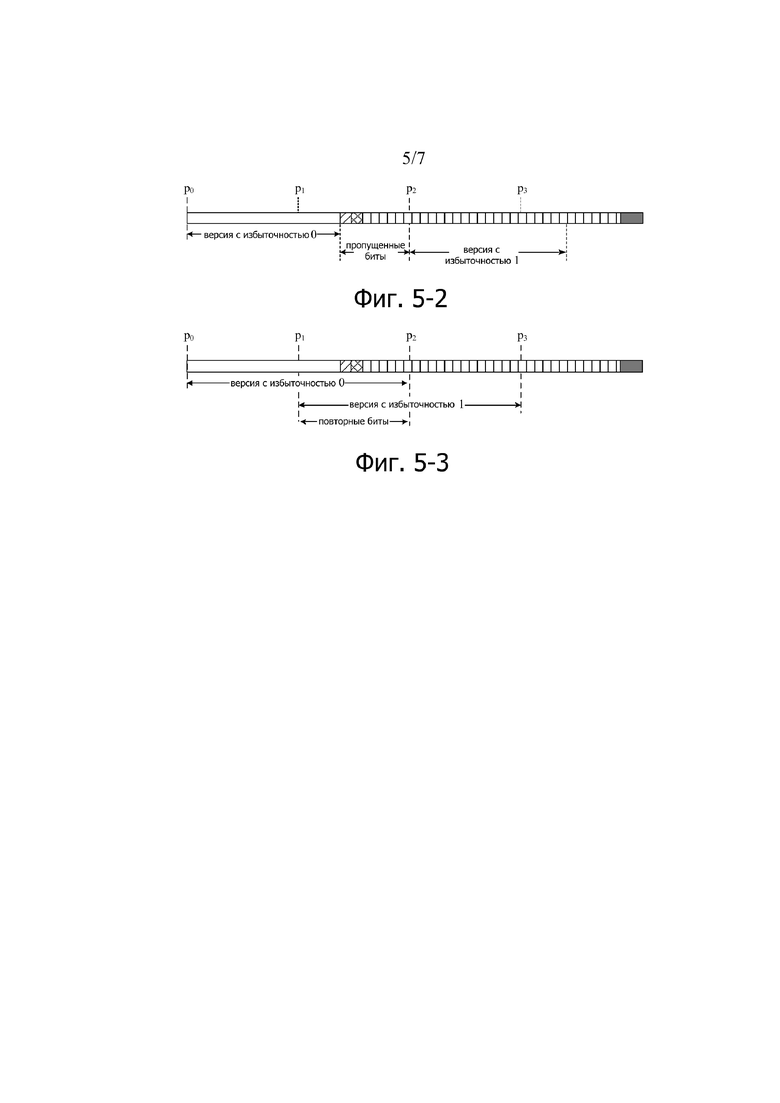

Фиг. 5-1 является схемой кодированного блока согласно другому варианту осуществления настоящего изобретения;

Фиг. 5-2 является схемой кодированного блока согласно другому варианту осуществления настоящего изобретения;

Фиг. 5-3 является схемой кодированного блока согласно другому варианту осуществления настоящего изобретения;

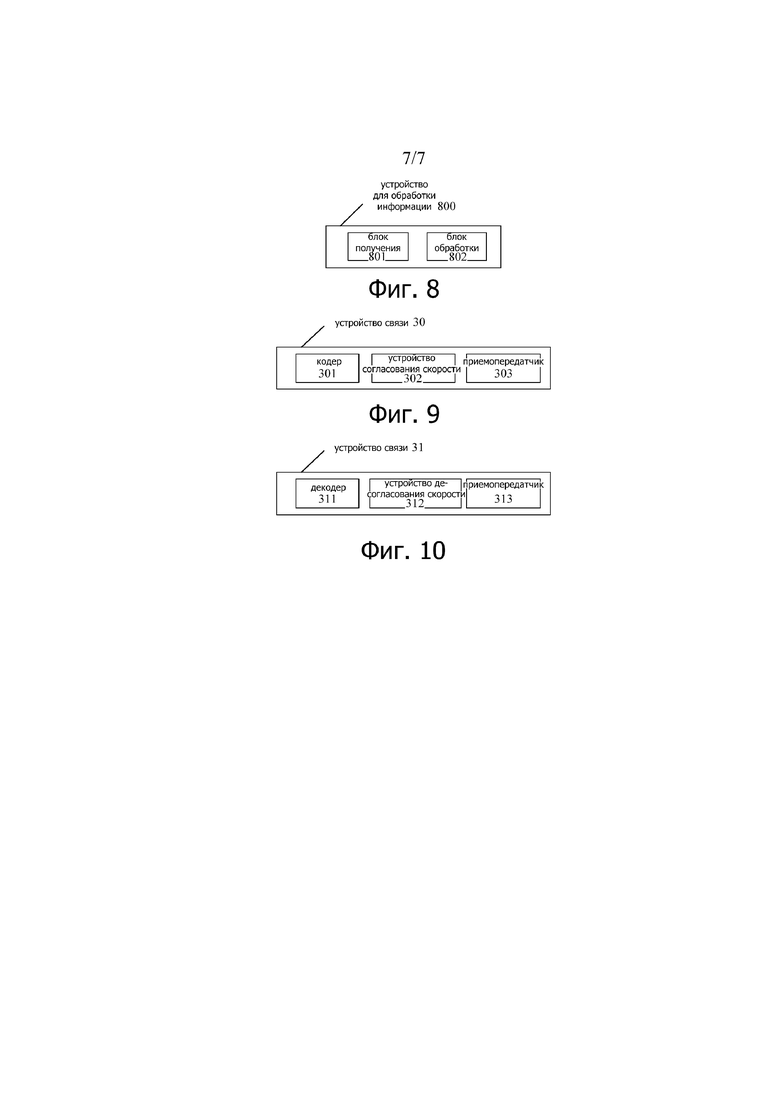

Фиг.6 является блок-схемой последовательности операций способа обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

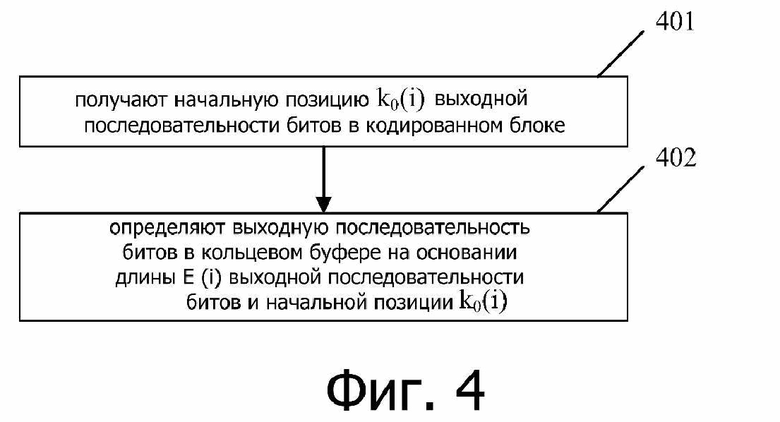

Фиг.7 является схемой устройства для обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг.8 является схемой устройства для обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

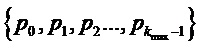

Фиг. 9 является схемой устройства связи в соответствии с другим вариантом осуществления настоящего изобретения; и

Фиг.10 является схемой устройства связи в соответствии с другим вариантом осуществления настоящего изобретения.

Описание вариантов осуществления

Далее приведено описание технических решений в вариантах осуществления настоящего изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления настоящего изобретения.

Фиг. 1 является схемой базовой матрицы LDPC кода в системе связи и матриц перестановок. Базовая матрица LDPC кода включает в себя mн * nн элементов, в которой mн является количеством строк и nн является количеством столбцов базовой матрицы. Если базовую матрицу поднимают с использованием z в качестве размера поднятия, может быть получена (mн * z) * (nн * z) матрица H поверки на четность. Чтобы быть конкретным, матрица Н проверки на четность включает в себя mн * nн блоков. Каждый блок получают путем выполнения циклического сдвига на единичной матрице размером z * z. Размер z поднятия обычно определяют на основании размера кодового блока, поддерживаемого системой, и объема информационных данных. Фиг. 1 показывает базовую матрицу, имеющую QC структуру LDPC кода, где mн = 13 и nн = 38. Скорость кодирования базовой матрицы составляет (nн - mн)/ nн = 0,6579. Если размер z = 4 поднятия, то каждый элемент, значение которого в матрице равно -1, поднимают до нулевой матрицы размером 4*4 и другие элементы поднимают до матриц перестановок размера 4*4. Матрица перестановок может быть получена путем выполнения циклического сдвига на единичной матрице I для соответствующего количества раз, и количество сдвигов равно значению соответствующего матричного элемента. Как показано на фиг. 1 соответствующая матрица перестановок, полученная после того, как элемент, значение которого равно 0 в базовой матрице, поднята, является единичной матрицей I размера 4*4, соответствующей матрице перестановок, полученной после того, как элемент, значение которой равно 1, поднят, является матрицей, полученной посредством сдвига единичной матрицы один раз и так далее. Повторное подробное описание опущено.

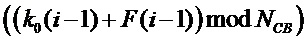

После поднятия базовая матрица может быть использована в качестве матрицы проверки на четность, используемой для кодирования или декодирования LDPC кода. LDPC код, имеющий длину nн кода и длину kс информационной последовательности, обозначен как (nн, kс) LDPC код и может быть однозначно определен матрицей Н проверки на четность. Матрица Н проверки на четность является разреженной матрицей, где каждая строка из проверочной матрицы H представляет собой одно ограничение уравнения проверки на четность и соответствует j кодированным битам, каждый столбец представляет один кодированный бит, ограниченный mн уравнениями проверки на четность, и любые два уравнения проверки на четность включают в себя не более одного одинакового кодированного бита. Пример матрицы H контроля четности LDPC кода и соответствующего уравнения проверки на четность приведен в следующей формуле (1):

Фиг. 2 показывает пример матрицы H проверки на четность LDPC кода. Как показано на фиг. 2, матрица проверки на четность включает в себя матрицы ядра и три расширенные части матрицы. Информационные данные могут быть закодированы и декодированы с использованием четырех матриц проверки на четность: матрицы ядра; матрицы 1 проверки на четность, включающую в себя матрицу ядра и расширенную часть 1 матрицы; матрицы 2 проверки на четность, включающую в себя матрицу ядра, расширенную часть 1 матрицы и расширенную часть 2 матрицы; полной матрицы, включающую в себя матрицу ядра, расширенную часть 1 матрицы, расширенную часть 2 матрицы и расширенную часть 3 матрицы. Каждая из матриц проверки на четность имеет Raptor-подобную структуру. Часть, соответствующая битам четности, имеет двойную структуру, а именно, двух диагональную структуру и структуру столбца с весом 1. Матрица ядра обычно включает в себя двух диагональную часть структуры. Если количество информационных битов перед кодированием равно k и длина LDPC кода кодированного блока, сгенерированного на основании матрицы проверки на четность, равна n, то скорость кода равна kc/nн. LDPC кодированные блоки, имеющие разные кодовые скорости, могут быть получены с использованием разных матриц проверки на четность для кодирования. Очевидно, что в кодированных блоках LDPC кодовое слово, сгенерированное на основании полной матрицы, имеет наибольшую длину кода и самую низкую кодовую скорость

В системе связи передача информационных данных между устройствами связи (например, базовыми станциями или терминалами) подвержена помехам и ошибкам, поскольку среда распространения радиоволн является сложной и изменчивой. Для надежной отправки информационных данных устройство связи на передающей стороне выполняет обработку, такую как CRC подключение, канальное кодирование, согласование скорости и перемежение информационных данных, отображает перемеженные кодированные биты на символы модуляции и отправляет символы модуляции в устройство связи на принимающей стороне. После приема символов модуляции устройство приема соответственно выполняет обратное перемежение, де-согласование скорости, декодирование и CRC для восстановления информационных данных. Эти процессы могут уменьшить ошибки передачи и повысить надежность передачи данных.

Система 300 связи, показанная на фиг. 3, может широко быть применима для различных типов связи, таких как речевая связь и передача данных. Система связи может включать в себя множество устройств беспроводной связи. Для ясности, фиг. 3 показывает только устройство 30 связи и устройство 31 связи. Управляющая информация или информация данных отправляются и принимаются как информационная последовательность между устройством 30 связи и устройством 31 связи. Устройство 30 связи служит в качестве устройства связи на передающей стороне, чтобы отправить информационную последовательность в транспортных блоках (блок передачи, TB) и присоединить CRC биты к каждому транспортному блоку. Если размер транспортного блока с присоединением CRC превышает наибольшую длину кодового блока, транспортный блок должен быть сегментирован на несколько кодовых блоков (кодовый блок, CB). CRC биты кодового блока также могут быть присоединены к каждому кодовому блоку или CRC биты группы кодовых блоков могут быть присоединены к каждой группе кодовых блоков, и биты заполнители могут быть дополнительно вставлены в каждый кодовый блок. Устройство 30 связи выполняет канальное кодирование для каждого кодового блока, например, выполняет LDPC кодирование для получения соответствующего кодированного блока. Каждый кодированный блок включает в себя информационные биты и биты четности. Если информационные биты включают в себя бит заполнитель, бит заполнитель обычно выражен как «ноль» (Null).

Кодированный блок или кодированный блок, для которого была выполнена перестановка битов, сохраняется в кольцевом буфере устройства 30 связи, и устройство 30 связи последовательно получает множество выходных битов из кодированного блока, хранящегося в кольцевом буфере, чтобы получить выходную последовательность битов. Выходной бит является битом, отличным от бита заполнителя в кодированном блоке, и поэтому выходная последовательность битов не включает в себя никакого бита заполнителя. Выходную последовательность битов отправляют после перемежения и отображения на символы модуляции. При выполнении повторной передачи устройство 30 связи выбирает другую выходную последовательность битов из кодированного блока в кольцевом буфере и отправляет другую выходную последовательность битов. Если получение выходных битов последовательно достигает последнего бита циклического буфера, выбор выходного бита продолжается, начиная с начального бита циклического буфера.

После демодуляции и обратного перемежения принятых символов модуляции устройство 31 связи сохраняет мягкие значения принятой выходной последовательности битов в соответствующей позиции в мягком буфере (soft buffer). Если происходят повторные передачи, устройство 31 связи объединяет мягкие значения выходных последовательностей битов во всех повторных передачах и сохраняет объединенные мягкие значения в мягком буфере. Объединение означает, что, если позиции выходных битов, принятых в двух передачах, являются одинаковыми, мягкие значения выходных битов, принятых в двух передачах, объединяются. Позиции в программном буфере устройства 31 связи находятся во взаимно-однозначном соответствии с позициями в кодированном блоке в кольцевом буфере устройства 30 связи. Конкретно, если позиция выходного бита в кодированном блоке в кольцевом буфере устройства 30 связи установлен p-й бит, позиция мягкого значения выходного бита в программном буфере устройства 31 связи также является p-м битом.

Устройство 31 связи декодирует все мягкие значения в мягком буфере, чтобы получить кодовый блок информационной последовательности. Устройство 31 связи может получить размер транспортного блока. Следовательно, может быть определено количество кодовых блоков, на которые сегментируют один транспортный блок, и длина каждого кодового блока. Если кодовый блок включает в себя CRC битовый сегмент, устройство 31 связи может дополнительно использовать CRC битовый сегмент для проверки кодового блока. Устройство 31 связи объединяет все кодовые блоки в один транспортный блок и дополнительно выполняет проверку и объединение транспортных блоков для окончательного получения информационной последовательности. Можно узнать, что устройство 31 связи выполняет процесс, обратный способу обработки информации, выполняемому устройством 30 связи.

Следует отметить, что в вариантах осуществления настоящего изобретения устройство 30 связи может быть сетевым устройством, таким как базовая станция в системе связи и, соответственно, устройство 31 связи может быть терминалом. Альтернативно, устройство 30 связи может быть терминалом в системе связи и, соответственно, устройство 31 связи может быть сетевым устройством, таким как базовая станция в системе связи.

Для простоты понимания некоторые термины, используемые в данном описании, описаны ниже.

В настоящем описании термины «сеть» и «система» часто используются попеременно, но специалист в данной области техники может понять их значения. Терминал является устройством, имеющим функцию связи, и может включать в себя портативное устройство, имеющее функцию беспроводной связи, автомобильное устройство, носимое устройство, вычислительное устройство или другое устройство обработки, подключенное к беспроводному модему. Терминал может иметь разные названия в разных сетях, например, устройство пользователя, мобильная станция, абонентское устройство, станция, сотовый телефон, персональный цифровой помощник, беспроводной модем, устройство беспроводной связи, портативное устройство, портативный компьютер, беспроводный телефон или беспроводная локальная абонентская станция. Для простоты описания в настоящем изобретении терминальное устройство кратко упоминается как терминал. Базовая станция (базовая станция, BS) также может называться устройством базовой станции и представляет собой устройство, развернутое в сети радиодоступа для обеспечения функции беспроводной связи. В разных системах беспроводного доступа базовая станция может иметь разные названия. Например, базовая станция в сети универсальной системы мобильной связи (Universal Mobile Telecommunications System, UMTS) упоминается как NodeB (NodeB), базовая станция в LTE сети упоминается как развитый NodeB (развитый NodeB, eNB). или eNodeB), базовая станция в сети нового радио (новое радио, NR) упоминается как точка приема передачи (точка приема передачи, TRP) или NodeB следующего поколения (NodeB поколения, gNB) или базовые станции в различных других развитых сетях могут также иметь другие названия. Настоящее изобретение этим не ограничено.

Фиг.4 является блок-схемой последовательности операций способа обработки информации в соответствии с вариантом осуществления настоящего изобретения. Способ может быть применен к системе связи. Система связи включает в себя устройство 30 связи и устройство 31 связи. Способ может быть реализован устройством 30 связи и включает в себя следующие этапы.

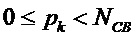

401: получают начальную позицию k0 (i) выходной последовательности битов в кодированном блоке.

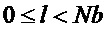

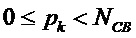

В устройстве 30 связи кодированный блок сохраняют в кольцевом буфере. Размер кодированного блока может быть представлен NCB. Кодированный блок также может включать в себя один или несколько битов заполнителей. Когда кодированный блок изначально является передачей или повторной передачей, устройство 30 связи определяет в кодированном блоке в кольцевом буфере выходную последовательность битов, используемую для начальной передачи или повторной передачи. Выходная последовательность битов не включает в себя бит заполнитель. Для простоты описания, i-я передача указывает начальную передачу или повторную передачу, i=0 обозначает начальную передачу, i>0 обозначает повторную передачу, и i является целым числом. Например, i=1 обозначает первую повторную передачу, i=2 указывает вторую повторную передачу и так далее. Верхний предел повторных передач зависит от максимального времени повторной передачи системы. Выходная последовательность битов для каждой начальной передачи или повторной передачи может быть версией с избыточностью кодированного блока. k0 (i) указывает начальную позицию выходной последовательности битов для i-й передачи в кодированном блоке кольцевого буфера, что также может упоминаться как начальная позиция версии rv (i) с избыточностью для i-й повторной передачи.

402: определяют выходную последовательность битов в кольцевом буфере на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i).

Устройство 30 связи может определять выходную последовательность битов на основании длины E (i) выходной последовательности битов для i-й передачи и начальной позиции k0 (i), полученных на этапе 401. Например, устройство 30 связи последовательно получает E (i) биты, начиная с (k0 (i))-го бита кодированного блока, в качестве выходной последовательности битов. Выходная последовательность битов не включает в себя бит заполнитель; поэтому, если устройство 30 связи получает в качестве выходной последовательности битов E (i) битов в F (i) битах, начиная с (k0 (i))-го бита кодированного блока, количество битов заполнителей равно F(i)-E(i). Следовательно, конечным местоположением выходной последовательности битов является k0 (i) + F (i). F (i) является количеством битов, необходимое для последовательного получения выходных битов E (i) из кодированного блока, начиная с k0 (i). F (i) является целым числом, большее или равное 0.

Например, после отправки выходной последовательности битов для начальной передачи, а именно, 0-й передачи, устройство 30 связи принимает отрицательное подтверждение NACK из устройства 31 связи. Устройство 30 связи должно определить начальную позицию k0 (1) выходной последовательности битов для 1-й передачи, а именно, 1-й версии rv (1) с избыточностью. Следовательно, устройство связи получает начальную позицию k0 (1) выходной последовательности битов в кодированном блоке, сохраненном в кольцевом буфере, и определяет выходную последовательность битов для 1-й передачи, а именно, версию rv (1) с избыточностью, на основании длины E (1) выходной последовательности битов и начальной позиции k0 (1). Устройство 30 связи отправляет выходную последовательность rv (1) битов в устройство 31 связи. Если устройство 30 связи принимает NACK из устройства 31 связи, устройству 30 связи необходимо определить начальную позицию k0 (2) выходной последовательности битов для 2-й передачи, а именно, 2-ю версию rv (2) с избыточностью, и определяют выходную последовательность битов для 2-й передачи на основании длины E (2) выходной последовательности битов и начальной позиции k0 (2), то есть, определяют версию rv (2) с избыточностью. Остальное можно вывести по аналогии. Устройство связи может завершить повторную передачу кодированного блока при достижении максимального количества повторных передач, или в случае, если устройство 30 связи примет ACK положительного подтверждения из устройства 31 связи. Конечно, устройство 30 связи может выполнить множество повторных передач без учета NACK или ACK из устройства связи 31.

Во время декодирования устройству 31 связи на приемной стороне необходимо выполнить объединение и декодирование мягких канальных битов, принятых в начальной передаче, и мягких канальных битов версий с избыточностью. Для кодированного блока, полученного посредством LDPC кодирования, количество повторных битов или пропущенных битов между версиями с избыточностью должно быть уменьшено для повышения производительности декодирования устройства связи на приемной стороне.

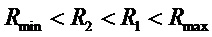

LDPC кодированный блок, показанный на фиг. 5-1, используют в качестве примера. Предполагают, что кодовая скорость матрицы ядра LDPC кодированного блока до выкалывания составляет 0,89, а самая низкая кодовая скорость, поддерживаемая LDPC кодированным блоком, составляет 0,33. LDPC кодированный блок включает в себя информационные биты и биты избыточности. Информационные биты включают в себя систематические выколотые биты и информационные биты, которые не могут быть выколоты. Биты избыточности включают в себя биты четности, которые соответствуют столбцам веса 2 и которые не могут быть выколоты, биты четности, которые соответствуют столбцам веса 2 и которые могут быть выколоты, и биты четности, которые соответствуют столбцам веса 1 и которые могут быть выколоты. Выкалывание также может указывать на отсутствие отправки. Выколотый бит является битом неподлежащим отправке и бит, который не может быть выколот, означает, что бит должен быть отправлен. Биты четности, соответствующие столбцам с весом 2, соответствуют столбцу в части двух диагональной структуры в матрице проверки на четность, или, другими словами, соответствуют столбцу в части двух диагональной структуры в матрице ядра. Выходная последовательность e0 битов, включающая в себя информационные биты, которые не выкалывают, и биты четности, которые соответствуют столбцам с весом 2 и которые не выкалывают, имеет самую высокую кодовую скорость.

Применяют множество размеров, влияющие на производительность декодирования LDPC кода. Например, во время декодирования LDPC кода часть с избыточностью, отличную от информационных битов, обычно выбирают в порядке кодирования для формирования кодового слова для декодирования. В другом примере, для LDPC кода биты четности, соответствующие столбцам веса 2, выкалывают для получения кодовой скорости, превышающей исходную кодовую скорость, поддерживаемую матрицей ядра. Во время повторной передачи выколотые биты четности, соответствующие столбцам веса 2, должны быть сначала повторно переданы, и затем отправляют выколотые биты четности в части столбца веса 1. В другом примере, во время повторной передачи более высокая пропорция повторяющихся битов с избыточностью указывает на более низкую производительность декодирования.

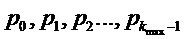

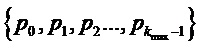

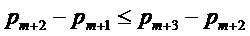

Как показано на фиг. 5-2, есть четыре значения p0, p1, p2 и p3 начальной позиции. При начальной передаче выходная последовательность битов, а именно, версию 0 с избыточностью, получают, начиная с 0-й начальной позиции p0. В 1-й повторной передаче выходную последовательность битов, а именно, версию 1 с избыточностью, получают, начиная со 1-й начальной позиции p1. Версия 0 с избыточностью и версия 1 с избыточностью не являются непрерывными. Большое количество пропущенных битов не передается, и особенно не выбирают биты четности, соответствующие столбцам веса 2. После приема двух версий с избыточностью устройство связи на приемной стороне выполняет объединение и декодирование. Однако, поскольку избыточные биты, пропущенные на фиг. 5-2, не передают в устройство связи на приемной стороне, избыточные биты не могут быть предварительно выбраны до избыточных битов в версии 1 с избыточностью, чтобы сформировать кодовое слово для декодирования. Следовательно, производительность декодирования значительно снижается. Кроме того, пропущенные биты на фиг. 5-2 также включают в себя выколотые биты четности, соответствующие столбцам с весом 2, что дополнительно ухудшает производительность декодирования.

Как показано на фиг. 5-3, при начальной передаче получают выходную последовательность битов, а именно, версию 0 с избыточностью, начиная с 0-й начальной позиции p0. В 1-й повторной передаче выходная последовательность битов, а именно, получают версию 1 с избыточностью, начиная с 1-й начальной позиции p1. Хотя версия 0 с избыточностью и версия 1 с избыточностью являются непрерывными, если кодовая скорость начальной передачи относительно низкая, существует относительно большое количество повторяющихся битов, что приводит к потере производительности декодирования.

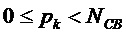

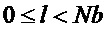

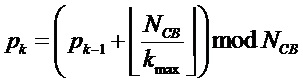

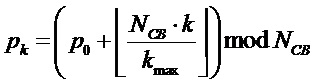

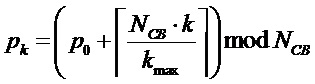

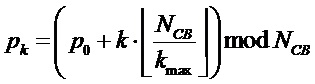

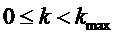

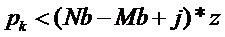

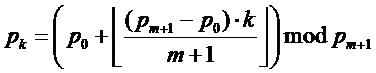

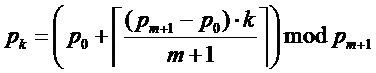

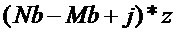

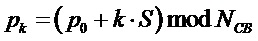

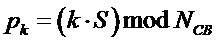

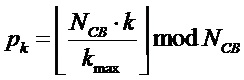

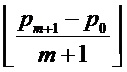

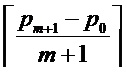

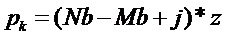

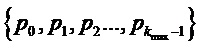

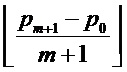

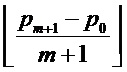

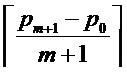

На этапе 401 значение k0 (i) может быть

Нижний индекс k в

В первой возможной реализации kmax значения

kmax значения

В примере, в котором кодированный блок имеет длину 215 битов, kmax равно 8, и разность между соседними значениями равна

Для другого примера,

Увеличение kmax может уменьшить расстояние между начальными позициями версий с избыточностью. Версия с избыточностью, определенная на основании начальной позиции, также может повысить производительность декодирования устройства связи на приемной стороне. Например, kmax может быть целым числом больше 4. Например, kmax = 5; или

В вышеприведенном способе интервал между передачами версии с избыточностью не сильно изменяется или не включает в себя большое количество повторяющихся битов. Следовательно, вышеупомянутый способ может быть адаптирован к различным начальным скоростям кодов передачи и имеет относительно стабильную производительность.

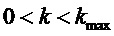

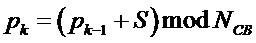

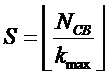

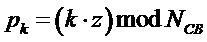

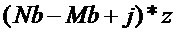

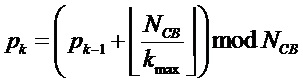

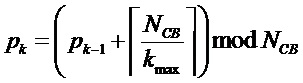

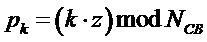

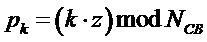

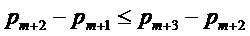

Во второй возможной реализации kmax значения

Например,

Например, во время начальной передачи получают выходную последовательность битов, имеющую высокую кодовую скорость, и включает в себя информационные биты и биты четности, которые соответствуют столбцам с весом 2 и которые не выкалывают, например, e0 на фиг. 5-1. Длина выходной последовательности битов равна

Если

Если

Согласно способу, начальные позиции более плотно распределены в позиции, более близкой к информационным битам, и начальные позиции более редко распределены в позиции, более близкой к последнему биту кодированного блока.

Базовую матрицу, показанную на фиг. 1, используют в качестве примера. Nb = 38, Mb=13 и z=4. Последние четыре столбца в матрице Hk ядра являются двухдиагональной структурной частью, а именно, соответствующими столбцами битов четности, соответствующим столбцам веса 2. Следовательно, количество битов четности, соответствующих столбцам веса 2, равно четырем. Если два столбца не выколоты, количество битов четности, соответствующих столбцам веса 2 и не выколотых, равно двум. Если j является количеством битов четности, соответствующих столбцам веса 2,

Для значения

На основании первой реализации или второй реализации, в третьей возможной реализации, если i> 0, начальную позицию k0 (i) определяют на основании начальной позиции k0 (i-1) предшествующего выходной последовательности битов передачи и длины E (i - 1) предшествующей выходной последовательности битов передачи.

Для простоты описания направление от последней позиции предшествующей выходной последовательности битов передачи к последнему биту ((NCB-1)-му биту) кодированного блока используют в качестве прямого направления, и направление от последней позиции предшествующей выходной последовательности битов передачи к начальному биту (0-й бит) кодированного блока используют в качестве обратного направления.

Например, для снижения количества повторяющихся битов избыточности, может быть получена начальная позиция k0 (i) в прямом направлении на основании начальной позиции k0 (i-1) предшествующей выходной последовательности битов передачи и длины E (i-1) предшествующей выходной последовательности битов передачи. Выходная последовательность битов не включает в себя бит заполнитель; следовательно, если F (i-1) представляет собой количество битов, необходимое для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i-1), то последняя позиция предшествующей полученной выходной последовательности битов равна (k0 (i-1) + F (i-1)-1) mod NCB. Значение

Может быть установлено, что

Значения {2, 28, 54, 80, 108, 114, 124, 138} в вышеприведенной реализации используются в качестве примера. Начальная позиция k0 (i-1) предшествующей выходной последовательности битов передачи равна 2, и длина E (i-1) предшествующей выходной последовательности битов передачи составляет 25 битов. Есть 5 битов наполнителя; следовательно, количество бит F (i-1), необходимое для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i-1) в последний раз, равно 30. Для выходной последовательности битов k0 (i) для i-й передачи k0 (i) = 54, если в этом варианте осуществления используют способ получения начальной позиции в прямом направлении. Если начальная позиция k0 (i-1) предшествующей выходной последовательности битов передачи составляет 124, длина E (i-1) предшествующей выходной последовательности битов передачи составляет 30 битов, и нет никаких битов-заполнителей, требуется количество битов для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i-1), последний раз равен 30, и k0 (i) = 2. Следует отметить, что это просто пример в данном документе, и настоящее изобретение этим не ограничивается.

В другом примере, чтобы удовлетворить требованию последовательного декодирования, начальную позицию k0 (i) получают в обратном направлении на основании начальной позиции k0 (i-1) предшествующей выходной последовательности битов передачи и длины E (i-1) предшествующей выходной последовательности битов передачи. Выходная последовательность битов не включает в себя бит заполнитель; следовательно, если F (i-1) является количеством битов, необходимым для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i-1), то последняя позиция предшествующей полученной выходной последовательности битов равна (k0 (i-1)+F (i-1) -1) mod NCB. Значение первой начальной позиции в обратном направлении от последней позиции предшествующей выходной полученной последовательности битов используют, как k0 (i). Если конечное местоположение предшествующей полученной выходной последовательности битов меньше, чем наименьшее значение в

Значения {2, 28, 54, 80, 108, 114, 124, 138} в предшествующем варианте осуществления и то, что длина кодированного блока составляет 152 бита, все еще используют в качестве примера. Начальная позиция k0 (i-1) предшествующей выходной последовательности битов передачи равна 2 и длина E (i-1) предшествующей выходной последовательности битов передачи составляет 25 битов. Есть 5 битов наполнителя. Следовательно, количество бит F (i - 1), необходимое для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i - 1) в последний раз, равно 30. Для выходной последовательности битов k0 (i) для i-й передачи k0 (i) = 28, если используют способ получения начальной позиции в обратном направлении. Если начальная позиция k0 (i-1) предшествующей выходной последовательности битов передачи составляет 124, длина E (i-1) предшествующей выходной последовательности битов передачи составляет 20 битов, и имеется девять заполняющих битов, количество бит F (i-1), требуемое для последовательного получения выходных битов E (i-1) из кодированного блока, начиная с k0 (i-1), в прошлый раз составляет 29, и k0 (i) = 138. Следует отметить, что это просто пример в данном документе, и настоящее изобретение этим не ограничивается.

В другом примере, чтобы компенсировать потери производительности декодирования, вызванные повторяющимися битами и пропуском избыточных битов, со ссылкой на результаты получения k0 (i) в обратном направлении и получения k0 (i) в прямом направлении, в двух приведенных примерах в качестве k0 (i) используют значение одного из двух результатов, которое имеет меньшую разницу с конечным местоположением предшествующей полученной выходной последовательности битов. Если

Значения {2, 28, 54, 80, 108, 114, 124, 138} в предшествующем варианте осуществления и то, что длина кодированного блока составляет 152 бита, все еще используют в качестве примера. Начальная позиция k0 (i-1) предшествующей выходной последовательности битов передачи равна 2 и длина E (i-1) предшествующей выходной последовательности битов передачи составляет 26 битов. Количество бит F (i-1), необходимое для последовательного получения E (i-1) выходных битов из кодированного блока, начиная с k0 (i-1) в последний раз, равно 30. Для выходной последовательности битов k0 (i) для i-й передачи k0 (i) = 28, если используют способ в этом варианте осуществления для получения начальной позиции. Если k0 (i-1) равно 124 битам, длина E (i-1) предшествующей выходной последовательности битов передачи составляет 29 битов и количество бит F (i-1) требуется для последовательного получения E (i-1) выходных биты из кодированного блока, начиная с k0 (i-1) в последний раз, равны 30, значение, полученное в прямом направлении, равно

В другом примере, с целью компенсации потери производительности декодирования, вызванные повторяющимися битами и пропуском избыточных битов, направление для получения начальной позиции k0 (i) в i-й передаче определяют на основании соответствия между величиной i передач и направлением для получения начальной позиции k0 (i), и начальную позицию k0 (i) получают на основании последней позиции предшествующей выходной последовательности битов передачи и определенного направления для получения начальной позиции k0 (i). Таблица количества передач i и направления для получения начальной позиции k0 (i), например, таблица 1, может быть применена в устройстве связи. Наибольшее количество повторных передач равно трем, и для начальной передачи не требуется установления направления получения.

Таблица 1

Значения {2, 28, 54, 80, 108, 114, 124, 138} в предшествующем варианте осуществления и то, что длина кодированного блока составляет 152 бита, все еще используют в качестве примера. Если начальная позиция k0 (0) выходной последовательности битов для начальной передачи равна 2, длина E (0) выходной битовой последовательности для начальной передачи составляет 20 битов, и количество битов заполнителей равно 10, F (0) = 30 бит. Предполагают, что каждый раз, при получении выходной последовательности битов имеется одинаковое количество битов заполнителей, выходная последовательность битов для каждой передачи имеет одинаковую длину, и начальную позицию получают с использованием соответствия в таблице 1 выше. Для выходной последовательности битов для 1-й передачи начальную позицию k0 (1) получают в прямом направлении и k0 (1) = 54. Для выходной последовательности битов для 2-й передачи начальную позицию k0 (2) получают в обратном направлении и k0 (2) = 80. Для выходной последовательности битов для 3-й передачи получают начальную позицию k0 (3) и k0 (3) = 108. Следует отметить, что это просто пример в данном документе, и настоящее изобретение этим не ограничивается.

«Прямое» и «обратное» в направлениях получения могут быть указаны с использованием конкретных числовых значений и не ограничиваются способом буквального выражения. Например, 0 представляет «обратное» и 1 представляет «прямое»; или используют другой способ числового выражения. Соответствие между величиной i передач и направлением для получения начальной позиции k0 (i) может быть альтернативно определено в другой форме. Этот вариант осуществления настоящего изобретения не ограничивается этим.

Направление для получения начальной позиции выходной последовательности битов для i-й передачи может быть определено на основании количества i передач. Начальную позицию k0 (i) получают в обратном направлении на основании направления для получения начальной позиции выходной последовательности битов для i-й передачи, начальной позиции k0 (i - 1) предшествующей выходной последовательности битов передачи и длины E (i - 1) предшествующей выходной последовательности битов передачи.

На основании первой реализации или второй реализации в четвертой возможной реализации может быть определен порядок, в котором начальную позицию получают во время каждой передачи, и также может быть выбран порядок выбора значения нижнего индекса k в

Нижний индекс k в

Может быть использован способ получения начальной позиции на основе фиксированного порядка. В варианте осуществления может быть определен порядок выбора значения rvidx. Количество значений в порядке выбора значений может быть kmax или может быть наибольшим количеством Rmax повторных передач. Например, когда kmax = 8, порядок выбора значения rvidx последовательно равен 0, 3, 6, 2, 5, 7, 4 и 1. Для начальной передачи определяют выходную последовательность битов начиная с этого

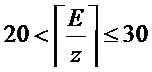

Кроме того, порядок выбора значения rvidx также может быть определен на основании значения начальной кодовой скорости передачи или может быть определен на основании длины E выходной последовательности битов для каждой передачи и размера z поднятия. В сценарии неадаптивной повторной передачи длина выходной последовательности битов в начальной передаче равна длине выходной последовательности битов в повторной передаче. Например, порядок выбора значения rvidx определяют на основании

Например, kmax = 8, и используют LDPC матрицу 66*82. Количество столбцов информационных битов равно 16. Для кодированного блока, для соответствия между порядком выбора значения rvidx и кодовой скоростью начальной передачи, см. таблицу 2. Например,

Таблица 2

Для другого примера, kmax = 8, и используют LDPC матрицу 66*82. Количество столбцов информационных битов равно 16. Для кодированного блока, со ссылкой на таблицу 3, где приведено соответствие между порядком выбора значения rvidx и начальной скоростью передачи кода. Например,

Таблица 3

Данный способ подходит для неадаптивной повторной передачи, и информация о начальной позиции не должна указываться устройству связи на приемной стороне перед каждым временем отправки.

Начальная позиция k0 (i) выходной последовательности битов в кодированном блоке может альтернативно быть получена на основании rvidx, указанного устройством связи на передающей стороне. Этот способ подходит для адаптивной повторной передачи.

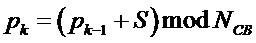

В пятой возможной реализации, для конкретной повторной передачи, для i> 0 выходная последовательность битов для i-й передачи и выходная последовательность битов для (i-1)-й передачи соединены друг с другом. В этой реализации k0 (i) определяют на основании начальной позиции k0 (i-1) предшествующей выходной последовательности битов передачи и длины E (i-1) предшествующей выходной последовательности битов передачи. Выходная последовательность битов не содержит бит заполнитель. Следовательно, F (i - 1) может быть получено на основании k0 (i - 1) и E (i - 1). F (i - 1) является количеством битов, необходимое для последовательного получения E (i - 1) выходных битов из кодированного блока, начиная с k0 (i - 1). k0 (i) = (k0 (i - 1) + F (i - 1)) mod NCB. В этой реализации выходные последовательности битов двух смежных передач являются последовательными, и между двумя выходными последовательностями битов не существует повторных битов, поэтому, когда такие выходные последовательности битов отправляются в устройство связи на приемной стороне, могут быть получены относительно хорошие характеристики декодирования.

Кроме того, на основании способа повторной передачи со сквозным соединением, после того как все биты кодированного блока были переданы один раз, добавляют смещение

Возможно, после того, как способ обработки информации выполнен, устройство связи может дополнительно обрабатывать выходную последовательность битов, так что выходную последовательность битов используют во время отправки или приема. Например, обработка включает в себя перемежение выходной последовательности битов, отображение выходной битовой последовательности на символы модуляции и тому подобное. Что касается обработки, обратитесь к соответствующему способу обработки в предшествующем уровне техники, и подробности в данном документе не описаны.

На фиг. 6 показана блок-схема последовательности операций способа обработки информации в соответствии с вариантом осуществления настоящего изобретения. Способ может быть применен к системе связи. Система связи включает в себя устройство 30 связи и устройство 31 связи. Способ может быть реализован устройством 31 связи и включает в себя следующие этапы.

601: получают начальную позицию k0 (i) последовательности мягких битов, имеющей длину E (i), сохраненной в мягком буфере.

602: объединяют и сохраняют последовательность мягких битов на этапе 601 в мягком буфере, начиная с начальной позиции k0 (i).

Устройство 30 связи отправляет выходную последовательность битов, полученную в предшествующих вариантах осуществления, в устройство 31 связи. Понятно, что выходная последовательность битов в предшествующих вариантах осуществления является выходной последовательностью битов, полученной после согласования скорости, устройство 30 связи может выполнять обработку, такую как перемежение и модуляция, для выходной последовательности битов, полученной после согласования скорости, и отправлять сигнал, соответствующий выходной последовательности битов, и устройство 31 связи принимает выходной сигнал и выполняет демодуляцию и обратное перемежение для выходного сигнала, чтобы получить последовательность мягких битов, соответствующую выходной последовательности битов. В частности, один бит в выходной последовательности битов соответствует одному мягкому канальному биту (soft channel bit) в последовательности мягких битов. Позиции мягких канальных битов, хранящиеся в мягком буфере устройства 31 связи, находятся во взаимно-однозначном соответствии с позициями в кодированном блоке в кольцевом буфере устройства 30 связи. Размер мягкого буфера и размер кодированного блока в кольцевом буфере также одинаковы и могут быть NCB.

Например, выходной бит, отправленный устройством 30 связи, равен 1, и после передачи по каналу устройство 31 связи получает мягкий канальный бит, соответствующий выходному биту, где мягкий канальный бит равен 1,45. Если позиция выходного бита в кодированном блоке равна 5-му биту, то 5-й мягкий канальный бит в мягком буфере устройства 31 связи равен 1,45. Следует отметить, что это просто пример для описания в данном документе, и этот вариант осуществления настоящего изобретения не ограничивается этим. Если выходная последовательность битов, полученная устройством 30 связи, включает в себя n выходных битов, устройство 31 связи может получить n соответствующих мягких канальных битов. Если два раза принимают мягкие канальные биты одной и той же позиции, устройство 31 связи объединяет два мягких значения. Например, если мягкий канальный бит, принятый в 1-й передаче, равен 1,45, и мягкий канальный бит, принятый во 2-й передаче, равен 0,5, после объединения получают 1,95. Следует отметить, что это просто пример в данном документе, и настоящее изобретение этим не ограничивается.

Очевидно, что начальная позиция k0 (i) и способ ее получения имеют признаки, соответствующие вышеприведенным вариантам осуществления. Обратимся к описаниям в вышеизложенных вариантах осуществления, и подробности не будут описаны здесь снова. Следует отметить, что в устройстве 30 связи начальная позиция относительна кодированному блоку в кольцевом буфере; в устройстве 31 связи начальная позиция относительна мягкому буферу; на стороне устройства 30 связи выходную последовательность битов определяют в кодированном блоке в кольцевом буфере, а на стороне устройства 31 связи принятую последовательность мягких битов сохраняют в мягком буфере.

На фиг. 7 показана структурная схема устройства 700 для обработки информации. Устройство может быть применено к устройству 30 связи в системе связи, показанной на фиг. 3. Устройство 700 также может упоминаться как устройство согласования скорости. Устройство 700 может быть выполнено с возможностью реализации вышеизложенных вариантов осуществления способа. Обратимся к описаниям в вышеприведенных вариантах осуществления способа, и подробности не будут описаны здесь снова.

Устройство 700 может включать в себя блок 701 получения и блок 702 обработки.

Блок 701 получения выполнен с возможностью получать начальную позицию k0 (i) выходной последовательности битов в кодированном блоке. Блок 702 обработки выполнен с возможностью определять выходную последовательность битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i). Кодированный блок хранят в кольцевом буфере, и i является целым числом, большим или равным 0. Для получения подробной информации о том, как получить k0 (i) и определить выходную последовательность битов на основании E (i) и k0 (i), обратитесь к описаниям в вышеупомянутых вариантах осуществления способа

На фиг. 8 показана схема устройства 800 для обработки информации. Устройство может быть применено к устройству 31 связи в системе связи, показанной на фиг. 3. Устройство 800 также может называться устройством де-согласования скорости. Устройство 800 может быть выполнено с возможностью реализации вышеизложенных вариантов осуществления способа. За подробностями обращайтесь к описаниям в вышеприведенных вариантах осуществления способа. Устройство 800 может включать в себя блок 801 получения и блок 802 обработки.

Блок 801 получения выполнен с возможностью получать начальную позицию k0 (i) последовательности мягких битов, имеющей длину E (i), сохраненной в мягком буфере. Блок 802 обработки выполнен с возможностью объединять и сохранять последовательности мягких битов, полученные блоком 801 получения, в мягком буфере, начиная с начальной позиции k0 (i).

Фиг. 9 является структурной схемой устройства связи. Устройство связи может быть применено к системе связи, показанной на фиг. 3. Устройство 30 связи может включать в себя кодер 301, устройство 302 согласования скорости и приемопередатчик 303. Кодер 301 также может упоминаться как блок кодирования, схема кодирования или тому подобное, и, в основном, выполнен с возможностью кодировать данные. Устройство 302 согласования скорости также может называться блоком согласования скорости, схемой согласования скорости или тому подобным, в основном, выполненным с возможностью определять, на основании кодированного блока, полученного кодером 301 путем кодирования, выходную последовательность битов, подлежащую отправке, например, выполненным с возможностью определять выходную последовательность битов в предшествующих вариантах осуществления и может включать в себя, например, устройство 700 на фиг. 7. Приемопередатчик 303 также может упоминаться как приемопередающий блок, приемопередатчик, схема приемопередатчика или тому подобное, и, в основном, выполнен с возможностью принимать и отправлять радиочастотные сигналы, например, выполненный с возможностью отправлять выходную последовательность битов в предшествующих вариантах осуществления для устройства 31 связи. Устройство 30 связи может дополнительно включать в себя другие компоненты, такие как компонент, выполненный с возможностью генерировать CRC транспортного блока, компонент, выполненный с возможностью выполнять сегментацию кодового блока и проверки CRC, перемежитель и модулятор, который могут быть соответственно выполнены с возможностью реализовывать функции частей устройства 30 связи на фиг. 3.

Следует отметить, что устройство 30 связи может включать в себя одно или несколько памяти и один или несколько процессоров. В памяти хранят инструкции. Процессор соединен с памятью, чтобы выполнять инструкции в памяти, чтобы выполнять этапы, описанные в вариантах осуществления способа. Память может дополнительно включать в себя другие инструкции для процессора, чтобы выполнять функции других частей устройства 30 связи, например, сегментацию кодового блока, проверки CRC, перемежения и модуляции.

Фиг. 10 является структурной схемой устройства связи. Устройство связи может быть применено к системе связи, показанной на фиг. 3. Устройство 31 связи может включать в себя декодер 311, устройство 312 де-согласование скорости и приемопередатчик 313. Устройство 312 де-согласования скорости также может упоминаться как блок де-согласования скорости или схема де-согласования скорости, может быть выполнено с возможностью объединять мягкие канальные биты, например, выполнено с возможностью объединять и сохранять мягкие канальные биты выходной последовательности битов согласно предшествующим вариантам осуществления в мягком буфере и может включать в себя, например, устройство 800 на фиг. 8. Декодер 311 также может упоминаться как блок декодирования или схема декодирования и, в основном, выполнен с возможностью декодировать принятый сигнал, например, выполнен с возможностью декодировать мягкие канальные биты в мягком буфере. Приемопередатчик 313 также может упоминаться как приемопередающий блок, приемопередатчик, схема приемопередатчика или тому подобное, и, в основном, выполнен с возможностью принимать и отправлять радиочастотный сигнал, например, выполнен с возможностью принимать выходную последовательность битов в вышеприведенных вариантах осуществления, которую отправляют устройством 30 связи. Устройство 31 связи может дополнительно включать в себя другие компоненты, такие как компонент, выполненный с возможностью выполнять проверку CRC на транспортном блоке, компонент, выполненный с возможностью выполнять конкатенацию кодовых блоков, обращенный перемежитель и демодулятор, который могут быть соответственно выполнены с возможностью реализации функций частей устройства 31 связи на фиг. 3.

Следует отметить, что устройство 31 связи может включать в себя одно или несколько памяти и процессоров, чтобы реализовывать функции частей устройства 31 связи на фиг. 3. Выделенная память и процессор могут быть расположены для каждого компонента. Альтернативно, множество компонентов совместно используют одну и ту же память и процессор.

Следует отметить, что устройство 31 связи может включать в себя одно или несколько памяти и один или несколько процессоров. В памяти хранят инструкции. Процессор соединен с памятью, чтобы выполнить инструкцию в памяти, чтобы выполнить этапы, описанные в вариантах осуществления способа. Память может дополнительно включать в себя другие инструкции для процессора, которые должны быть выполнены для выполнения функций других частей устройства 30 связи, например, конкатенации кодовых блоков, обратное перемежение и демодуляции.

Специалист в данной области техники может также понимать, что различные иллюстративные логические блоки (иллюстративный логический блок) и этапы (этап), которые перечислены в вариантах осуществления настоящего изобретения, могут быть реализованы с использованием электронного аппаратного обеспечения, компьютерного программного обеспечения или их комбинация. Реализация функций с использованием аппаратного или программного обеспечения зависит от конкретных приложений и требований к проектированию всей системы. Специалист в данной области техники может использовать различные способы для реализации функций для каждого конкретного приложения, но такую реализацию не следует истолковывать как выход за пределы объема вариантов осуществления настоящего изобретения.

Различные иллюстративные логические блоки и схемы, описанные в вариантах осуществления настоящего изобретения, могут реализовывать или управлять описанными функциями, используя схему процессора общего назначения, процессора цифровых сигналов, специализированной интегральной схемы (ASIC), программируемая пользователем полевая матрица (FPGA) или другое программируемое логическое устройство, дискретная логическая схема шлюза или транзисторная логика, дискретный аппаратный компонент или любая их комбинация. Процессор общего назначения может быть микропроцессором. Возможно, универсальный процессор также может быть любым обычным процессором, контроллером, микроконтроллером или машиной состояния. Процессор также может быть реализован с помощью комбинации вычислительных устройств, например, процессора цифровых сигналов и микропроцессора, множества микропроцессоров, одного или нескольких микропроцессоров в сочетании с ядром процессора цифровых сигналов или любой другой подобной конфигурации.

Этапы способов или алгоритмов, описанных в вариантах осуществления настоящего изобретения, могут быть непосредственно встроены в аппаратные средства, в инструкции, выполняемые процессором, или в их комбинации. Память может быть памятью RAM, флеш-памятью, памятью ROM, памятью EPROM, памятью EEPROM, регистром, жестким диском, съемным жестким диском, CD-ROM или любым другим видом носителя информации в данной области техники. Например, память может быть подключена к процессору, так что процессор может считывать информацию из памяти и записывать информацию в память. Возможно, память может быть дополнительно интегрирована в процессор. Процессор и память могут быть расположены в ASIC, и ASIC может быть расположена в UE. Возможно, процессор и память могут быть расположены в разных компонентах UE.

С учетом описания вышеупомянутых реализаций, специалист в данной области техники может четко понимать, что настоящее изобретение может быть реализовано посредством аппаратного обеспечения, встроенного программного обеспечения или их комбинации. При реализации с использованием программного обеспечения способы могут быть полностью или частично реализованы в форме компьютерного программного продукта, и компьютерный программный продукт включает в себя одну или несколько компьютерных инструкций. Когда компьютерные инструкции загружаются и выполняются на компьютере, генерируют процедуру или функции согласно вариантам осуществления настоящего изобретения полностью или частично. Когда настоящее изобретение реализуют с использованием программного обеспечения, вышеупомянутые функции могут быть сохранены на машиночитаемом носителе или переданы в виде одной или нескольких инструкций или кода на машиночитаемом носителе. Компьютер может быть компьютером общего назначения, выделенным компьютером, компьютерной сетью или другими программируемыми устройствами. Компьютерные инструкции могут храниться на машиночитаемом носителе или могут передаваться с машиночитаемого носителя на другой машиночитаемый носитель. Машиночитаемый носитель включает в себя компьютерный носитель данных и носитель связи, где носитель связи включает в себя любой носитель, который вызывает передачу компьютерной программы из одного места в другое. Носитель данных может быть любым доступным носителем, доступным для компьютера. Ниже приведен пример, но не накладывает ограничение: машиночитаемый носитель может включать в себя RAM, ROM, EEPROM, CD-ROM или другое хранилище на оптических дисках, или дисковый носитель, или другое магнитное запоминающее устройство, или любой другой носитель, который может использоваться для переноса или хранения ожидаемого программного кода в форме инструкций или структур данных и может быть доступен с помощью компьютера. Кроме того, любое соединение может быть соответствующим образом определено как машиночитаемый носитель. Например, если программное обеспечение передают с веб-сайта, сервера или другого удаленного источника с использованием коаксиального кабеля, оптоволокна/кабеля, витой пары, цифровой абонентской линии (DSL) или беспроводных технологий, таких как инфракрасное излучение, радио и сигнал микроволнового диапазона, и коаксиальный кабель, оптоволокно/кабель, витая пара, DSL или беспроводные технологии, такие как инфракрасное излучение, радио и сигнал микроволнового диапазона определены в качестве среды, к которой они принадлежат. Например, диск (Disk) и диск (disk), используемые в настоящем изобретении, включают в себя компакт-диск (CD), лазерный диск, оптический диск, цифровой универсальный диск (DVD), дискету и диск Blu-ray. диск, на котором диск обычно копирует данные с помощью магнитного средства, и диск оптически копирует данные с помощью лазерного средства. Вышеуказанная комбинация также должна находиться в рамках объема защиты машиночитаемого носителя.

В заключение, необходимо отметить, что приведенное выше описание является просто примерными вариантами осуществления технических решений настоящего изобретения, но не предназначено для ограничения объема защиты настоящего изобретения. Любая модификация, эквивалентная замена или улучшение, выполненные без отклонения от принципа настоящего изобретения, должны находиться в рамках объема защиты настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И УСТРОЙСТВО СВЯЗИ | 2017 |

|

RU2740154C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И УСТРОЙСТВО СВЯЗИ | 2017 |

|

RU2740151C1 |

| Способ и устройство | 2020 |

|

RU2748852C1 |

| Способ и устройство кодирования данных, носитель данных и процессор | 2018 |

|

RU2742912C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ, ПРИСПОСОБЛЕНИЕ И УСТРОЙСТВО СВЯЗИ | 2018 |

|

RU2769096C2 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ СОГЛАСОВАНИЯ СКОРОСТИ, ЧТОБЫ УЛУЧШИТЬ ОПЕРАЦИИ ГИБРИДНОГО ARQ | 2008 |

|

RU2426246C1 |

| АППАРАТУРА, СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И АППАРАТУРА СВЯЗИ | 2018 |

|

RU2758968C2 |

| СПОСОБЫ СОГЛАСОВАНИЯ СКОРОСТИ ДЛЯ LDPC-КОДОВ | 2017 |

|

RU2730434C1 |

| УСТРОЙСТВО БАЗОВОЙ СТАНЦИИ, ТЕРМИНАЛЬНОЕ УСТРОЙСТВО И СПОСОБ СВЯЗИ | 2017 |

|

RU2739589C2 |

| УСТРОЙСТВО И СПОСОБ КОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ КАНАЛА С ИСПОЛЬЗОВАНИЕМ ПАРАЛЛЕЛЬНОГО КАСКАДНОГО КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2004 |

|

RU2310274C1 |

Группа изобретений относится к области связи и, в частности, к способу и устройству для обработки информации, устройству связи и системе связи. Техническим результатом является повышение производительности при обработке информации. Предложен способ обработки информации в системе связи. Согласно способу, осуществляют получение начальной позиции k0 (i) выходной последовательности битов в кодированном блоке с низкой плотностью проверок на четность (LDPC), в котором выходная последовательности битов является версией с избыточностью для i-й передачи. Далее осуществляют определение выходной последовательности битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i), в котором кодированный блок хранят в кольцевом буфере, i является целым числом, большим или равным 0. 6 н. и 25 з.п. ф-лы, 12 ил., 3 табл.

1. Способ обработки информации в системе связи, содержащий:

получение начальной позиции k0 (i) выходной последовательности битов в кодированном блоке с низкой плотностью проверок на четность (LDPC), в котором выходная последовательности битов является версией с избыточностью для i-й передачи; и

определение выходной последовательности битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i), в котором кодированный блок хранят в кольцевом буфере, i является целым числом, большим или равным 0,

значение k0 (i) является

в котором

2. Способ по п.1, в котором

3. Способ по п.1, в котором

4. Способ по п.3, в котором

0< k ≤ m+1.

5. Способ по п.3, в котором kmax=4, p2-p1<p3-p2.

6. Способ по п.5, в котором во время начальной передачи выходная последовательность битов включает в себя информационные биты и биты четности, которые соответствуют столбцам весом 2.

7. Способ по п.1, в котором начальную позицию k0 (i) определяют на основании номера rvidx (i) начальной позиции версии с избыточностью.

8. Способ по п.7, в котором номер rvidx (i) начальной позиции версии с избыточностью получают посредством сигнализации.

9. Способ по п.7, в котором номер rvidx (i) начальной позиции версии с избыточностью получают на основании номеров начальной позиции версии с избыточностью и количества i передач.

10. Способ по п.9, в котором последовательность номеров начальной позиции версии с избыточностью считывают из памяти, или последовательность номеров начальных позиций версии с избыточностью определяют на основании кодовой скорости начальной передачи.

11. Способ обработки информации в системе связи, содержащий:

получение начальной позиции k0 (i) последовательности мягких битов, имеющей длину E(i), сохраненной в мягком буфере, в котором последовательность мягких битов соответствует выходной последовательности битов в кодированном блоке LDPC и выходная последовательности битов является версией с избыточностью для i-й передачи; и

объединение и сохранение последовательности мягких битов в мягком буфере, начиная с начальной позиции k0 (i), в котором i является целым числом, большим или равным 0, значение k0 (i) является

12. Способ по п.11, в котором

13. Способ по п.11, в котором

14. Способ по п.13, в котором

15. Способ по п.11, в котором kmax=4, p2-p1<p3-p2.

16. Способ по п.15, в котором во время начальной передачи выходная последовательность битов включает в себя информационные биты и биты четности, которые соответствуют столбцам весом 2.

17. Способ по п.11, в котором начальную позицию k0 (i) определяют на основании номера rvidx (i) начальной позиции версии с избыточностью.

18. Способ по п.17, в котором номер rvidx (i) начальной позиции версии с избыточностью получают на основании номеров начальной позиции версии с избыточностью и количества i передач.

19. Устройство для обработки информации в системе связи, содержащее:

блок получения, выполненный с возможностью получения начальной позиции k0 (i) выходной последовательности битов в кодированном блоке с низкой плотностью проверок на четность (LDPC), в котором выходная последовательности битов является версией с избыточностью для i-й передачи; и

блок обработки, выполненный с возможностью определения выходной последовательности битов в кодированном блоке на основании длины E (i) выходной последовательности битов и начальной позиции k0 (i), в котором кодированный блок хранят в кольцевом буфере, i является целым числом, большим или равным 0,

значение k0(i) является

в котором

20. Устройство по п.19, в котором

21. Устройство по п.19, в котором

22. Устройство по п.21, в котором

23. Устройство по п.21, в котором kmax=4, p2-p1<p3-p2.

24. Устройство по п.23, в котором во время начальной передачи выходная последовательность битов включает в себя информационные биты и биты четности, которые соответствуют столбцам весом 2.

25. Устройство по п.19, в котором начальную позицию k0 (i) определяют на основании номера rvidx (i) начальной позиции версии с избыточностью.

26. Устройство по п.25, в котором номер rvidx (i) начальной позиции версии с избыточностью получают посредством сигнализации.

27. Устройство по п.25, в котором номер rvidx (i) начальной позиции версии с избыточностью получают на основании номеров начальной позиции версии с избыточностью и количества i передач.

28. Устройство по п.27, в котором последовательность номеров начальной позиции версии с избыточностью считывают из памяти, или последовательность номеров начальных позиций версии с избыточностью определяют на основании кодовой скорости начальной передачи.

29. Аппаратура связи, содержащая процессор и память, в котором память хранит инструкции, и процессор соединен с памятью, чтобы выполнять инструкции для выполнения способа по любому из пп.1-18.

30. Машиночитаемый носитель данных, содержащий инструкции, в которых, когда машиночитаемый носитель данных используют на компьютере, компьютер выполняет способ по любому из пп.1-18.

31. Система связи, содержащая первое устройство связи и второе устройство связи, в которой первое устройство связи выполнено с возможностью кодировать информационную последовательность для получения кодированного блока и выполнять способ по любому из пп.1-10 на кодированном блоке, и первое устройство связи дополнительно выполнено с возможностью выполнять, по меньшей мере, одну из операций перемежения и модуляции над выходной последовательностью битов для генерирования выходного сигнала и отправлять выходной сигнал во второе устройство связи; и второе устройство связи выполнено с возможностью: принимать из первого устройства связи сигнал, содержащий выходной сигнал, выполнять, по меньшей мере, одну из операций демодуляции и обратного перемежения и выполнять способ по любому одному из пп.11-18, чтобы получить мягкий буфер закодированного блока, и декодировать мягкий буфер для получения информационной последовательности.

| CN 101188428 B, 05.09.2012 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| ZTE, "Bit rearrangement of LDPC for high order modulation", 3GPP TSG RAN WG1 AH_NR Meeting, Spokane, USA 16th - 20th January 2017, Document: R1-1700248, 5 л., опубл | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Найдено в интернет по адресу: | |||

Авторы

Даты

2021-07-28—Публикация

2018-01-30—Подача