Область техники, к которой относится изобретение

Настоящее изобретение относится к области масштабирования гибридной Оперативной обработки транзакций/Оперативной аналитической обработки данных (Online-Transaction-Processing/Online Analytical Processing) встроенных в память баз данных путем связывания разделов памяти с процессорными ядрами. В частности, настоящая заявка относится к системе для синхронизации памяти в многоядерной системе.

Уровень техники

Традиционно системы баз данных, которые должны обслуживать рабочие нагрузки и Оперативной обработки транзакций (Online-Transaction-Processing, OLTP), и Оперативной аналитической обработки данных (Online Analytical Processing, OLAP), развязаны одни от других, так что одна система обслуживает нагрузку транзакций OLTP в реальном времени, а другая, отдельная система обслуживает аналитическую нагрузку OLAP, оперирующую над ранее импортированным массивом данных. Такая конфигурация имеет ряд недостатков: она требует больше физических ресурсов, порождает издержки на обслуживание и поддержание в работоспособном состоянии, и что наиболее важно – она препятствует выполнению аналитической обработки OLAP почти в реальном времени поверх базы данных для обработки OLTP, поскольку это делает необходимым групповой экспорт и импорт данных из системы транзакций OLTP в систему аналитической обработки OLAP.

Идея создания мгновенных копий содержания памяти для аналитических запросов путем привлечения блока управления памятью (Memory Management Unit (MMU)) частично решает проблему, позволяя одной базе данных обслуживать обе нагрузки – и нагрузку OLTP обработки транзакций, и нагрузку OLAP аналитической обработки, но эта идея жестко ограничена узкими местами масштабируемости, связанными с необходимыми взаимодействиями ядра операционной системы с базовой аппаратной платформой и, в частности, с ответственностью операционной системы за поддержание согласованности с элементами кэша буфера быстрого преобразования адресов (TLB), особенно в случае многоядерной платформы, содержащей большое число компьютерных блоков (процессорных (CPU) ядер).

Заявка US 2013/0073513 A1 описывает способ поддержания и обслуживания гибридной базы данных транзакций OLTP и анализа OLAP, этот способ содержит: выполнение одной или нескольких транзакций OLTP; создание виртуальной мгновенной копии памяти; и выполнение одного или нескольких запросов анализа OLAP с использованием этой виртуальной мгновенной копии памяти. Описываемый здесь способ далее содержит дублирование виртуальной страницы памяти, на которой сохранен объект данных, в ответ на обновление этого объекта данных, вследствие чего этот обновленный объект данных становится доступен для транзакций OLTP, тогда как необновленный объект данных остается доступен для запросов анализа OLAP. Соответственно, описываемая здесь гибридная система может выполнять и транзакции OLTP, и аналитическую обработку OLAP одновременно с использованием механизмов дублирования с применением аппаратных средств для поддержания согласованных мгновенных копий данных транзакций.

Раскрытие сущности изобретения

Целью настоящего изобретения является усовершенствование синхронизации в многоядерной системе, в частности, создание усовершенствованного способа масштабирования гибридных встроенных в память баз данных транзакций/аналитической обработки (OLTP/OLAP), привлекающего блок MMU для поддерживаемого аппаратурой создания виртуальных мгновенных копий данных, т.е. создания виртуальных копий или версий данных.

Эта цель достигается с использованием признаков независимых пунктов Формулы изобретения. Другие формы осуществления изобретения очевидны из зависимых пунктов Формулы изобретения, описания и чертежей.

Настоящее изобретение непосредственно рассматривает проблему масштабируемости встроенных в память гибридных баз данных транзакций/аналитической обработки (OLTP/OLAP), привлекающего блок MMU для поддерживаемого аппаратурой создания виртуальных мгновенных копий данных, т.е. создания виртуальных копий или версий данных.

Согласно первому аспекту предложена система синхронизации памяти в многоядерной системе, содержащая: модуль назначения для назначения по меньшей мере одного раздела памяти по меньшей мере одному процессорному ядру в многоядерной системе; модуль отображения для предоставления информации для отключения буфера быстрого преобразования адресов в многоядерной системе, с привлечением передачи прерывания в это по меньшей одно процессорное ядро многоядерной системы, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным указанному по меньшей мере одному процессорному ядру, оказался модифицирован; и интерфейсный модуль для создания интерфейса с модулем назначения из пользовательского пространства.

Другими словами настоящее изобретение рассматривает проблему масштабируемости путем использования интерфейса от ядра операционной системы к базе данных, через который база данных может информировать ядро операционной относительно «связывания» областей памяти или разделов памяти с конкретными ядрами центрального процессора (CPU). Ядро операционной системы на основе информации предварительно поступившей из базы данных, избирательно отключает конкретные элементы буфера быстрого преобразования адресов (TLB) конкретных процессорных ядер (отключение буфера TLB) вместо того, чтобы «передавать в режиме вещания» команды отключения буфера TLB всем процессорным ядрам, совместно использующим адресное пространство базы данных, посредством потоков.

Следующее преимущество настоящего изобретения состоит в том, что оно с успехом предлагает средства, позволяющие любые схемы мгновенных копий на основе блока MMU масштабировать на многоядерных машинах путем осуществления косвенного управления процедурой отключения буфера TLB в системе базы данных.

Например, система базы данных, путем управления размещением ее транзакционных (OLTP) потоков, оказывается осведомлена о том, какие процессорные (CPU) ядра/потоки оперируют в каких частях памяти (разделах базы данных). Передавая эту информацию в ядро операционной системы, база данных косвенно управляет процедурой отключения буфера TLB, так что межпроцессорные прерывания (inter-processor interrupt (IPI)) ограничены группой выбранных процессорных ядер, для каждого раздела. Это освобождает систему от избыточной нагрузки (издержек), связанной с осуществлением очень затратных отключений буфера TLB на основе прерываний IPI для всех имеющихся процессорных ядер, совместно использующих адресное пространство, во время обработки страницы, в которой произошел сбой, и дает возможность высокой степени масштабируемости системы с использованием схемы создания мгновенных копий на основе блока MMU.

Настоящее изобретение использует преимущества того факта, что приложение или база данных имеет возможность поддерживать связывание потоков транзакций OLTP с разделами памяти и предоставлять эту информацию ядру операционной системы с целью иметь возможность осуществлять более избирательное и направленное отключение буфера TLB в случае сбоев при копировании страниц при записи, действуя тем самым в качестве согласованного механизма создания мгновенных копий для систем встроенных в память гибридных баз данных транзакций/аналитической обработки (OLTP/OLAP).

Без этой информации, поступающей от базы данных в ядро операционной системы, это ядро операционной системы вынуждено передавать команды прерывания IPI для отключения буфера TLB в режиме широкого вещания всем процессорным ядрам, совместно использующим адресное пространство, что влечет очень большие затраты, или в качестве альтернативы ядро операционной системы должно быть переделано с целью отслеживать использование страниц для всех имеющихся в наличии процессорных ядер системы, что влечет за собой высокие затраты при реализации, равно как и повышенные затраты во время работы.

Настоящее изобретение с успехом обеспечивает масштабируемость при создании мгновенных копий на основе блока MMU в контексте систем встроенных в память баз данных.

Базовая концепция настоящего изобретения обеспечивает высокую степень масштабируемости для систем гибридных встроенных в память баз данных транзакций/аналитической обработки (OLTP/OLAP), использующих механизм создания мгновенных копий на основе блока MMU. Это достигается посредством обеспечения управления отключениями буфера TLB со стороны ядра операционной системы в пользовательском пространстве, где на это может влиять система базы данных.

Согласно схеме создания мгновенных копий на основе блока MMU (осуществление отложенного совместного использования страницы, копируемой при записи) основной объем издержек является следствием прерываний IPI для отключения буфера TLB, осуществляемых в процессе обработки сбоя при копировании страниц в процессе записи (copy-on-write, CoW).

В частности, настоящее изобретение предпочтительно предлагает, что за счет предоставления базе данных возможности управлять тем, какие процессорные ядра должны принять команды прерывания IPI для отключения буфера TLB для различных частей адресного пространства, достигается масштабируемость способа на основе блока MMU, служащего механизмом для создания мгновенных копий в системах гибридных встроенных в память баз данных транзакций/аналитической обработки (OLTP/OLAP).

В частности, настоящее изобретение с успехом использует имеющиеся у системы базы данных знания или информацию, которая может быть привлечена операционной системой, с целью значительного снижения затрат на отключение буфера TLB, свойственных самой природе механизма создания мгновенных копий на основе блока MMU.

В частности, настоящее изобретение предпочтительно предлагает способ, согласно которому система базы данных назначает связи между памятью и/или разделами памяти с одной стороны и аппаратными процессорными ядрами с другой стороны с целью отключения буфера TLB во время копирования при записи (CoW) и обеспечивает, что потоки, осуществляющие транзакции (OLTP), оперируют на назначенных им разделах памяти.

В частности, настоящее изобретение предпочтительно предлагает способ передачи, посредством новых системных вызовов, из базы данных в ядро операционной системы информации о связывании аппаратного процессорного ядра с разделом данных с целью отключения буфера TLB во время копирования при записи (CoW).

В частности, настоящее изобретение предпочтительно предлагает механизм ядра операционной системы, который в момент отключений буфера TLB, требуемых во время обработки сбоев страниц в ходе копирования при записи (CoW), обращается к поступившей от базы данных информации о связывании процессорных ядер с разделами и поэтому выдает команды прерывания IPI при отключении буфера TLB избирательно, так что эти команды направляются только в конкретные процессорные ядра, которые связаны с конкретным разделом памяти, к которому принадлежит страница, где произошел сбой.

Одним из преимуществ является улучшение характеристик транзакций OLTP (как с точки зрения меньшего времени задержки отклика, так и с точки зрения пропускной способности) за счет сокращения времени обработки данных в потоке, осуществляющем транзакции.

Другое преимущество состоит в том, что система тратит значительно меньше времени в ядре операционной системы, когда происходит сбой страницы во время копирования при записи (CoW). Кроме того механизм создания мгновенных копий (CoW) с использованием блока MMU/аппаратуры масштабируется при увеличении числа процессорных ядер.

Термин «копирование при записи», как он применяется в настоящем изобретении, может описывать стратегию оптимизации, используемую в комёпьютерном программировании. Появление копирования при записи произошло из понимания, что когда несколько раздельных задач используют первоначально идентичные копии некоторой информации (т.е. данные, хранящиеся в памяти компьютера), обрабатывая их как локальные данные, которые может потребоваться время от времени модифицировать, тогда нет необходимости немедленно создавать отдельные копии этой информации для каждой задачи.

Термин «синхронизация памяти», как он применяется в настоящем изобретении, может описывать процесс, используемый в многоядерных процессорных системах, реализующих механизмы синхронизации с целью синхронизации памяти в многоядерных системах.

Термин «блок управления памятью» (“memory management unit (MMU)”), иногда именуемый здесь блоком управления страничной памятью (paged memory management unit (PMMU)), как он применяется в настоящем изобретении, может обозначать компьютерный аппаратный блок, через который проходят все ссылки к памяти и который главным образом осуществляет трансляцию виртуальных адресов памяти в физические адресы.

Термин «мгновенная копия» или «создание мгновенной копии», как он применяется в настоящем изобретении, может обозначать мгновенную копию, представляющую состояние системы в конкретный момент времени. Термин может быть использован в качестве аналога фотографии. Термин может относиться к актуальной копии состояния системы или к возможностям, реализуемым некоторыми системами.

Термин «межпроцессорное прерывание», как он применяется в настоящем изобретении, может обозначать конкретный тип прерывания, посредством которого один процессор может прерывать работу другого процессора в многопроцессорной системе, если прерывающий процессор требует действия от другого процессора.

В первом возможном варианте реализации системы согласно первому аспекту модуль отображения выполнен с возможностью предоставления информации для отключения буфера быстрого преобразования адресов во время копирования при записи страницы, совместно использующей по меньшей мере один раздел памяти. Это предпочтительно создает средства, позволяющие какую-либо схему создания мгновенной копии на основе блока MMU масштабировать на многоядерных машинах.

Во втором возможном варианте реализации системы согласно первому аспекту, как таковому или согласно первому варианту реализации этого первого аспекта, интерфейсный модуль выполнен с возможностью создания интерфейса с модулем назначения и пользовательским пространством посредством группы системных вызовов для управлением связыванием по меньшей мере одного раздела памяти по меньшей мере с одним ядром. Это предпочтительно обеспечивает осведомленность базы данных или приложения о том, какие процессорные (CPU) ядра и/или потоки оперируют в каких частях памяти (разделах базы данных).

В третьем возможном варианте реализации системы согласно первому аспекту, как таковому или согласно какому-либо из предшествующих вариантов реализации этого первого аспекта, интерфейсный модуль выполнен с возможностью адаптации отключения буфера быстрого преобразования адресов посредством информации, принятой с использованием группы системных вызовов. Это предпочтительно обеспечивает осуществление более избирательного и целенаправленного отключения буфера TLB.

Согласно второму аспекту настоящее изобретение относится к базе данных, содержащей многоядерную систему, имеющую по меньшей мере одно процессорное ядро; систему памяти, имеющую по меньшей мере один раздел памяти; и систему синхронизации памяти в многоядерной системе, причем указанная система синхронизации содержит: модуль назначения для назначения по меньшей мере одного раздела памяти по меньшей мере одному процессорному ядру в многоядерной системе; модуль отображения для предоставления информации для отключения буфера быстрого преобразования адресов в многоядерной системе путем передачи команды прерывания по меньшей мере одному процессорному ядру в многоядерной системе, если происходит модификация элемента таблицы страниц, ассоциированного с разделом памяти, назначенным рассматриваемому по меньшей мере одному процессорному ядру; и интерфейсный модуль для создания интерфейса с модулем назначения из пользовательского пространства.

В первом возможном варианте реализации базы данных согласно второму аспекту эта база данных представляет собой гибридную базу данных для оперативной обработки транзакций и оперативной аналитической обработки данных. Это предпочтительно обеспечивает осуществление транзакций OLTP и аналитической обработки OLAP над одними и теми же данными, находящимися в памяти.

Во втором возможном варианте реализации базы данных согласно второму аспекту или согласно какому-либо из предшествующих вариантов реализации этого второго аспекта, указанная база данных выполнена с возможностью осуществления оперативной обработки транзакций посредством обеспечения того, что по меньшей мере один поток оперативной обработки транзакций оперирует с одним или более разделами из указанной совокупности, содержащей по меньшей мере один раздел памяти. Это предпочтительно создает эффективный способ многопроцессорной обработки и повышает эффективность распределения задач между ними.

В третьем возможном варианте реализации базы данных согласно второму аспекту или согласно какому-либо из предшествующих вариантов реализации указанного второго аспекта, указанная база данных выполнена с возможностью управляемого дитспетчирования отключений буфера быстрого преобразования адресов с использованием структуры данных, указывающей, какое из процессорных ядер связано с каким из совокупности разделов, содержащей по меньшей мере один раздел данных. Это дополнительно совершенствует выполнение нескольких одновременных процессов в многоядерной системе.

В четвертом возможном варианте реализации базы данных согласно второму аспекту или согласно какому-либо из предшествующих вариантов реализации указанного второго аспекта, интерфейсный модуль выполнен с возможностью передачи информации о связывании по меньшей мере одного раздела памяти по меньшей мере с одним процессорным ядром. Это предпочтительно обеспечивает осведомленность базы данных или приложения о том, какие процессорные (CPU) ядра/потоки оперируют с какими частями памяти (разделы базы данных).

В пятом возможном варианте реализации базы данных согласно четвертому возможному варианту реализации этого второго аспекта, интерфейсный модуль выполнен с возможностью адаптации отключения буфера быстрого преобразования адресов посредством информации, принимаемой с использованием группы системных вызовов. Это предпочтительно обеспечивает осуществление более избирательного и целенаправленного отключения буфера TLB.

Согласно третьему аспекту настоящее изобретение относится к способу синхронизации памяти в многоядерной системе, способ содержит: этапы, на которых назначают по меньшей мере один раздел памяти по меньшей мере одному процессорному ядру в многоядерной системе с использованием модуля назначения; осуществляют отключение буфера быстрого преобразования адресов в многоядерной системе с использованием модуля отображения посредством передачи команды прерывания по меньшей мере одному процессорному ядру в многоядерной системе, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным этому по меньшей мере одному процессорному ядру, оказался модифицирован; и создают интерфейс с модулем назначения и пользовательским пространством с использованием интерфейсного модуля.

В первом возможном варианте реализации способа согласно третьему аспекту, этап осуществления отключения буфера быстрого преобразования адресов выполняется во время копирования при записи страницы, совместно использующей по меньшей мере один раздел памяти. Это предпочтительно создает средства, обеспечивающие какую-либо схему создания мгновенной копии на основе блока MMU масштабировать на многоядерных машинах.

Во втором возможном варианте реализации способа согласно третьему аспекту или согласно первому возможному варианту реализации способа согласно этому третьему аспекту этап осуществления отключения буфера быстрого преобразования адресов выполняется посредством набора системных вызовов для управления связыванием по меньшей мере одного раздела памяти по меньшей мере с одним процессорным ядром. Это предпочтительно обеспечивает осведомленность базы данных или приложения о том, какие процессорные (CPU) ядра/потоки оперируют с какими частями памяти (разделы базы данных).

В третьем возможном варианте реализации способа согласно третьему аспекту как таковому или согласно какому-либо из предшествующих вариантов реализации третьего аспекта отключение буфера быстрого преобразования адресов адаптируется посредством информации, принятой с использованием группы системных вызовов. Это предпочтительно обеспечивает осуществление более избирательного и целенаправленного отключения буфера TLB.

Согласно пятому аспекту настоящее изобретение относится к компьютерной программе, содержащей программный код для осуществления способа согласно какому-либо из предшествующих вариантов реализации указанного третьего аспекта, когда эту компьютерную программу выполняет компьютер.

Способы, системы и устройства, описываемые здесь, могут быть реализованы в виде программного обеспечения в цифровом процессоре сигнала (Digital Signal Processor (DSP)), в микроконтроллере или в какой-либо другой процессорной или аппаратной схеме, в составе специализированной интегральной схемы (application specific integrated circuit (ASIC)) или в программируемой пользователем вентильной матрице, представляющей собой интегральную схему, рассчитанную на конфигурирование потребителем или проектировщиком уже после изготовления, и потому она и называется «программируемая пользователем».

Настоящее изобретение может быть осуществлено в цифровой электронной схеме или в виде компьютерной аппаратуры, встроенного программного обеспечения, загружаемого программного обеспечения или сочетания этих компонентов, например, в виде имеющейся аппаратуры обычных мобильных устройств, либо в виде специализированной аппаратуры, разработанной для осуществления описываемых здесь способов.

Эти и другие аспекты настоящего изобретения станут очевидны со ссылками на описываемые далее варианты. Более полное понимание настоящего изобретения и его преимуществ станут возможны со ссылками на последующие схематичные чертежи.

Краткое описание чертежей

Далее варианты настоящего изобретения будут описаны применительно к следующим чертежам, на которых:

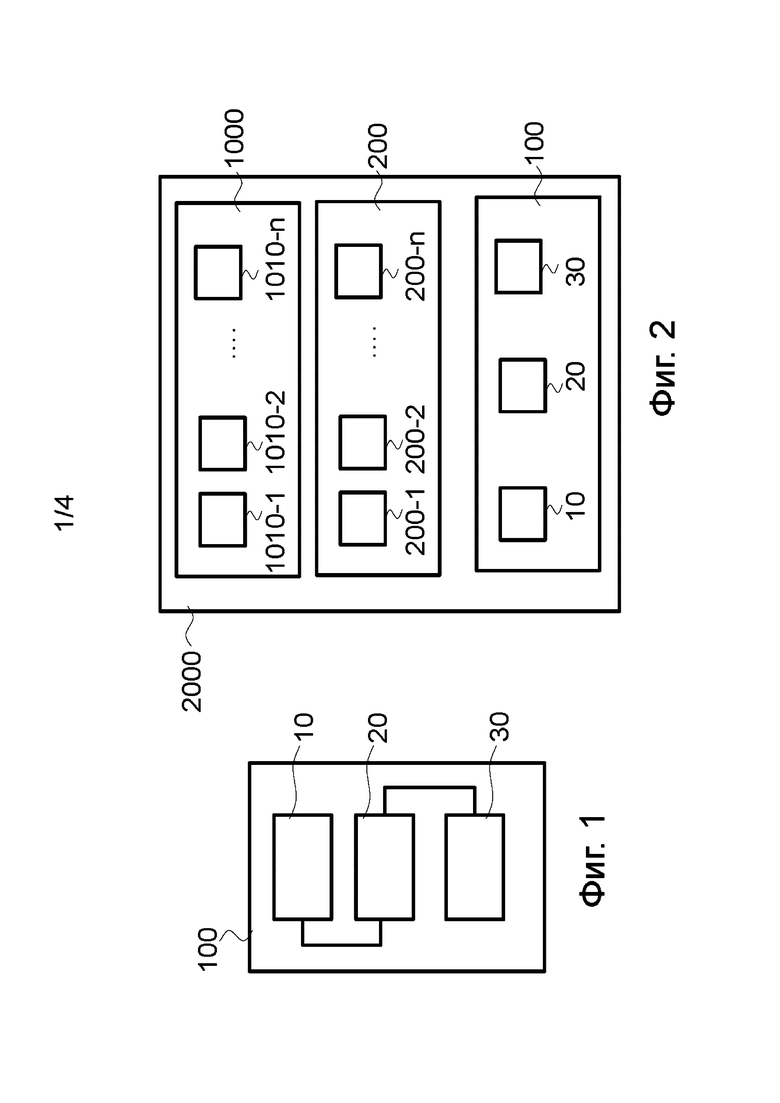

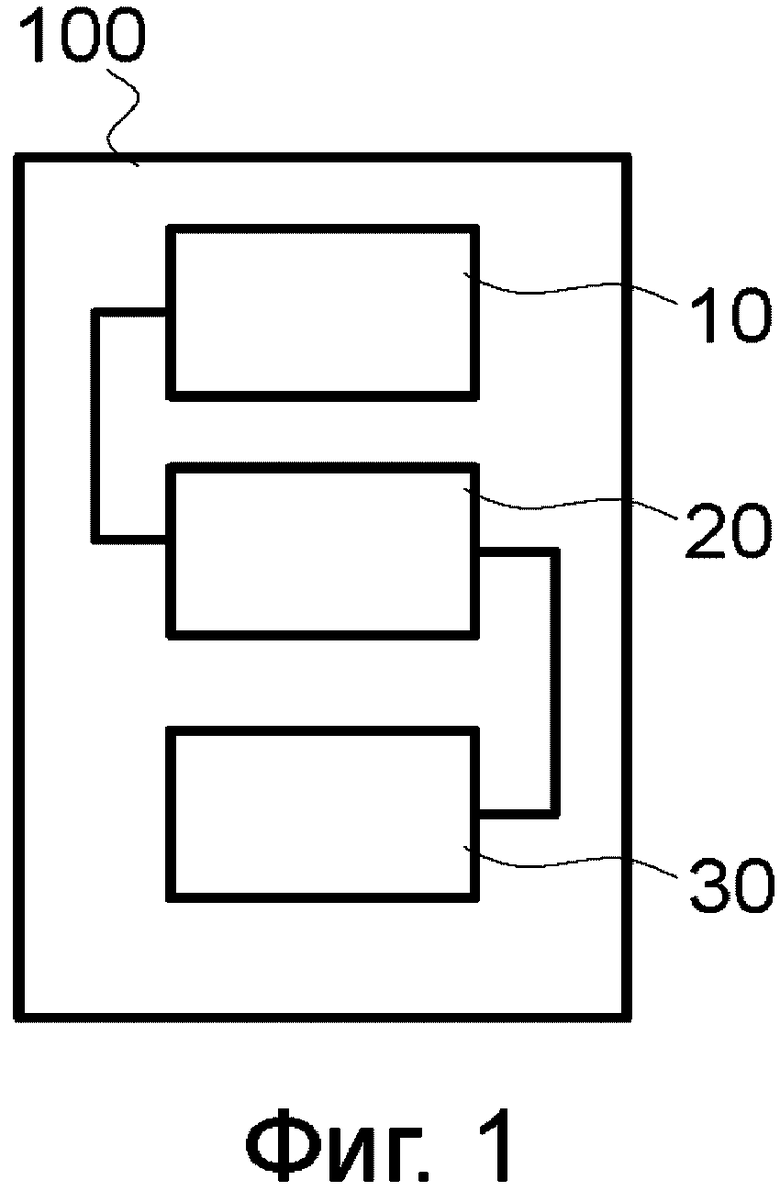

Фиг. 1 представляет упрощенную схему системы для синхронизации памяти в многоядерной системе согласно одному из вариантов настоящего изобретения;

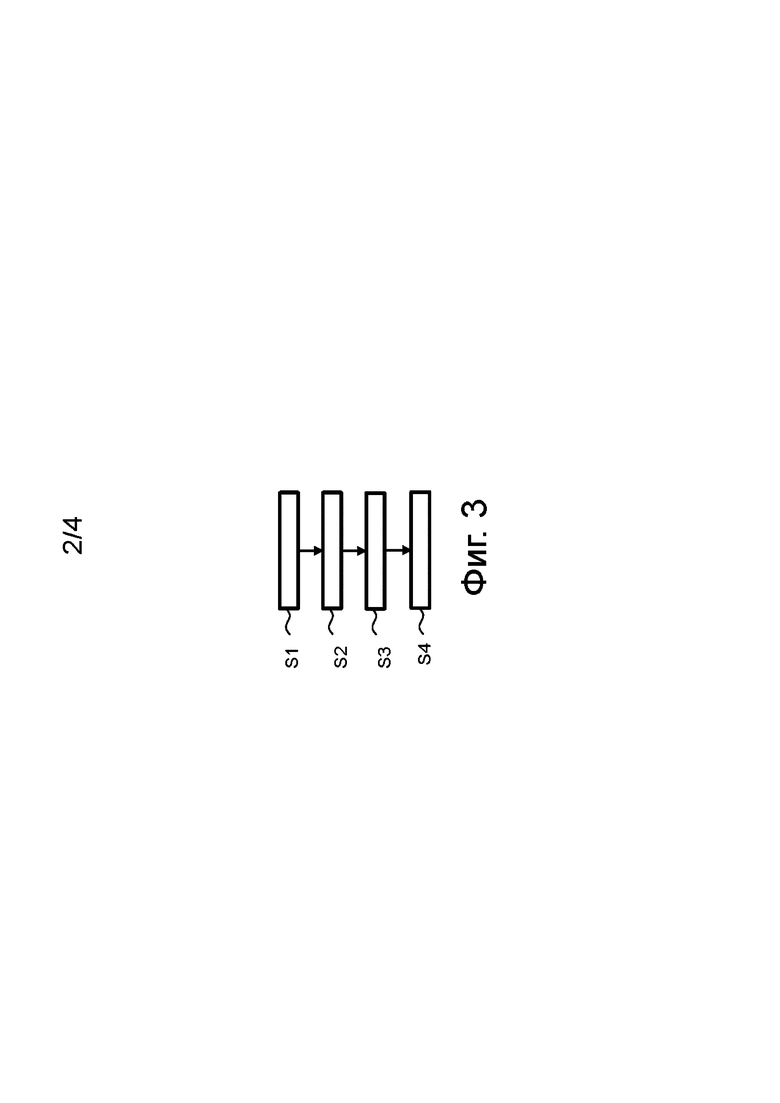

Фиг. 2 представляет упрощенную схему базы данных, содержащей систему для синхронизации памяти в многоядерной системе согласно одному из вариантов настоящего изобретения;

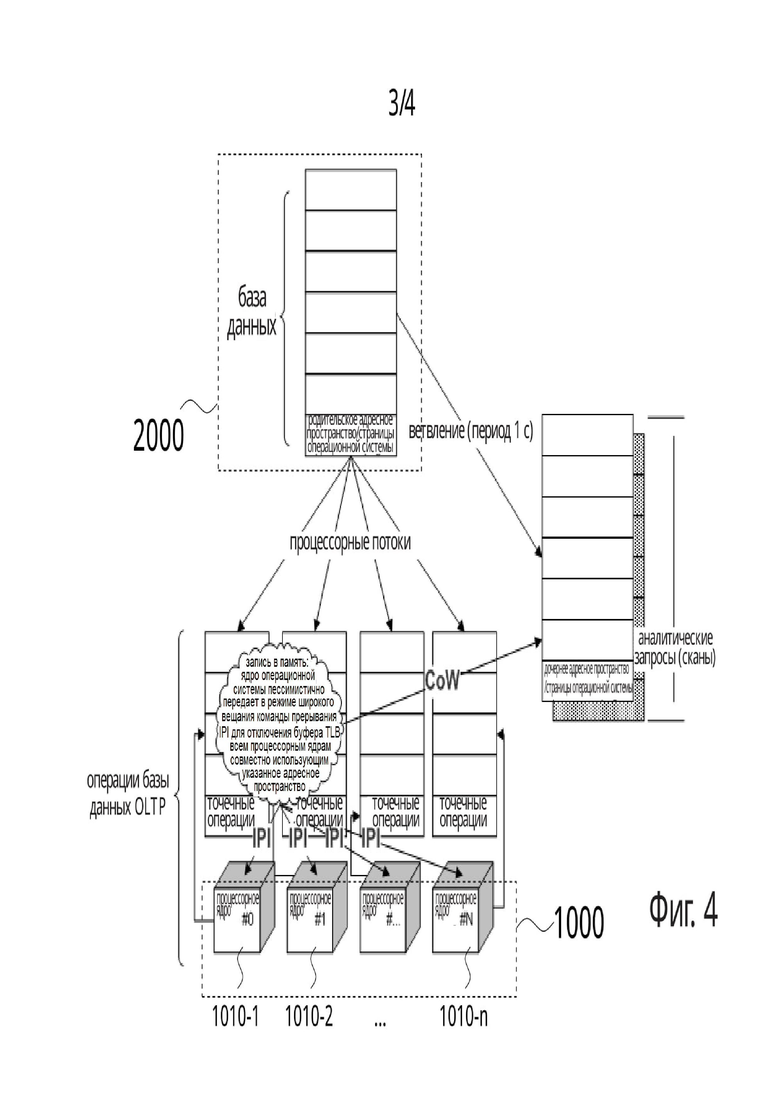

Фиг. 3 представляет упрощенную логическую схему способа синхронизации памяти согласно одному из вариантов настоящего изобретения;

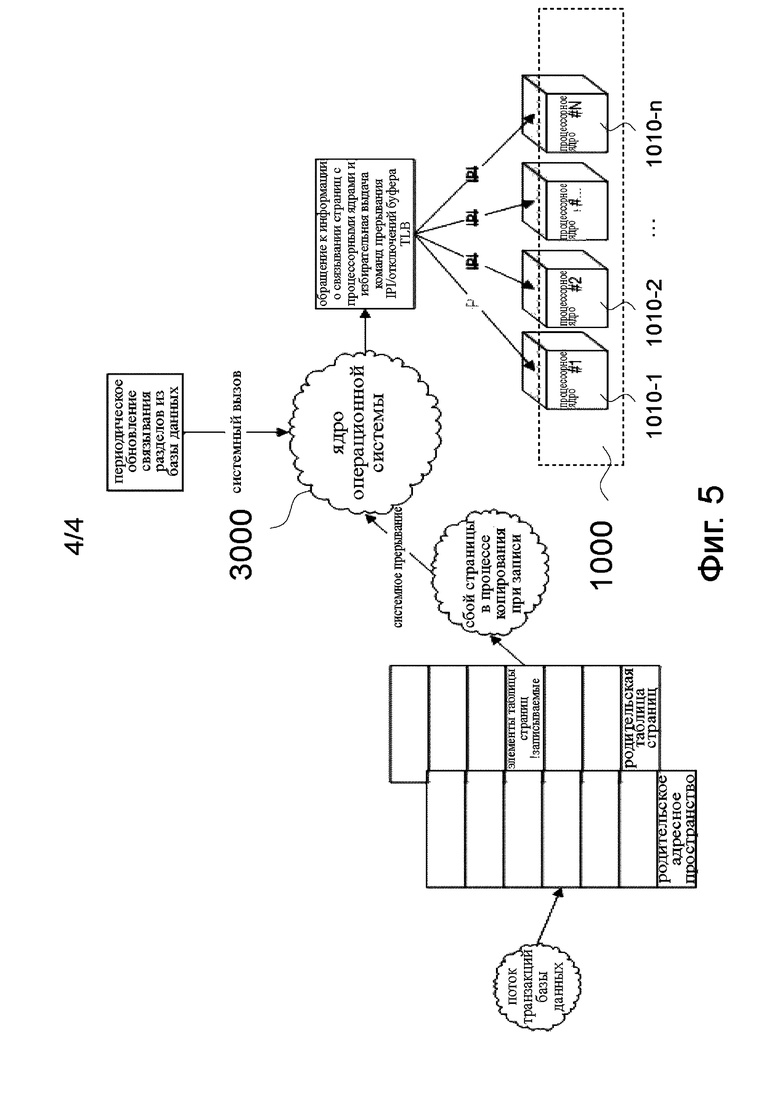

Фиг. 4 представляет упрощенную схему того, как ядро операционной системы выдает команды прерывания IPI для отключения буфера TLB всем аппаратным процессорным ядрам, совместно использующим родительское адресное пространство согласно одному из вариантов настоящего изобретения; и

Фиг. 5 представляет упрощенную схему того, как ядро операционной системы, обрабатывает сбой копирования при записи (CoW) страницы согласно одному из вариантов настоящего изобретения.

Осуществление изобретения

На прилагаемых чертежах идентичные позиционные обозначения указывают идентичные или по меньшей мере эквивалентные элементы, части, блоки или этапы. Кроме того, следует отметить, что все прилагаемые чертежи выполнены не в масштабе.

Технические решения вариантов настоящего изобретения описаны в дальнейшем ясно и полно с подробными ссылками на прилагаемые чертежи в вариантах настоящего изобретения.

Очевидно, что рассмотренные здесь варианты являются лишь некоторыми, но не всеми, вариантами настоящего изобретения. Все другие варианты, полученные специалистами в рассматриваемой области на основе описанных здесь вариантов без особых творческих усилий, попадут в объем защиты настоящего изобретения.

На Фиг. 1 представлена упрощенная схема системы для синхронизации памяти в многоядерной системе согласно одному из вариантов настоящего изобретения.

Фиг. 1 показывает систему 100 для синхронизации памяти в многоядерной системе 1000, эта система 100 содержит: назначающий модуль 10, отображающий модуль 20 и интерфейсный модуль 30.

Назначающий модуль 10 может быть конфигурирован для назначения по меньшей мере одного раздела 200-1,..., 200-n памяти по меньшей мере одному процессорному ядру 1010-1,...,1010-n в многоядерной системе 1000.

Отображающий модуль 20 может быть конфигурирован для передачи информации для отключения буфера быстрого преобразования адресов в многоядерной системе 1000 с использованием передачи команды прерывания по меньшей мере одному процессорному ядру 1010-1,...,1010-n в многоядерной системе 1000, если элемент таблицы страниц, ассоциированный с разделом 200-1,..., 200-n памяти, назначенным указанному по меньшей мере одному процессорному ядру 1010-1,...,1010-n, оказался модифицирован.

Отображающий модуль 20 может генерировать информацию отображения, которая будет использована во время отключения буфера TLB посредством ядра 3000 операционной системы, осуществляющего отключение буфера TLB.

Интерфейсный модуль 30 может быть конфигурирован для создания интерфейса к назначающему модулю 10 из пользовательского пространства.

На Фиг. 2 представлена упрощенная схема базы данных, содержащей систему для синхронизации памяти в многоядерной системе согласно одному из вариантов настоящего изобретения.

На Фиг. 2 показана упрощенная схема базы 2000 данных, содержащей многоядерную систему 1000, имеющую по меньшей мере одно процессорное ядро 1010-1,...,1010-n; систему 200 памяти, имеющую по меньшей мере один раздел 200-1,..., 200-n памяти; и систему 100 для синхронизации памяти в многоядерной системе.

Система 100 может содержать назначающий модуль 10, отображающий модуль 20 и интерфейсный модуль 30.

На Фиг. 3 представлена упрощенная логическая схема способа синхронизации памяти согласно одному из вариантов настоящего изобретения.

На первом этапе способа назначают, S1, по меньшей мере один раздел 200-1,..., 200-n памяти по меньшей мере одному процессорному ядру 1010-1,...,1010-n в многоядерной системе 1000 с использованием назначающего модуля 10.

На втором этапе способа, осуществляют, S2, отключение буфера быстрого преобразования адресов в многоядерной системе 1000 с использованием отображающего модуля 20.

На третье этапе способа, передают, S3, команду прерывания по меньшей мере одного процессорного ядра 1010-1,...,1010-n в многоядерной системе 100, если элемент таблицы страниц, ассоциированный с разделом 200-1,..., 200-n памяти, назначенным указанному по меньшей мере одному процессорному ядру 1010-1,...,1010-n, оказался модифицирован.

На четвертом этапе способа, создают, S4, интерфейс между назначающим модулем 10 и пользовательским пространством с использованием интерфейсного модуля 30.

На Фиг. 4 представлена упрощенная схема того, как ядро операционной системы выдает команды прерывания IPI для отключения буфера TLB всем аппаратным процессорным ядрам, совместно использующим родительское адресное пространство согласно одному из вариантов настоящего изобретения; и

Фиг. 4 показывает, как ядро 3000 операционной системы выдает команды прерывания IPI для отключения буфера TLB всем аппаратным процессорным ядрам, совместно использующим родительское адресное пространство, когда операция обработки транзакций OLTP предпринимает попытку обновить память. Это происходит во время обработки сбоя страницы в процессе копирования при записи (CoW), выполняемой операционной системой, вызванной командой исключения, поступившей от блока защиты в составе аппаратного блока MMU.

Согласно примеру варианта настоящего изобретения в процессе реализации могут быть внесены модификации или усовершенствования в ядро 3000 операционной системы с целью: создать требуемый интерфейс к пользовательскому пространству/приложениям базы данных, управляющим связыванием разделов памяти с конкретными процессорными (CPU) ядрами, для целей отключения буфера TLB (например, путем введения группы новых системных вызовов в ядро операционной системы).

Следующее преимущество обусловлено соответствующим усилением относящихся к делу функций отключения буфера TLB в ядре 3000 операционной системы, которые (функции) вовлечены в обработку сбоев страниц в процессе копирования страниц при записи, с целью ознакомления с информацией, переданной из базы 2000 данных в ядро 3000 операционной системы посредством новой группы системных вызовов.

Кроме того, привлечение указанного механизма базой 2000 данных улучшено, посредством обеспечения того, что каждый поток транзакций OLTP оперирует на одном или нескольких разделах памяти, и посредством передачи этой информации в ядро 3000 операционной системы с использованием новой группы системных вызовов.

Согласно одному из примеров вариантов настоящего изобретения в сценарии, в котором встроенная в память гибридная база 2000 данных транзакций/аналитической обработки (OLTP/OLAP) использует механизм создания мгновенных копий в процессе копирования при записи (CoW) на основе блока MMU, ядро 3000 операционной системы по необходимости передает в режиме вещания запросы отключения буфера TLB посредством передачи команд прерывания IPI всем аппаратным процессорным ядрам 1010-1,...,1010-n, совместно использующим родительское адресное пространство, посредством потоков, когда транзакция OLTP предпринимает попытку обновить какую-либо часть памяти, мгновенную копию каковой формируют в текущий момент (во время обработки сбоев страниц в процессе копирования при записи (CoW)), как показано на Фиг. 4.

Согласно одному из примеров вариантов настоящего изобретения в системе может быть инсталлирована процедура управляемого диспетчирования команд прерывания IPI для отключении буфера TLB, на которое влияет пользовательское пространство. Указанные база данных/приложение ответственны за уменьшение группы процессорных ядер 1010-1,...,1010-n, которые принимают команды прерывания IPI, путем периодической (или по требованию) генерации ограничивающей процессорной (CPU) маски передачи ее в ядро операционной системы с помощью группы вновь введенных системных вызовов.

Согласно одному из примеров вариантов настоящего изобретения процессорная (CPU) маска представляет собой структуру данных, указывающую, какие процессорные (CPU) ядра 1010-1,...,1010-n из состава многоядерной системы 1000 следует включить в текущий процесс, а какие следует исключить, посредством связывания. При этом функции, связанные с отключением ядра операционной системы модифицируют для привлечения сформированной процессорной (CPU) маски с целью избирательного диспетчерования команд прерывания IPI в процессе обработки сбоев страниц в ходе копирования при записи (CoW).

Согласно одному из примеров вариантов настоящего изобретения база 2000 данных или какое-либо приложение ответственно за обеспечение того, что потоки этого приложения в пользовательском пространстве (выполняющие транзакции OLTP) учитывают информацию о связывании, переданную в ядро 3000 операционной системы, путем ограничений их операций на соответствующей области памяти и оперирования от конкретных процессорных ядер 1010-1,...,1010-n, связанных с этой областью.

Системные вызовы, управляющие командами прерывания IPI, отключающими буфер TLB, оперируют путем специфицирования блока памяти, идентифицированного его стартовым виртуальным адресом памяти, и путем создания процессорной (CPU) маски, идентифицирующей, какие процессорные ядра 1010-1,...,1010-n в многоядерной системе 1000 должны принимать команды прерывания IPI для отключения буфера TLB, когда происходит сбой страницы в процессе копирования при записи (CoW) в конкретном блоке памяти.

Согласно одному из примеров вариантов настоящего изобретения операционная система автоматически определяет блок памяти (здесь нет необходимости в передаче пары адрес-длина с точки зрения пользовательского пространства), поскольку операционная система сама осуществляет внутреннее отслеживание выделенных областей и может легко найти место заключающего блока памяти, которому принадлежит поступивший виртуальный адрес памяти.

Например, в ядро операционной системы могут быть введены следующие системные вызовы:

• mem_region_set_cpumask(void *addr, cpumask_t *cpumask);

• mem_region_get_cpumask(void *addr, cpumask_t *cpumask);

Такое внутреннее отслеживание находит место, где находится заключающая область памяти, куда указывает поступивший виртуальный адрес памяти (addr), обращаясь к некоторой структуре во внутренней памяти ядра операционной системы, сохраняющей данные о распределении памяти для каждого процесса.

Согласно одному из примеров вариантов настоящего изобретения указанную внутреннюю структуру, соответствующую выделенному блоку памяти также усиливают с целью сохранить структуру процессорной (CPU) маски, поступившую в составе системных вызовов.

Согласно одному из примеров вариантов настоящего изобретения системные вызовы, после определения местонахождения конкретной структуры для заключающей области памяти, копируют процессорную (CPU) маску из пользовательского пространства памяти в пространство памяти ядра операционной системы (или из пространства памяти ядра операционной системы в пользовательское пространство) для вызова mem_region_set_cpumask (и mem_region_get_cpumask) соответственно. В случае вызова mem_region_set_cpumask, процессорную (CPU) маску копируют в пространство ядра операционной системы и сохраняют в структуре, которая идентифицирует выделенный блок памяти.

На Фиг. 5 представлена упрощенная схема того, как ядро операционной системы, обрабатывает сбой копирования при записи (CoW) страницы согласно одному из вариантов настоящего изобретения.

На Фиг. 5 показано, что ядро 3000 операционной системы, во время обработки сбоя страницы в процессе копирования при записи (CoW), может привлекать информацию о связывании, поступившую ранее от базы 2000 данных (через группу новых системных вызовов), с целью выдавать команды прерывания IPI для отключения буфера TLB избирательно вместо того, чтобы передавать их в режиме вещания каждому из имеющихся и доступных процессорных ядер 1010-1,...,1010-n, которые совместно используют рассматриваемое адресное пространство.

Согласно одному из примеров вариантов настоящего изобретения во время обработки сбоя страницы в процессе копирования при записи ядро 3000 операционной системы имеет достаточно информации (обработка аппаратных исключений дает адрес сбоя) для того, чтобы определить местонахождение заключающей области памяти и получить процессорную (CPU) маску, ассоциированную с этой областью.

Согласно одному из примеров вариантов настоящего изобретения ядро 3000 операционной системы может после этого использовать процессорную (CPU) маску с целью избирательно выдавать команды прерывания IPI при отключении буфера TLB, направленные только процессорным ядрам 1010-1,...,1010-n, указанным в соответствующей процессорной (CPU) маске, как показано на Фиг. 5.

По умолчанию, если от базы данных не поступила никакая процессорная (CPU) маска, ядро операционной системы обрабатывает отключение буфера TLB путем передачи в режиме широкого вещания команд прерывания IPI всем процессорным ядрам 1010-1,...,1010-n, совместно использующим адресное пространство, в предположении, что из пользовательского пространства/базы данных не поступило никакой информации, которая могла бы быть привлечена для сужения множества процессорных ядер 1010-1,...,1010-n для приема отключений буфера TLB в случае сбоя страницы в процессе копирования при записи (CoW).

Согласно одному из примеров вариантов настоящего изобретения, в случае, когда приложению/базе данных нужно вернуться назад к поведению операционной системы «по умолчанию» после того, как была передана процессорная (CPU) маска посредством соответствующего системного вызова, это сообщение/база данных может выдать «нулевую» процессорную (CPU) маску, чтобы восстановить поведение по умолчанию.

Этот вариант реализации изобретения служит только для целей иллюстрации. Такая же схема может быть осуществлена посредством разного рода интерфейсов и семантики, направленных от базы данных/приложения в ядро 3000 операционной системы.

Согласно одному из примеров вариантов настоящего изобретения связанные с управлением памятью вызовы ядра операционной системы (например, mmap или новый системный вызов) могут быть расширены с целью аккомодации параметра, указывающего процессорную (CPU) маску (т.е. связывание области памяти с группой процессорных ядер 1010-1,...,1010-n).

Другой пример должен представлять собой модификацию и расширение существующих вызовов ядра операционной системы (например, mmap), введение нового флага (например, MAP_BIND), каковой должен указывать в неявном виде, что область памяти, которая должна быть выделена этим вызовом, должна быть связана с процессором CPU, вызванным посредством этого системного вызова (например, процессором CPU потока, выделившего эту область памяти), для целей прерываний IPI при отключении буфера TLB.

Рассмотренный вариант, впрочем, предоставляет больше гибкости, поскольку он позволяет в явном виде связывать области памяти с процессорными ядрами 1010-1,...,1010-n и модифицировать это связывание во время работы системы 200 базы данных.

Настоящее изобретение также поддерживает компьютерный программный продукт, содержащий выполняемый компьютером код или выполняемые компьютером команды, при выполнении которых по меньшей мере один компьютер осуществляет описанные здесь этапы.

Многие альтернативы, модификации и вариации будут очевидны специалистам в рассматриваемой области в свете изложенных выше положений. Безусловно, специалисты в рассматриваемой области легко поймут, что существуют многочисленные приложения настоящего изобретения и помимо тех, которые описаны здесь.

Тогда как настоящее изобретение было описано со ссылками на один или несколько конкретных вариантов, специалисты в рассматриваемой области понимают, что могут быть сделаны многочисленные изменения, не отклоняясь от объема настоящего изобретения. Поэтому должно быть понятно, что настоящее изобретение может быть практически осуществлено и другим способом, чем конкретно описано здесь, не выходя за пределы объема прилагаемой Формулы изобретения и ее эквивалентов.

В этой Формуле изобретения слово «содержащий» не исключает других элементов или этапов, а неопределенный артикль "a" или "an" не исключает множественного числа. Один процессор или другой блок может выполнять функции нескольких объектов, упомянутых в Формуле изобретения.

Тот факт, что некоторые меры упоминаются в отличных один от другого зависимых пунктах Формулы изобретения, не означает, что сочетание этих мер не может быть с успехом использовано. Компьютерная программа может быть записана или распределена на подходящем носителе, таком как оптический носитель информации или твердотельный носитель информации, поставляемый вместе или в качестве части другой аппаратуры, но может быть также распределена в других формах, таких как через Интернет или другую проводную или беспроводную телекоммуникационную систему.

Изобретение относится к средствам синхронизации памяти в многоядерной системе. Техническим результатом является расширение арсенала средств синхронизации памяти в многоядерной системе. Система содержит: модуль назначения для назначения по меньшей мере одного раздела памяти по меньшей мере одному процессорному ядру в многоядерной системе; модуль отображения для предоставления информации для отключения буфера быстрого преобразования адресов в многоядерной системе путем передачи команды прерывания по меньшей мере одному ядру в многоядерной системе, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным этому по меньшей мере одному процессорному ядру, модифицирован; и интерфейсный модуль для создания интерфейса пользовательского пространства с модулем назначения. 4 н. и 11 з.п. ф-лы, 5 ил.

1. Система синхронизации памяти в многоядерной системе, содержащая:

модуль назначения для назначения по меньшей мере одного раздела памяти по меньшей мере одному процессорному ядру в многоядерной системе;

модуль отображения для предоставления информации для отключения буфера быстрого преобразования адресов в многоядерной системе посредством передачи команды прерывания по меньшей мере одному ядру в многоядерной системе, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным этому по меньшей мере одному процессорному ядру, оказался модифицирован; и

интерфейсный модуль для создания интерфейса пользовательского пространства с модулем назначения.

2. Система по п. 1, в которой

модуль отображения дополнительно выполнен с возможностью предоставления информации для отключения буфера быстрого преобразования адресов во время копирования при записи страницы, совместно использующей по меньшей мере один раздел памяти.

3. Система по одному из пп. 1 и 2, в которой

интерфейсный модуль дополнительно выполнен с возможностью создания интерфейса между модулем назначения и пользовательским пространством с использованием набора системных вызовов для управления связыванием по меньшей мере одного раздела памяти по меньшей мере с одним процессорным ядром.

4. Система по п. 3, в которой

интерфейсный модуль дополнительно выполнен с возможностью адаптации отключения буфера быстрого преобразования адресов посредством информации, принятой с использованием набора системных вызовов.

5. База данных, содержащая

многоядерную систему, включающую в себя по меньшей мере одно процессорное ядро;

систему памяти, включающую в себя по меньшей мере один раздел памяти; и

систему синхронизации памяти в многоядерной системе, содержащую:

модуль назначения для назначения по меньшей мере одного раздела памяти по меньшей мере одному процессорному ядру из состава многоядерной системы;

модуль отображения для предоставления информации для отключения буфера быстрого преобразования адресов в многоядерной системе посредством передачи команды прерывания по меньшей мере одному процессорному ядру в многоядерной системе, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным этому по меньшей мере одному процессорному ядру, оказался модифицирован; и

интерфейсный модуль для создания интерфейса пользовательского пространства с модулем назначения.

6. База данных по п. 5, характеризующаяся тем, что

представляет собой гибридную базу данных для интерактивной обработки транзакций и интерактивной аналитической обработки.

7. База данных по п. 6, характеризующаяся тем, что

выполнена с возможностью осуществления интерактивной обработки транзакций посредством обеспечения того, что по меньшей мере один поток интерактивной обработки транзакций оперирует с одним или более разделами из совокупности, содержащей по меньшей мере один раздел памяти.

8. База данных по любому из пп. 5–7, характеризующаяся тем, что

выполнена с возможностью осуществления управляемой диспетчеризации отключения буфера быстрого преобразования адресов с использованием структуры данных, указывающей, какое ядро из совокупности, содержащей по меньшей мере одно процессорное ядро, связано с каким разделом из совокупности, содержащей по меньшей один раздел памяти.

9. База данных по п. 5, в которой

интерфейсный модуль выполнен с возможностью передачи информации о связывании по меньшей мере одного раздела памяти по меньшей мере с одним процессорным ядром.

10. База данных по п. 9, в которой

интерфейсный модуль выполнен с возможностью адаптации отключения буфера быстрого преобразования адресов посредством информации, принятой с использованием набора системных вызовов.

11. Способ синхронизации памяти в многоядерной системе, содержащий этапы, на которых:

назначают (S1) по меньшей мере один раздел памяти по меньшей мере одному процессорному ядру в многоядерной системе с использованием модуля назначения;

осуществляют (S2) отключение буфера быстрого преобразования адресов в многоядерной системе с использованием модуля отображения посредством передачи (S3) команды прерывания по меньшей мере одному процессорному ядру многоядерной системы, если элемент таблицы страниц, ассоциированный с разделом памяти, назначенным по меньшей мере одному процессорному ядру, модифицирован; и

создают (S4) интерфейс пользовательского пространства с модулем назначения с использованием интерфейсного модуля.

12. Способ по п. 11, в котором

этап осуществления (S2) отключения буфера быстрого преобразования адресов осуществляется в процессе копирования при записи страницы, совместно использующей по меньшей мере один раздел памяти.

13. Способ по п. 11 или 12, в котором

этап реализации (S2) отключения буфера быстрого преобразования адресов осуществляется с использованием набора системных вызовов для управления связыванием по меньшей мере одного раздела памяти по меньшей мере с одним процессорным ядром.

14. Способ по п. 13, в котором

процедура отключения буфера быстрого преобразования адресов адаптируется посредством информации, принятой с использованием набора системных вызовов.

15. Машиночитаемый носитель информации, хранящий компьютерную программу, содержащую программный код, вызывающий, при его исполнении компьютером, выполнение способа по п. 12 или 14.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| ИЕРАРХИЧЕСКАЯ ИНФРАСТРУКТУРА ПЛАНИРОВАНИЯ РЕЗЕРВИРОВАНИЯ РЕСУРСОВ | 2008 |

|

RU2481618C2 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ УПРЕЖДАЮЩЕГО УПРАВЛЕНИЯ ПАМЯТЬЮ | 2003 |

|

RU2348067C2 |

Авторы

Даты

2019-03-06—Публикация

2015-08-03—Подача