ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к устройству преобразования мощности с резонансной нагрузкой, которое подает сигнал напряжения прямоугольной формы на резонансную нагрузку, такую как схема индукционного нагрева.

УРОВЕНЬ ТЕХНИКИ

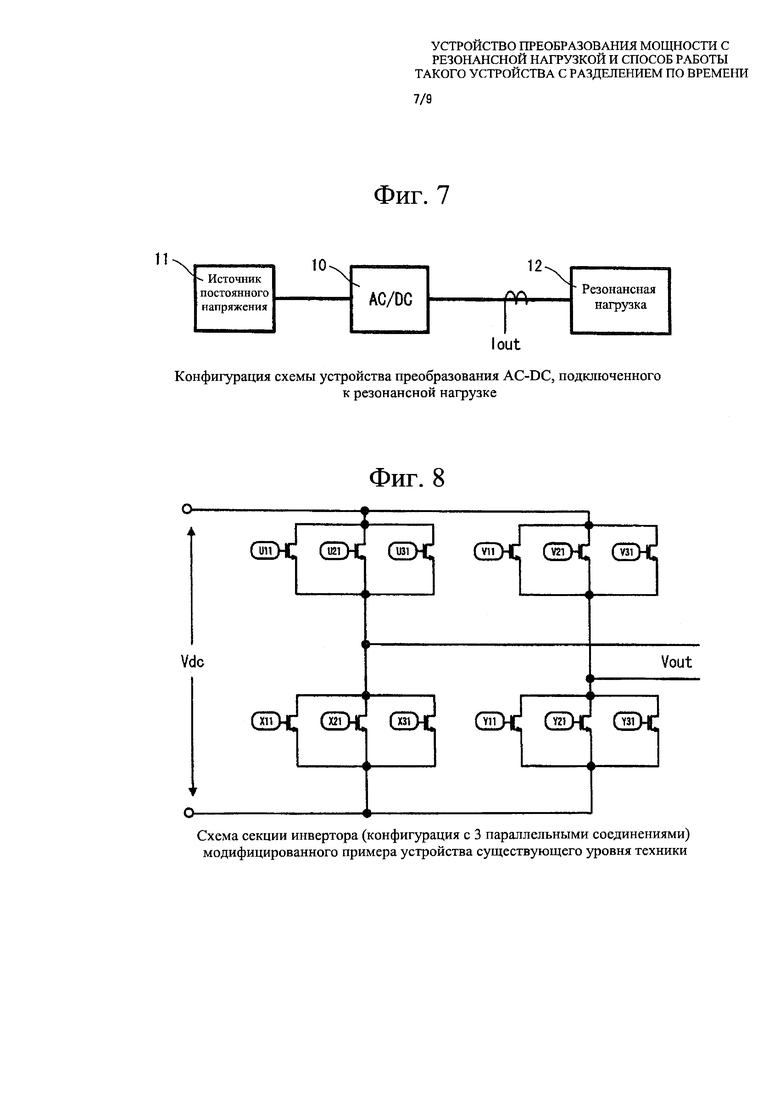

[0002] На фиг. 7 показана конфигурация схемы устройства преобразования мощности с резонансной нагрузкой (устройство преобразования AC-DC (переменного тока в постоянный)), соединенное с резонансной нагрузкой. На фиг. 7 показано, что устройство 10 преобразования AC-DC содержит однофазный инвертор, вход которого соединен с источником 11 постоянного тока, а выход - с резонансной нагрузкой 12, такой как схема индукционного нагрева. В результате двухпозиционного управления (ON/OFF, Открыт/Закрыт) каждым переключающим элементом этого однофазного инвертора устройство 10 преобразования AC-DC выводит сигнал напряжения прямоугольной формы резонансной частоты на резонансную нагрузку 12 (устройство 10 преобразования AC-DC выводит сигнал напряжения прямоугольной формы на резонансную нагрузку 12 на резонансной частоте).

[0003] В том случае если резонансная нагрузка 12 представляет собой схему индукционного нагрева, устройство 10 преобразования AC-DC конфигурируется как устройство преобразования AC-DC с резонансной нагрузкой для индукционного нагрева (инвертор резонансного типа с индукционным нагревом).

[0004] Это устройство преобразования AC-DC с резонансной нагрузкой для индукционного нагрева конфигурируется таким образом, чтобы переменный ток, сгенерированный путем двухпозиционного управления каждым переключающим элементом однофазного инвертора, протекал в резонансной схеме LC, сформированной катушкой индуктивности и конденсатором, вихревые токи протекали в нагревательном элементе (электрическом проводнике) под действием поля переменного тока, которое генерируется в результате протекания переменного тока, подаваемого на нагревательный элемент (электрический проводник), и резонансная схема LC нагревалась изнутри посредством джоулевой теплоты, сгенерированной потоком вихревого тока.

[0005] Что касается схемы индукционного нагрева в виде резонансной нагрузки, подключенной к выходу устройства преобразования мощности с резонансной нагрузкой (например, устройства 10 преобразования AC-DC, показанного на фиг. 7), известно, что чем выше частота, тем в большей степени уменьшается глубина проникновения тока.

[0006] Поскольку трубное соединение, получаемое контактной электросваркой методом сопротивления (соединение, получаемое электросваркой методом сопротивления для формирования трубы), выполняется путем поверхностной закалки (поверхностного упрочнения), требуется, чтобы устройство преобразования AC-DC с резонансной нагрузкой, используемой для индукционного нагрева, могло вырабатывать напряжение высокой частоты.

[0007] С другой стороны, у переключающего элемента устройства преобразования AC-DC с резонансной нагрузкой, используемого для индукционного нагрева, существует верхний предел задающей частоты. Таким образом, устройству преобразования AC-DC с резонансной нагрузкой свойственна проблема, связанная с отсутствием реагирования на частоту напряжения, большую задающей частоты переключающего элемента.

[0008] На современном уровне техники решение этой проблемы, например, предложено с помощью системы инвертора с резонансной нагрузкой, раскрытой в патентном документе 1. Как показано на фиг. 3 и описано в параграфах [0007]-[0009] этого патентного документа 1, путем разделения однофазного инвертора на n секций (N параллельных соединений, составляющих однофазный инвертор) переключающий элемент может управляться в течение периода 1/N. Вследствие этого задающая частота переключающего элемента может уменьшаться до значения, обратно пропорционального количеству параллельных соединений, с учетом требуемой резонансной частоты.

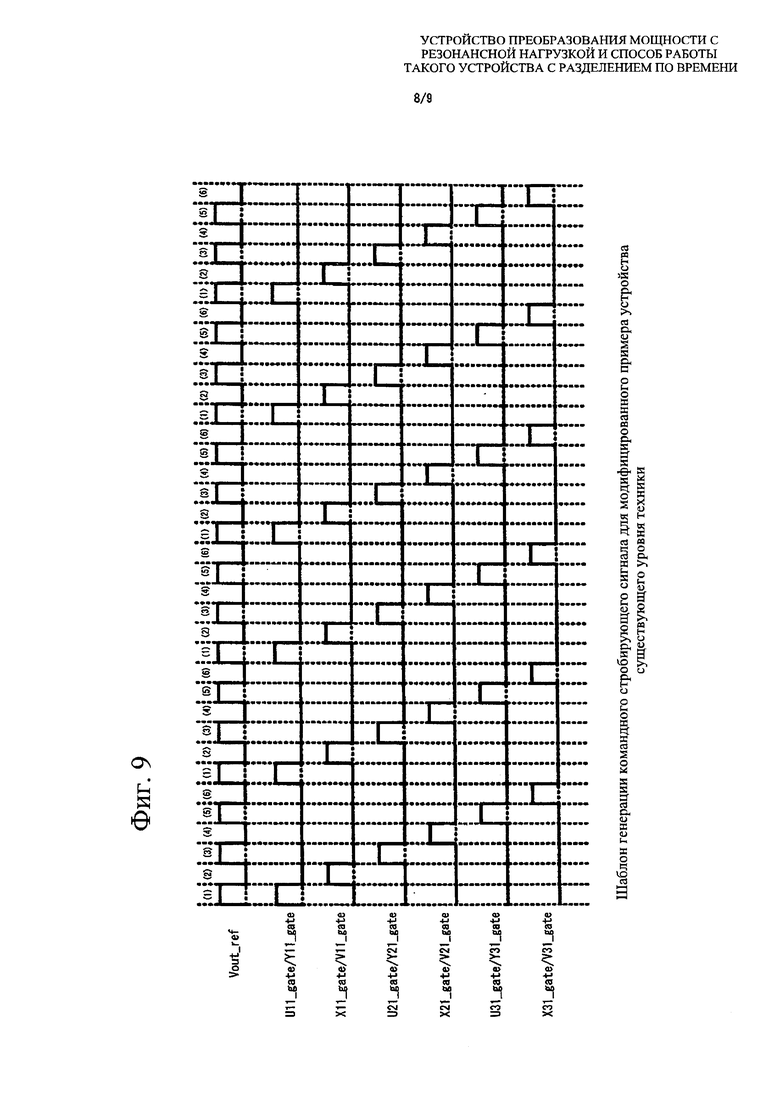

[0009] Кроме того, в качестве модифицированного примера системы инвертора с резонансной нагрузкой, раскрытой в патентном документе 1, как показано, например, на фиг. 8, может рассматриваться схема, в которой N переключающих элементов (например, IGBT, биполярных транзисторов с изолированным затвором) в одном плече однофазного инвертора соединяются параллельно.

[0010] На фиг. 8 показано устройство преобразования AC-DC с резонансной нагрузкой, например устройство, используемое для устройства 10 преобразования AC-DC с резонансной нагрузкой, изображенного на фиг. 7. Устройство преобразования AC-DC с резонансной нагрузкой содержит входную секцию Vdc линии постоянного тока, выходную секцию Vout сигнала напряжения прямоугольной формы и однофазный инвертор, в котором N переключающих элементов (в данном случае 3: U11, U21, U31, V11, V21, V31, X11, Х21, С31 и Y11, Y21, Y31) в каждом плече соединены параллельно.

[0011] Как показано на фиг. 8, путем увеличения количества N параллельно соединенных переключающих элементов в одном плече, так же как и в системе инвертора с резонансной нагрузкой, раскрытой в патентном документе 1, возможно уменьшить частоту переключения для одного переключающего элемента.

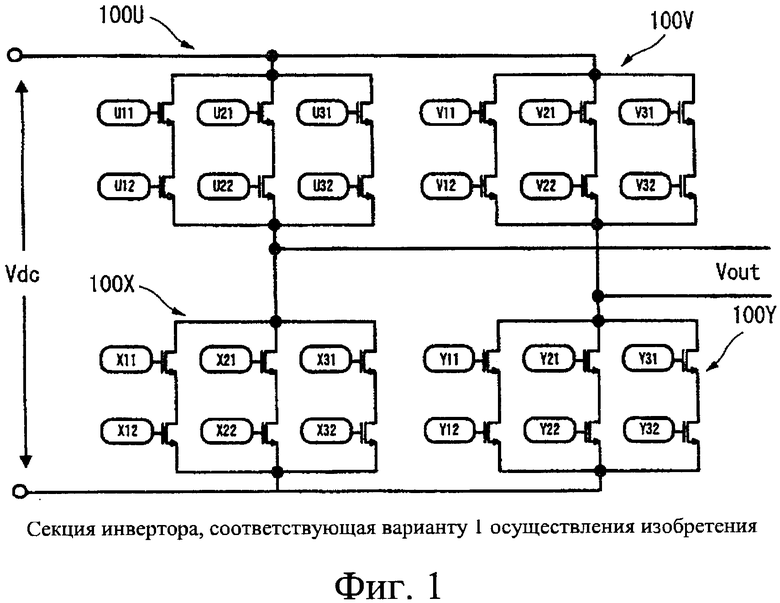

[0012] Для каждого переключающего элемента, показанного на фиг. 8, используется двухпозиционное управление в соответствии с показанным на фиг. 9 шаблоном генерации командного стробирующего сигнала.

[0013] Показанный на фиг. 9 шаблон генерации командного стробирующего сигнала формируется из следующих компонентов:

тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом,

стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate) с периодом в 6 тактов (один цикл), в течение которых отпирающий сигнал выводится в 1 такте, а запирающий сигнал выводится в течение 5 тактов,

стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U11_gate/Y11_gate,

стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала X11_gate/V11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X11_gate/V11_gate,

стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала U21_gate/Y21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U21_gate/Y21_gate,

стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), который задержан на 1 такт относительно стробирующего командного сигнала X21_gate/V21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X21_gate/V21_gate, и

стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), который задержан на 1 такт относительно стробирующего командного сигнала U31_gate/Y31_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U31_gate/Y31_gate.

[0014] Для каждого переключающего элемента, показанного на фиг. 8, используется двухпозиционное управление посредством стробирующих командных сигналов U11_gate/Y11_gate … X31_gate/V31_gate с повторяющимися шаблонами (1)-(6), изображенными на фиг. 10A-10F.

[0015] Взаимосвязь с выходным током при управлении каждым переключающим элементом, изображенным на фиг. 8, посредством показанного на фиг. 9 шаблона генерации командного стробирующего сигнала иллюстрируется на фиг. 10A-10F.

[0016] Фиг. 10A-10F соответствуют шаблонам (1)-(6), показанным на фиг. 9. На фиг. 10A-10F переключающий элемент, управляемый сигналом отпирания команды стробирования, указывается меткой "ON", и маршрут выходного тока Iout, протекающего через этот переключающий элемент и нагрузку, показан стрелкой.

[0017] На основе фиг. 9 и 10A-10F можно понять, что с помощью последовательного переключения каждого переключающего элемента посредством шаблонов (1)-(6) для одного переключающего элемента можно получить коэффициент частоты переключения (задающей частоты), равный 1/3 (1/N).

СПИСОК ЦИТИРУЕМЫХ ДОКУМЕНТОВ

ПАТЕНТНЫЙ ДОКУМЕНТ

[0018]

Патентный документ 1: Публикация нерассмотренной патентной заявки №2004-510400 Японии

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0019] Как было описано выше, частота переключения может составлять 1/N в системе, раскрытой в патентном документе 1, и в схемной конфигурации, показанной на фиг. 10A-10F. Однако, на фиг. 9, где изображен шаблон генерации командного стробирующего сигнала, показано, что поскольку длительность импульса каждого стробирующего командного сигнала U11_gate/Y11_gate … X31_gate/V31_gate составляет один такт, верхний предел выходной частоты определяется минимальной длительностью импульса, основанной на характеристиках элемента в соответствии с временем нарастания сигнала отпирания и временем спада сигнала запирания переключающего элемента.

[0020] Кроме того, для конфигурации схемы системы, раскрытой в патентном документе 1, требуются ряд проводников главной цепи (токопроводящих проводников), которые осуществляют соединение переключающих элементов между однофазными инверторами (n секций), количество которых пропорционально числу N параллельных соединений. Помимо этого, для конфигурации схемы, показанной на фиг. 10A-10F, требуется ряд проводников главной цепи (токопроводящих проводников), которые осуществляют соединения переключающих элементов в однофазном инверторе, количество которых пропорционально числу N параллельных соединений. Кроме того, для конфигурации схемы, раскрытой в патентном документе 1 и показанной на фиг. 10A-10F, требуется ряд проводников главной цепи (то есть, N параллельных соединений × 4 плеча = 4N проводников главной цепи), число которых совпадает с количеством переключающих элементов, между входной секцией Vdc напряжения линии постоянного тока и входной клеммой постоянного тока каждого переключающего элемента верхнего и нижнего плеча и между выходной секцией Vout сигнала напряжения прямоугольной формы и выходной клеммой каждого переключающего элемента верхнего и нижнего плеча. Вследствие этого возникают проблемы, связанные с возрастанием затрат на проводники главной цепи пропорционально количеству N параллельных соединений и расширением пространства для их размещения.

[0021] Кроме того, поскольку пространство размещения переключающих элементов возрастает пропорционально их количеству, а также увеличивается разность длин маршрутов проводников главной цепи, также увеличиваются изменения импеданса, связанные с длиной маршрута проводников главной цепи. Вследствие этих проблем возникает смещение позиции точки пересечения нулевой отметки током, протекающим через проводники главной цепи, и ток, проходящий схему защиты от паразитного тока (не показанную на чертеже), которая подключена к каждому переключающему элементу, возрастает, в связи с этими увеличиваются потери. Кроме того, переключающий элемент может быть выведен из строя из-за увеличения паразитного тока.

[0022] Помимо решения указанных выше проблем требуется также уменьшить частоту переключения для одного переключающего элемента.

[0023] Настоящее изобретение направлено на решение описанных выше технических проблем. Предмет настоящего изобретения, таким образом, заключается в создании устройства преобразования мощности с резонансной нагрузкой и способа работы устройства преобразования мощности с резонансной нагрузкой с разделением по времени, которые способны понизить частоту переключения каждого переключающего элемента и уменьшить количество проводников главной цепи между входной секцией Vdc напряжения линии постоянного тока и входной клеммой постоянного тока каждого переключающего элемента верхнего и нижнего плеча и между выходной секцией Vout сигнала напряжения прямоугольной формы и выходной клеммой каждого переключающего элемента верхнего и нижнего плеча.

[0024] Описанное в п. 1 устройство преобразования мощности с резонансной нагрузкой для решения вышеуказанных проблем, снабженное однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), содержит: схемы групп переключателей (100U, 100V, 100Х, 100Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (100U, 100V, 100Х, 100Y) сконфигурирована таким образом, чтобы N (N - целое число, равное 2 и более) последовательных групп, состоящих из М (М - целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи, и при этом схема групп переключателей (100U) верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента U11 и U12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента U21 и U22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента U31 и U32 соединены последовательно, и схема групп переключателей (100U) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, схема групп переключателей (100Х) нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента X11 и Х12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Х21 и Х22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Х31 и Х32 соединены последовательно, и схема групп переключателей (100Х) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, схема групп переключателей (100V) верхнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента V11 и V12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента V21 и V22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента V31 и V32 соединены последовательно, и схема групп переключателей (100V) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, и схема групп переключателей (100Y) нижнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента Y11 и Y12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Y21 и Y22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Y31 и Y32 соединены последовательно, и схема групп переключателей (100Y) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи; и контроллер, выполняющий управление переключением каждого переключающего элемента схем групп переключателей (100U, 100V, 100Х, 100Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(М×N) и снабженный генератором команды стробирования, который генерирует тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом, стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один цикл которого составляет (2 × 2 (количество М последовательных соединений) × 3 (N параллельных соединений)) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего (2 × 3 (количество N параллельных соединений) × 1 (количество М последовательных соединений - 1) + 1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего [(2 × 2 (количество М последовательных соединений) × 3 (количество N параллельных соединений)) - (2×3 (количество N параллельных соединений) × 1 (количество М последовательных соединений - 1) + 1)] тактов, стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов X11 и V11 (X11_gate/V11_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U21 и Y21 (U21_gate/Y21_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х21 и V21 (X21_gate/V21_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U31 и Y31 (U31_gate/Y31_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х31 и V31 (X31_gate/V31_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), стробирующий командный сигнал переключающих элементов X12 и V12 (X12_gate/V12_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U12 и Y12 (U12_gate/Y12_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов X12 и V12 (X12_gate/V12_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х12 и V12 (X12_gate/V12_gate), стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U22 и Y22 (U22_gate/Y22_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), стробирующий командный сигнал переключающих элементов U32 и Y32 (U32_gate/Y32_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х22 и V22 (X22_gate/V22_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), и стробирующий командный сигнал переключающих элементов Х32 и V32 (X32_gate/V32_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U32 и Y32 (U32_gate/Y32_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U32 и Y32 (U32_gate/Y32_gate), и при этом с помощью каждого сгенерированного стробирующего командного сигнала осуществляется двухпозиционное управление каждым переключающим элементом.

[0025] Способ работы с разделением по времени устройства преобразования мощности с резонансной нагрузкой, снабженного однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), описан в п. 4, и устройство преобразования мощности с резонансной нагрузкой содержит схемы групп переключателей (100U, 100V, 100Х, 100Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (100U, 100V, 100Х, 100Y) сконфигурирована таким образом, чтобы N (N - целое число, равное 2 и более) последовательных групп, состоящих из М (М - целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи, и при этом схема групп переключателей (100U) верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента U11 и U12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента U21 и U22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента U31 и U32 соединены последовательно, и схема групп переключателей (100U) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, схема групп переключателей (100Х) нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента X11 и Х12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Х21 и Х22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Х31 и Х32 соединены последовательно, и схема групп переключателей (100Х) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, схема групп переключателей (100V) верхнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента V11 и V12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента V21 и V22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента V31 и V32 соединены последовательно, и схема групп переключателей (100V) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, и схема групп переключателей (100Y) нижнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента Y11 и Y12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Y21 и Y22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Y31 и Y32 соединены последовательно, и схема групп переключателей (100Y) сконфигурирована таким образом, чтобы три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи, и контроллер, выполняющий управление переключением каждого переключающего элемента схем группы переключающих элементов (100U, 100V, 100Х, 100Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(М×N), при этом способ работы с разделением по времени включает: шаг генерации контроллером следующих сигналов: тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом, стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один цикл которого составляет (2 × 2 (количество М последовательных соединений) × 3 (N параллельных соединений)) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего (2 × 3 (количество N параллельных соединений) × 1 (количество М последовательных соединений - 1) + 1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего [(2 × 2 (количество М последовательных соединений) × 3 (количество N параллельных соединений)) - (2 × 3 (количество N параллельных соединений) × 1 (количество М последовательных соединений - 1) + 1)] тактов, стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов X11 и V11 (X11_gate/V11_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U21 и Y21 (U21_gate/Y21_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х21 и V21 (X21_gate/V21_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U31 и Y31 (U31_gate/Y31_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х31 и V31 (X31_gate/V31_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), стробирующий командный сигнал переключающих элементов Х12 и V12 (X12_gate/V12_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U12 и Y12 (U12_gate/Y12_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х12 и V12 (X12_gate/V12_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов X12 и V12 (X12_gate/V12_gate), стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U22 и Y22 (U22_gate/Y22_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), стробирующий командный сигнал переключающих элементов U32 и Y32 (U32_gate/Y32_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов Х22 и V22 (X22_gate/V22_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), и стробирующий командный сигнал переключающих элементов Х32 и V32 (X32_gate/V32_gate), который задержан на 1 такт относительно стробирующего командного сигнала переключающих элементов U32 и Y32 (U32_gate/Y32_gate) и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал переключающих элементов U32 и Y32 (U32_gate/Y32_gate), и шаг двухпозиционного управления каждым переключающим элементом с помощью каждого из сгенерированных стробирующих командных сигналов.

[0026] Устройство преобразования мощности с резонансной нагрузкой, снабженное однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), описанное в п. 2, содержит: схемы групп переключателей (100U, 100V, 100Х, 100Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (100U, 100V, 100Х, 100Y) сконфигурирована таким образом, чтобы N (N - целое число, равное 2 и более) последовательных групп, состоящих из М (М - целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи; и контроллер, выполняющий управление переключением каждого переключающего элемента схем группы переключающих элементов (100U, 100V, 100Х, 100Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(М×N), и при этом каждая из N последовательных групп в каждой схеме групп переключателей сформирована модулем, и М переключающих элементов в каждой последовательной группе соединяются внутри модуля.

[0027] Способ работы с разделением по времени устройства преобразования мощности с резонансной нагрузкой, снабженного однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), описан в п. 5, и устройство преобразования мощности с резонансной нагрузкой содержит: схемы групп переключателей (100U, 100V, 100Х, 100Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (100U, 100V, 100Х, 100Y) сконфигурирована таким образом, чтобы N (N - целое число, равное 2 и более) последовательных групп, состоящих из М (М - целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи, и при этом каждая из N последовательных групп в каждой схеме групп переключателей сформирована в виде модуля, и М переключающих элементов в каждой последовательной группе соединяются внутри модуля, при этом способ работы с разделением по времени включает шаг выполнения контроллером управления переключением каждого переключающего элемента схем групп переключателей (100U, 100V, 100Х, 100Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(М×N).

[0028] Устройство преобразования мощности с резонансной нагрузкой, снабженное однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), описанное в п. 3, содержит: схемы групп переключателей (200U, 200V, 200Х, 200Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (200U, 200V, 200Х, 200Y) сконфигурирована таким образом, чтобы n (n - целое число, равное 2 и более) последовательных групп, состоящих из m (m -целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи, и при этом схема групп переключателей (200U) верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов U11-U1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Un1-Unm соединены последовательно, и схема групп переключателей (200U) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи, схема групп переключателей (200Х) нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов X11-X1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Xn1-Xnm соединены последовательно, и схема групп переключателей (200Х) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи, схема групп переключателей (200V) верхнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов V11-V1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Vn1-Vnm соединены последовательно, и схема групп переключателей (200V) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю -были соединены параллельно проводниками главной цепи, и схема групп переключателей (200Y) нижнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов Y11-Y1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Yn1-Ynm соединены последовательно, и схема групп переключателей (200Y) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи; и контроллер, выполняющий управление переключением каждого переключающего элемента схем групп переключателей (200U, 200V, 200Х, 200Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(m×n) и снабженный генератором команды стробирования, который генерирует тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом, стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один цикл которого составляет (2 × М последовательных соединений × N параллельных соединений, где М, N - целое число, большее 2) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего (2 × N параллельных соединений) × (М последовательных соединений - 1) + 1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего [(2 × М последовательных соединений × N параллельных соединений) - (2 × N параллельных соединений) × (М последовательных соединений - 1)+1)] тактов, стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U11_gate/Y11_gate, стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала X11_gate/V11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X11_gate/V11_gate, стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала U21_gate/Y21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U21_gate/Y21_gate, … стробирующий командный сигнал переключающих элементов Un1 и Yn1 (Un1_gate/Yn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)1_gate/V(n-1)1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)1_gate/V(n-1)1_gate, стробирующий командный сигнал переключающих элементов Xn1 и Vn1 (Xn1_gate/Vn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала Un1_gate/Yn1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Un1_gate/Yn1_gate, стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), который задержан на 1 такт относительно стробирующего командного сигнала Xn1_gate/Vn1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Xn1_gate/Vn1_gate, стробирующий командный сигнал переключающих элементов Х12 и V12 (X12_gate/V12_gate), который задержан на 1 такт относительно стробирующего командного сигнала U12_gate/Y12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U12_gate/Y12_gate, стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), который задержан на 1 такт относительно стробирующего командного сигнала X12_gate/V12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X12_gate/V12_gate, стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), который задержан на 1 такт относительно стробирующего командного сигнала U22_gate/Y22_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U22_gate/Y22_gate,... стробирующий командный сигнал переключающих элементов Un2 и Yn2 (Un2_gate/Yn2_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)2_gate/V(n-1)2_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)2_gate/V(n-1)2_gate, стробирующий командный сигнал переключающих элементов Xn2 и Vn2 (Xn2_gate/Vn2_gate), который задержан на 1 такт относительно стробирующего командного сигнала Un2_gate/Yn2_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Un2_gate/Yn2_gate, … стробирующий командный сигнал переключающих элементов Unm и Ynm (Unm_gate/Ynm_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)m_gate/V(n-1)m_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)m_gate/V(n-1)m_gate, и стробирующий командный сигнал переключающих элементов Xnm и Vnm (Xnm_gate/Vnm_gate), который задержан на 1 такт относительно стробирующего командного сигнала Unm_gate/Ynm_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Unm_gate/Ynm_gate, и при этом с помощью каждого сгенерированного стробирующего командного сигнала осуществляется двухпозиционное управление каждым переключающим элементом.

[0029] Способ работы с разделением по времени устройства преобразования мощности с резонансной нагрузкой, снабженного однофазным инвертором, вход постоянного тока которого соединен с источником (11) напряжения постоянного тока, а выход, с которого выводится сигнал напряжения прямоугольной формы на резонансной частоте, соединен с резонансной нагрузкой (12), описан в п. 5, и устройство преобразования мощности с резонансной нагрузкой содержит: схемы групп переключателей (200U, 200V, 200Х, 200Y), соединенные с соответствующими верхними и нижними плечами одной фазы однофазного инвертора и другой фазы однофазного инвертора, при этом каждая из схем групп переключателей (200U, 200V, 200Х, 200Y) сконфигурирована таким образом, чтобы n (n - целое число, равное 2 и более) последовательных групп, состоящих из m (m - целое число, равное 2 и более) переключающих элементов, были соединены параллельно посредством проводников главной цепи, и при этом схема групп переключателей (200U) верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов U11-U1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Un1-Unm соединены последовательно, и схема групп переключателей (200U) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю -были соединены параллельно проводниками главной цепи, схема групп переключателей (200Х) нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов X11-X1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Xn1-Xnm соединены последовательно, и схема групп переключателей (200Х) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи, схема групп переключателей (200V) верхнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов V11-V1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Vn1-Vnm соединены последовательно, и схема групп переключателей (200V) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи, и схема групп переключателей (200Y) нижнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов Y11-Y1m соединены последовательно, … и n-ю последовательную группу, в которой m переключающих элементов Yn1-Ynm соединены последовательно, и схема групп переключателей (200Y) сконфигурирована таким образом, чтобы n последовательных групп - с первой по n-ю -были соединены параллельно проводниками главной цепи, при этом способ работы с разделением по времени включает шаг выполнения контроллером управления переключением каждого переключающего элемента схем групп переключателей (200U, 200V, 200Х, 200Y) однофазного инвертора путем разделения по времени с коэффициентом 1/(m×n); шаг генерации генератором команды стробирования следующих сигналов: тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом, стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один цикл которого составляет (2 × М последовательных соединений × N параллельных соединений, где М, N - целое число, большее 2) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего (2 × N параллельных соединений) × (М последовательных соединений - 1) + 1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего [(2 × М последовательных соединений × N параллельных соединений) - (2 × N параллельных соединений) × (М последовательных соединений - 1) + 1)] тактов, стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U11_gate/Y11_gate, стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала X11_gate/V11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X11_gate/V11_gate, стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала U21_gate/Y21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U21_gate/Y21_gate, … стробирующий командный сигнал переключающих элементов Un1 и Yn1 (Un1_gate/Yn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)1_gate/V(n-1)1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)1_gate/V(n-1)1_gate, стробирующий командный сигнал переключающих элементов Xn1 и Vn1 (Xn1_gate/Vn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала Un1_gate/Yn1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Un1_gate/Yn1_gate, стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), который задержан на 1 такт относительно стробирующего командного сигнала Xn1_gate/Vn1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Xn1_gate/Vn1_gate, стробирующий командный сигнал переключающих элементов X12 и V12 (X12_gate/V12_gate), который задержан на 1 такт относительно стробирующего командного сигнала U12_gate/Y12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U12_gate/Y12_gate, стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), который задержан на 1 такт относительно стробирующего командного сигнала X12_gate/V12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X12_gate/V12_gate, стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), который задержан на 1 такт относительно стробирующего командного сигнала U22_gate/Y22_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U22_gate/Y22_gate,... стробирующий командный сигнал переключающих элементов Un2 и Yn2 (Un2_gate/Yn2_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)2_gate/V(n-1)2_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)2_gate/V(n-1)2_gate, стробирующий командный сигнал переключающих элементов Xn2 и Vh2 (Xn2_gate/Vn2_gate), который задержан на 1 такт относительно стробирующего командного сигнала Un2_gate/Yn2_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Un2_gate/Yn2_gate, … стробирующий командный сигнал переключающих элементов Unm и Ynm (Unm_gate/Ynm_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)m_gate/V(n-1)m_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)m_gate/V(n-1)m_gate, и стробирующий командный сигнал переключающих элементов Xnm и Vnm (Xnm_gate/Vnm_gate), который задержан на 1 такт относительно стробирующего командного сигнала Unm_gate/Ynm_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Unm_gate/Ynm_gate; и шаг двухпозиционного управления каждым переключающим элементом с помощью каждого из сгенерированных стробирующих командных сигналов.

(1) Посредством изобретения, описанного в п.п. 1-6 формулы изобретения, возможно уменьшить частоту переключения каждого переключающего элемента до частоты, обратно пропорциональной произведению (М последовательных соединений × N параллельных соединений) количества последовательных и параллельных соединений.

[0030] Кроме того, количество проводников главной цепи, соединяющих входную секцию Vdc линии напряжения постоянного тока и входную клемму постоянного тока каждого переключающего элемента верхнего и нижнего плеча, а также соединяющих выходную секцию Vout сигнала напряжения прямоугольной формы и выходную клемму каждого переключающего элемента верхнего и нижнего плеча, может быть уменьшено относительно количества переключающих элементов (М×N) (количество проводников главной цепи может быть меньше количества переключающих элементов (М×N)). Благодаря этому можно уменьшить стоимость устройства. Кроме того, можно уменьшить пространство, требуемое для размещения проводников главной цепи.

[0031] Поскольку переключающие элементы схемы групп переключателей подключаются с использованием М последовательных и N параллельных соединений, пространство размещения переключающих элементов не возрастает по сравнению со стандартным устройством, следовательно изменение импеданса вследствие изменений длины маршрута проводников главной цепи могут быть уменьшены.

(2) Как описано в п.п. 1, 3, 4 и 6 формулы изобретения, поскольку период, в течение которого переключающие элементы находятся в открытом и запертом состояниях, длится множество тактов и стробирующих командных сигналов, генерируемых генератором команд стробирования, зависимость предельной выходной частоты от предельной минимальной длительности импульса, определяемой характеристиками элемента, может устраняться.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0032]

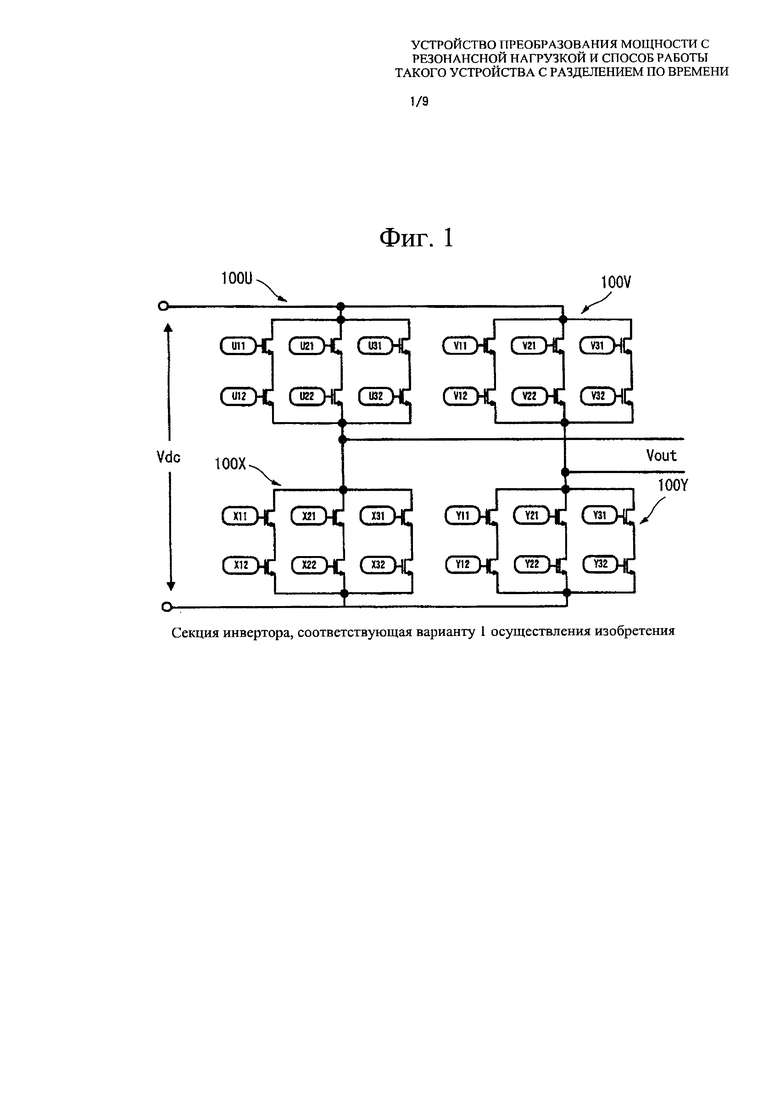

На фиг. 1 показана конфигурация однофазного инвертора в соответствии с вариантом 1 осуществления настоящего изобретения.

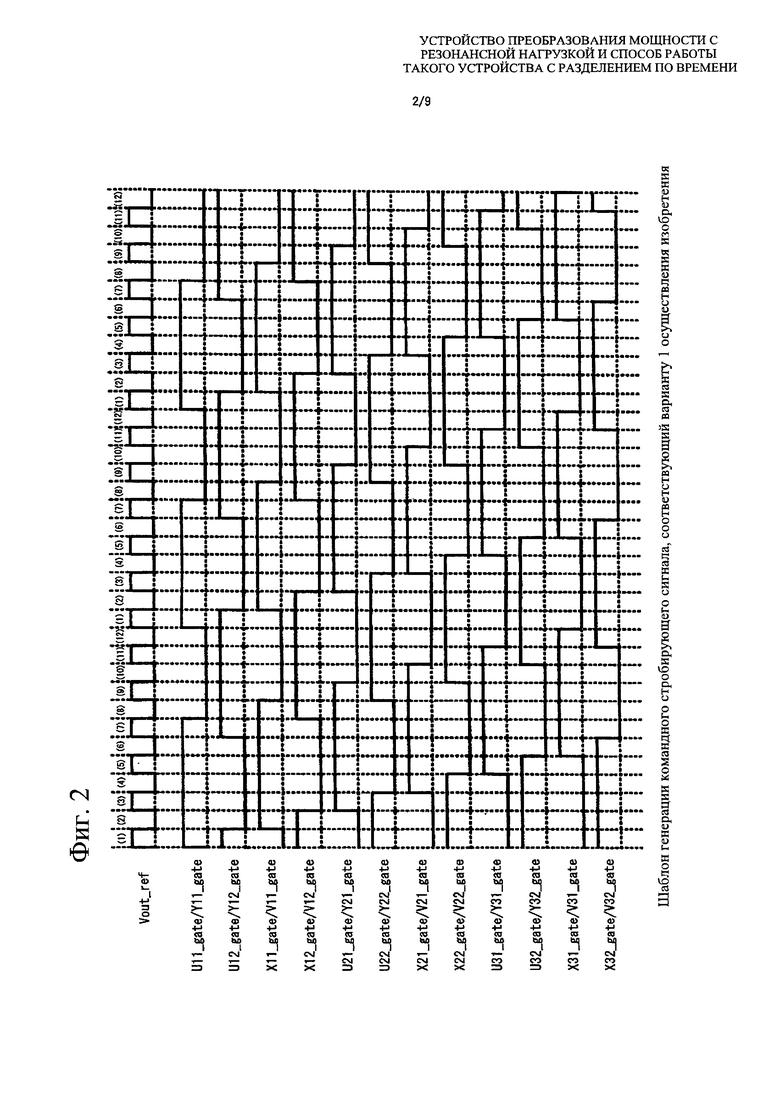

На фиг. 2 показана диаграмма формы сигнала, иллюстрирующая пример шаблона генерации командного стробирующего сигнала в соответствии с вариантом 1 осуществления настоящего изобретения.

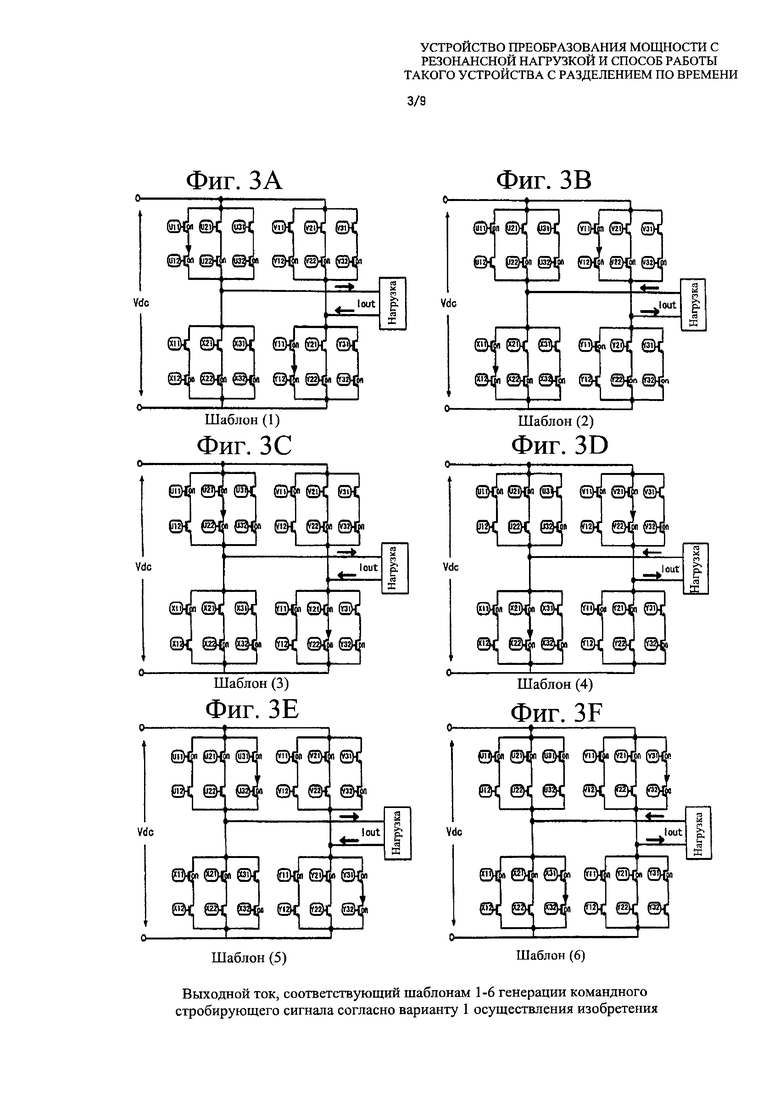

На фиг. 3A-3F показаны диаграммы, соответствующие изображенным на фиг. 2 шаблонам (1)-(6) генерации командного стробирующего сигнала, и указывается состояние управляемых сигналом отпирания переключающих элементов, а также путь прохождения выходного тока.

На фиг. 4А-4F показаны диаграммы, соответствующие изображенным на фиг. 2 шаблонам (7)-(12) генерации командного стробирующего сигнала, и указывается состояние управляемых сигналом отпирания переключающих элементов, а также путь прохождения выходного тока.

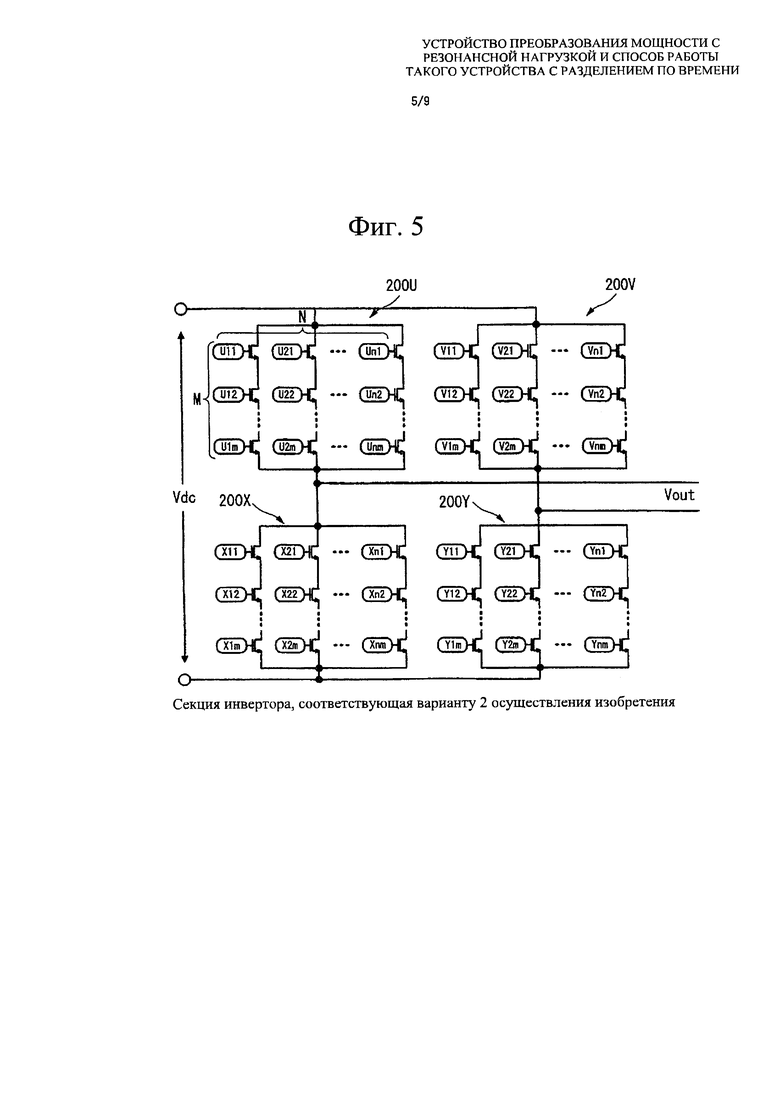

На фиг. 5 показана конфигурация схемы однофазного инвертора в соответствии с вариантом 2 осуществления настоящего изобретения.

На фиг. 6 показана диаграмма формы сигнала, иллюстрирующая пример шаблона генерации командного стробирующего сигнала, в соответствии с вариантом 2 осуществления настоящего изобретения.

На фиг. 7 показана блок-схема устройства преобразования мощности с резонансной нагрузкой, к которой применимо настоящее изобретение.

На фиг. 8 показана конфигурация схемы секции инвертора, являющегося модифицированным примером системы инвертора с резонансной нагрузкой, раскрытого в патентном документе 1.

На фиг. 9 показана диаграмма формы сигнала, иллюстрирующая пример шаблона генерации командного стробирующего сигнала, для управления каждым переключающим элементом секции инвертора, показанной на фиг. 8.

На фиг. 10A-10F показаны диаграммы, соответствующие изображенным на фиг. 9 шаблонам (1)-(6) генерации командного стробирующего сигнала, и указывается состояние управляемого сигналом отпирания переключающего элемента, а также путь прохождения выходного тока.

ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

[0033] Ниже со ссылкой на прилагаемые чертежи объясняются варианты осуществления настоящего изобретения. Однако настоящее изобретение не ограничено этими вариантами осуществления.

Вариант 1 осуществления изобретения

[0034] На фиг. 1 показана конфигурация схемы секции однофазного инвертора в соответствии с вариантом 1 осуществления настоящего изобретения, а также показан однофазный инвертор, применимый, например, к устройству 10 преобразования AC-DC (устройству преобразования мощности с резонансной нагрузкой), показанному на фиг. 7.

[0035] Однофазный инвертор, показанный на фиг. 1, сконфигурирован таким образом, чтобы входная секция постоянного тока подключалась к входной секции Vdc напряжения линии постоянного тока; каждая из схем 100U, 100V, 100Х и 100Y групп переключателей, содержащая переключающие элементы (например, IGBT), образующие М последовательных и N параллельных соединений (М - целое число, равное 2 и более, N - целое число, равное 2 и более, например, на фиг. 1: М=2, N=3 (2 последовательные и 3 параллельные группы)), подключалась к соответствующим плечам, и сигнал Vout напряжения прямоугольной формы выводился между общей точкой соединения схем 100U и 100Х групп переключателей и общей точкой соединения схем 100V и 100Y групп переключателей.

[0036] Схема 100U групп переключателей верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента U11 и U12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента U21 и U22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента U31 и U32 соединены последовательно. Схема 100U групп переключателей сконфигурирована таким образом, чтобы эти три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи между этими тремя последовательными группами.

[0037] Схема 100Х групп переключателей нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента X11 и Х12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Х21 и Х22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Х31 и Х32 соединены последовательно. Схема 100Х групп переключателей сконфигурирована таким образом, чтобы эти три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи между этими тремя последовательными группами.

[0038] Схема 100V групп переключателей верхнего плеча, представляющего собой другую, фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента V11 и V12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента V21 и V22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента V31 и V32 соединены последовательно. Схема 100V групп переключателей сконфигурирована таким образом, чтобы эти три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи между этими тремя последовательными группами.

[0039] Схема 100Y групп переключателей нижнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой два переключающих элемента Y11 и Y12 соединены последовательно, вторую последовательную группу, в которой два переключающих элемента Y21 и Y22 соединены последовательно, и третью последовательную группу, в которой два переключающих элемента Y31 и Y32 соединены последовательно. Схема 100Y групп переключателей сконфигурирована таким образом, чтобы эти три последовательные группы - с первой по третью - были соединены параллельно проводниками главной цепи между этими тремя последовательными группами.

[0040] Каждая последовательная группа формируется модулем, объединяющим два элемента. Два переключающих элемента в каждой последовательной группе соединяются внутри модуля.

[0041] Как описано выше, в соответствии с конфигурацией однофазного инвертора, показанного на фиг. 1, поскольку переключающие элементы схемы групп переключателей соединены последовательно и параллельно (поскольку соединение схемы групп переключателей представляет собой последовательное и параллельное соединение), количество проводников главной цепи, соединяющих входную секцию Vdc линии напряжения постоянного тока и входную клемму постоянного тока каждого переключающего элемента верхнего и нижнего плеча, а также соединяющих выходную секцию Vout сигнала напряжения прямоугольной формы и выходную клемму каждого переключающего элемента верхнего и нижнего плеча, может быть уменьшено относительно количества переключающих элементов (М×N) (количество проводников главной цепи может быть меньше количества переключающих элементов (М×N)). Кроме того, поскольку соединение переключающих элементов схемы групп переключателей представляет собой последовательное и параллельное соединение, пространство размещения проводника главной цепи не увеличивается пропорционально количеству переключающих элементов (М×N), и изменения импеданса вследствие изменений длины маршрута проводника главной цепи могут быть уменьшены.

[0042] Секция управления (контроллер), управляющая однофазным инвертором, показанным на фиг. 1, содержит секцию генерации команды стробирования (генератор команды стробирования), которая генерирует тактовые сигналы и стробирующие командные сигналы в соответствии с шаблоном генерации стробирующего командного сигнала, изображенным на фиг. 2. Секция управления осуществляет двухпозиционное управление каждым переключающим элементом посредством стробирующего командного сигнала.

[0043] На фиг. 2 показан шаблон генерации командного стробирующего сигнала для случая, когда число М последовательных соединений равно 2, и число N параллельных соединений равно 3, в соответствии со схемой, показанной на фиг. 1, и в шаблоне используется тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора в качестве запускающего сигнала, при этом один период (один цикл) составляет 2*M*N=12 тактов, сигнал отпирания подается в течение 2*N*(M-1)+1=7 тактов, а сигнал запирания - в течение (2*М*N) - [2*N*(М-1)+1]=5 тактов.

[0044] Таким образом, показанный на фиг. 2 шаблон генерации командного стробирующего сигнала формируется из следующих компонентов:

тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом,

стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один период (цикл) которого составляет 12 (2 × (М последовательных соединений) × (N параллельных соединений)) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего 7 (2 × (N параллельных соединений) × (М последовательных соединений - 1)+1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего 5 [(2 × (М последовательных соединений) × (N параллельных соединений)) - (2 × (N параллельных соединений) × (М последовательных соединений - 1) + 1)] тактов,

стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U11_gate/Y11_gate,

стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала X11_gate/V11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X11_gate/V11_gate,

стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала U21_gate/Y21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U21 _gate/Y21_gate,

стробирующий командный сигнал переключающих элементов U31 и Y31 (U31_gate/Y31_gate), который задержан на 1 такт по сравнению со стробирующим командным сигналом X21_gate/V21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X21_gate/V21_gate,

стробирующий командный сигнал переключающих элементов Х31 и V31 (X31_gate/V31_gate), который задержан на 1 такт по сравнению со стробирующим командным сигналом U31_gate/Y31_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U31_gate/Y31_gate,

стробирующий командный сигнал переключающих элементов U12 и Y12 (U12_gate/Y12_gate), который задержан на 1 такт относительно стробирующего командного сигнала X31_gate/V31_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X31_gate/V31_gate,

стробирующий командный сигнал переключающих элементов X12 и V12 (X12_gate/V12_gate), который задержан на 1 такт относительно стробирующего командного сигнала U12_gate/Y12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U12_gate/Y12_gate,

стробирующий командный сигнал переключающих элементов U22 и Y22 (U22_gate/Y22_gate), который задержан на 1 такт относительно стробирующего командного сигнала X12_gate/V12_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X12_gate/V12_gate,

стробирующий командный сигнал переключающих элементов Х22 и V22 (X22_gate/V22_gate), который задержан на 1 такт относительно стробирующего командного сигнала U22_gate/Y22_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U22_gate/Y22_gate,

стробирующий командный сигнал переключающих элементов U32 и Y32 (U32_gate/Y32_gate), который задержан на 1 такт по сравнению со стробирующим командным сигналом X22_gate/V22_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X22_gate/V22_gate,

стробирующий командный сигнал переключающих элементов Х32 и V32 (X32_gate/V32_gate), который задержан на 1 такт относительно стробирующего командного сигнала U32_gate/Y32_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U32_gate/Y32_gate,

[0045] Для каждого переключающего элемента, показанного на фиг. 1, используется двухпозиционное управление посредством стробирующих командных сигналов U11_gate/Y11_gate … X32_gate/V32_gate с повторяющимися шаблонами (1) … (12), изображенными на фиг. 2.

[0046] Взаимосвязь с выходным током при двухпозиционном управлении каждым переключающим элементом схем групп переключателей, изображенных на фиг. 1, посредством показанного на фиг. 2 шаблона генерации командного стробирующего сигнала иллюстрируется на фиг. 3A-3F и 4A-4F.

[0047] Фиг. 3A-3F соответствуют шаблонам (1)-(6), показанным на фиг. 2. Фиг. 4A-4F соответствуют шаблонам (7)-(12), показанным на фиг. 2. На фиг. 3A-3F и 4A-4F переключающий элемент, управляемый сигналом отпирания команды стробирования, указывается меткой "ON", и маршрут выходного тока Iout, протекающего через этот переключающий элемент и нагрузку, показан стрелкой.

[0048] На фиг. 3А-3F и 4А-4F показана резонансная нагрузка, такая как устройство индукционного нагрева.

[0049] Согласно шаблону (1), показанному на фиг. 3А, переключающие элементы U11, Y11, U12, Y12, Х12, V12, U22, Y22, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы X11, V11, U21, Y21, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U11 → U12 → нагрузка → переключающие элементы Y11 → Y12.

[0050] Согласно шаблону (2), показанному на фиг. 3В, переключающие элементы U11 Y11, X11, V11, Х12, V12, U22, Y22, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U12, Y12, U21, Y21, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V11 → V12 → нагрузка → переключающие элементы X11 → X12.

[0051] Согласно шаблону (3), показанному на фиг. 3С, переключающие элементы U11, Y11, X11, V11, U21, Y21, U22, Y22, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U12, Y12, Х12, V12, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U21 → U22 → нагрузка → переключающие элементы Y21 → Y22.

[0052] Согласно шаблону (4), показанному на фиг. 3D, переключающие элементы U11, Y11, X11, V11, U21, Y21, Х21, V21, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U12, Y12, Х12, V12, U22, Y22, U31, Y31, Х31 и V31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V21 → V22 → нагрузка → переключающие элементы Х21 → Х22.

[0053] Согласно шаблону (5), показанному на фиг. 3Е, переключающие элементы U11, Y11, X11, V11, U21, Y21, Х21, V21, U31, Y31, U32, Y32, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U12, Y12, X12, V12, U22, Y22, Х22, V22, Х31 и V31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U31 → U32 → нагрузка → переключающие элементы Y31 → Y32.

[0054] Согласно шаблону (6), показанному на фиг. 3F, переключающие элементы U11, Y11, X11, V11, U21, Y21, Х21, V21, U31, Y31, Х31, V31, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U12, Y12, X12, V12, U22, Y22, Х22, V22, U32 и Y32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V31 → V32 → нагрузка → переключающие элементы Х31 → Х32.

[0055] Согласно шаблону (7), показанному на фиг. 4А, переключающие элементы U11, Y11, U12, Y12, X11, V11, U21, Y21, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом отпирания (ON). Переключающие элементы X12, V12, U22, Y22, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U11 → U12 → нагрузка → переключающие элементы Y11 → Y12.

[0056] Согласно шаблону (8), показанному на фиг. 4В, переключающие элементы U12, Y12, X11, V11, Х12, V12, U21, Y21, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом отпирания (ON). Переключающие элементы U11, Y11, U22, Y22, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V11 → V12 → нагрузка → переключающие элементы X11 → X12.

[0057] Согласно шаблону (9), показанному на фиг. 4С, переключающие элементы U12, Y12, Х12, V12, U21, Y21, U22, Y22, Х21, V21, U31, Y31, Х31 и V31 управляются сигналом отпирания (ON). Переключающие элементы U11, Y11, X11, V11, Х22, V22, U32, Y32, Х32 и V32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U21 → U22 → нагрузка → переключающие элементы Y21 → Y22.

[0058] Согласно шаблону (10), показанному на фиг. 4D, переключающие элементы U12, Y12, Х12, V12, U22, Y22, Х21, V21, Х22, V22, U31, Y31, Х31 и V31 управляются сигналом отпирания (ON). Переключающие элементы U11, Y11, X11, V11, U21, Y21, U32, Y32, Х32 и V32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V21 → V22 → нагрузка → переключающие элементы Х21 → Х22.

[0059] Согласно шаблону (11), показанному на фиг. 4Е, переключающие элементы U12, Y12, Х12, V12, U22, Y22, Х22, V22, U31, Y31, U32, Y32, Х31 и V31 управляются сигналом отпирания (ON). Переключающие элементы U11, Y11, X11 V11, U21, Y21, Х21, V21, Х32 и V32 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы U31 → U32 → нагрузка → переключающие элементы Y31 → Y32.

[0060] Согласно шаблону (12), показанному на фиг. 4F, переключающие элементы U12, Y12, X12, V12, U22, Y22, Х22, V22, U32, Y32, Х31, V31, Х32 и V32 управляются сигналом отпирания (ON). Переключающие элементы U11, Y11, X11, V11, U21, Y21, Х21, V21, U31 и Y31 управляются сигналом запирания (OFF). Вследствие этого ток протекает по следующему маршруту: переключающие элементы V31 → V32 → нагрузка → переключающие элементы Х31 → Х32.

[0061] Путем последовательного переключения (двухпозиционного управления) каждого переключающего элемента (то есть путем выполнения операции разделения по времени для каждого переключающего элемента) посредством шаблонов (1)-(12), показанных на фиг. 3A-3F и 4A-4F, возможно уменьшить задающую частоту переключающего элемента до значения 1/(М×N), которое обратно пропорционально произведению (М×N) количества последовательных и параллельных соединений, то есть до 1/6. Кроме того, поскольку период отпирания и запирания переключающего элемента длится в течение множества тактов, предел выходной частоты, который зависит от предельного значения минимальной длительности импульса, определяемой характеристиками элементов, может быть устранен (выходная частота устройства преобразования AC-DC не ограничивается характеристиками переключающего элемента).

[0062] Помимо этого, поскольку переключающие элементы схемы групп переключателей соединены последовательно и параллельно (поскольку соединение переключающих элементов схемы групп переключателей представляет собой последовательное и параллельное соединение), количество проводников главной цепи, соединяющих входную секцию Vdc линии напряжения постоянного тока и входную клемму постоянного тока каждого переключающего элемента верхнего и нижнего плеча, а также соединяющих выходную секцию Vout сигнала напряжения прямоугольной формы и выходную клемму каждого переключающего элемента верхнего и нижнего плеча, может быть уменьшено относительно количества переключающих элементов (М×N) (количество проводников главной цепи может быть меньше количества переключающих элементов (М×N)). Кроме того, поскольку соединение переключающих элементов схемы групп переключателей представляет собой последовательное и параллельное соединение, пространство размещения проводника главной цепи не увеличивается пропорционально количеству переключающих элементов (М×N), и изменения импеданса вследствие изменений длины маршрута проводника главной цепи могут быть уменьшены.

[0063] В данном случае количество М последовательных соединений переключающих элементов в схеме групп переключателей для каждого плеча однофазного инвертора не ограничено двумя соединениями, а может составлять 3 или более соединений. Кроме того, количество N параллельных соединений не ограничено тремя соединениями, а может составлять 2 или 4, или более соединений. Возможно также уменьшить задающую частоту (частоту переключения) переключающего элемента однофазного инвертора обратно пропорционально произведению (М×N) количества последовательных и параллельных соединений.

Вариант 2 осуществления изобретения

[0064] На фиг. 5 показана конфигурация секции однофазного инвертора в соответствии с вариантом 2 осуществления настоящего изобретения, а также показан однофазный инвертор, применимый, например, к устройству 10 преобразования AC-DC с резонансной нагрузкой (устройству преобразования мощности с резонансной нагрузкой), показанному на фиг. 7.

[0065] Однофазный инвертор, показанный на фиг. 5, сконфигурирован таким образом, чтобы входная секция постоянного тока подключалась к входной секции Vdc напряжения линии постоянного тока; схемы 200U, 200V, 200Х и 200Y групп переключателей, каждая из которых содержит переключающие элементы (например, IGBT), образующие М последовательных и N параллельных соединений (М - целое число, не меньшее 2, N - целое число, не меньшее 2, например, на фиг. 5 М составляет 3 или более, N составляет 3 или более), подключались к соответствующим плечам, и сигнал Vout выходного напряжения прямоугольной формы выводился между общей точкой соединения схем 200U и 200Х групп переключателей и общей точкой соединения схем 200V и 200Y групп переключателей.

[0066] Схема 200U групп переключателей верхнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов U11, U12 … U1m соединены последовательно, вторую последовательную группу, в которой m переключающих элементов U21, U22 … U2m соединены последовательно, и n-ю последовательную группу, в которой m переключающих элементов Un1. Un2 … Unm соединены последовательно. Схема 200U групп переключателей сконфигурирована таким образом, чтобы эти n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи между этими n последовательными группами.

[0067] Схема 200Х групп переключателей нижнего плеча, представляющего собой одну фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов X11, Х12 … X1m соединены последовательно, вторую последовательную группу, в которой m переключающих элементов Х21, Х22 … X2m соединены последовательно, и n-ю последовательную группу, в которой m переключающих элементов Xn1. Xn2 … Xnm соединены последовательно. Схема 200Х групп переключателей сконфигурирована таким образом, чтобы эти n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи между этими n последовательными группами.

[0068] Схема 200V групп переключателей верхнего плеча, представляющего собой другую фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов V11, V12 … V1m соединены последовательно, вторую последовательную группу, в которой m переключающих элементов V21, V22 … V2m соединены последовательно, и n-ю последовательную группу, в которой m переключающих элементов Vn1, Vn2 … Vnm соединены последовательно. Схема 200V групп переключателей сконфигурирована таким образом, чтобы эти n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи между этими n последовательными группами.

[0069] Схема 200Y групп переключателей нижнего плеча, представляющего собой другую, фазу однофазного инвертора, содержит первую последовательную группу, в которой m переключающих элементов Y11, Y12 … Y1m соединены последовательно, вторую последовательную группу, в которой m переключающих элементов Y21, Y22 … Y2m соединены последовательно, и n-ю последовательную группу, в которой m переключающих элементов Yn1, Yn2 … Ynm соединены последовательно. Схема 200Y групп переключателей сконфигурирована таким образом, чтобы эти n последовательных групп - с первой по n-ю - были соединены параллельно проводниками главной цепи между этими n последовательными группами.

[0070] Каждая последовательная группа, состоящая из m переключающих элементов, формируется одним модулем. И m переключающих элементов в каждой последовательной группе соединяются внутри модуля.

[0071] Как описано выше, в соответствии с конфигурацией однофазного инвертора, показанного на фиг. 5, поскольку переключающие элементы схемы групп переключателей соединены последовательно и параллельно (поскольку соединение переключающих элементов схемы групп переключателей представляет собой последовательное и параллельное соединение), количество проводников главной цепи, соединяющих входную секцию Vdc линии напряжения постоянного тока и входную клемму постоянного тока каждого переключающего элемента верхнего и нижнего плеча, а также соединяющих выходную секцию Vout сигнала напряжения прямоугольной формы и выходную клемму каждого переключающего элемента верхнего и нижнего плеча, может быть уменьшено относительно количества переключающих элементов (М×N) (количество проводников главной цепи может быть меньше количества переключающих элементов (М×N)). Кроме того, поскольку соединение переключающих элементов схемы групп переключателей представляет собой последовательное и параллельное соединение, пространство размещения проводника главной цепи не увеличивается пропорционально количеству переключающих элементов (М×N), и изменения импеданса вследствие изменений длины маршрута проводника главной цепи могут быть уменьшены.

[0072] Секция управления (контроллер), управляющая однофазным инвертором, показанным на фиг. 5, содержит секцию генерации команды стробирования, которая генерирует тактовые сигналы и стробирующие командные сигналы, например, показанные в виде шаблона генерации стробирующего командного сигнала, изображенного на фиг. 6. Секция управления осуществляет двухпозиционное управление каждым переключающим элементом посредством стробирующего командного сигнала.

[0073] На фиг. 6 показан шаблон генерации командного стробирующего сигнала для случая, когда число М последовательных соединений переключающих элементов в схеме групп переключателей для каждого плеча в однофазном инверторе равно 3, и число N параллельных соединений равно 6, один период (один цикл) составляет 2*М*N=36 тактов, сигнал отпирания подается в течение 2*N*(М-1)+1=25 тактов, а сигнал запирания - в течение (2*М*N)-[2*N*(М-1)+1]=11 тактов.

[0074] В данном случае на фиг. 6 не показаны:

стробирующий командный сигнал U31_gate/Y31_gate переключающих элементов U31 и Y31 … стробирующий командный сигнал X(n-1)1_gate/V(n-1)1_gate переключающих элементов X(n-1)1 and V(n-1)1,

стробирующий командный сигнал U32_gate/Y32_gate переключающих элементов U32 и Y32 … стробирующий командный сигнал X(n-1)2_gate/V(n-1)2_gate переключающих элементов Х(n-1)2 и V(n-1)2,

стробирующий командный сигнал U1m_gate/Y1m_gate переключающих элементов U1m и Y1m … стробирующий командный сигнал X(n-1)m_gate/V(n-1)m_gate переключающих элементов X(n-1)m и V(n-1)m.

[0075] Таким образом, показанный на фиг. 6 шаблон генерации командного стробирующего сигнала формируется из следующих компонентов:

тактовый сигнал отпирания (ON) и запирания (OFF) команды выходного напряжения (Vout_ref) однофазного инвертора, являющийся запускающим сигналом,

стробирующий командный сигнал переключающих элементов U11 и Y11 (U11_gate/Y11_gate), один период (цикл) которого составляет 36 (2 × (М последовательных соединений) × (N параллельных соединений)) тактов, и сигнал отпирания (ON) выводится в течение периода, составляющего 25 (2 × (N параллельных соединений) × (М последовательных соединений - 1) + 1) тактов, а сигнал запирания (OFF) выводится в течение периода, составляющего 11 [(2 × (М последовательных соединений) × (N параллельных соединений)) - (2 × (N параллельных соединений) × (М последовательных соединений - 1) + 1)] тактов,

стробирующий командный сигнал переключающих элементов X11 и V11 (X11_gate/V11_gate), который задержан на 1 такт относительно стробирующего командного сигнала U11_gate/Y11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U11_gate/Y11_gate,

стробирующий командный сигнал переключающих элементов U21 и Y21 (U21_gate/Y21_gate), который задержан на 1 такт относительно стробирующего командного сигнала X11_gate/V11_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X11_gate/V11_gate,

стробирующий командный сигнал переключающих элементов Х21 и V21 (X21_gate/V21_gate), который задержан на 1 такт относительно стробирующего командного сигнала U21_gate/Y21_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал U21_gate/Y21_gate,

…

стробирующий командный сигнал переключающих элементов Un1 и Yn1 (Un1_gate/Yn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала X(n-1)1_gate/V(n-1)1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал X(n-1)1_gate/V(n-1)1_gate,

стробирующий командный сигнал переключающих элементов Xn1 и Vn1 (Xn1_gate/Vn1_gate), который задержан на 1 такт относительно стробирующего командного сигнала Un1_gate/Yn1_gate и выводится с теми же периодами отпирания и запирания, что и стробирующий командный сигнал Un1_gate/Yn1_gate,