Изобретение .относится к средствам вычислительной техники и можег быть использовано в качестве специализированной машины в АСУ группой станков, переналаживаемой автоматической линией, интегрированным участком металлообрабатывающей, электронной и других отраслей промышленности, где широко применяется числовое программное управление (ЧПУ) и централизованное управление от ЭВМ, например для управления транспортно-накопительными системами деталей и ииструментав. Известна цифровая логическая машина (ЦЛМ), содержаш,ая оперативное запоминаюш,ее устройство и устройство связи с объектами. Недостатком известной ЦЛМ является низкая эффективность работы лри управлении поточно-траиспортными .системами. Наиболее близкой по техническому решению д данному изобретению является цифровая логическая машина, содержап;ая микро программное устройство управления, оперативное запоминаюш,ее устройство, полупостоянное запоминающее устройство и устройство связи с объектами, причем лервый и второй выходы и первый вход микропрограммного устройства управления соединены с лервым и вторым входами и первым выходом оперативного запоминающего устройства, третий вход и второй выход оперативного запоминающего устройства связаны с первым выходом и лервым входом полупостоянного запоминающего устрой-ства, а третий выход - с выходом цифровой логической машины, второй выход полупостоянного запоминающего устройства соединен с выходом цифровой логической машины, а второй вход - с третьим выходом микропрограммного устройства управления. К недостаткам известных ЦЛМ относится отсутствие аппаратного обеспечения приоритетного выбора алгоритмов для одновременно управляемых объектов и разделения машинного времени между ними и необходимость решения этих задач программным путем, что лриводит к увеличению объема памяти и непролзводительным лотерям машинного времени, и как следствие - к низкому коэффициенту использования оборудования. Целью изобретения является повышение коэффициента использования оборудования. Указанная цель достигается - тем, что устройство связи с объектами содерл ит блок коммутаторов, блок буферных регистров, блок регистров первого уровня, блок адресных дешифраторов и регистр второго уровня, причем управляющие входы блока коммутаторов соединены с первыми выходами блока адресных дешифраторов, информационные

входы -с соответствующими входами цифровой .логической угашины, а выходы - с первыми входами блока буферных регистров, вторые входы которого связаны с соответствующим-и выходами оперативного запомин-ающего устройства, управляющие входы -с соответствующими выходами микропрограммного устройства управления, основные выходы- с соответствующими входами оперативного запоминающего устройства, а дополнительные входы и выход - с соответствующими входом и выходом цифровой логической мащины, вторые выходы блока адресных дещифраторов связаны с соответствующими входами полупостоянного запоминающего устройства, а входы - с установочными входами регистра второго уровня и выходами блока регистров первого уровня, первые управляющие и (Первые установочные входы которого соединены с соответствующими выходами микропрограммного устройства управления, вторые управляющие входы - с соответствующими входами цифровой логической м.ащины и первыми управляющими входами регистра второго уровня, вторые управляющие входы которого связаны с соответствующими выходами микропрограммного устройства управления, а выходы - с соответствующими входами оперативного запоминающего устройства, вторые установочные входы блока регистров .первого уровня соединены с соответствующими входами цифровой логической мащины.

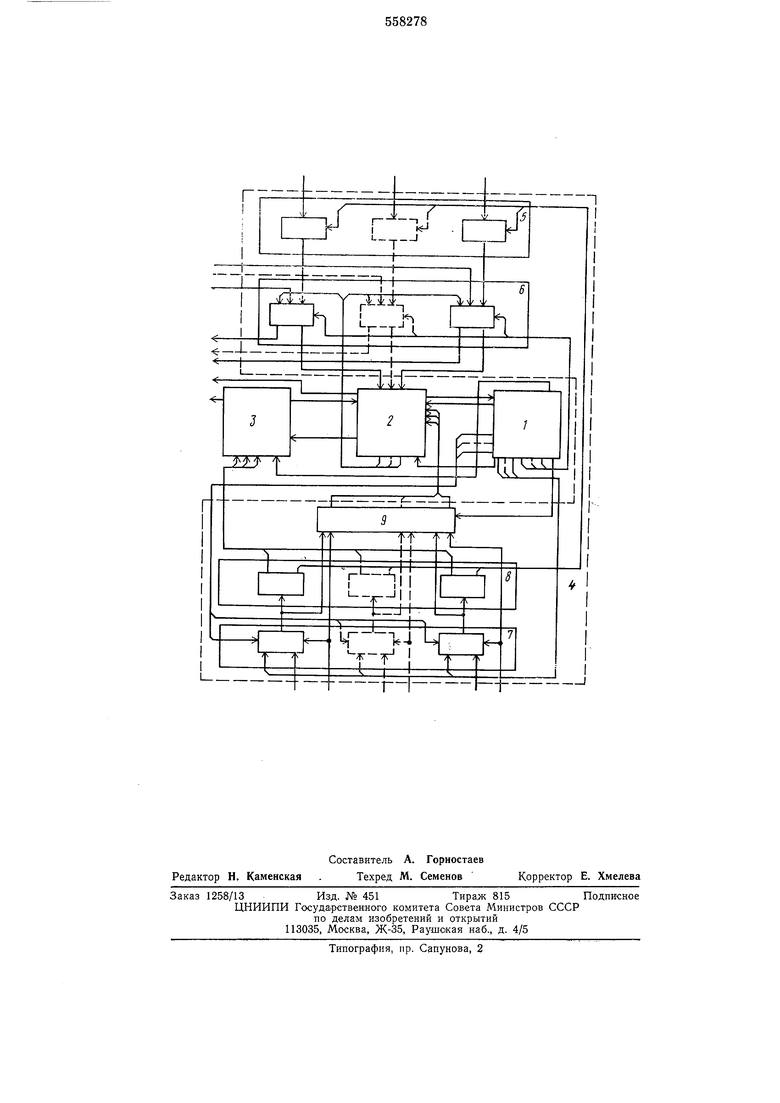

На чертеже показана функциональная схема предлагаемой цифровой логической мащины, где 1 - микропрограммное устройство управления (МУУ), 2 - оперативное запоминающее устройство (ОЗУ), 3 - полупостоянное запоминающее устройство (ППЗУ), 4 - устройство связи с объектами (УСО), 5 - блок коммутаторов (БК), 6 - блок буферных регистров (ББРг), 7-блок регистров первого уровня .(БРг1), 8 - блок адресных дещифраторов (БДщА), 9 - регистр второго уровня (РгП).

Блок регистров первого уровня (БРг1) предназначен для приема заявок на алгоритмы работы объектов управления, алгоритмы поиска и алгоритмы связи с внещними устройствами. Заявки формируются внещними сигналами ло вторым установочным входам или сигналами от МУУ, формируемыми в процессе рещения других алгоритмов, по первым установочным входам.

Регистр второго уровня (РгП) предназначен для лриема заявок на выполнение центральным устройством логической обработки информации операторов алгоритмов. Заявки в РгП формируются БРг1 по установочным входам фиксированных разрядов и первым управляющим входам от объектов управления, :Либо только по устаповочным входам фиксированных разрядов РгП путем опроса БРг1 сигналами конца выполнения предыдущих алгоритмов от МУУ по первым управляющим входам и при наличии сигналов конца дикла отработки от объектов по вторым управляющим входам, либо только сигналами конца выполнения предыдущих алгоритмое от МУУ по первым управляющим входам.

Блок адресных дещифраторов (БДщА) преобразует номер разряда регистра БРг1, который соответствует номеру позиции (станка) обслуживаемого объекта (детали), от которой прищла заявка, в адрес ППЗУ управляющего слова этой .позиции.

Блок коммутаторов (БК) предназначен для коммутации и передачи в .блок .буферных регистров (ББРг) и далее в ОЗУ соответствующей информации об обслуживаемых объектах (код номера детали, инструмента) на соответствующих позициях по сигналам от МУУ ло управляющим входам ББРг. ,

Микропрограммное устройство управления (МУУ) содержит последовательности микрокоманд, составляющие отдельным операторы алгоритмов, и предназначено для управления всеми блоками ЦЛМ IB режиме выполнения

соответствующих алгоритмов.

В ОЗУ хранятся макропрограммы, слова прерывания, промежуточные результаты, технологические марщруты, а также вся исходная информация об управляемой транспортно-накоеительной системе.

ППЗУ предпазначено для хранения адресов и констант, относящихся к позициям обслуживаемых объектов, необходимых для рещения алгоритмов.

Принцип работы ПЛМ основывается на следующих факторах: особенностью технологических алгоритмов управления является последовательное чередование лтащинных операторов (поиск и (выдача задания объекту управления) и механических циклов отработки задания объектом, поэтому прерывание .мащинного алгоритма осуществляется в конце каждого оператора по сигналу «Конец оператора, вход в прерванный алгоритм осуществляется по сигналу от о-бъекта управления, подтверждающему зав-ерщение предыдущего цикла отработки задания; естественные прерывания з выполнении ЦЛМ управляющих алгоритмов используются для разделения времени ЦЛМ на решение операторов алгоритмов остальных объектов управления, а также рещение других алгоритмов, не связанных с объектами управления; |Схемное выполнение приоритетной иерархии алгоритмЬв

как в БРг1 внутри группы алгоритмов для каждого объекта управления, так и в РгП между всеми программно реализуемыми ЦЛМ алгоритмами, определяемое технологической важностью и очередностью алгоритмов, обеспечивается непосредственной связью выходов БРг1 с установочными входами фиксированных разрядов РгП.

Выбор заявки на алгоритм в БРг1 осуществляется циклическим опросом групп разрядов соответствующего регистра заявок из

БРг1 и записью «1 (зая1в,ки) в соответствующий выбранному алгоритму разряд РгП. Таким образом, заявки в РгП становятся в очередь к ЦЛМ.

Выбор заявки в РгП производится по сигналам конца -оператора, имеющимся в .конце каждого оператора всех алгоритмов, путем циклического опроса разрядов РгП по вторым управляющим входам от ММУ; .каждому разряду регистра соответствует своя ячейка слова прерывания в ОЗУ, в которой записан адрес очередного оператора в алгоритме. :

ЦЛМ работает .следующим образом.

В текущий момент времени в конце выполнения последнего оператора ,в алгоритме работы, например, первого объекта управления при поступшении по вторым управляющим входам сигнала конца цикла работы да.нного объекта и по первому управляющему входу сигнала .«Конец .алгоритма от МУУ I производится опрос разрядов регистра БРг1 заявок на алгоритмы работы данного объекта управления.

Если в регистре нет заявок (нули во всех разрядах), то опрос ..повторяется до тех пор, пока в регистре не возникнет .хотя бы одна заявка (единичное состояние разряда).

Пусть заявка была выбрана во втором разряде регистра, в котором записана по второму устано.вочно му входу заявка ,от .первой позиции обслуживаемого объекта на алгоритм работы первого транспортного объекта управления. При этом соответствующий дещифратор адреса БДщА устанавливается в состояние «1, которое второму выходу пересылается в регистр-счетчик адреса ППЗУЗ, после чего в регистр числа ППЗУ считывается управляющее слово, относящееся .к первой позиции, от которой по второму уст ановочному входу поступила заявка на алгоритм; первый выход соответствующего дещифратора БДщА 8 управляет пересылкой кода обслуживаемого объекта, поступающего по пнформапиюнным входам через коммутатор блока коммутаторов БК 5 по первому входу в буферный регистр ББРг б, который будет использоваться при выполнении алгоритма работы первого объекта управления; сигналом выбора .заявки по второму управляющему входу во второй разряд РгП 9 заявок на операторы записывается «1, этим же сигналом запрещается дальнейщий опрос регистра ,(БРг1) ,7.

Таким образом, алгоритм работы первого объекта управления, обслуживающего первую позицию, стал в очередь к устройству логической обработки информации ЦЛМ.

В момент времени работы ЦЛМ в конце выполнения текущего оператора МУУ 1 выдает сигнал «Конец оператора для опроса РгП 9 на новый оператор для выполнения его ЦЛМ. Алгоритмы в регистре схемно выстроены в лорядке возрастания их номера приоритета. Если в лервом разряде не было заявки с высщим приоритетом, то выбирается заявка из второго разряда. При этом дещифратор адреса ОЗУ 2, связанный с регистром адреса ОЗУ 2, устанавливается в состояние ,«2, соответствующее адресу текущего слова прерывания для выбранного алгоритма. В момент выбора зая1в.ки код дещифратора адреса ОЗУ пересылается в регистр-счетчик адреса ОЗУ 2, опрос ,РгП 9 запрещается и выбранный разряд устанавливается в «О.

Содержимое текущего .слова прерывания, т. е. адрес первого оператора алгоритма в ОЗУ очитывается в регистр числа ОЗУ 2, а оттуда по сигналам местного устройства

управления пересылается в регистр-счетчик адреса ОЗУ. В регистр числа считывается адpeic записанной в МУУ 1 первой .микрокоманды, .который пересылается в регистр адреса |МУУ , адрес второй и последующих .микрокоманд формируется самим МУУ. Начинается выполнение первого оператора алгоритма, содержаюего ряд операций: например, выдача из регистра .числа ППЗУ 3 по -второму выходу объекту .управления координат первой позиции и других данных; перезапись кода обслуживаемого объекта из буферного регистра ББРг 6 ,в фиксированную ячейку промежуточной информации ОЗУ; прибавление «1 ,к содержимому текущего слова лрерывания (адрес текущего слова прерывания содержится в дещифраторе адреса ОЗУ); выдача сигнала «Конец оператора, опращивающего РгП 9 заявок на операторы.,

После отработки задания объект управления выдает сигнал «Конец цикла, который подается на первые разряды РгП 9, относящиеся к алгоритмам работы .первого объекта управления и воздействует только на возбужденный регистром БРг1 второй разряд,

устанавливая его в i«l.

Во время очередных .циклов опроса РгП 9 при отсутствии заяво.к с более высоким приоритетом произв-одится выбор заявки во втором разряде, обращение к текущему слову

прерывания и выполнение оператора начатого алгоритма.

Оператор определяет сл едующей позиции марщрута объекта управления и содержит следующие операции: пересылка из

фиксированной ячейки отсека промежуточной информации ОЗУ кода обслуживаемого объекта в буферный регистр ББРг 6; пересылка состояния соответствующего дешифратора адреса ОЗУ из БДщА 8 в регистр

адреса ППЗУ и считывание в регистр числа ППЗУ управляющего слова, относящегося к пер.вой позиции обслул иваемого объекта; пересылка из регистра числа ППЗУ в регистрсчетчик адреса ОЗУ адреса .начальной ячейки отсека ОЗУ технологических марщрутов; обращение к начальным ячейкам марщрутоБ, в которых записаны коды обслуживаемых объектов, сравнение их содержимого с кодом обслуживаемого объекта в буферном

регистре ББРг 6; по сигналу сравнения остаHote поиска и обр ащение к ячейке маршрута, содержащей счетчик слов ло маршруту; обращение к ячейке марщрута, адрес которой записан в счетчике слов, и считывание в регистр числа ОЗУ управляющего слова маршрута; пересылка из регистра числа ОЗУ 2 .кода помера следующей .позиции по маршруту в регистр адреса ППЗУ 3 и о.бращение к управляющему слову позиции; выдача из регистра числа ППЗУ координат следующей позиции и других данинх объекту упра вления; добавление «1 к текущему слову |Прерывания; выдача .сигнала «Конец оператора-жонец алгоритма для опроса РгП 9 и опроса после прихода .сигнала .«Коиец .цикла .от объекта управления Рг заявок на алгоритмы работы первого объекта управления .БРг1.

Аппаратная реализация режима разделения машинного времени между алгоритмами одновременно управляемых объектов повышает козффииие-нт использ ования оборудования ЦЛМ по сравнению с существующими ЭВМ за счет сокращения непроизводительных потерь машинного времени и объема памяти. Применение ЦЛМ, в Чзстности, для управления транспортно-накопительными системами деталей и инструментов в АСУ интегрированными участками и переналаживаемыми линиями мелко- и среднесерийных производств металлообрабатывающей промыщленности, обеспечивает повышение коэффициента загрузки технологического оборудования за счет сокращения межоперационного времени в технологических маршрутах обработки деталей на участках и в линиях с большим .количеством станочных агрегатов.

Формула изобретения

Цифровая логическая машина, содержащая .микропрограммное устройство управления, оперативное заноминаюшее устройство, полупостоянное запоминающее устройство и устройство связи с 0;бъектами, причем первый и второй выходы и первый вход микропрограммного устройства управления соединены с первым и вторым вХодами и первым выходом оперативного запоминающего устройства, третий вход и второй выход оперативного запоминающего устройства связаны с .первым выходом и первым входом полупостоянного запоминающего .устройства, а третий выход - с .выходом цифровой логИческой ма.шины, второй выход полупЪстоянного запоминающего зСтройства соединен с Bbixotд ом цифровой логической машины, а второй вход - с третьим выходом микропрограммного устройства .уцравления, отличающаяс я тем, что, с целью ,повышения коэффициента использования оборудования, устройство связки с объектами coдepжiит блок коммутаторЪв, блок буферных регистров, блок регистров .первого уровня, блок адресных дешифраторов и регистр второго уровня, причем управляющие входы блока .коммутаторов соединены с первыми выходами блока адресных дешифраторов, информационные входы- с соответствующими входами цифровой

логической .машины, а выходы-с первыми входами блока буферных регистров, .вторые входы .которого, связаны с соответсгвующими выходами оперативного запоминающего устройства ,управляющие входы - с соответствующими .выходами микропрограммного устройства упра вления, основные выходы - с соответствующими входами оперативного запоминающего устройства, а дополнительные вход и «выход - с соответствующими вхоДом и выходом цифровой логической машины, BTopfrie выходы блака адресных дешифраторов связаны с соответствующими входами л о л.у по сто ЯП но го запоминающего устройства, а входы - с установочными входами

регистра второго .уровня и выходами блока регистров первого уров.ня, лервые управляюшие и первые установочные входы которого (соединены с ,соответствую.щими выходами микропрограммного устройства управления,

вторые управляющие входы - с соответствующими входами цифровой логической машины и первыми управляющими входами регистра второго уровня, вторые управляющие входы которого связаны с соответствую|Щими выходами микропрограммного устройства управления, а выходы-с соответствующими входами оперативно.го запоминающего устройства, вторые установочные входы блока регистров первого уровня соединены с соответствующими входами цифровой логической машины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| ПРОГРАММАТОР | 1991 |

|

RU2078381C1 |

| ЭЛЕКТРОННЫЕ ЧАСЫ С РЕЧЕВЫМ ОПОВЕЩЕНИЕМ | 1992 |

|

RU2029333C1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Программируемое постоянное запоминающее устройство | 1984 |

|

SU1300563A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Однородный параллельный процессор | 1978 |

|

SU736107A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

Авторы

Даты

1977-05-15—Публикация

1974-04-30—Подача